Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 8MHz                                                                      |

| Connectivity               | -                                                                         |

| Peripherals                | POR, WDT                                                                  |

| Number of I/O              | 4                                                                         |

| Program Memory Size        | 768B (512 x 12)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | -                                                                         |

| RAM Size                   | 23 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 2x8b                                                                  |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | SOT-23-6                                                                  |

| Supplier Device Package    | SOT-23-6                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic10f222t-i-ot |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 1.0   | General Description                                    | 5  |

|-------|--------------------------------------------------------|----|

| 2.0   | Device Varieties                                       |    |

| 3.0   | Architectural Overview                                 |    |

| 4.0   | Memory Organization<br>I/O Port                        | 13 |

| 5.0   | I/O Port                                               | 21 |

| 6.0   | TMR0 Module and TMR0 Register                          | 25 |

| 7.0   | Analog-to-Digital (A/D) converter                      | 29 |

| 8.0   | Special Features Of The CPU<br>Instruction Set Summary | 33 |

| 9.0   | Instruction Set Summary                                | 43 |

| 10.0  | Electrical Characteristics                             | 51 |

| 11.0  | Development Support                                    | 61 |

| 12.0  | DC and AC Characteristics Graphs and Charts            | 69 |

| 13.0  | Packaging Information                                  | 73 |

|       |                                                        |    |

| The N | /icrochip Web Site                                     | 83 |

| Custo | mer Change Notification Service                        | 83 |

| Custo | mer Support                                            | 83 |

| Produ | Ict Identification System                              | 85 |

## TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@mail.microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000A is version A of document DS30000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

- The Microchip Corporate Literature Center; U.S. FAX: (480) 792-7277

When contacting a sales office or the literature center, please specify which device, revision of silicon and data sheet (include \_literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com/cn to receive the most current information on all of our products.

NOTES:

## 2.0 DEVICE VARIETIES

A variety of packaging options are available. Depending on application and production requirements, the proper device option can be selected using the information in this section. When placing orders, please use the PIC10F220/222 Product Identification System at the back of this data sheet to specify the correct part number.

## 2.1 Quick Turn Programming (QTP) Devices

Microchip offers a QTP programming service for factory production orders. This service is made available for users who choose not to program medium-to-high quantity units and whose code patterns have stabilized. The devices are identical to the Flash devices but with all Flash locations and fuse options already programmed by the factory. Certain code and prototype verification procedures do apply before production shipments are available. Please contact your local Microchip Technology sales office for more details.

## 2.2 Serialized Quick Turn Programming<sup>SM</sup> (SQTP<sup>SM</sup>) Devices

Microchip offers a unique programming service, where a few user-defined locations in each device are programmed with different serial numbers. The serial numbers may be random, pseudo-random or sequential.

Serial programming allows each device to have a unique number, which can serve as an entry-code, password or ID number.

NOTES:

## 4.6 OSCCAL Register

**REGISTER 4-3:**

The Oscillator Calibration (OSCCAL) register is used to calibrate the internal precision 4/8 MHz oscillator. It contains seven bits for calibration.

| Note: | Erasing the device will also erase the pre- |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|

|       | programmed internal calibration value for   |  |  |  |  |

|       | the internal oscillator. The calibration    |  |  |  |  |

|       | value must be read prior to erasing the     |  |  |  |  |

|       | part so it can be reprogrammed correctly    |  |  |  |  |

|       | later.                                      |  |  |  |  |

After you move in the calibration constant, do not change the value. See Section 8.2.2 "Internal 4/8 MHz Oscillator".

| R/W-1     | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-1 | R/W-0 |

|-----------|-------|-------|-------|-------|-------|-------|-------|

| CAL6      | CAL5  | CAL4  | CAL3  | CAL2  | CAL1  | CAL0  | FOSC4 |

| bit 7 bit |       |       |       |       |       |       | bit 0 |

|           |       |       |       |       |       |       |       |

OSCCAL – OSCILLATOR CALIBRATION REGISTER (ADDRESS: 05h)

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-1

CAL<6:0>: Oscillator Calibration bits

0111111 = Maximum frequency

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

•

<

Note 1: Overrides GP2/T0CKI control registers when enabled.

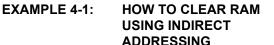

### 4.9 Indirect Data Addressing; INDF and FSR Registers

The INDF register is not a physical register. Addressing INDF actually addresses the register whose address is contained in the FSR register (FSR is a *pointer*). This is indirect addressing.

#### 4.9.1 INDIRECT ADDRESSING

- · Register file 09 contains the value 10h

- · Register file 0A contains the value 0Ah

- · Load the value 09 into the FSR register

- A read of the INDF register will return the value of 10h

- Increment the value of the FSR register by one (FSR = 0A)

- A read of the INDR register now will return the value of 0Ah.

Reading INDF itself indirectly (FSR = 0) will produce 00h. Writing to the INDF register indirectly results in a no-operation (although Status bits may be affected).

A simple program to clear RAM locations 10h-1Fh using Indirect addressing is shown in Example 4-1.

#### FIGURE 4-6: DIRECT/INDIRECT ADDRESSING

|      |                                |                              | DILLOUINO                                                                  |

|------|--------------------------------|------------------------------|----------------------------------------------------------------------------|

| NEXT | MOVLW<br>MOVWF<br>CLRF<br>INCF | 0x10<br>FSR<br>INDF<br>FSR,F | ;initialize pointer<br>;to RAM<br>;clear INDF<br>;register<br>;inc pointer |

|      | BTFSC<br>GOTO                  | FSR <b>,</b> 4<br>NEXT       | ;all done?<br>;NO, clear next                                              |

| CONT | INUE                           |                              |                                                                            |

|      | :                              |                              | ;YES, continue                                                             |

|      | :                              |                              |                                                                            |

|      |                                |                              |                                                                            |

The FSR is a 5-bit wide register. It is used in conjunction with the INDF register to indirectly address the data memory area.

The FSR<4:0> bits are used to select data memory addresses 00h to 1Fh.

**Note:** Do not use banking. FSR <7:5> are unimplemented and read as '1's.

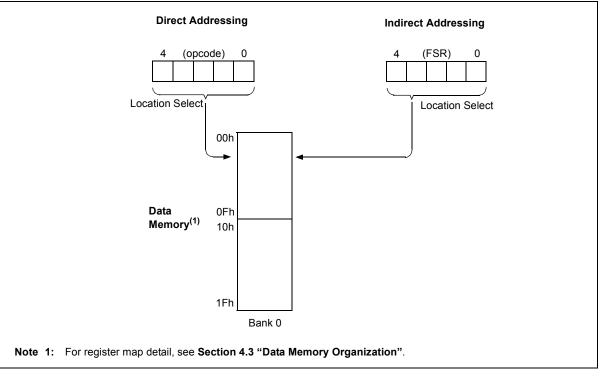

## FIGURE 6-3: TIMER0 TIMING: INTERNAL CLOCK/PRESCALE 1:2

#### TABLE 6-1: REGISTERS ASSOCIATED WITH TIMER0

| Address | Name                    | Bit 7    | Bit 6                                 | Bit 5 | Bit 4 | Bit 3   | Bit 2     | Bit 1 | Bit 0     | Value on<br>Power-On<br>Reset | Value on<br>All Other<br>Resets |

|---------|-------------------------|----------|---------------------------------------|-------|-------|---------|-----------|-------|-----------|-------------------------------|---------------------------------|

| 01h     | TMR0                    | Timer0 – | imer0 – 8-Bit Real-Time Clock/Counter |       |       |         |           |       | XXXX XXXX | uuuu uuuu                     |                                 |

| N/A     | OPTION                  | GPWU     | GPPU                                  | TOCS  | T0SE  | PSA     | PS2       | PS1   | PS0       | 1111 1111                     | 1111 1111                       |

| N/A     | TRISGPIO <sup>(1)</sup> | —        | _                                     |       |       | I/O Cor | ntrol Reg | ister |           | 1111                          | 1111                            |

Legend: Shaded cells not used by Timer0, - = unimplemented, x = unknown, u = unchanged.

Note 1: The TRIS of the TOCKI pin is overridden when TOCS = 1

#### 6.1 Using Timer0 With An External Clock

When an external clock input is used for Timer0, it must meet certain requirements. The external clock requirement is due to internal phase clock (Tosc) synchronization. Also, there is a delay in the actual incrementing of Timer0 after synchronization.

### 6.1.1 EXTERNAL CLOCK SYNCHRONIZATION

When no prescaler is used, the external clock input is the same as the prescaler output. The synchronization of T0CKI with the internal phase clocks is accomplished by sampling the prescaler output on the Q2 and Q4 cycles of the internal phase clocks (Figure 6-4). Therefore, it is necessary for T0CKI to be high for at least 2Tosc (and a small RC delay of 2Tt0H) and low for at least 2Tosc (and a small RC delay of 2Tt0H). Refer to the electrical specification of the desired device.

When a prescaler is used, the external clock input is divided by the asynchronous ripple counter-type prescaler, so that the prescaler output is symmetrical. For the external clock to meet the sampling requirement, the ripple counter must be taken into account. Therefore, it is necessary for TOCKI to have a period of at least 4Tosc (and a small RC delay of 4Tt0H) divided by the prescaler value. The only requirement on TOCKI high and low time is that they do not violate the minimum pulse width requirement of Tt0H. Refer to parameters 40, 41 and 42 in the electrical specification of the desired device.

## 7.0 ANALOG-TO-DIGITAL (A/D) CONVERTER

The A/D converter allows conversion of an analog signal into an 8-bit digital signal.

## 7.1 Clock Divisors

The A/D Converter has a single clock source setting, INTOSC/4. The A/D Converter requires 13 TAD periods to complete a conversion. The divisor values do not affect the number of TAD periods required to perform a conversion. The divisor values determine the length of the TAD period.

**Note:** Due to the fixed clock divisor, a conversion will complete in 13 CPU instruction cycles.

## 7.2 Voltage Reference

Due to the nature of the design, there is no external voltage reference allowed for the A/D Converter. The A/D Converter reference voltage will always be VDD.

## 7.3 Analog Mode Selection

The ANS<1:0> bits are used to configure pins for analog input. Upon any Reset ANS<1:0> defaults to 11. This configures pins AN0 and AN1 as analog inputs. Pins configured as analog inputs are not available for digital output. Users should not change the ANS bits while a conversion is in process. ANS bits are active regardless of the condition of ADON.

## 7.4 A/D Converter Channel Selection

The CHS bits are used to select the analog channel to be sampled by the A/D Converter. The CHS bits should not be changed during a conversion. To acquire an analog signal, the CHS selection must match one of the pin(s) selected by the ANS bits. The Internal Absolute Voltage Reference can be selected regardless of the condition of the ANS bits. All channel selection information will be lost when the device enters Sleep. Note: The A/D Converter module consumes power when the ADON bit is set even when no channels are selected as analog inputs. For low-power applications, it is recommended that the ADON bit be cleared when the A/D Converter is not in use.

## 7.5 The GO/DONE bit

The GO/DONE bit is used to determine the status of a conversion, to start a conversion and to manually halt a conversion in process. Setting the GO/DONE bit starts a conversion. When the conversion is complete, the A/D Converter module clears the GO/DONE bit. A conversion can be terminated by manually clearing the GO/DONE bit while a conversion is in process. Manual termination of a conversion may result in a partially converted result in ADRES.

The GO/DONE bit is cleared when the device enters Sleep, stopping the current conversion. The A/D Converter does not have a dedicated oscillator, it runs off of the system clock.

The GO/DONE bit cannot be set when ADON is clear.

## 7.6 Sleep

This A/D Converter does not have a dedicated A/D Converter clock and therefore no conversion in Sleep is possible. If a conversion is underway and a Sleep command is executed, the GO/DONE and ADON bit will be cleared. This will stop any conversion in process and power-down the A/D Converter module to conserve power. Due to the nature of the conversion process, the ADRES may contain a partial conversion. At least 1 bit must have been converted prior to Sleep to have partial conversion data in ADRES. The CHS bits are reset to their default condition and CHS<1:0> = 11.

For accurate conversions, TAD must meet the following:

- + 500 ns < TAD < 50  $\mu s$

- TAD = 1/(FOSC/divisor)

|                | ANS1      | ANS0      | CHS1 | CHS0 | GO/DONE | ADON |

|----------------|-----------|-----------|------|------|---------|------|

| Prior to Sleep | Х         | Х         | Х    | Х    | 0       | 0    |

| Prior to Sleep | х         | х         | х    | х    | 1       | 1    |

| Entering Sleep | Unchanged | Unchanged | 1    | 1    | 0       | 0    |

| Wake           | 1         | 1         | 1    | 1    | 0       | 0    |

TABLE 7-1:

EFFECTS OF SLEEP AND WAKE ON ADCON0

## 7.9 A/D Acquisition Requirements

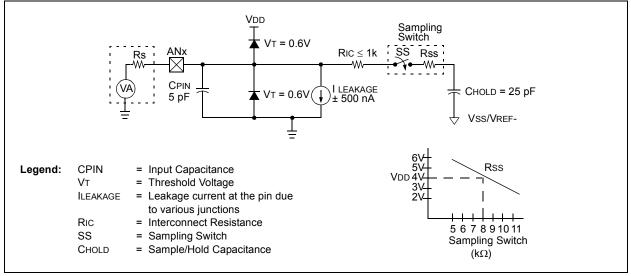

For the ADC to meet its specified accuracy, the charge holding capacitor (CHOLD) must be allowed to fully charge to the input channel voltage level. The Analog Input model is shown in Figure 7-1. The source impedance (Rs) and the internal sampling switch (Rss) impedance directly affect the time required to charge the capacitor CHOLD. The sampling switch (Rss) impedance varies over the device voltage (VDD), see Figure 7-1. **The maximum recommended impedance for analog sources is 10 k** $\Omega$ . As the source impedance is decreased, the acquisition time may be decreased.

After the analog input channel is selected (or changed), an A/D acquisition must be done before the conversion can be started. To calculate the minimum acquisition time, Equation 7-1 may be used. This equation assumes that 1/2 LSb error is used (256 steps for the ADC). The 1/2 LSb error is the maximum error allowed for the ADC to meet its specified resolution.

### EQUATION 7-1: ACQUISITION TIME EXAMPLE

| Assumptions:    |             |     |                                                                                  |

|-----------------|-------------|-----|----------------------------------------------------------------------------------|

|                 | Temperature | 2 = | 50°C and external impedance of 10 k $\Omega$ 5.0V VDD                            |

|                 | Tacq        | =   | Amplifier Settling Time + Hold Capacitor Charging Time + Temperature Coefficient |

|                 |             | =   | TAMP + TC + TCOFF                                                                |

|                 |             | =   | $2 \ \mu s + TC + [(Temperature - 25^{\circ}C)(0.05 \ \mu s/^{\circ}C)]$         |

| Solving for Tc: |             |     |                                                                                  |

|                 | Тс          | =   | CHOLD (RIC + RSS + RS) In(1/512)                                                 |

|                 |             | =   | $-25pF(l k\Omega + 7 k\Omega + 10 k\Omega) In(0.00196)$                          |

|                 |             | =   | 2.81 µs                                                                          |

| Therefore:      |             |     |                                                                                  |

|                 | Tacq        | =   | $2 \mu s + 2.81 \mu s + [(50^{\circ}C-25^{\circ}C)(0.05 \mu s/^{\circ}C)]$       |

|                 |             | =   | 6.06 µs                                                                          |

|                 |             |     |                                                                                  |

Note 1: The charge holding capacitor (CHOLD) is not discharged after each conversion.

**2:** The maximum recommended impedance for analog sources is 10 k $\Omega$ . This is required to meet the pin leakage specification.

#### 8.9.2 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. An external Reset input on GP3/MCLR/VPP pin, when configured as MCLR.

- 2. A Watchdog Timer Time-out Reset (if WDT was enabled).

- 3. A change on input pin GP0, GP1 or GP3 when wake-up on change is enabled.

These events cause a device Reset. The  $\overline{\text{TO}}$ ,  $\overline{\text{PD}}$  GPWUF bits can be used to determine the cause of a device Reset. The  $\overline{\text{TO}}$  bit is cleared if a WDT time-out occurred (and caused wake-up). The  $\overline{\text{PD}}$  bit, which is set on power-up, is cleared when SLEEP is invoked. The GPWUF bit indicates a change in state while in Sleep at pins GP0, GP1 or GP3 (since the last file or bit operation on GP port).

- **Caution:** Right before entering Sleep, read the input pins. When in Sleep, wake up occurs when the values at the pins change from the state they were in at the last reading. If a wake-up on change occurs and the pins are not read before re-entering Sleep, a wake-up will occur immediately even if no pins change while in Sleep mode.

- Note: The WDT is cleared when the device wakes from Sleep, regardless of the wakeup source.

### 8.10 Program Verification/Code Protection

If the Code Protection bit has not been programmed, the on-chip program memory can be read out for verification purposes.

The first 64 locations and the last location (Reset Vector) can be read, regardless of the code protection bit setting.

### 8.11 ID Locations

Four memory locations are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during program/verify.

Use only the lower 4 bits of the ID locations and always program the upper 8 bits as '1's.

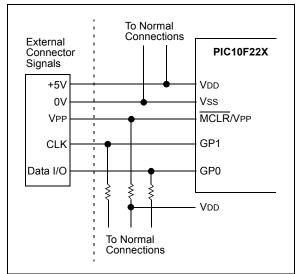

## 8.12 In-Circuit Serial Programming™

The PIC10F220/222 microcontrollers can be serially programmed while in the end application circuit. This is simply done with two lines for clock and data, and three other lines for power, ground and the programming voltage. This allows customers to manufacture boards with unprogrammed devices and then program the microcontroller just before shipping the product. This also allows the most recent firmware, or a custom firmware, to be programmed.

The devices are placed into a Program/Verify mode by holding the GP1 and GP0 pins low while raising the MCLR (VPP) pin from VIL to VIHH (see programming specification). GP1 becomes the programming clock and GP0 becomes the programming data. Both GP1 and GP0 are Schmitt Trigger inputs in this mode.

After Reset, a 6-bit command is then supplied to the device. Depending on the command, 16 bits of program data are then supplied to or from the device, depending if the command was a Load or a Read. For complete details of serial programming, please refer to the PIC10F220/222 Programming Specifications.

A typical In-Circuit Serial Programming connection is shown in Figure 8-10.

FIGURE 8-10:

#### TYPICAL IN-CIRCUIT SERIAL PROGRAMMING™ CONNECTION

| IORWF            | Inclusive OR W with f                                                                                                                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] IORWF f,d                                                                                                                                      |

| Operands:        | $\begin{array}{l} 0\leq f\leq 31\\ d\in [0,1] \end{array}$                                                                                                      |

| Operation:       | (W).OR. (f) $\rightarrow$ (dest)                                                                                                                                |

| Status Affected: | Z                                                                                                                                                               |

| Description:     | Inclusive OR the W register with register 'f'. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |

| MOVWF            | Move W to f                                    |

|------------------|------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVWF f                       |

| Operands:        | $0 \leq f \leq 31$                             |

| Operation:       | $(W) \rightarrow (f)$                          |

| Status Affected: | None                                           |

| Description:     | Move data from the W register to register 'f'. |

| MOVF             | Move f                                                                                                                                                                                                                                                           |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] MOVF f,d                                                                                                                                                                                                                                        |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 31 \\ d  \in  [0,1] \end{array}$                                                                                                                                                                                                 |

| Operation:       | $(f) \rightarrow (dest)$                                                                                                                                                                                                                                         |

| Status Affected: | Z                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>moved to destination 'd'. If 'd' is '0',<br>destination is the W register. If 'd'<br>is '1', the destination is file register<br>'f'. 'd' = 1 is useful as a test of a file<br>register, since status flag Z is<br>affected. |

| NOP              | No Operation  |  |  |  |

|------------------|---------------|--|--|--|

| Syntax:          | [label] NOP   |  |  |  |

| Operands:        | None          |  |  |  |

| Operation:       | No operation  |  |  |  |

| Status Affected: | None          |  |  |  |

| Description:     | No operation. |  |  |  |

| MOVLW            | Move Literal to W                                                                                  |  |  |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] MOVLW k                                                                           |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                  |  |  |  |  |  |

| Operation:       | $k \rightarrow (W)$                                                                                |  |  |  |  |  |

| Status Affected: | None                                                                                               |  |  |  |  |  |

| Description:     | The eight-bit literal 'k' is loaded into the W register. The "don't cares" will assembled as '0's. |  |  |  |  |  |

| OPTION           | Load OPTION Register                                                 |  |  |  |  |

|------------------|----------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [label] OPTION                                                       |  |  |  |  |

| Operands:        | None                                                                 |  |  |  |  |

| Operation:       | $(W) \rightarrow OPTION$                                             |  |  |  |  |

| Status Affected: | None                                                                 |  |  |  |  |

| Description:     | The content of the W register is<br>loaded into the OPTION register. |  |  |  |  |

| DC CHARACTERISTICS              |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature $-40 \times C \le TA \le +85^{\circ}C$ (industrial) |       |                    |     |            |                          |

|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------|-------|--------------------|-----|------------|--------------------------|

| Param<br>No.                    | Sym  | Characteristic                                                                                                                          | Min   | Typ <sup>(1)</sup> | Max | Units      | Conditions               |

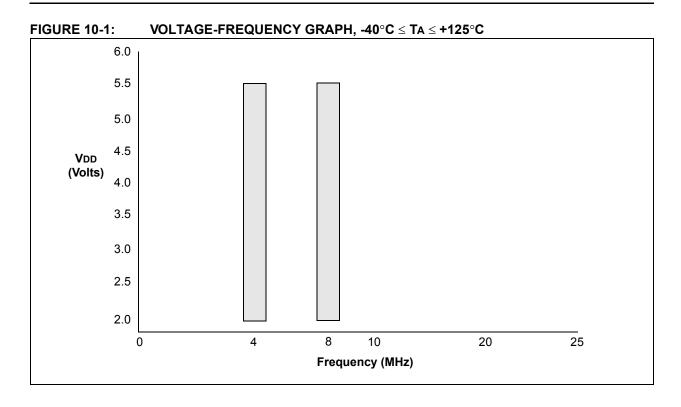

| D001                            | Vdd  | Supply Voltage                                                                                                                          | 2.0   |                    | 5.5 | V          | See Figure 10-1          |

| D002                            | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                                                                               | 1.5*  |                    |     | V          | Device in Sleep mode     |

| D003                            | VPOR | VDD Start Voltage<br>to ensure Power-on Reset                                                                                           | —     | Vss                |     | V          |                          |

| D004                            | SVDD | VDD Rise Rate<br>to ensure Power-on Reset                                                                                               | 0.05* | —                  |     | V/ms       |                          |

|                                 | IDD  | Supply Current <sup>(3)</sup>                                                                                                           |       |                    |     |            |                          |

| D010                            |      |                                                                                                                                         | _     | 175                | 275 | μA         | VDD = 2.0V, Fosc = 4 MHz |

|                                 |      |                                                                                                                                         | _     | 0.625              | 1.1 | mA         | VDD = 5.0V, Fosc = 4 MHz |

|                                 |      |                                                                                                                                         | —     | 250                | 400 | μA         | VDD = 2.0V, Fosc = 8 MHz |

|                                 |      |                                                                                                                                         | —     | 0.800              | 1.5 | mA         | VDD = 5.0V, Fosc = 8 MHz |

|                                 | IPD  | Power-down Current <sup>(4)</sup>                                                                                                       |       | •                  |     |            |                          |

| D020                            |      |                                                                                                                                         | _     | 0.1                | 1.2 | μA         | VDD = 2.0V               |

|                                 |      | —                                                                                                                                       | 1     | 2.4                | μA  | VDD = 5.0V |                          |

| IWDT WDT Current <sup>(4)</sup> |      |                                                                                                                                         |       |                    | ·   |            |                          |

| D022                            |      |                                                                                                                                         |       | 1.0                | 3   | μA         | VDD = 2.0V               |

|                                 |      |                                                                                                                                         | —     | 7                  | 16  | μA         | VDD = 5.0V               |

### 10.1 DC Characteristics: PIC10F220/222 (Industrial)

These parameters are characterized but not tested.

**Note 1:** Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

All I/O pins tri-stated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss. The peripheral current is the sum of the base IPD and the additional current consumed when the peripheral is enabled.

## 10.2 DC Characteristics: PIC10F220/222 (Extended)

| DC CHARACTERISTICS |      | Standard Operating Conditions (unless otherwise specified)<br>Operating Temperature -40×C £ TA £ +125×C (extended) |                                            |                              |                          |                      |                                                                                                              |

|--------------------|------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------|--------------------------|----------------------|--------------------------------------------------------------------------------------------------------------|

| Param<br>No.       | Sym  | Characteristic                                                                                                     | Min Typ <sup>(1)</sup> Max Units Condition |                              | Conditions               |                      |                                                                                                              |

| D001               | Vdd  | Supply Voltage                                                                                                     | 2.0                                        |                              | 5.5                      | V                    | See Figure 10-1                                                                                              |

| D002               | Vdr  | RAM Data Retention Voltage <sup>(2)</sup>                                                                          | 1.5*                                       |                              |                          | V                    | Device in Sleep mode                                                                                         |

| D003               | VPOR | VDD Start Voltage<br>to ensure Power-on Reset                                                                      | -                                          | Vss                          | -                        | V                    |                                                                                                              |

|                    | IDD  | Supply Current <sup>(3)</sup>                                                                                      |                                            |                              |                          |                      |                                                                                                              |

| D010               |      |                                                                                                                    |                                            | 175<br>0.625<br>250<br>0.800 | 275<br>1.1<br>400<br>1.5 | μΑ<br>mA<br>μA<br>mA | VDD = 2.0V, Fosc = 4 MHz<br>VDD = 5.0V, Fosc = 4 MHz<br>VDD = 2.0V, Fosc = 8 MHz<br>VDD = 5.0V, Fosc = 8 MHz |

|                    | IPD  | Power-down Current <sup>(4)</sup>                                                                                  |                                            |                              |                          |                      |                                                                                                              |

| D020               |      |                                                                                                                    | _                                          | 0.1<br>1                     | 9<br>15                  | μΑ<br>μΑ             | VDD = 2.0V<br>VDD = 5.0V                                                                                     |

|                    | Iwdt | WDT Current <sup>(4)</sup>                                                                                         |                                            |                              |                          |                      | •                                                                                                            |

| D022               |      |                                                                                                                    | _                                          | 1.0<br>7                     | 18<br>22                 | μΑ<br>μΑ             | VDD = 2.0V<br>VDD = 5.0V                                                                                     |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is based on characterization results at 25°C. This data is for design guidance only and is not tested.

2: This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

**3:** The supply current is mainly a function of the operating voltage and frequency. Other factors such as bus loading, bus rate, internal code execution pattern and temperature also have an impact on the current consumption.

a) The test conditions for all IDD measurements in active operation mode are:

All I/O pins tri-stated, pulled to Vss, TOCKI = VDD, MCLR = VDD; WDT enabled/disabled as specified.

b) For standby current measurements, the conditions are the same, except that the device is in Sleep mode.

4: Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD or Vss. The peripheral current is the sum of the base IPD and the additional current consumed when the peripheral is enabled.

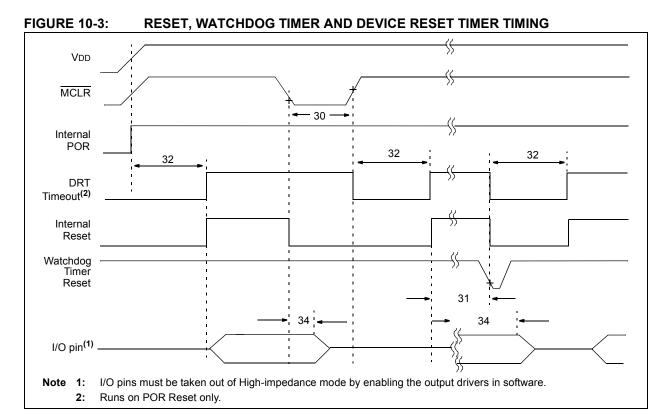

#### RESET, WATCHDOG TIMER AND DEVICE RESET TIMER - PIC10F220/222 TABLE 10-3:

| AC CHARACTERISTICS |                  | Standard Operating Conditions (unless otherwise specified)Operating Temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ (industrial) $-40^{\circ}C \le TA \le +125^{\circ}C$ (extended)Operating Voltage VDD range is described in Section 10.1 "DCCharacteristics:PIC10F220/222 (Industrial)" |                                             |                |              |          |                                                  |

|--------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|----------------|--------------|----------|--------------------------------------------------|

| Param<br>No.       | Sym              | Characteristic                                                                                                                                                                                                                                                                                | Min Typ <sup>(1)</sup> Max Units Conditions |                |              |          | Conditions                                       |

| 30                 | Тмс <sub>L</sub> | MCLR Pulse Width (low)                                                                                                                                                                                                                                                                        | 2*<br>5*                                    | _              |              | μS<br>μS | VDD = 5V, -40°C to +85°C<br>VDD = 5.0V           |

| 31                 | Twdt             | Watchdog Timer Time-out Period (no prescaler)                                                                                                                                                                                                                                                 | 10<br>10                                    | 18<br>18       | 29<br>31     | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 32                 | Tdrt*            | Device Reset Timer Period<br>(standard)                                                                                                                                                                                                                                                       | 0.600<br>0.600                              | 1.125<br>1.125 | 1.85<br>1.95 | ms<br>ms | VDD = 5.0V (Industrial)<br>VDD = 5.0V (Extended) |

| 34                 | Tioz             | I/O High-impedance from MCLR low                                                                                                                                                                                                                                                              | _                                           | _              | 2*           | μS       |                                                  |

These parameters are characterized but not tested.

Note 1: Data in the Typical ("Typ") column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

## 12.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 12.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

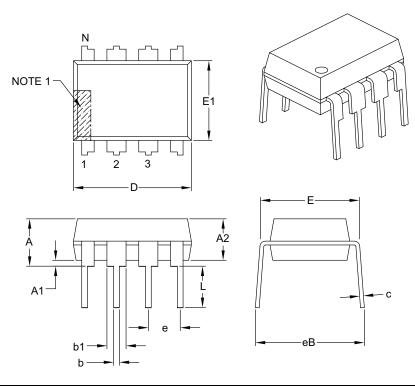

## 8-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units          |      |          | INCHES |  |  |

|----------------------------|----------------|------|----------|--------|--|--|

| Dir                        | nension Limits | MIN  | NOM      | MAX    |  |  |

| Number of Pins             | N              |      | 8        |        |  |  |

| Pitch                      | e              |      | .100 BSC |        |  |  |

| Top to Seating Plane       | А              | _    | -        | .210   |  |  |

| Molded Package Thickness   | A2             | .115 | .130     | .195   |  |  |

| Base to Seating Plane      | A1             | .015 | -        | -      |  |  |

| Shoulder to Shoulder Width | E              | .290 | .310     | .325   |  |  |

| Molded Package Width       | E1             | .240 | .250     | .280   |  |  |

| Overall Length             | D              | .348 | .365     | .400   |  |  |

| Tip to Seating Plane       | L              | .115 | .130     | .150   |  |  |

| Lead Thickness             | С              | .008 | .010     | .015   |  |  |

| Upper Lead Width           | b1             | .040 | .060     | .070   |  |  |

| Lower Lead Width           | b              | .014 | .018     | .022   |  |  |

| Overall Row Spacing §      | eB             | _    | —        | .430   |  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

## W

| Wake-up from Sleep         | 41     |

|----------------------------|--------|

| Watchdog Timer (WDT)       | 33, 38 |

| Period                     |        |

| Programming Considerations |        |

| WWW Address                | 75     |

| WWW, On-Line Support       | 3      |

| Z                          |        |

| Zero bit                   | 9      |

NOTES:

## **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PART NO.<br>Device    | X <u>/XX</u> XXX<br>Temperature Package Pattern<br>Range                                                  | <ul> <li>Examples:</li> <li>a) PIC10F220-I/P = Industrial temp., PDIP package (Pb-free)</li> <li>b) PIC10F222T-E/OT = Extended temp., SOT-23 package (Pb-free), Tape and Reel</li> </ul> |

|-----------------------|-----------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device:               | PIC10F220<br>PIC10F222<br>PIC10F220T (Tape & Reel)<br>PIC10F222T (Tape & Reel)                            | <ul> <li>c) PIC10F222-E/MC = Extended temp., DFN package (Pb-free)</li> </ul>                                                                                                            |

| Temperature<br>Range: | I = $-40^{\circ}$ C to $+85^{\circ}$ C (Industrial)<br>E = $-40^{\circ}$ C to $+125^{\circ}$ C (Extended) |                                                                                                                                                                                          |

| Package:              | P = 300 mil PDIP (Pb-free)<br>OT = SOT-23, 6-LD (Pb-free)<br>MC = DFN, 8-LD 2x3 (Pb-free)                 |                                                                                                                                                                                          |

| Pattern:              | Special Requirements                                                                                      |                                                                                                                                                                                          |