#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XF

| Product Status             | Active                                                    |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | Coldfire V1                                               |

| Core Size                  | 32-Bit Single-Core                                        |

| Speed                      | 50MHz                                                     |

| Connectivity               | EBI/EMI, I <sup>2</sup> C, SPI, UART/USART                |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                   |

| Number of I/O              | 31                                                        |

| Program Memory Size        | 32KB (32K x 8)                                            |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 8K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                              |

| Data Converters            | A/D 11x12b; D/A 1x12b                                     |

| Oscillator Type            | External                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 44-VFLGA Exposed Pad                                      |

| Supplier Device Package    | 44-MAPLGA (5x5)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf51qu32vhs |

|                            |                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.4.1 Example

This is an example of an operating rating:

| Symbol          | Description               | Min. | Max. | Unit |

|-----------------|---------------------------|------|------|------|

| V <sub>DD</sub> | 1.0 V core supply voltage | -0.3 | 1.2  | V    |

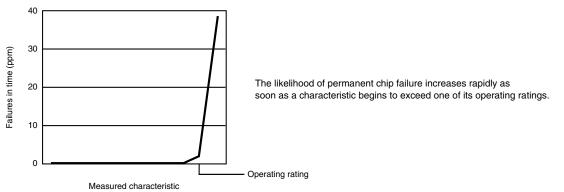

#### **Result of exceeding a rating** 3.5

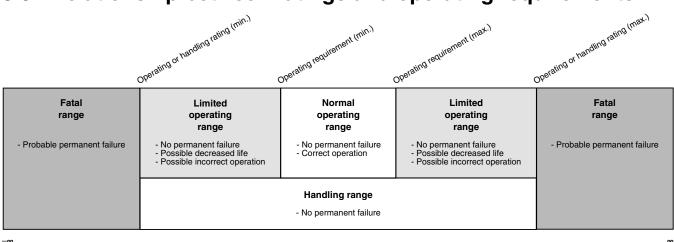

### Relationship between ratings and operating requirements 3.6

#### 3.7 Guidelines for ratings and operating requirements

Follow these guidelines for ratings and operating requirements:

• Never exceed any of the chip's ratings.

# 5.2 Nonswitching electrical specifications

## 5.2.1 Voltage and Current Operating Requirements

Table 1. Voltage and current operating requirements

| Symbol                     | Description                                                                                        | Min.                 | Max.                 | Unit | Notes |

|----------------------------|----------------------------------------------------------------------------------------------------|----------------------|----------------------|------|-------|

| V <sub>DD</sub>            | Supply voltage                                                                                     | 1.71                 | 3.6                  | V    |       |

| V <sub>DDA</sub>           | Analog supply voltage                                                                              | 1.71                 | 3.6                  | V    |       |

| $V_{DD} - V_{DDA}$         | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                          | -0.1                 | 0.1                  | V    |       |

| $V_{\rm SS} - V_{\rm SSA}$ | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                          | -0.1                 | 0.1                  | V    |       |

| V <sub>IH</sub>            | Input high voltage                                                                                 |                      |                      |      | 1     |

|                            | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                       | $0.7 \times V_{DD}$  | —                    | V    |       |

|                            | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                       | $0.75 \times V_{DD}$ | _                    | V    |       |

| V <sub>IL</sub>            | Input low voltage                                                                                  |                      |                      |      | 2     |

|                            | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                        | _                    | $0.35 \times V_{DD}$ | V    |       |

|                            | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                       | —                    | $0.3 \times V_{DD}$  | V    |       |

| I <sub>IC</sub>            | DC injection current — single pin                                                                  |                      |                      |      | 3     |

|                            | • V <sub>IN</sub> > V <sub>DD</sub>                                                                | 0                    | 2                    | mA   |       |

|                            | • V <sub>IN</sub> < V <sub>SS</sub>                                                                | 0                    | -0.2                 | mA   |       |

|                            | DC injection current — total MCU limit, includes sum                                               |                      |                      |      | 3     |

|                            | of all stressed pins<br>• V <sub>IN</sub> > V <sub>DD</sub>                                        | 0                    | 25                   | mA   |       |

|                            | <ul> <li>V<sub>IN</sub> &gt; V<sub>DD</sub></li> <li>V<sub>IN</sub> &lt; V<sub>SS</sub></li> </ul> | 0                    | -5                   | mA   |       |

| V <sub>RAM</sub>           | V <sub>DD</sub> voltage required to retain RAM                                                     | 1.2                  |                      | V    |       |

1. The device always interprets an input as a 1 when the input is greater than or equal to  $V_{IH}$  (min.) and less than or equal to  $V_{IH}$  (max.), regardless of whether input hysteresis is turned on.

2. The device always interprets an input as a 0 when the input is less than or equal to  $V_{IL}$  (max.) and greater than or equal to  $V_{IL}$  (min.), regardless of whether input hysteresis is turned on.

3. All functional non-supply pins are internally clamped to VSS and VDD. Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values. Power supply must maintain regulation within operating VDD range during instantaneous and operating maximum current conditions. If positive injection current (VIn > VDD) is greater than IDD, the injection current may flow out of VDD and could result in external power supply going out of regulation. Ensure external VDD load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low (which would reduce overall power consumption).

| Symbol           | Description                                                                                                                                                       | Min. | Max. | Unit | Notes |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|------|-------|

| t <sub>POR</sub> | After a POR event, amount of time from the point $V_{DD}$ reaches 1.8 V to execution of the first instruction across the operating temperature range of the chip. |      | 300  | μs   | 1     |

|                  | • VLLS1 → RUN                                                                                                                                                     | _    | 150  | μs   | 1, 2  |

|                  | • VLLS2 $\rightarrow$ RUN                                                                                                                                         |      |      |      | 1, 2  |

|                  |                                                                                                                                                                   | _    | 75   | μs   |       |

|                  | • VLLS3 → RUN                                                                                                                                                     |      |      |      | 1, 2  |

|                  |                                                                                                                                                                   | —    | 75   | μs   |       |

|                  | • LLS $\rightarrow$ RUN                                                                                                                                           |      |      |      | 2     |

|                  |                                                                                                                                                                   | —    | 6.5  | μs   |       |

|                  | VLPS → RUN                                                                                                                                                        |      |      |      | 2     |

|                  |                                                                                                                                                                   | —    | 4.6  | μs   |       |

|                  | • STOP $\rightarrow$ RUN                                                                                                                                          |      |      |      | 2     |

|                  |                                                                                                                                                                   | —    | 4.6  | μs   |       |

Table 4. Power mode transition operating behaviors

1. Normal boot (FTFL\_FOPT[LPBOOT] is 1)

2. The wakeup time includes the execution time for a small amount of firmware used to produce a GPIO clear event. Wakeup time is measured from the falling edge of the external wakeup event to the falling edge of a GPIO clear performed by software.

# 5.2.5 Power consumption operating behaviors

## Table 5. Power consumption operating behaviors

| Symbol              | Description                                                                                                      | Min. | Тур. | Max.     | Unit | Notes |

|---------------------|------------------------------------------------------------------------------------------------------------------|------|------|----------|------|-------|

| I <sub>DDA</sub>    | Analog supply current                                                                                            | _    | —    | See note | mA   | 1     |

| I <sub>DD_RUN</sub> | Run mode current — all peripheral clocks disabled, code executing from RAM                                       |      |      |          |      | 2     |

|                     | • @ 1.8 V                                                                                                        | _    | 13   | _        | mA   |       |

|                     | • @ 3.0 V                                                                                                        | _    | 13   | 16       | mA   |       |

| I <sub>DD_RUN</sub> | Run mode current — all peripheral clocks disabled, code executing from flash memory with page buffering disabled |      |      |          |      | 2     |

|                     | • @ 1.8 V                                                                                                        | —    | 14.3 | -        | mA   |       |

|                     | • @ 3.0 V                                                                                                        | —    | 14.5 | 17.9     | mA   |       |

Table continues on the next page...

| Symbol                | Description                                                                                              | Min. | Тур. | Max. | Unit | Notes  |

|-----------------------|----------------------------------------------------------------------------------------------------------|------|------|------|------|--------|

| I <sub>DD_RUN</sub>   | Run mode current — all peripheral clocks<br>enabled, code executing from RAM, exercising<br>flash memory |      |      |      |      | 3      |

|                       | • @ 1.8 V                                                                                                | —    | 20   | 23.5 | mA   |        |

|                       | • @ 3.0 V                                                                                                | —    | 20   | 25   | mA   |        |

| I <sub>DD_WAIT</sub>  | Wait mode current at 3.0 V — all peripheral clocks disabled                                              | _    | 5.8  | 6.8  | mA   | 4      |

| I <sub>DD_STOP</sub>  | Stop mode current at 3.0 V<br>• @ -40 to 25 °C                                                           | _    | 0.34 | 0.41 | mA   |        |

|                       | • @ 105 °C                                                                                               | _    | 0.90 | 1.8  | mA   |        |

| I <sub>DD_VLPR</sub>  | Very low-power run mode current at 3.0 V — all peripheral clocks disabled                                | _    | 0.63 | 1.32 | mA   | 5      |

| I <sub>DD_VLPR</sub>  | Very low-power run mode current at 3.0 V — all peripheral clocks enabled                                 | _    | 0.78 | 1.46 | mA   | 6      |

| I <sub>DD_VLPW</sub>  | Very low-power wait mode current at 3.0 V                                                                |      | 0.15 | 0.62 | mA   | 7      |

| I <sub>DD_VLPS</sub>  | Very low-power stop mode current at 3.0 V<br>• @ -40 to 25 °C                                            |      | 19   | 45   | μΑ   | 8      |

|                       | • @ 105 °C                                                                                               | _    | 145  | 312  |      |        |

| I <sub>DD_LLS</sub>   | Low leakage stop mode current at 3.0 V                                                                   |      |      |      |      | 8,9,10 |

|                       | • @ -40 to 25 °C                                                                                         | _    | 3.0  | 4.8  | μΑ   |        |

|                       | • @ 105 °C                                                                                               | —    | 53.3 | 157  | μA   |        |

| I <sub>DD_VLLS3</sub> | Very low-leakage stop mode 3 current at 3.0 V                                                            |      |      |      |      | 8,9,10 |

|                       | • @ -40 to 25 °C                                                                                         | —    | 1.8  | 3.3  | μA   |        |

|                       | • @ 105 °C                                                                                               | —    | 39.2 | 115  | μA   |        |

| I <sub>DD_VLLS2</sub> | Very low-leakage stop mode 2 current at 3.0 V                                                            |      |      |      |      | 8,9    |

|                       | • @ -40 to 25 °C                                                                                         | _    | 1.6  | 2.8  | μΑ   |        |

|                       | • @ 105 °C                                                                                               | —    | 22.2 | 65   | μA   |        |

| I <sub>DD_VLLS1</sub> | Very low-leakage stop mode 1 current at 3.0 V                                                            |      |      |      |      | 8,9    |

|                       | • @ -40 to 25 °C                                                                                         | —    | 1.4  | 2.6  | μA   |        |

|                       | • @ 105 °C                                                                                               | —    | 17.6 | 50   | μA   |        |

| I <sub>DD_RTC</sub>   | Average current adder for real-time clock                                                                |      |      |      |      | 11     |

## Table 5. Power consumption operating behaviors (continued)

1. The analog supply current is the sum of the active current for each of the analog modules on the device. See each module's specification for its supply current.

2. 50 MHz core and system clocks, and 25 MHz bus clock. MCG configured for FEI mode. All peripheral clocks disabled.

3. 50 MHz core and system clocks, and 25 MHz bus clock. MCG configured for FEI mode. All peripheral clocks enabled, but peripherals are not in active operation.

4. 50 MHz core and system clocks, and 25 MHz bus clock. MCG configured for FEI mode.

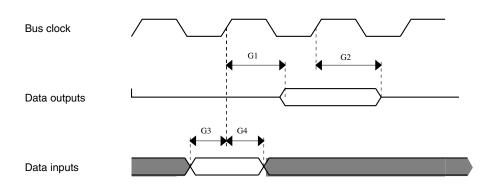

## 5.3.1 General Switching Specifications

These general purpose specifications apply to all signals configured for EGPIO, MTIM, CMT, PDB, IRQ, and I<sup>2</sup>C signals. The conditions are 50 pf load,  $V_{DD} = 1.71$  V to 3.6 V, and full temperature range. The GPIO are set for high drive, no slew rate control, and no input filter, digital or analog, unless otherwise specified.

| Symbol | Description                                                                                                              | Min. | Max. | Unit                   |

|--------|--------------------------------------------------------------------------------------------------------------------------|------|------|------------------------|

| G1     | Bus clock from CLK_OUT pin high to GPIO output valid                                                                     | —    | 32   | ns                     |

| G2     | Bus clock from CLK_OUT pin high to GPIO output invalid (output hold)                                                     | 1    | —    | ns                     |

| G3     | GPIO input valid to bus clock high                                                                                       | 28   | —    | ns                     |

| G4     | Bus clock from CLK_OUT pin high to GPIO input invalid                                                                    | —    | 4    | ns                     |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled)<br>Synchronous path <sup>1</sup>                         | 1.5  | -    | Bus<br>clock<br>cycles |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter enabled)<br>Asynchronous path <sup>2</sup> | 100  | -    | ns                     |

|        | GPIO pin interrupt pulse width (digital glitch filter disabled, analog filter disabled)                                  | 50   | -    | ns                     |

|        | Asynchronous path <sup>2</sup>                                                                                           |      |      |                        |

|        | External reset pulse width (digital glitch filter disabled)                                                              | 100  | —    | ns                     |

|        | Mode select (MS) hold time after reset deassertion                                                                       | 2    | _    | Bus<br>clock<br>cycles |

## Table 9. EGPIO General Control Timing

1. The greater synchronous and asynchronous timing must be met.

2. This is the shortest pulse that is guaranteed to be recognized.

### Thermal specifications

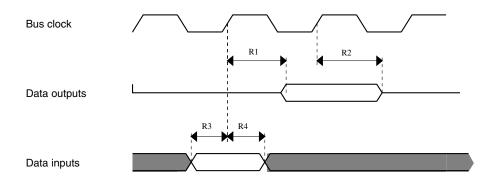

The following general purpose specifications apply to all signals configured for RGPIO, FTM, and UART. The conditions are 25 pf load,  $V_{DD} = 3.6$  V to 1.71 V, and full temperature range. The GPIO are set for high drive, no slew rate control, and no input filter, digital or analog, unless otherwise specified.

| Symbol | Description                                                       | Min. | Max. | Unit |

|--------|-------------------------------------------------------------------|------|------|------|

| R1     | CPUCLK from CLK_OUT pin high to GPIO output valid                 | —    | 16   | ns   |

| R2     | CPUCLK from CLK_OUT pin high to GPIO output invalid (output hold) | 1    | —    | ns   |

| R3     | GPIO input valid to bus clock high                                | 17   | —    | ns   |

| R4     | CPUCLK from CLK_OUT pin high to GPIO input invalid                | —    | 2    | ns   |

Table 10. RGPIO General Control Timing

# 5.4 Thermal specifications

## 5.4.1 Thermal operating requirements

Table 11. Thermal operating requirements

| Symbol         | Description              | Min. | Max. | Unit |

|----------------|--------------------------|------|------|------|

| TJ             | Die junction temperature | -40  | 115  | °C   |

| T <sub>A</sub> | Ambient temperature      | -40  | 105  | °C   |

System modules

To enter BDM mode following a POR, BKGD/MS should be held low during the power-up and for a hold time of t<sub>MSH</sub> after V<sub>DD</sub> rises above V<sub>LVD</sub>.

## 6.2 System modules

## 6.2.1 VREG electrical specifications

| Table 13. | VREG electrical specifications |

|-----------|--------------------------------|

|-----------|--------------------------------|

| Symbol                | Description                                                                                                                                         | Min. | Typ. <sup>1</sup> | Max. | Unit     | Notes |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------|------|----------|-------|

| VREGIN                | Input supply voltage                                                                                                                                | 2.7  | —                 | 5.5  | V        |       |

| I <sub>DDon</sub>     | Quiescent current — Run mode, load current<br>equal zero, input supply (VREGIN) > 3.6 V                                                             | _    | 120               | 186  | μΑ       |       |

| I <sub>DDstby</sub>   | Quiescent current — Standby mode, load current equal zero                                                                                           | _    | 1.1               | 1.54 | μΑ       |       |

| I <sub>DDoff</sub>    | <ul> <li>Quiescent current — Shutdown mode</li> <li>VREGIN = 5.0 V and temperature=25C</li> <li>Across operating voltage and temperature</li> </ul> | _    | 650<br>—          | 4    | nA<br>μA |       |

| I <sub>LOADrun</sub>  | Maximum load current — Run mode                                                                                                                     | _    | —                 | 120  | mA       |       |

| I <sub>LOADstby</sub> | Maximum load current — Standby mode                                                                                                                 | —    | —                 | 1    | mA       |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply<br>(VREGIN) > 3.6 V                                                                                         |      |                   |      |          |       |

|                       | Run mode                                                                                                                                            | 3    | 3.3               | 3.6  | v        |       |

|                       | Standby mode                                                                                                                                        | 2.1  | 2.8               | 3.6  | v        |       |

| V <sub>Reg33out</sub> | Regulator output voltage — Input supply<br>(VREGIN) < 3.6 V, pass-through mode                                                                      | 2.1  | -                 | 3.6  | V        | 2     |

| C <sub>OUT</sub>      | External output capacitor                                                                                                                           | 1.76 | 2.2               | 8.16 | μF       |       |

| ESR                   | External output capacitor equivalent series resistance                                                                                              | 1    | -                 | 100  | mΩ       |       |

| I <sub>LIM</sub>      | Short circuit current                                                                                                                               | _    | 290               | —    | mA       |       |

1. Typical values assume VREGIN = 5.0 V, Temp = 25  $^{\circ}$ C unless otherwise stated.

2. Operating in pass-through mode: regulator output voltage equal to the input voltage minus a drop proportional to I<sub>Load</sub>.

# 6.3 Clock modules

## 6.3.1 MCG specifications

## Table 14. MCG specifications

| Symbol                   | Description                                                                         |                                                                  | Min.                            | Тур.   | Max.              | Unit              | Notes |

|--------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------------------------|--------|-------------------|-------------------|-------|

| f <sub>ints_ft</sub>     |                                                                                     | frequency (slow clock) —<br>nominal VDD and 25 °C                | _                               | 32.768 | —                 | kHz               |       |

| f <sub>ints_t</sub>      | Internal reference frequency (slow clock) — user trimmed                            |                                                                  | 31.25                           | _      | 39.0625           | kHz               |       |

| $\Delta_{fdco\_res\_t}$  |                                                                                     | ned average DCO output<br>voltage and temperature —<br>d SCFTRIM | _                               | ± 0.3  | ± 0.6             | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco\_res\_t}$ |                                                                                     | ned average DCO output<br>voltage and temperature —<br>y         | _                               | ± 0.2  | ± 0.5             | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$       |                                                                                     | trimmed average DCO output<br>Itage and temperature              | _                               | ± 10   | —                 | %f <sub>dco</sub> | 1     |

| $\Delta f_{dco_t}$       | Total deviation of f<br>frequency over fixe<br>range of 0–70°C                      | —                                                                | ± 1.0                           | ± 4.5  | %f <sub>dco</sub> | 1                 |       |

| f <sub>intf_ft</sub>     | Internal reference frequency (fast clock) — factory trimmed at nominal VDD and 25°C |                                                                  | _                               | 3.3    | 4                 | MHz               |       |

| f <sub>intf_t</sub>      | Internal reference frequency (fast clock) — user trimmed at nominal VDD and 25 °C   |                                                                  | 3                               | —      | 5                 | MHz               |       |

| f <sub>loc_low</sub>     | Loss of external clock minimum frequency —<br>RANGE = 00                            |                                                                  | (3/5) x<br>f <sub>ints_t</sub>  | _      | _                 | kHz               |       |

| f <sub>loc_high</sub>    | Loss of external cl<br>RANGE = 01, 10,                                              | ock minimum frequency —<br>or 11                                 | (16/5) x<br>f <sub>ints_t</sub> | _      | —                 | kHz               |       |

|                          |                                                                                     | FL                                                               | L                               |        |                   |                   | •     |

| f <sub>fll_ref</sub>     | FLL reference free                                                                  | luency range                                                     | 31.25                           | —      | 39.0625           | kHz               |       |

| f <sub>dco</sub>         | DCO output<br>frequency range                                                       | Low range (DRS=00)<br>640 × f <sub>fl_ref</sub>                  | 20                              | 20.97  | 25                | MHz               | 2, 3  |

|                          |                                                                                     | Mid range (DRS=01)<br>1280 × f <sub>fll_ref</sub>                | 40                              | 41.94  | 50                | MHz               | 1     |

|                          |                                                                                     | Mid-high range (DRS=10)<br>1920 × f <sub>fll_ref</sub>           | 60                              | 62.91  | 75                | MHz               |       |

|                          |                                                                                     | High range (DRS=11)<br>2560 × f <sub>fll_ref</sub>               | 80                              | 83.89  | 100               | MHz               | -     |

Table continues on the next page...

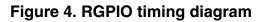

The bytes not assigned to data flash via the FlexNVM partition code are used by the FTFL to obtain an effective endurance increase for the EEPROM data. The built-in EEPROM record management system raises the number of program/erase cycles that can be attained prior to device wear-out by cycling the EEPROM data through a larger EEPROM NVM storage space.

While different partitions of the FlexNVM are available, the intention is that a single choice for the FlexNVM partition code and EEPROM data set size is used throughout the entire lifetime of a given application. The EEPROM endurance equation and graph shown below assume that only one configuration is ever used.

Writes\_FlexRAM =  $\frac{\text{EEPROM} - 2 \times \text{EEESIZE}}{\text{EEESIZE}} \times \text{Write_efficiency} \times n_{\text{nvmcycd}}$

where

- Writes\_FlexRAM minimum number of writes to each FlexRAM location

- EEPROM allocated FlexNVM based on DEPART; entered with Program Partition command

- EEESIZE allocated FlexRAM based on DEPART; entered with Program Partition command

- Write\_efficiency

- 0.25 for 8-bit writes to FlexRAM

- 0.50 for 16-bit or 32-bit writes to FlexRAM

- n<sub>nvmcycd</sub> data flash cycling endurance

Figure 5. EEPROM backup writes to FlexRAM

# 6.4.2 EzPort Switching Specifications

All timing is shown with respect to a maximum pin load of 50 pF and input signal transitions of 3 ns.

| Num  | Description                                              | Min.                    | Max.                | Unit |

|------|----------------------------------------------------------|-------------------------|---------------------|------|

|      | Operating voltage                                        | 2.7                     | 3.6                 | V    |

| EP1  | EZP_CK frequency of operation (all commands except READ) | _                       | f <sub>SYS</sub> /2 | MHz  |

| EP1a | EZP_CK frequency of operation (READ command)             | -                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion                 | 2 x t <sub>EZP_CK</sub> | —                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)                | 15                      | _                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)               | 0.0                     | —                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)                 | 15                      | _                   | ns   |

Table 21. EzPort switching specifications

Table continues on the next page...

### Analog

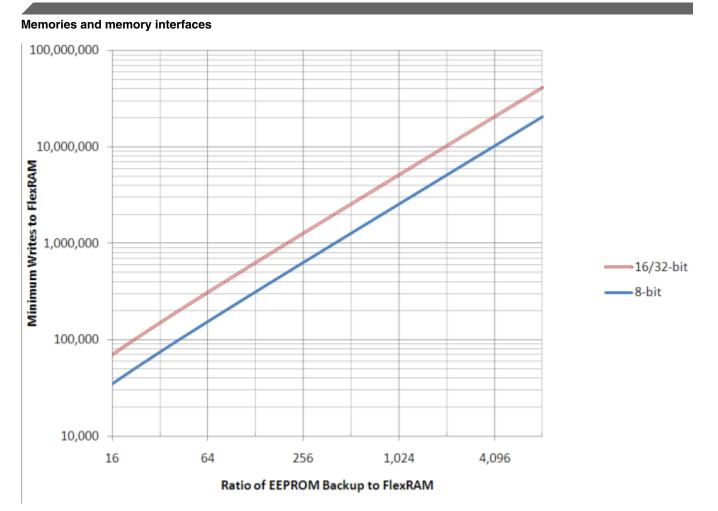

5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool: http://cache.freescale.com/ files/soft\_dev\_tools/software/app\_software/converters/ADC\_CALCULATOR\_CNV.zip?fpsp=1

Figure 9. ADC input impedance equivalency diagram

## 6.6.1.2 12-bit ADC electrical characteristics Table 24. 12-bit ADC characteristics (V<sub>REFH</sub> = V<sub>DDA</sub>, V<sub>REFL</sub> = V<sub>SSA</sub>)

| Symbol               | Description                                   | Conditions <sup>1</sup>              | Min.           | Typ. <sup>2</sup> | Max.            | Unit             | Notes                   |

|----------------------|-----------------------------------------------|--------------------------------------|----------------|-------------------|-----------------|------------------|-------------------------|

| I <sub>DDA_ADC</sub> | Supply current                                |                                      | 0.215          | —                 | 1.7             | mA               | 3                       |

|                      | ADC                                           | ADLPC=1, ADHSC=0                     | 1.2            | 2.4               | 3.9             | MHz              | t <sub>ADACK</sub> = 1/ |

| 4                    | asynchronous<br>clock source                  | ADLPC=1, ADHSC=1                     | 3.0            | 4.0               | 7.3             | MHz              | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub>   |                                               | ADLPC=0, ADHSC=0                     | 2.4            | 5.2               | 6.1             | MHz              |                         |

|                      |                                               | ADLPC=0, ADHSC=1                     | 4.4            | 6.2               | 9.5             | MHz              |                         |

|                      | Sample Time                                   | See Reference Manual chapte          | r for sample t | times             |                 |                  |                         |

| TUE                  | Total unadjusted                              | 12 bit modes                         | —              | ±4                | ±6.8            | LSB <sup>4</sup> | 5                       |

|                      | error                                         | 12 bit modes                         | —              | ±1.4              | ±2.1            |                  |                         |

| DNL                  | Differential non-<br>linearity                | 12 bit modes                         | _              | ±0.7              | -1.1 to<br>+1.9 | LSB <sup>4</sup> | 5                       |

|                      |                                               | • <12 bit modes                      | _              | ±0.2              | -0.3 to 0.5     |                  |                         |

| INL                  | INL Integral non-<br>linearity • 12 bit modes |                                      | —              | ±1.0              | -2.7 to<br>+1.9 | LSB <sup>4</sup> | 5                       |

|                      |                                               | <ul> <li>&lt;12 bit modes</li> </ul> | _              | ±0.5              | -0.7 to<br>+0.5 |                  |                         |

Table continues on the next page...

### 12-bit DAC electrical characteristics

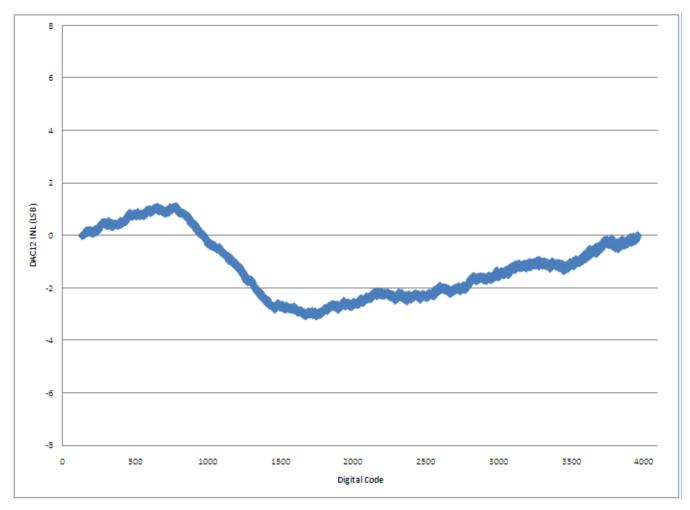

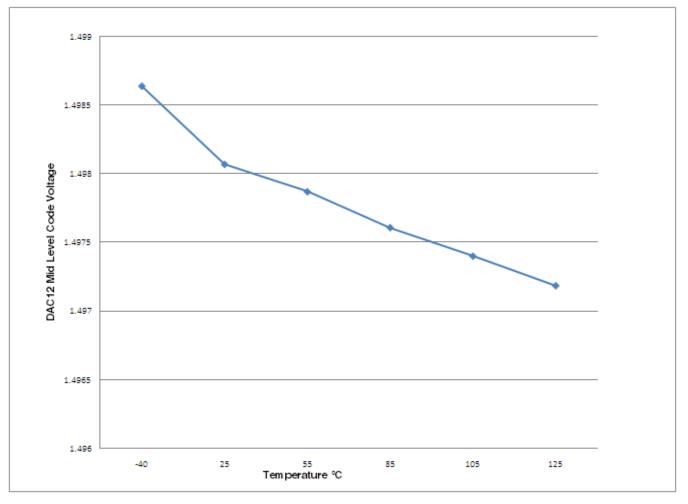

- 5. Calculated by a best fit curve from  $V_{SS}\text{+}100\ \text{mV}$  to  $V_{DACR}\text{-}100\ \text{mV}$

- VDDA = 3.0V, reference select set for VDDA (DACx\_CO:DACRFS = 1), high power mode(DACx\_CO:LPEN = 0), DAC set to 0x800, Temp range from -40C to 105C

Figure 12. Typical INL error vs. digital code

Figure 13. Offset at half scale vs. temperature

## 6.6.4 Voltage reference electrical specifications

| Table 28. | VREF full-range | operating | requirements |

|-----------|-----------------|-----------|--------------|

|           |                 |           |              |

| Symbol           | Description             | Min. | Max.    | Unit | Notes |

|------------------|-------------------------|------|---------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71 | 3.6     | V    |       |

| T <sub>A</sub>   | Temperature             | -40  | -40 105 |      |       |

| CL               | Output load capacitance | 100  |         | nF   | 1     |

1. C<sub>L</sub> must be connected to VREF\_OUT if the VREF\_OUT functionality is being used for either an internal or external reference.

| Symbol              | Description                                                                                            | Min.   | Тур. | Max.   | Unit | Notes |

|---------------------|--------------------------------------------------------------------------------------------------------|--------|------|--------|------|-------|

| V <sub>out</sub>    | Voltage reference output with factory trim at nominal $V_{\text{DDA}}$ and temperature=25C             | 1.1965 | 1.2  | 1.2027 | V    |       |

| V <sub>out</sub>    | Voltage reference output with— factory trim                                                            | 1.1584 |      | 1.2376 | V    |       |

| V <sub>out</sub>    | Voltage reference output — user trim                                                                   | 1.198  | _    | 1.202  | V    |       |

| V <sub>step</sub>   | Voltage reference trim step                                                                            | _      | 0.5  | —      | mV   |       |

| V <sub>tdrift</sub> | V <sub>tdrift</sub> Temperature drift (Vmax -Vmin across the full temperature range)                   |        | —    | 80     | mV   |       |

| I <sub>bg</sub>     | Bandgap only (MODE_LV = 00) current                                                                    | _      |      | 80     | μA   |       |

| l <sub>tr</sub>     | Tight-regulation buffer (MODE_LV =10) current                                                          | _      | _    | 1.1    | mA   |       |

| $\Delta V_{LOAD}$   | Load regulation (MODE_LV = 10)                                                                         |        |      |        | mV   | 1     |

|                     | • current = + 1.0 mA                                                                                   | _      | 2    | _      |      |       |

|                     | • current = - 1.0 mA                                                                                   | _      | 5    | _      |      |       |

| T <sub>stup</sub>   | Buffer startup time                                                                                    |        |      | 100    | μs   |       |

| V <sub>vdrift</sub> | V <sub>vdrift</sub> Voltage drift (Vmax -Vmin across the full voltage range) (MODE_LV = 10, REGEN = 1) |        | 2    | _      | mV   |       |

Table 29. VREF full-range operating behaviors

1. Load regulation voltage is the difference between the VREF\_OUT voltage with no load vs. voltage with defined load

## Table 30. VREF limited-range operating requirements

| Symbol         | Description | Min. | Max. | Unit | Notes |

|----------------|-------------|------|------|------|-------|

| T <sub>A</sub> | Temperature | 0    | 50   | °C   |       |

## Table 31. VREF limited-range operating behaviors

| Symbol           | Description                                | Min.  | Max.  | Unit | Notes |

|------------------|--------------------------------------------|-------|-------|------|-------|

| V <sub>out</sub> | Voltage reference output with factory trim | 1.173 | 1.225 | V    |       |

## 6.7 Timers

See General Switching Specifications.

| Symbol               | Description                  | Min. | Тур. | Max. | Unit | Notes |

|----------------------|------------------------------|------|------|------|------|-------|

| Res                  | Resolution                   | —    | —    | 16   | bits |       |

| T <sub>Con20</sub>   | Response time @ 20 pF        | 8    | 15   | 25   | μs   | 11    |

| I <sub>TSI_RUN</sub> | Current added in run mode    | _    | 55   | _    | μA   |       |

| I <sub>TSI_LP</sub>  | Low power mode current adder |      | 1.3  | 2.5  | μA   | 12    |

Table 34. TSI electrical specifications (continued)

1. The TSI module is functional with capacitance values outside this range. However, optimal performance is not guaranteed.

- 2. CAPTRM=7, DELVOL=7, and fixed external capacitance of 20 pF.

- 3. CAPTRM=0, DELVOL=2, and fixed external capacitance of 20 pF.

- 4. CAPTRM=0, EXTCHRG=9, and fixed external capacitance of 20 pF.

- 5. The programmable current source value is generated by multiplying the SCANC[REFCHRG] value and the base current.

- 6. The programmable current source value is generated by multiplying the SCANC[EXTCHRG] value and the base current.

- 7. Measured with a 5 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 8; lext = 16.

- 8. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 128, NSCN = 2; lext = 16.

- 9. Measured with a 20 pF electrode, reference oscillator frequency of 10 MHz, PS = 16, NSCN = 3; lext = 16.

- 10. Sensitivity defines the minimum capacitance change when a single count from the TSI module changes, it is equal to (C<sub>ref</sub> \* I<sub>ext</sub>)/(I<sub>ref</sub> \* PS \* NSCN). Sensitivity depends on the configuration used. The typical value listed is based on the following configuration: lext = 5 μA, EXTCHRG = 4, PS = 128, NSCN = 2, I<sub>ref</sub> = 16 μA, REFCHRG = 15, C<sub>ref</sub> = 1.0 pF. The minimum sensitivity describes the smallest possible capacitance that can be measured by a single count (this is the best sensitivity but is described as a minimum because it's the smallest number). The minimum sensitivity parameter is based on the following configuration: I<sub>ext</sub> = 1 μA, EXTCHRG = 0, PS = 128, NSCN = 32, I<sub>ref</sub> = 32 μA, REFCHRG = 31, C<sub>ref</sub> = 0.5 pF

- 11. Time to do one complete measurement of the electrode. Sensitivity resolution of 0.0133 pF, PS = 0, NSCN = 0, 1 electrode, DELVOL = 2, EXTCHRG = 15.

- 12. CAPTRM=7, DELVOL=2, REFCHRG=0, EXTCHRG=4, PS=7, NSCN=0F, LPSCNITV=F, LPO is selected (1 kHz), and fixed external capacitance of 20 pF. Data is captured with an average of 7 periods window.

# 7 Dimensions

## 7.1 Obtaining package dimensions

Package dimensions are provided in package drawings.

To find a package drawing, go to http://www.freescale.com and perform a keyword search for the drawing's document number:

| If you want the drawing for this package | Then use this document number |

|------------------------------------------|-------------------------------|

| 32-pin QFN                               | 98ARE10566D                   |

| 44-pin Laminate QFN                      | 98ASA00239D                   |

| 48-pin LQFP                              | 98ASH00962A                   |

| 64-pin LQFP                              | 98ASS23234W                   |

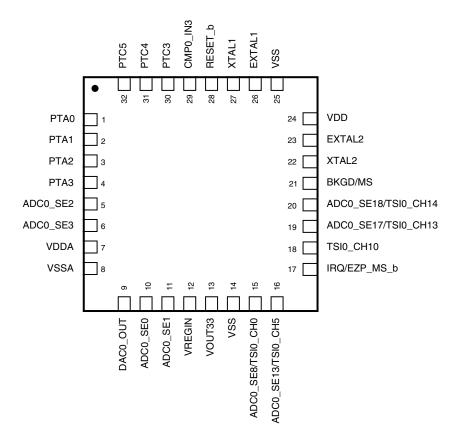

# 8 Pinout

# 8.1 Signal Multiplexing and Pin Assignments

The following table shows the signals available on each pin and the locations of these pins on the devices supported by this document. The Port Mux Control module is responsible for selecting which ALT functionality is available on each pin.

## NOTE

• On PTB0, EZP\_MS\_b is active only during reset. Refer to the detailed boot description.

| 64-<br>pin | 48-<br>pin | 44-<br>pin | 32-<br>pin | Default  | ALT0     | ALT1 | ALT2            | ALT3     | ALT4     | ALT5      | ALT6     | ALT7 | EzPort  |

|------------|------------|------------|------------|----------|----------|------|-----------------|----------|----------|-----------|----------|------|---------|

| 1          | _          | _          | _          | VDD      | VDD      |      |                 |          |          |           |          |      |         |

| 2          | _          | _          | _          | VSS      | VSS      |      |                 |          |          |           |          |      |         |

| 3          | _          | _          | _          | Disabled | Disabled | PTC6 | UART0_TX        | I2C0_SCL | RGPIO6   | SPI1_MOSI | FBa_AD11 |      |         |

| 4          | _          | _          | _          | Disabled | Disabled | PTC7 | UART0_RX        | I2C0_SDA | RGPI07   | SPI1_MISO | FBa_AD12 |      |         |

| 5          | 1          | _          | _          | Disabled | Disabled | PTD0 | UART0_CT<br>S_b | I2C1_SDA | RGPIO8   | SPI1_SCLK | FBa_AD13 |      |         |

| 6          | 2          | _          | _          | Disabled | Disabled | PTD1 | UART0_RT<br>S_b | I2C1_SCL | RGPIO9   | SPI1_SS   | FBa_AD14 |      |         |

| 7          | 3          | 1          | 1          | Disabled | Disabled | PTA0 |                 | I2C2_SCL | FTM1_CH0 | SPI0_SS   | FBa_AD15 |      |         |

| 8          | 4          | 2          | 2          | Disabled | Disabled | PTA1 |                 | I2C2_SDA | FTM1_CH1 |           | FBa_AD16 |      |         |

| 9          | 5          | 3          | 3          | Disabled | Disabled | PTA2 | UART1_TX        |          | FTM1_CH2 | SPI1_SS   |          |      |         |

| 10         | 6          | 4          | 4          | Disabled | Disabled | PTA3 | UART1_RX        |          | FTM1_CH3 | SPI1_SCLK |          |      | EZP_CLK |

| 11         | 7          | 5          | 5          | ADC0_SE2 | ADC0_SE2 | PTA4 | UART1_CT<br>S_b | I2C2_SCL | FTM1_CH4 | SPI1_MISO |          |      | EZP_DI  |

| 12         | 8          | 6          | 6          | ADC0_SE3 | ADC0_SE3 | PTA5 | UART1_RT<br>S_b | I2C2_SDA | FTM1_CH5 | SPI1_MOSI | CLKOUT   |      | EZP_DO  |

| 13         | 9          | 7          | 7          | VDDA     | VDDA     |      |                 |          |          |           |          |      |         |

| 14         | 10         | 8          | _          | VREFH    | VREFH    |      |                 |          |          |           |          |      |         |

| 15         | 11         | 9          | _          | VREF_OUT | VREF_OUT |      |                 |          |          |           |          |      |         |

| 16         | 12         | 10         | -          | VREFL    | VREFL    |      |                 |          |          |           |          |      |         |

| 17         | 13         | 11         | 8          | VSSA     | VSSA     |      |                 |          |          |           |          |      |         |

| 18         | 14         | 12         | 9          | DAC0_OUT | DAC0_OUT |      |                 |          |          |           |          |      |         |

| 19         | 15         | 13         | 10         | ADC0_SE0 | ADC0_SE0 |      |                 |          |          |           |          |      |         |

| 20         | 16         | 14         | 11         | ADC0_SE1 | ADC0_SE1 |      |                 |          |          |           |          |      |         |

| 21         | 17         | 15         | 12         | VREGIN   | VREGIN   |      |                 |          |          |           |          |      |         |

| 22         | 18         | 16         | 13         | VOUT33   | VOUT33   |      |                 |          |          |           |          |      |         |

| 23         | 19         | 17         | 14         | VSS      | VSS      |      |                 |          |          |           |          |      |         |

• PTC1 is open drain.

Figure 21. 32-pin QFN

## 8.3 Module-by-module signals

## NOTE

- On PTB0, EZP\_MS\_b is active only during reset. Refer to the detailed boot description.

- PTC1 is open drain.

### Table 35. Module signals by GPIO port and pin

| 64-pin           | 48-pin | 44-pin 32-pin P |  | Port | Module signal(s) |  |  |  |  |  |  |

|------------------|--------|-----------------|--|------|------------------|--|--|--|--|--|--|

| Power and ground |        |                 |  |      |                  |  |  |  |  |  |  |

| 1                |        |                 |  |      | VDD              |  |  |  |  |  |  |

| 24               | 20     | 18              |  |      | VDD              |  |  |  |  |  |  |

Table continues on the next page ...

| 64-pin | 48-pin | 44-pin | 32-pin  | Port | Module signal(s) |

|--------|--------|--------|---------|------|------------------|

| 27     | 22     | 20     |         | PTD3 | FBa_D6           |

| 25     | 21     | 19     | 15      | PTA6 | FBa_D7           |

| 44     | 31     | 27     |         | PTE7 | FBa_RW_b         |

|        |        | I2C0 a | nd I2C1 | 1    |                  |

| 3      |        |        |         | PTC6 | I2C0_SCL         |

| 35     | 25     | 23     | 17      | PTB0 | I2C0_SCL         |

| 4      |        |        |         | PTC7 | I2C0_SDA         |

| 36     | 26     | 24     | 18      | PTB1 | I2C0_SDA         |

| 6      | 2      |        |         | PTD1 | I2C1_SCL         |

| 42     | 30     |        |         | PTE5 | I2C1_SCL         |

| 51     | 38     | 34     | 27      | PTC0 | I2C1_SCL         |

| 5      | 1      |        |         | PTD0 | I2C1_SDA         |

| 43     |        |        |         | PTE6 | I2C1_SDA         |

| 50     | 37     | 33     | 26      | PTB7 | I2C1_SDA         |

|        |        | 12C2 a | nd I2C3 | 1    |                  |

| 7      | 3      | 1      | 1       | PTA0 | I2C2_SCL         |

| 11     | 7      | 5      | 5       | PTA4 | I2C2_SCL         |

| 8      | 4      | 2      | 2       | PTA1 | I2C2_SDA         |

| 12     | 8      | 6      | 6       | PTA5 | I2C2_SDA         |

| 32     |        |        |         | PTD7 | I2C3_SCL         |

| 37     |        |        |         | PTE2 | I2C3_SCL         |

| 33     |        |        |         | PTE0 | I2C3_SDA         |

| 38     |        |        |         | PTE3 | I2C3_SDA         |

|        |        | SI     | P10     | 1    |                  |

| 39     | 27     | 25     | 19      | PTB2 | SPI0_MISO        |

| 55     |        |        |         | PTF2 | SPI0_MISO        |

| 63     | 47     | 43     | 31      | PTC4 | SPI0_MISO        |

| 38     |        |        |         | PTE3 | SPI0_MOSI        |

| 40     | 28     | 26     | 20      | РТВЗ | SPI0_MOSI        |

| 56     | 40     | 36     |         | PTF3 | SPI0_MOSI        |

| 64     | 48     | 44     | 32      | PTC5 | SPI0_MOSI        |

| 36     | 26     | 24     | 18      | PTB1 | SPI0_SCLK        |

| 54     |        |        |         | PTF1 | SPI0_SCLK        |

| 62     | 46     | 42     | 30      | PTC3 | SPI0_SCLK        |

| 7      | 3      | 1      | 1       | PTA0 | SPI0_SS          |

Table continues on the next page...

| Table 35. | Module signals b | y GPIO po | ort and pin ( | (continued) |

|-----------|------------------|-----------|---------------|-------------|

|-----------|------------------|-----------|---------------|-------------|

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s) |

|--------|--------|--------|--------|------|------------------|

| 34     |        |        |        | PTE1 | SPI0_SS          |

| 53     |        |        |        | PTF0 | SPI0_SS          |

| 61     | 45     | 41     |        | PTF7 | SPI0_SS          |

|        |        | S      | PI1    |      |                  |

| 4      |        |        |        | PTC7 | SPI1_MISO        |

| 11     | 7      | 5      | 5      | PTA4 | SPI1_MISO        |

| 43     |        |        |        | PTE6 | SPI1_MISO        |

| 59     | 43     | 39     |        | PTF5 | SPI1_MISO        |

| 3      |        |        |        | PTC6 | SPI1_MOSI        |

| 12     | 8      | 6      | 6      | PTA5 | SPI1_MOSI        |

| 44     | 31     | 27     |        | PTE7 | SPI1_MOSI        |

| 60     | 44     | 40     |        | PTF6 | SPI1_MOSI        |

| 5      | 1      |        |        | PTD0 | SPI1_SCLK        |

| 10     | 6      | 4      | 4      | PTA3 | SPI1_SCLK        |

| 42     | 30     |        |        | PTE5 | SPI1_SCLK        |

| 58     | 42     | 38     |        | PTF4 | SPI1_SCLK        |

| 6      | 2      |        |        | PTD1 | SPI1_SS          |

| 9      | 5      | 3      | 3      | PTA2 | SPI1_SS          |

| 41     | 29     |        |        | PTE4 | SPI1_SS          |

| 57     | 41     | 37     | 29     | PTC2 | SPI1_SS          |

|        |        | UA     | RT0    | -    |                  |

| 5      | 1      |        |        | PTD0 | UART0_CTS_b      |

| 32     |        |        |        | PTD7 | UART0_CTS_b      |

| 42     | 30     |        |        | PTE5 | UART0_CTS_b      |

| 62     | 46     | 42     | 30     | PTC3 | UART0_CTS_b      |

| 6      | 2      |        |        | PTD1 | UART0_RTS_b      |

| 33     |        |        |        | PTE0 | UART0_RTS_b      |

| 41     | 29     |        |        | PTE4 | UART0_RTS_b      |

| 61     | 45     | 41     |        | PTF7 | UART0_RTS_b      |

| 4      |        |        |        | PTC7 | UART0_RX         |

| 31     | 24     | 22     |        | PTD6 | UART0_RX         |

| 43     |        |        |        | PTE6 | UART0_RX         |

| 63     | 47     | 43     | 31     | PTC4 | UART0_RX         |

| 3      |        |        |        | PTC6 | UART0_TX         |

| 30     | 23     | 21     | 16     | PTA7 | UART0_TX         |

Table continues on the next page...

**Revision History**

| 64-pin | 48-pin | 44-pin | 32-pin | Port | Module signal(s) |

|--------|--------|--------|--------|------|------------------|

| 44     | 31     | 27     |        | PTE7 | UART0_TX         |

| 64     | 48     | 44     | 32     | PTC5 | UART0_TX         |

|        | •      | UAI    | RT1    |      |                  |

| 11     | 7      | 5      | 5      | PTA4 | UART1_CTS_b      |

| 58     | 42     | 38     |        | PTF4 | UART1_CTS_b      |

| 12     | 8      | 6      | 6      | PTA5 | UART1_RTS_b      |

| 57     | 41     | 37     | 29     | PTC2 | UART1_RTS_b      |

| 10     | 6      | 4      | 4      | PTA3 | UART1_RX         |

| 59     | 43     | 39     |        | PTF5 | UART1_RX         |

| 9      | 5      | 3      | 3      | PTA2 | UART1_TX         |

| 60     | 44     | 40     |        | PTF6 | UART1_TX         |

Table 35. Module signals by GPIO port and pin (continued)

# 9 Revision History

The following table summarizes content changes since the previous release of this document.

| Rev. No. | Date    | Substantial Changes                                                             |

|----------|---------|---------------------------------------------------------------------------------|

| 4        | 01/2012 | Thermal operating requirements: Changed maximum $T_J$ value from 125°C to 115°C |