#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessorSH-1Core Size32-Bit Single-CoreSpeed20MHzConnectivityEBI/EMI, SCIPeripheralsDMA, POR, PWM, WDTNumber of I/O32Program Memory Size-Program Memory TypeROMlessEEPROM Size-Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8.10bOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPrackage / Case112-OFP (20x20)Purchase URLhttps://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417034affi20v |                            |                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|----------------------------------------------------------------------------------|

| Core Size32-Bit Single-CoreSpeed20MHzConnectivityEBI/EMI, SCIPeripheralsDMA, POR, PWM, WDTNumber of I/O32Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-QFP (20x20)                                                                                                  | Product Status             | Obsolete                                                                         |

| Speed20MHzConnectivityEBI/EMI, SCIPeripheralsDMA, POR, PWM, WDTNumber of I/O32Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-QFP (20x20)                                                                                                                             | Core Processor             | SH-1                                                                             |

| ConnectivityEBI/EMI, SCIPeripheralsDMA, POR, PWM, WDTNumber of I/O32Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-QFP (20x20)                                                                                                                                       | Core Size                  | 32-Bit Single-Core                                                               |

| PeripheralsDMA, POR, PWM, WDTNumber of I/O32Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-QFP (20x20)                                                                                                                                                               | Speed                      | 20MHz                                                                            |

| Number of I/O32Program Memory Size-Program Memory TypeROMIessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                             | Connectivity               | EBI/EMI, SCI                                                                     |

| Program Memory Size-Program Memory TypeROMlessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                             | Peripherals                | DMA, POR, PWM, WDT                                                               |

| Program Memory TypeROMlessEEPROM Size-RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                | Number of I/O              | 32                                                                               |

| EEPROM Size-RAM Size4K × 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                          | Program Memory Size        | -                                                                                |

| RAM Size4K x 8Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                                      | Program Memory Type        | ROMIess                                                                          |

| Voltage - Supply (Vcc/Vdd)4.5V ~ 5.5VData ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                                                    | EEPROM Size                | -                                                                                |

| Data ConvertersA/D 8x10bOscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                                                                                         | RAM Size                   | 4K x 8                                                                           |

| Oscillator TypeInternalOperating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                                                                                                                 | Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                      |

| Operating Temperature-20°C ~ 75°C (TA)Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                                                                                                                                        | Data Converters            | A/D 8x10b                                                                        |

| Mounting TypeSurface MountPackage / Case112-BQFPSupplier Device Package112-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                              | Oscillator Type            | Internal                                                                         |

| Package / Case     112-BQFP       Supplier Device Package     112-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                                       | Operating Temperature      | -20°C ~ 75°C (TA)                                                                |

| Supplier Device Package 112-QFP (20x20)                                                                                                                                                                                                                                                                                                                                                                                                                             | Mounting Type              | Surface Mount                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Package / Case             | 112-BQFP                                                                         |

| Purchase URL https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417034afi20v                                                                                                                                                                                                                                                                                                                                                                       | Supplier Device Package    | 112-QFP (20x20)                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/hd6417034afi20v |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|      | 20.1.3  | AC Characteristics                                                                    | . 477 |

|------|---------|---------------------------------------------------------------------------------------|-------|

|      |         | (1) Clock Timing                                                                      | . 477 |

|      |         | (2) Control Signal Timing                                                             | . 479 |

|      |         | (3) Bus Timing                                                                        | . 482 |

|      |         | (4) DMAC Timing                                                                       | 512   |

|      |         | (5) 16-bit Integrated Timer Pulse Unit Timing                                         | 514   |

|      |         | (6) Programmable Timing Pattern Controller and I/O Port Timing                        | . 515 |

|      |         | (7) Watchdog Timer Timing                                                             | . 516 |

|      |         | (8) Serial Communication Interface Timing                                             | 517   |

|      |         | (9) A/D Converter Timing                                                              | 518   |

|      |         | (10) AC Characteristics Test Conditions                                               | 520   |

|      | 20.1.4  | A/D Converter Characteristics                                                         | . 521 |

| 20.2 | SH703   | 4B 3.3 V 12.5 MHz Version and 20 MHz Version* <sup>1</sup> Electrical Characteristics | . 522 |

|      | 20.2.1  | Absolute Maximum Ratings                                                              | . 522 |

|      | 20.2.2  | DC Characteristics                                                                    | . 522 |

|      | 20.2.3  | AC Characteristics                                                                    | . 526 |

|      |         | (1) Clock Timing                                                                      | 526   |

|      |         | (2) Control Signal Timing                                                             | . 528 |

|      |         | (3) Bus Timing                                                                        | . 531 |

|      |         | (4) DMAC Timing                                                                       | . 549 |

|      |         | (5) 16-bit Integrated Timer Pulse Unit Timing                                         | 551   |

|      |         | (6) Programmable Timing Pattern Controller and I/O Port Timing                        | . 552 |

|      |         | (7) Watchdog Timer Timing                                                             | . 553 |

|      |         | (8) Serial Communication Interface Timing                                             | . 554 |

|      |         | (9) A/D Converter Timing                                                              | . 555 |

|      |         | (10) AC Characteristics Test Conditions                                               | . 557 |

|      | 20.2.4  | A/D Converter Characteristics                                                         | . 558 |

|      |         |                                                                                       |       |

| App  | endix A | A On-Chip Supporting Module Registers                                                 | 559   |

| A.1  | List of | Registers                                                                             | 559   |

| A.2  | Registe | er Tables                                                                             | . 569 |

|      | A.2.1   | Serial Mode Register (SMR) SCI                                                        | 569   |

|      | A.2.2   | Bit Rate Register (BRR) SCI                                                           | . 570 |

|      | A.2.3   | Serial Control Register (SCR) SCI                                                     | . 570 |

|      | A.2.4   | Transmit Data Register (TDR) SCI                                                      | . 572 |

|      | A.2.5   | Serial Status Register (SSR) SCI                                                      | . 572 |

|      | A.2.6   | Receive Data Register (RDR) SCI                                                       |       |

|      | A.2.7   | A/D Data Register AH-DL (ADDRAH-ADDRL) A/D                                            |       |

|      | A.2.8   | A/D Control/Status Register (ADCSR) A/D.                                              |       |

|      | A.2.9   | A/D Control Register (ADCR) A/D                                                       | . 577 |

|      |         |                                                                                       |       |

Rev. 7.00 Jan 31, 2006 page xxiii of xxvi

| Instruction |           | Instruction Code | Operation                                                                   | Execution<br>Cycles | T Bit |

|-------------|-----------|------------------|-----------------------------------------------------------------------------|---------------------|-------|

| CLRT        |           | 0000000000001000 | $0 \rightarrow T$                                                           | 1                   | 0     |

| CLRMAC      | 1         | 000000000101000  | $0 \rightarrow MACH, MACL$                                                  | 1                   | _     |

| LDC         | Rm,SR     | 0100mmmm00001110 | $Rm\toSR$                                                                   | 1                   | LSB   |

| LDC         | Rm,GBR    | 0100mmmm00011110 | $Rm\toGBR$                                                                  | 1                   | _     |

| LDC         | Rm,VBR    | 0100mmmm00101110 | $Rm \rightarrow VBR$                                                        | 1                   | _     |

| LDC.L       | @Rm+,SR   | 0100mmmm00000111 | $(Rm) \to SR, \ Rm + 4 \to Rm$                                              | 3                   | LSB   |

| LDC.L       | @Rm+,GBR  | 0100mmmm00010111 | $(Rm) \to GBR, \ Rm + 4 \to Rm$                                             | 3                   | _     |

| LDC.L       | @Rm+,VBR  | 0100mmmm00100111 | $(\text{Rm}) \rightarrow \text{VBR}, \ \text{Rm} + 4 \rightarrow \text{Rm}$ | 3                   | _     |

| LDS         | Rm,MACH   | 0100mmmm00001010 | $\text{Rm} \rightarrow \text{MACH}$                                         | 1                   | _     |

| LDS         | Rm,MACL   | 0100mmmm00011010 | $\text{Rm} \rightarrow \text{MACL}$                                         | 1                   | _     |

| LDS         | Rm,PR     | 0100mmmm00101010 | $Rm \to PR$                                                                 | 1                   | _     |

| LDS.L       | @Rm+,MACH | 0100mmmm00000110 | $(Rm) \rightarrow MACH, Rm + 4 \rightarrow Rm$                              | 1                   | —     |

| LDS.L       | @Rm+,MACL | 0100mmmm00010110 | $(Rm) \rightarrow MACL, Rm + 4 \rightarrow Rm$                              | 1                   | —     |

| LDS.L       | @Rm+,PR   | 0100mmmm00100110 | $(Rm) \to PR,  Rm + 4 \to Rm$                                               | 1                   | _     |

| NOP         |           | 0000000000001001 | No operation                                                                | 1                   | _     |

| RTE         |           | 000000000101011  | Delayed branch, stack area $\rightarrow$ PC/SR                              | 4                   | —     |

| SETT        |           | 000000000011000  | $1 \rightarrow T$                                                           | 1                   | 1     |

| SLEEP       |           | 000000000011011  | Sleep                                                                       | 3*                  | _     |

| STC         | SR,Rn     | 0000nnnn00000010 | $SR \to Rn$                                                                 | 1                   | _     |

| STC         | GBR,Rn    | 0000nnnn00010010 | $GBR\toRn$                                                                  | 1                   | _     |

| STC         | VBR,Rn    | 0000nnnn00100010 | $VBR\toRn$                                                                  | 1                   | _     |

| STC.L       | SR,@-Rn   | 0100nnnn00000011 | Rn–4 $\rightarrow$ Rn, SR $\rightarrow$ (Rn)                                | 2                   | _     |

| STC.L       | GBR,@-Rn  | 0100nnnn00010011 | $Rn4 \rightarrow Rn, \ GBR \rightarrow (Rn)$                                | 2                   | _     |

| STC.L       | VBR,@-Rn  | 0100nnnn00100011 | $Rn-4 \rightarrow Rn, \ VBR \rightarrow (Rn)$                               | 2                   | _     |

| STS         | MACH,Rn   | 0000nnnn00001010 | $MACH \to Rn$                                                               | 1                   | _     |

#### Table 2.17 System Control Instructions

Note: \* The number of execution states before the chip enters the sleep state.

**Bits 9 and 8—Multiplex Shift Count 1 and 0 (MXC1 and MXC0):** Shift row addresses downward by a certain number of bits (8–10) when row and column addresses are multiplexed (MXE = 1). Regardless of the MXE bit setting, these bits also select the range of row addresses compared in burst operation.

| Bit 9:<br>MXC1 | Bit 8:<br>MXC0 | Row Addr<br>(MXE = 1) |                 | Row Address Bits (in Burst Operation |                 |

|----------------|----------------|-----------------------|-----------------|--------------------------------------|-----------------|

| 0              | 0              | 8 bits                | (Initial value) | A8–A27                               | (Initial value) |

|                | 1              | 9 bits                |                 | A9–A27                               |                 |

| 1              | 0              | 10 bits               |                 | A10–A27                              |                 |

|                | 1              | Reserved              |                 | Reserved                             |                 |

Bits 7–0—Reserved: These bits are always read as 0. The write value should always be 0.

#### 8.2.6 Refresh Control Register (RCR)

The refresh control register (RCR) is a 16-bit read/write register that controls the start of refreshing and selects the refresh mode and the number of wait states during refreshing. It is initialized to H'0000 by a power-on reset, but is not initialized by a manual reset or in standby mode.

To prevent RCR from being written incorrectly, it must be written by a different method from most other registers. A word transfer operation is used, H'5A is written in the upper byte, and the actual data is written in the lower byte. For details, see section 8.2.11, Notes on Register Access.

| Bit           | 15    | 14    | 13   | 12   | 11 | 10 | 9 | 8 |

|---------------|-------|-------|------|------|----|----|---|---|

|               | —     | _     | —    | —    |    |    |   | — |

| Initial value | 0     | 0     | 0    | 0    | 0  | 0  | 0 | 0 |

| Read/Write    | _     | _     | —    | _    | _  | _  | — | — |

| Bit           | 7     | 6     | 5    | 4    | 3  | 2  | 1 | 0 |

|               | RFSHE | RMODE | RLW1 | RLW0 | —  | —  | — | — |

| Initial value | 0     | 0     | 0    | 0    | 0  | 0  | 0 | 0 |

| Read/Write    | R/W   | R/W   | R/W  | R/W  | —  | _  | — | — |

Bit 15–8—Reserved: These bits are always read as 0.

#### 8.4.2 Wait State Control

The number of external memory space access states and the insertion of wait states can be controlled using the WCR1–WCR3 bits. The bus cycles that can be controlled are the CPU read cycle and the DMAC dual mode read cycle. The bus cycle that can be controlled using the WCR2 is the DMAC single-mode read/write cycle.

Table 8.9 shows the number of states and number of wait states in access cycles to external memory spaces.

|                                                                                                                                                                    | CPU Read Cycle, DMAC<br>DMAC Single Mod           | CPU Write Cycle and<br>DMAC Dual Mode Write                             |                                                       |  |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------|--|--|--|--|

| Area                                                                                                                                                               | Corresponding Bits in WCR1 and WCR2 = 0           | Corresponding Bits in<br>WCR1 and WCR2 = 1                              | Cycle (Cannot be<br>controlled by WCR1)* <sup>2</sup> |  |  |  |  |

| 1, 3–5, 7                                                                                                                                                          | 1 cycle fixed; WAIT signal ignored                | 2 cycles fixed + wait state from $\overline{WAIT}$ signal* <sup>3</sup> |                                                       |  |  |  |  |

| 0, 2, 6 (long<br>wait available)                                                                                                                                   | 1 cycle + long wait state,<br>WAIT signal ignored | 1 cycle + long wait state*<br>signal                                    | <sup>1</sup> + wait state from $\overline{WAIT}$      |  |  |  |  |

| <ul><li>Notes: 1. The number of long wait states is set by WCR3.</li><li>2. When DRAME = 1, short pitch/long pitch is selected with the WW1 bit in WCR1.</li></ul> |                                                   |                                                                         |                                                       |  |  |  |  |

#### Table 8.9 Number of States and Number of Wait States in Access Cycles to External Memory Spaces

3. Pin wait cannot be used for the CS7 and WAIT pins of area 3 because they are multiplexed.

For the CPU read cycle, DMAC dual mode read cycle, and DMAC single mode read/write cycle, the access cycle is completed in 1 state when the corresponding bits of WCR1 and WCR2 for areas 1, 3–5, and 7 are cleared to 0 and the  $\overline{WAIT}$  pin input signal is not sampled. When the bits are set to 1, the  $\overline{WAIT}$  signal is sampled and the number of states is 2 plus the number of wait states set by the  $\overline{WAIT}$  signal. The  $\overline{WAIT}$  signal is sampled at the rise of the system clock (CK) directly preceding the second state of the bus cycle and the wait states are inserted as long as the level is low. When a high level is detected, it shifts to the second state (final state). Figure 8.13 shows the wait state timing when accessing the external memory spaces of areas 1, 3, 4, 5, and 7.

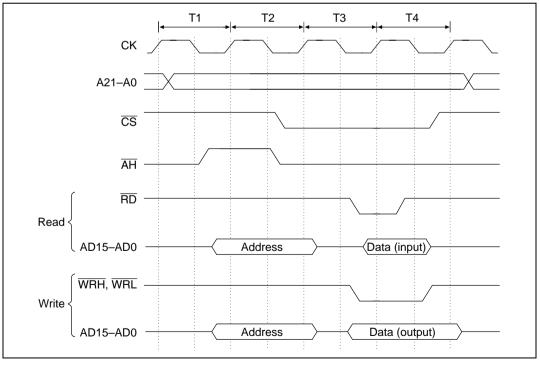

### 8.6 Address/Data Multiplexed I/O Space Access

The BSC is equipped with a function that multiplexes address and data input/output on pins AD15–AD0 in area 6. This allows the SH microprocessor to be directly connected to peripheral chips that require address/data multiplexing.

### 8.6.1 Basic Timing

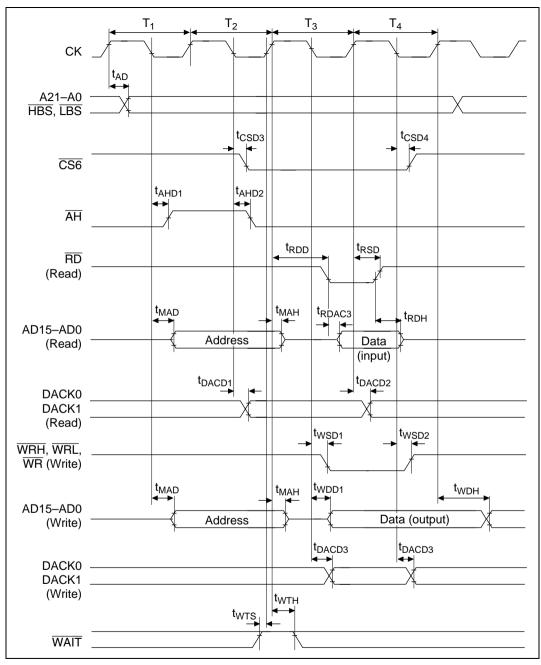

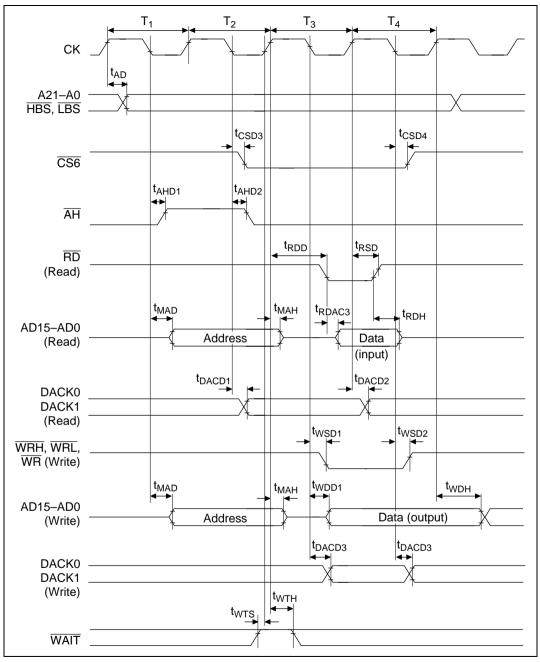

When the multiplexed I/O enable bit (IOE) in BCR is set to 1, the area 6 space with address bit A27 as 0 (H'6000000–H'6FFFFF) becomes an address/data multiplexed I/O space that, when accessed, multiplexes addresses and data. When the A14 address bit is 0, the bus width is 8 bits and address output and data input/output are performed on the AD7–AD0 pins. When the A14 address bit is 1, the bus width is 16 bits and address output and data input/output are performed on the AD15–AD0 pins. In the address/data multiplexed I/O space, access is controlled with the  $\overline{AH}$ ,  $\overline{RD}$ , and  $\overline{WR}$  signals. Accesses in the address/data multiplexed I/O space are performed in 4 states, regardless of the WCR settings. Figure 8.32 shows the timing when the address/data multiplexed I/O space is accessed.

Figure 8.32 Access Timing For Address/Data Multiplexed I/O Space

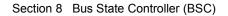

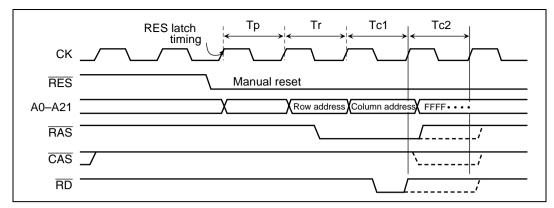

Figure 8.40 Long-Pitch Mode Read (1)

Figure 8.41 Long-Pitch Mode Read (2)

For the signal output shown by solid lines, DRAM data may not be held. Therefore, when DRAM data must be held after a reset, take one of the measures described below.

- 1. When resetting manually, use the watchdog timer (WDT) reset function.

- 2. Even if the low width of  $\overline{RAS}$  becomes as short as 1.5 tcyc as shown above, use with a frequency that satisfies the DRAM standard (t<sub>RAS</sub>).

- 3. Even if the low width of  $\overline{RAS}$  is 1.5 tcyc, use an external circuit so that a  $\overline{RAS}$  signal with a low width of 2.5 tcyc is input in the DRAM (if the low width of  $\overline{RAS}$  is higher than 2.5 tcyc, operate so that the current waveform is input in the DRAM).

These measures are not required when DRAM data is initialized or loaded again after a manual reset.

# Section 9 Direct Memory Access Controller (DMAC)

### 9.1 Overview

The SuperH microcomputer chip includes a four-channel direct memory access controller (DMAC). The DMAC can be used in place of the CPU to perform high speed transfers between external devices that have DACK (transfer request acknowledge signal), external memory, memory-mapped external devices, on-chip memory, and on-chip supporting modules (excluding the DMAC itself). Using the DMAC reduces the burden on the CPU and increases overall operating efficiency.

### 9.1.1 Features

The DMAC has the following features.

- Four channels

- Four Gbytes of address space in the architecture

- Byte or word selectable as data transfer unit

- 65536 transfers (maximum)

- Single address mode transfers (channels 0 and 1): Either the transfer source or transfer destination (peripheral device) is accessed by a DACK signal (selectable) while the other is accessed by address. One transfer unit of data is transferred in each bus cycle.

Device combinations for which transfer is possible:

- External device with DACK and memory-mapped external device (including external memories)

- External device with DACK and memory-mapped external memory

- Dual address mode transfer (channels 0–3): Both the transfer source and transfer destination are accessed by address. One transfer unit of data is transferred in 2 bus cycles.

Device combinations for which transfer is possible:

- Two external memories

- External memory and memory-mapped external device

- Two memory-mapped devices

- External memory and on-chip memory

- Memory-mapped external device and on-chip supporting module (excluding the DMAC)

- External memory and on-chip memory

- Memory-mapped external device and on-chip supporting module (excluding the DMAC)

- Two on-chip memories

### 9.1.3 Pin Configuration

Table 9.1 shows the DMAC pins.

### Table 9.1Pin Configuration

| Channel | Name                             | Symbol | I/O | Function                                                                        |

|---------|----------------------------------|--------|-----|---------------------------------------------------------------------------------|

| 0       | DMA transfer request             | DREQ0  | I   | DMA transfer request input from external device to channel 0                    |

|         | DMA transfer request acknowledge | DACK0  | 0   | DMA transfer request acknowledge<br>output from channel 0 to external<br>device |

| 1       | DMA transfer request             | DREQ1  | I   | DMA transfer request input from external device to channel 1                    |

|         | DMA transfer request acknowledge | DACK1  | 0   | DMA transfer request acknowledge<br>output from channel 1 to external<br>device |

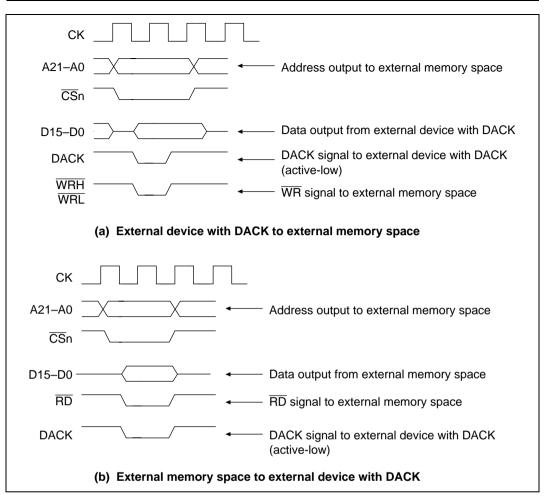

Figure 9.7 Examples of DMA Transfer Timing in Single Address Mode

• Dual Address Mode

In dual address mode, both the transfer source and destination are accessed (selectable) by an address. The source and destination can be located externally or internally. The source is accessed in the read cycle and the destination in the write cycle, so the transfer is performed in two separate bus cycles. The transfer data is temporarily stored in the DMAC. Figure 9.8 shows an example of a transfer between two external memories in which data is read from one memory in the read cycle and written to the other memory in the following write cycle.

#### Bit 3—Count Start 3 (STR3): STR3 starts and stops TCNT3.

| Bit 3: STR3 | Description       |                 |

|-------------|-------------------|-----------------|

| 0           | TCNT3 is halted   | (Initial value) |

| 1           | TCNT3 is counting |                 |

Bit 2—Count Start 2 (STR2): STR2 starts and stops TCNT2.

| Bit 2: STR2 | Description       |                 |

|-------------|-------------------|-----------------|

| 0           | TCNT2 is halted   | (Initial value) |

| 1           | TCNT2 is counting |                 |

Bit 1—Count Start 1 (STR1): STR1 starts and stops TCNT1.

| Bit 1: STR1 | Description       |                 |

|-------------|-------------------|-----------------|

| 0           | TCNT1 is halted   | (Initial value) |

| 1           | TCNT1 is counting |                 |

Bit 0—Count Start 0 (STR0): STR0 starts and stops TCNT0.

| Bit 0: STR0 | Description       |                 |

|-------------|-------------------|-----------------|

| 0           | TCNT0 is halted   | (Initial value) |

| 1           | TCNT0 is counting |                 |

#### 10.2.2 Timer Synchro Register (TSNC)

The timer synchro register (TSNC) is an eight-bit read/write register that selects timer synchronizing modes for channels 0–4. Channels for which 1 is set in the corresponding bit will be synchronized. TSNC is initialized to H'E0 or H'60 by a reset and in standby mode.

| Bit               | 7 | 6 | 5 | 4     | 3     | 2     | 1     | 0     |

|-------------------|---|---|---|-------|-------|-------|-------|-------|

|                   | _ | _ | — | SYNC4 | SYNC3 | SYNC2 | SYNC1 | SYNC0 |

| Initial value     | * | 1 | 1 | 0     | 0     | 0     | 0     | 0     |

| Read/Write        | _ | _ | _ | R/W   | R/W   | R/W   | R/W   | R/W   |

| Note: * Undefined |   |   |   |       |       |       |       |       |

| Bit               | 7 | 6    | 5    | 4    | 3 | 2    | 1    | 0    |

|-------------------|---|------|------|------|---|------|------|------|

|                   | — | IOB2 | IOB1 | IOB0 |   | IOA2 | IOA1 | IOA0 |

| Initial value     | * | 0    | 0    | 0    | 1 | 0    | 0    | 0    |

| Read/Write        | — | R/W  | R/W  | R/W  | — | R/W  | R/W  | R/W  |

| Note: * Undefined |   |      |      |      |   |      |      |      |

#### Section 10 16-Bit Integrated Timer Pulse Unit (ITU)

Bit 7—Reserved: Bit 7 is read as undefined. The write value should be 0 or 1.

Bits 6-4-I/O Control B2-B0 (IOB2-IOB0): IOB2-IOB0 selects the GRB function.

| Bit 6:<br>IOB2 | Bit 5:<br>IOB1 | Bit 4:<br>IOB0            | GRB<br>Function                          |                                                                                                |  |  |  |  |  |  |

|----------------|----------------|---------------------------|------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 0              | 0              | 0                         | GRB is an                                | Compare match with pin output disabled (Initial value)                                         |  |  |  |  |  |  |

|                |                | 1                         | output                                   | 0 output at GRB compare match*1                                                                |  |  |  |  |  |  |

|                | 1              | 0                         | <ul> <li>compare<br/>register</li> </ul> | 1 output at GRB compare match*1                                                                |  |  |  |  |  |  |

|                |                | 1                         | _                                        | Output toggles at GRB compare match (1 output for channel 2 only)* <sup>1</sup> * <sup>2</sup> |  |  |  |  |  |  |

| 1              | 0              | 0                         | GRB is an                                | GRB captures rising edge of input                                                              |  |  |  |  |  |  |

|                | 1              | input capture<br>register | GRB captures falling edge of input       |                                                                                                |  |  |  |  |  |  |

|                | 1              | 0                         |                                          | GRB captures both edges of input                                                               |  |  |  |  |  |  |

|                |                | 1                         | _                                        |                                                                                                |  |  |  |  |  |  |

Notes: 1. After reset, the value output is 0 until the first compare match occurs.

2. Channel 2 has no compare-match driven toggle output function. If it is set for toggle, 1 is automatically selected as the output.

Bit 3—Reserved: Bit 3 always is read as 1. The write value should always be 1.

**Bits 13 and 12—PB6 Mode (PB6MD1 and PB6MD0):** PB6MD1 and PB6MD0 select the function of the PB6/TP6/TOCXA4/TCLKC pin.

| Bit 13: | Bit 12: |                               |                 |

|---------|---------|-------------------------------|-----------------|

| PB6MD1  | PB6MD0  | Function                      |                 |

| 0       | 0       | Input/output (PB6)            | (Initial value) |

|         | 1       | ITU timer clock input (TCLKC) |                 |

| 1       | 0       | ITU output compare (TOCXA4)   |                 |

|         | 1       | Timing pattern output (TP6)   |                 |

**Bits 11 and 10—PB5 Mode (PB5MD1 and PB5MD0):** PB5MD1 and PB5MD0 select the function of the PB5/TP5/TIOCB4 pin.

| Bit 11:<br>PB5MD1 | Bit 10:<br>PB5MD0 | Function                                  |                 |

|-------------------|-------------------|-------------------------------------------|-----------------|

| 0                 | 0                 | Input/output (PB5)                        | (Initial value) |

|                   | 1                 | Reserved                                  |                 |

| 1                 | 0                 | ITU input capture/output compare (TIOCB4) |                 |

|                   | 1                 | Timing pattern output (TP5)               |                 |

**Bits 9 and 8—PB4 Mode (PB4MD1 and PB4MD0):** PB4MD1 and PB4MD0 select the function of the PB4/TP4/TIOCA4 pin.

| Bit 9:<br>PB4MD1 | Bit 8:<br>PB4MD0 | Function                                  |                 |

|------------------|------------------|-------------------------------------------|-----------------|

| 0                | 0                | Input/output (PB4)                        | (Initial value) |

|                  | 1                | Reserved                                  |                 |

| 1                | 0                | ITU input capture/output compare (TIOCA4) |                 |

|                  | 1                | Timing pattern output (TP4)               |                 |

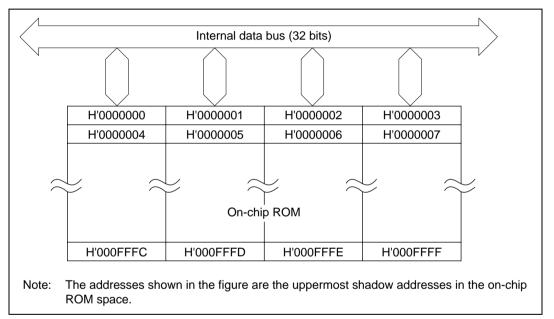

# Section 17 ROM

### 17.1 Overview

The SH7034 microcomputer has 64 kbytes of on-chip ROM (mask ROM or PROM). The on-chip ROM is connected to the CPU and the direct memory access controller (DMAC) through a 32-bit data bus (figure 17.1). The CPU can access the on-chip ROM in 8-, 16- and 32-bit widths and the DMAC can access the ROM in 8- and 16-bit widths. Data in the on-chip ROM can always be accessed in one cycle.

### Figure 17.1 Block Diagram of ROM

The operating mode determines whether the on-chip ROM is valid or not. The operating mode is selected using mode-setting pins MD0–MD2 as shown in table 17.1. When using the on-chip ROM, select mode 2; otherwise, select mode 0 or 1. The on-chip ROM is allocated to addresses H'0000000–H'000FFFF of memory area 0. Memory area 0 (H'0000000–H'0FFFFFF and H'8000000–H'8FFFFFF) is divided into 64-kbyte shadows. No matter which shadow is accessed, the on-chip ROM is accessed. See section 8, Bus State Controller (BSC), for more information on shadows.

**Bits 5–0—Reserved:** Bit 5 is a read-only bit that is always read as 0. Only write 0 in bit 5. Writing to bits 4–0 is disabled. These bits are always read as 1.

### 19.3 Sleep Mode

#### **19.3.1** Transition to Sleep Mode

Execution of the SLEEP instruction when the standby bit (SBY) in the standby control register (SBYCR) is cleared to 0 causes a transition from the program execution state to sleep mode. Although the CPU halts immediately after executing the SLEEP instruction, the contents of its internal registers remain unchanged. The on-chip supporting modules do not halt in sleep mode.

#### 19.3.2 Exiting Sleep Mode

Sleep mode is exited by an interrupt, DMA address error, power-on reset, or manual reset.

**Exit by Interrupt:** When an interrupt occurs, sleep mode is exited and interrupt exception handling is executed. Sleep mode is not exited if the interrupt cannot be accepted because its priority level is equal to or less than the mask level set in the CPU's status register (SR). Likewise, sleep mode is not exited if the interrupt is disabled by the on-chip supporting module.

**Exit by DMA Address Error:** If the DMAC operates during sleep mode and a DMA address error occurs, sleep mode is exited and DMA address error exception handling is executed.

**Exit by Power-On Reset:** If the  $\overline{\text{RES}}$  signal goes low while the NMI signal is high, sleep mode is exited and the power-on reset state is entered. If the NMI signal is brought from low to high in order to set the chip for a power-on reset, an NMI interrupt will occur whenever the rising edge of NMI is selected as the valid edge (with NMI edge select bit NMIE in the interrupt control register (ICR) of the interrupt controller). When this occurs, the NMI interrupt clears sleep mode.

**Exit by Manual Reset:** If the  $\overline{\text{RES}}$  signal goes low while the NMI signal is low, sleep mode is exited and the manual reset state is entered. If the NMI signal is brought from high to low in order to set the chip for a manual reset, sleep mode will be exited by an NMI interrupt whenever the falling edge of NMI is selected as the valid edge (with the NMIE bit).

Figure 20.19 Address/Data Multiplex I/O Bus Cycle

Figure 20.32 Address/Data Multiplex I/O Bus Cycle

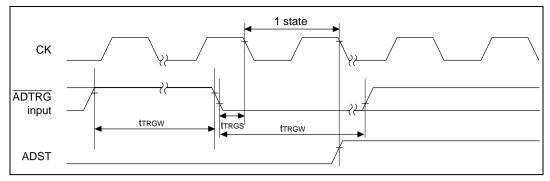

Figure 20.42 External Trigger Input Timing

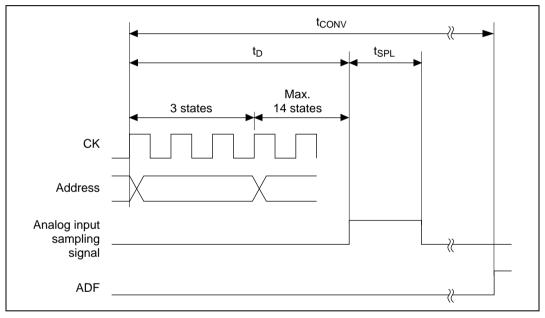

Figure 20.43 Analog Conversion Timing

#### **Table 20.16 DC Characteristics**

Conditions:  $V_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $AV_{CC} = 3.3 \text{ V} \pm 0.3 \text{ V}$ ,  $AV_{CC} = V_{CC} \pm 0.3 \text{ V}$ ,  $AV_{ref} = 3.0 \text{ V}$  to  $AV_{CC}$ ,  $V_{SS} = AV_{SS} = 0 \text{ V}$ ,  $\phi = 12.5 \text{ to } 20 \text{ MHz}^{*1}$ ,  $Ta = -20 \text{ to } +75^{\circ}\text{C}^{*2}$

#### Notes: 1. ROMless products only for 20 MHz version

2. Regular-specification products; for wide-temperature-range products, Ta = -40 to  $+85^{\circ}C$

| ltem                                      |                                                   | Symbol                            | Min                   | Тур | Мах                    | Unit | Test Conditions                         |

|-------------------------------------------|---------------------------------------------------|-----------------------------------|-----------------------|-----|------------------------|------|-----------------------------------------|

| Input high-level voltage                  | EXTAL                                             | V <sub>IH</sub>                   | $V_{CC} \times 0.9$   | _   | V <sub>CC</sub> + 0.3  | V    |                                         |

|                                           | Port C                                            | _                                 | $V_{CC} \times 0.7$   | _   | AV <sub>CC</sub> + 0.3 | V    | _                                       |

|                                           | Other input pins                                  | _                                 | $V_{CC} \times 0.7$   | _   | V <sub>CC</sub> + 0.3  | V    | _                                       |

| Input low-level<br>voltage                | Other<br>Schmidt<br>trigger input<br>pins         | V <sub>IL</sub>                   | -0.3                  | _   | $V_{CC} \times 0.2$    | V    |                                         |

| Schmidt trigger                           |                                                   | V <sub>T</sub> <sup>+</sup>       | $V_{CC}\!\times\!0.9$ |     | _                      | V    |                                         |

| input voltage                             | MD2-MD0,<br>PA13-10 PA2                           | V <sub>T</sub> <sup>-</sup>       | —                     | —   | $V_{CC} 	imes 0.1$     | V    |                                         |

|                                           | MD2–MD0,<br>PA13–10, PA2,<br>PA0, PB7–PB0         | V <sub>T</sub> +–V <sub>T</sub> - | $V_{CC} \times 0.07$  | 7   | _                      | V    | _                                       |

| Input leakage<br>current                  | RES                                               | lin                               | _                     | —   | 1.0                    | μA   | Vin = 0.5 to V <sub>CC</sub> – 0.5 V    |

|                                           | NMI,<br>MD2–MD0                                   | _                                 | _                     | _   | 1.0                    | μA   | Vin = 0.5 to V <sub>CC</sub> –<br>0.5 V |

|                                           | Port C                                            | -                                 | _                     | _   | 1.0                    | μA   | Vin = 0.5 to AV <sub>CC</sub> – 0.5 V   |

| 3-state leakage<br>current<br>(off state) | Ports A and<br>B, CS3–CS0,<br>A21–A0,<br>AD15–AD0 | I <sub>TSI</sub>                  | _                     | _   | 1.0                    | μA   | Vin = 0.5 to V <sub>CC</sub> –<br>0.5 V |

| Input pull-up<br>MOS current              | PA3                                               | –lp                               | 20                    | _   | 300                    | μA   | Vin = 0V                                |

| Output high-                              | All output                                        | V <sub>OH</sub>                   | $V_{CC} - 0.7$        | _   | _                      | V    | I <sub>OH</sub> = –200 μA               |

| level voltage                             | pins                                              |                                   | V <sub>CC</sub> – 1.0 | _   | _                      | V    | I <sub>OH</sub> = -1 mA                 |

| Output low                                | All output                                        | V <sub>OL</sub>                   | _                     | _   | 0.4                    | V    | I <sub>OL</sub> = 1.6 mA                |

| level voltage                             | pins                                              |                                   | _                     | _   | 1.2                    | V    | I <sub>OL</sub> = 8 mA                  |

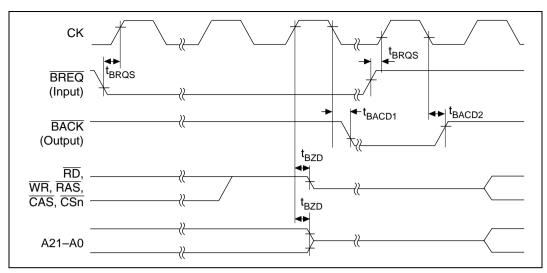

Figure 20.51 Bus Release Timing

| Item                                         |                        | Symbol             | Min                     | Max                          | Unit  | Figures                                     |

|----------------------------------------------|------------------------|--------------------|-------------------------|------------------------------|-------|---------------------------------------------|

| AH delay time 1                              | t <sub>AHD1</sub>      |                    | 20                      | ns                           | 20.63 |                                             |

| AH delay time 2                              |                        | t <sub>AHD2</sub>  | _                       | 20                           | ns    | _                                           |

| Multiplexed addres                           | s delay time           | t <sub>MAD</sub>   | _                       | 30                           | ns    | _                                           |

| Multiplexed addres                           | s hold time            | t <sub>MAH</sub>   | 0                       | —                            | ns    | _                                           |

| DACK0, DACK1 delay time 1                    |                        | t <sub>DACD1</sub> | —                       | 23                           | ns    | 20.52, 20.53, 20.55–<br>20.58, 20.63, 20.64 |

| DACK0, DACK1 de                              | elay time 2            | t <sub>DACD2</sub> | _                       | 23                           | ns    | _                                           |

| DACK0, DACK1 delay time 3*7                  |                        | t <sub>DACD3</sub> | _                       | 20                           | ns    | 20.53, 20.57, 20.58,<br>20.63               |

| DACK0, DACK1 delay time 4                    |                        | t <sub>DACD4</sub> | _                       | 20                           | ns    | 20.55, 20.56                                |

| DACK0, DACK1 delay time 5                    |                        | t <sub>DACD5</sub> | _                       | 20                           | ns    | _                                           |

| Read delay time                              | 35% duty* <sup>2</sup> | t <sub>RDD</sub>   | _                       | t <sub>cyc</sub> × 0.35 + 12 | ns    | 20.52, 20.53, 20.55–                        |

| 50% dut                                      |                        | _                  | _                       | $t_{cyc} 	imes 0.5 + 15$     | ns    | 20.59, 20.63                                |

| Data setup time for                          | CAS                    | t <sub>DS</sub>    | 0* <sup>5</sup>         | —                            | ns    | 20.55, 20.57                                |

| CAS setup time for                           | RAS                    | t <sub>CSR</sub>   | 10                      | _                            | ns    | 20.60–20.62                                 |

| Row address hold time                        |                        | t <sub>RAH</sub>   | 10                      | —                            | ns    | 20.55, 20.57                                |

| Write command hold time                      |                        | t <sub>WCH</sub>   | 15                      | —                            | ns    | _                                           |

| Write command                                | 35% duty* <sup>2</sup> | t <sub>WCS</sub>   | 0                       | —                            | ns    | 20.55                                       |

| setup time                                   | 50% duty               | t <sub>WCS</sub>   | 0                       | —                            | ns    | _                                           |

| Access time from CAS precharge* <sup>6</sup> |                        | t <sub>ACP</sub>   | t <sub>cyc</sub><br>–20 |                              | ns    | 20.56                                       |

Notes: 1. HBS and LBS signals are 25 ns.

- 2. When frequency is 10 MHz or more.

- 3. n is the number of wait cycles.

- 4. Access time from addresses A0 to A21 is tcyc-25 ns.

- 5. -5ns for parity output of DRAM long-pitch access.

- 6. It is not necessary to meet the  $t_{\text{RDS}}$  specification as long as the access time specification is met.

- In the relationship of t<sub>CASD2</sub> and t<sub>CASD3</sub> with respect to t<sub>DACD3</sub>, a Min-Max combination does not occur because of the logic structure.