# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

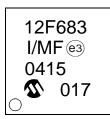

| Product Status             | Active                                                                   |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-VDFN Exposed Pad                                                       |

| Supplier Device Package    | 8-DFN-S (6x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683-e-mf |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

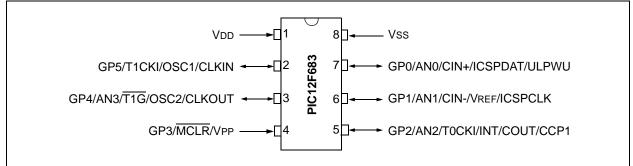

## 8-Pin Diagram (PDIP, SOIC)

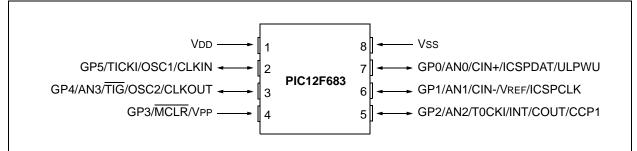

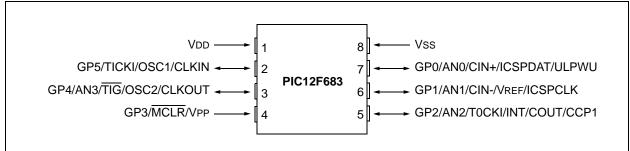

## 8-Pin Diagram (DFN)

#### 8-Pin Diagram (DFN-S)

#### TABLE 1: 8-PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР  | Interrupts | Pull-ups | Basic         |

|--------------------|-----|----------|-------------|-------|------|------------|----------|---------------|

| GP0                | 7   | AN0      | CIN+        | _     | _    | IOC        | Y        | ICSPDAT/ULPWU |

| GP1                | 6   | AN1/VREF | CIN-        | —     | —    | IOC        | Y        | ICSPCLK       |

| GP2                | 5   | AN2      | COUT        | T0CKI | CCP1 | INT/IOC    | Y        | —             |

| GP3 <sup>(1)</sup> | 4   |          | —           | _     | _    | IOC        | Y(2)     | MCLR/Vpp      |

| GP4                | 3   | AN3      | —           | T1G   | -    | IOC        | Y        | OSC2/CLKOUT   |

| GP5                | 2   | _        | —           | T1CKI |      | IOC        | Y        | OSC1/CLKIN    |

| _                  | 1   |          | —           |       | _    | —          | —        | Vdd           |

|                    | 8   | _        |             | _     | _    | _          | _        | Vss           |

Note 1: Input only.

**2:** Only when pin is configured for external  $\overline{MCLR}$ .

## 2.0 MEMORY ORGANIZATION

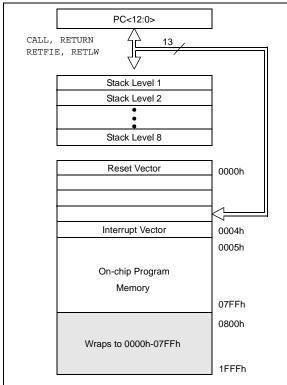

#### 2.1 Program Memory Organization

The PIC12F683 has a 13-bit program counter capable of addressing an  $8k \times 14$  program memory space. Only the first  $2k \times 14$  (0000h-07FFh) for the PIC12F683 is physically implemented. Accessing a location above these boundaries will cause a wraparound within the first  $2K \times 14$  space. The Reset vector is at 0000h and the interrupt vector is at 0004h (see Figure 2-1).

#### FIGURE 2-1: PROGRAM MEMORY MAP AND STACK FOR THE PIC12F683

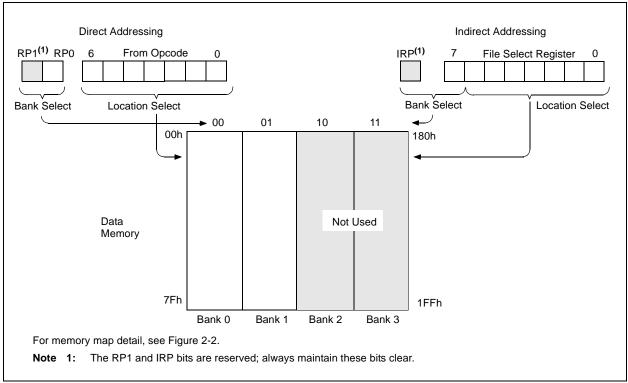

## 2.2 Data Memory Organization

The data memory (see Figure 2-2) is partitioned into two banks, which contain the General Purpose Registers (GPR) and the Special Function Registers (SFR). The Special Function Registers are located in the first 32 locations of each bank. Register locations 20h-7Fh in Bank 0 and A0h-BFh in Bank 1 are General Purpose Registers, implemented as static RAM. Register locations F0h-FFh in Bank 1 point to addresses 70h-7Fh in Bank 0. All other RAM is unimplemented and returns '0' when read. RP0 of the STATUS register is the bank select bit.

#### <u>RP0</u>

- $0 \rightarrow Bank 0 is selected$

- $1 \rightarrow Bank 1 is selected$

Note: The IRP and RP1 bits of the STATUS register are reserved and should always be maintained as '0's.

| Addr | Name               | Bit 7              | Bit 6                                         | Bit 5         | Bit 4        | Bit 3               | Bit 2          | Bit 1        | Bit 0         | Value on<br>POR, BOR | Page   |  |

|------|--------------------|--------------------|-----------------------------------------------|---------------|--------------|---------------------|----------------|--------------|---------------|----------------------|--------|--|

| Bank | Bank 1             |                    |                                               |               |              |                     |                |              |               |                      |        |  |

| 80h  | INDF               | Addressing         | this location                                 | uses conte    | nts of FSR t | o address da        | ata memory     | (not a physi | cal register) | xxxx xxxx            | 17, 90 |  |

| 81h  | OPTION_REG         | GPPU               | INTEDG                                        | TOCS          | T0SE         | PSA                 | PS2            | PS1          | PS0           | 1111 1111            | 12, 90 |  |

| 82h  | PCL                | Program C          | Program Counter's (PC) Least Significant Byte |               |              |                     |                |              |               |                      |        |  |

| 83h  | STATUS             | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                            | RP0           | TO           | PD                  | Z              | DC           | С             | 0001 1xxx            | 11, 90 |  |

| 84h  | FSR                | Indirect Da        | ta Memory                                     | Address Po    | ointer       |                     |                |              |               | xxxx xxxx            | 17, 90 |  |

| 85h  | TRISIO             | —                  | _                                             | TRISIO5       | TRISIO4      | TRISIO3             | TRISIO2        | TRISIO1      | TRISIO0       | 11 1111              | 32, 90 |  |

| 86h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    | _      |  |

| 87h  | —                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    | _      |  |

| 88h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    | _      |  |

| 89h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    | _      |  |

| 8Ah  | PCLATH             | _                  | _                                             |               | Write Buffe  | r for upper         | 5 bits of Pro  | ogram Cou    | nter          | 0 0000               | 17, 90 |  |

| 8Bh  | INTCON             | GIE                | PEIE                                          | TOIE          | INTE         | GPIE                | TOIF           | INTF         | GPIF          | 0000 0000            | 13, 90 |  |

| 8Ch  | PIE1               | EEIE               | ADIE                                          | CCP1IE        | _            | CMIE                | OSFIE          | TMR2IE       | TMR1IE        | 000- 0000            | 14, 90 |  |

| 8Dh  |                    | Unimpleme          |                                               | —             |              |                     |                |              |               |                      |        |  |

| 8Eh  | PCON               | _                  | _                                             | ULPWUE        | SBOREN       | _                   | —              | POR          | BOR           | 01qq                 | 16, 90 |  |

| 8Fh  | OSCCON             |                    | IRCF2                                         | IRCF1         | IRCF0        | OSTS <sup>(2)</sup> | HTS            | LTS          | SCS           | -110 x000            | 20, 90 |  |

| 90h  | OSCTUNE            | —                  | —                                             | _             | TUN4         | TUN3                | TUN2           | TUN1         | TUN0          | 0 0000               | 24, 90 |  |

| 91h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    | —      |  |

| 92h  | PR2                | Timer2 Mo          | dule Period                                   | Register      |              |                     |                |              |               | 1111 1111            | 49, 90 |  |

| 93h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    |        |  |

| 94h  |                    | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    |        |  |

| 95h  | WPU <sup>(3)</sup> | —                  | —                                             | WPU5          | WPU4         | _                   | WPU2           | WPU1         | WPU0          | 11 -111              | 34, 90 |  |

| 96h  | IOC                | —                  | —                                             | IOC5          | IOC4         | IOC3                | IOC2           | IOC1         | IOC0          | 00 0000              | 34, 90 |  |

| 97h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | —                    |        |  |

| 98h  | _                  | Unimpleme          | ented                                         |               |              |                     |                |              |               | _                    | —      |  |

| 99h  | VRCON              | VREN               | —                                             | VRR           | —            | VR3                 | VR2            | VR1          | VR0           | 0-0- 0000            | 58, 90 |  |

| 9Ah  | EEDAT              | EEDAT7             | EEDAT6                                        | EEDAT5        | EEDAT4       | EEDAT3              | EEDAT2         | EEDAT1       | EEDAT0        | 0000 0000            | 71, 90 |  |

| 9Bh  | EEADR              | EEADR7             | EEADR6                                        | EEADR5        | EEADR4       | EEADR3              | EEADR2         | EEADR1       | EEADR0        | 0000 0000            | 71, 90 |  |

| 9Ch  | EECON1             | —                  | _                                             | —             | —            | WRERR               | WREN           | WR           | RD            | x000                 | 72, 91 |  |

| 9Dh  | EECON2             |                    |                                               |               | a physical   |                     |                |              |               |                      | 72, 91 |  |

| 9Eh  | ADRESL             | Least Sign         |                                               | s of the left | shifted resu | lt or 8 bits o      | of the right s | shifted resu | lt            | xxxx xxxx            | 66, 91 |  |

| 9Fh  | ANSEL              | _                  | ADCS2                                         | ADCS1         | ADCS0        | ANS3                | ANS2           | ANS1         | ANS0          | -000 1111            | 33, 91 |  |

#### TABLE 2-2: PIC12F683 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Legend: -= unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** IRP and RP1 bits are reserved, always maintain these bits clear.

2: OSTS bit of the OSCCON register reset to '0' with Dual Speed Start-up and LP, HS or XT selected as the oscillator.

3: GP3 pull-up is enabled when MCLRE is '1' in the Configuration Word register.

#### 3.5.2.1 OSCTUNE Register

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0     | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-----------|-------|-------|

| —     | _   | —   | TUN4  | TUN3  | TUN3 TUN2 |       | TUN0  |

| bit 7 |     |     |       |       |           |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                        |  |  |  |  |  |  |

|---------|-------------------------------------------------------------------|--|--|--|--|--|--|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                   |  |  |  |  |  |  |

|         | 01111 = Maximum frequency                                         |  |  |  |  |  |  |

|         | 01110 =                                                           |  |  |  |  |  |  |

|         | •                                                                 |  |  |  |  |  |  |

|         | •                                                                 |  |  |  |  |  |  |

|         | •                                                                 |  |  |  |  |  |  |

|         | 00001 =                                                           |  |  |  |  |  |  |

|         | 00000 = Oscillator module is running at the calibrated frequency. |  |  |  |  |  |  |

|         | 11111 =                                                           |  |  |  |  |  |  |

|         | •                                                                 |  |  |  |  |  |  |

|         | •                                                                 |  |  |  |  |  |  |

|         | •                                                                 |  |  |  |  |  |  |

|         | 10000 = Minimum frequency                                         |  |  |  |  |  |  |

## **PIC12F683**

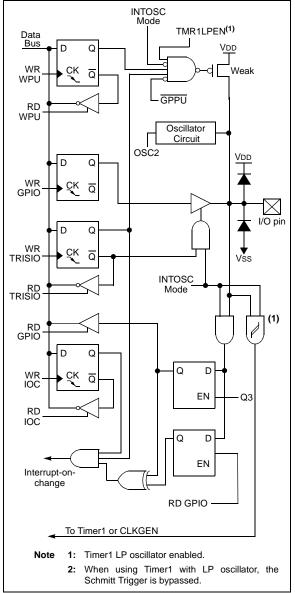

#### 4.2.5.6 GP5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

#### FIGURE 4-6:

## BLOCK DIAGRAM OF GP5

#### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH GPIO

| Name       | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|---------|---------|---------|---------|---------|---------|-------------------|---------------------------------|

| ANSEL      | _      | ADCS2  | ADCS1   | ADCS0   | ANS3    | ANS2    | ANS1    | ANS0    | -000 1111         | -000 1111                       |

| CCP1CON    | _      | _      | DC1B1   | DC1B0   | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 00 0000           | 00 0000                         |

| CMCON0     | _      | COUT   | _       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000         | -0-0 0000                       |

| PCON       | _      | _      | ULPWUE  | SBOREN  | _       | _       | POR     | BOR     | 01qq              | 0uuu                            |

| INTCON     | GIE    | PEIE   | TOIE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000         | 0000 000x                       |

| IOC        | _      | _      | IOC5    | IOC4    | IOC3    | IOC2    | IOC1    | IOC0    | 00 0000           | 00 0000                         |

| OPTION_REG | GPPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111         | 1111 1111                       |

| GPIO       | _      | _      | GP5     | GP4     | GP3     | GP2     | GP1     | GP0     | xx xxxx           | x0 x000                         |

| T1CON      | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC  | TMR1CS  | TMR10N  | 0000 0000         | 0000 0000                       |

| TRISIO     | _      | _      | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111           | 11 1111                         |

| WPU        | _      | _      | WPU5    | WPU4    | _       | WPU2    | WPU1    | WPU0    | 11 -111           | 11 -111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by GPIO.

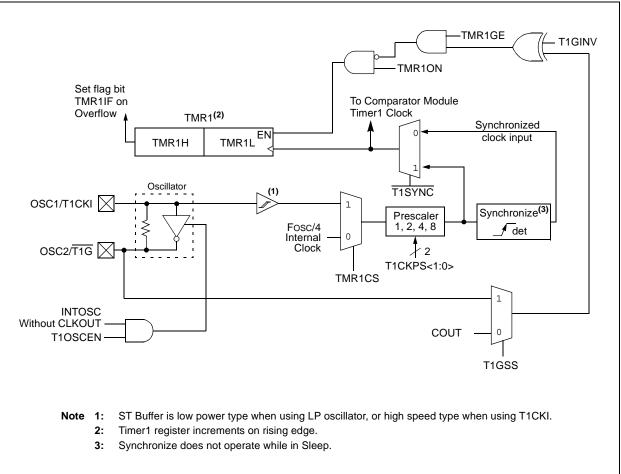

## 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- · Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or T1G pin

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Special Event Trigger (with CCP)

- Comparator output synchronization to Timer1 clock

Figure 6-1 is a block diagram of the Timer1 module.

#### FIGURE 6-1: TIMER1 BLOCK DIAGRAM

#### 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

## 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock Source | TMR1CS |

|--------------|--------|

| Fosc/4       | 0      |

| T1CKI pin    | 1      |

## 8.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. The comparators are very useful mixed signal building blocks because they provide analog functionality independent of the program execution. The analog comparator module includes the following features:

- Multiple comparator configurations

- · Comparator output is available internally/externally

- Programmable output polarity

- Interrupt-on-change

- Wake-up from Sleep

- Timer1 gate (count enable)

- Output synchronization to Timer1 clock input

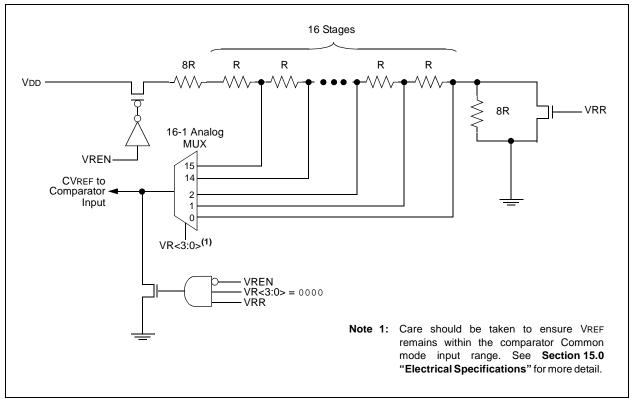

- Programmable voltage reference

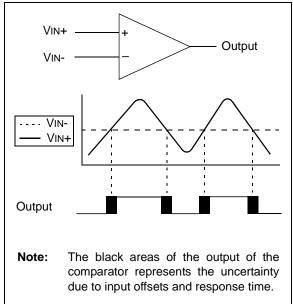

#### 8.1 Comparator Overview

The comparator is shown in Figure 8-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

#### SINGLE COMPARATOR

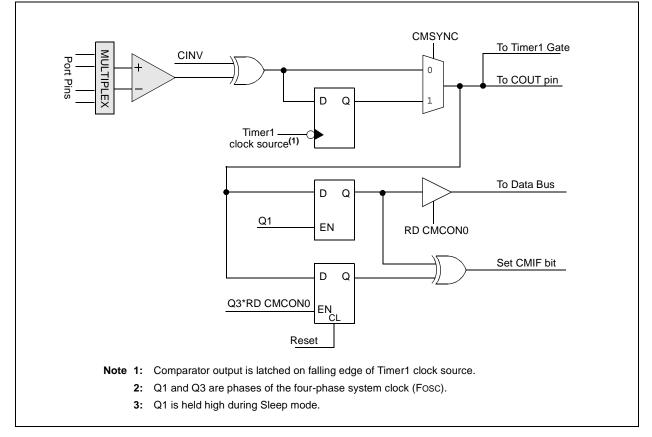

#### FIGURE 8-2: COMPARATOR OUTPUT BLOCK DIAGRAM

## 8.7 Operation During Sleep

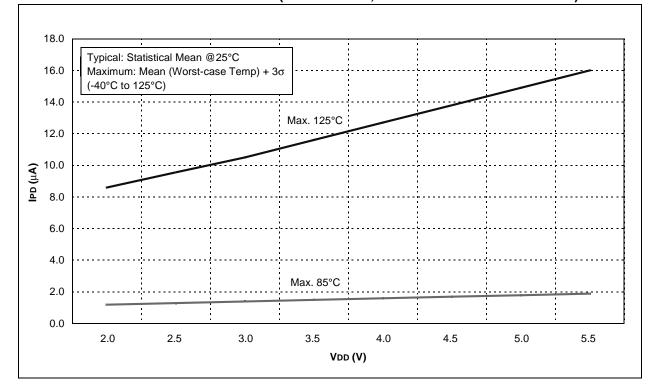

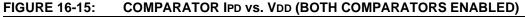

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 15.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. The comparator is turned off by selecting mode CM<2:0> = 000 or CM<2:0> = 111 of the CMCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CMIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

## 8.8 Effects of a Reset

A device Reset forces the CMCON0 and CMCON1 registers to their Reset states. This forces the Comparator module to be in the Comparator Reset mode (CM<2:0> = 000). Thus, all comparator inputs are analog inputs with the comparator disabled to consume the smallest current possible.

#### REGISTER 8-1: CMCON0: COMPARATOR CONFIGURATION REGISTER

| U-0             | R-0                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                      | R/W-0                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                              | R/W-0                                                                                                                                | R/W-0                                                                  | R/W-0            |  |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------|--|--|--|--|

| _               | COUT                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                        | CINV                                                                                                                                                                                                          | CIS                                                                                                                                                                                                                | CM2                                                                                                                                  | CM1                                                                    | CM0              |  |  |  |  |

| bit 7           |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        | bit 0            |  |  |  |  |

|                 |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| Legend:         |                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| R = Readable    |                                                                                                                                                                       | W = Writable bit                                                                                                                                                                                                                                                                                         | t                                                                                                                                                                                                             | •                                                                                                                                                                                                                  | nted bit, read as                                                                                                                    |                                                                        |                  |  |  |  |  |

| -n = Value at F | POR                                                                                                                                                                   | '1' = Bit is set                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                               | '0' = Bit is cleare                                                                                                                                                                                                | ed                                                                                                                                   | x = Bit is unknow                                                      | wn               |  |  |  |  |

| bit 7           | Unimplement                                                                                                                                                           | ed: Read as '0'                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| bit 6           | COUT: Compa           When CINV =           1 = VIN+ > VIN           0 = VIN+ < VIN                                                                                   | -<br>-<br><u>1:</u><br>-                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| bit 5           | Unimplement                                                                                                                                                           | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| bit 4           | <b>CINV:</b> Compar<br>1 = Output invo<br>0 = Output not                                                                                                              |                                                                                                                                                                                                                                                                                                          | on bit                                                                                                                                                                                                        |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| bit 3           | $\frac{\text{When CM} < 2:0}{1 = \text{CIN} + \text{conn}}$ $0 = \text{CIN} - \text{conn}$                                                                            | ects to VIN-<br>> = <u>0xx</u> or <u>100 or</u>                                                                                                                                                                                                                                                          |                                                                                                                                                                                                               |                                                                                                                                                                                                                    |                                                                                                                                      |                                                                        |                  |  |  |  |  |

| bit 2-0         | 000 = CIN pins<br>001 = CIN pins<br>010 = CIN pins<br>011 = CIN- pin<br>Compar<br>100 = CIN- pin<br>available<br>101 = CIN pins<br>Compar<br>110 = CIN pins<br>Compar | nparator Mode bits<br>s are configured as<br>s are configured as<br>n is configured as a<br>ator output, CVREF<br>n is configured as a<br>e internally, CVREF<br>s are configured as<br>rator output, CVREF<br>s are configured as<br>rator output, CVREF<br>s are configured as<br>a as a configured as | analog, COUT p<br>analog, COUT p<br>analog, COUT p<br>nalog, CIN+ pin<br>is non-inverting<br>nalog, CIN+ pin<br>is non-inverting<br>analog and mul-<br>is non-inverting<br>analog and mul-<br>analog and mul- | bin configured as I/<br>bin configured as C<br>bin configured as I/<br>is configured as I/C<br>input<br>is configured as I/C<br>input<br>tiplexed, COUT pir<br>input<br>tiplexed, COUT pir<br>REF is non-inverting | Comparator outpu<br>(O, Comparator o<br>D, COUT pin conf<br>D, COUT pin is co<br>n is configured as<br>n is configured as<br>g input | t<br>utput available inte<br>igured as<br>onfigured as I/O, Co<br>I/O, | omparator output |  |  |  |  |

## TABLE 8-2:SUMMARY OF REGISTERS ASSOCIATED WITH THE COMPARATOR AND VOLTAGE<br/>REFERENCE MODULES

| Name   | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| ANSEL  |       | ADCS2 | ADCS1   | ADCS0   | ANS3    | ANS2    | ANS1    | ANS0    | -000 1111            | -000 1111                       |

| CMCON0 | _     | COUT  | —       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000            | -0-0 0000                       |

| CMCON1 | _     | _     | —       | —       | —       | _       | T1GSS   | CMSYNC  | 10                   | 10                              |

| INTCON | GIE   | PEIE  | TOIE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000            | 0000 000x                       |

| PIE1   | EEIE  | ADIE  | CCP1IE  | —       | CMIE    | OSFIE   | TMR2IE  | TMR1IE  | 000- 0000            | 0000 0000                       |

| PIR1   | EEIF  | ADIF  | CCP1IF  | —       | CMIF    | OSFIF   | TMR2IF  | TMR1IF  | 000- 0000            | 000- 0000                       |

| GPIO   | _     | _     | GP5     | GP4     | GP3     | GP2     | GP1     | GP0     | xx xxxx              | uu uuuu                         |

| TRISIO |       |       | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

| VRCON  | VREN  |       | VRR     | _       | VR3     | VR2     | VR1     | VR0     | 0-0- 0000            | -0-0 0000                       |

Legend: x = unknown, u = unchanged, - = unimplemented, read as '0'. Shaded cells are not used for comparator.

| R/W-0                                                                                            | R/W-0                                                                                                                                                                                                                                                     | U-0              | U-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|----------------|------------------|------------------|-----------------|-------|--|--|

| ADFM                                                                                             | VCFG                                                                                                                                                                                                                                                      | _                | _              | CHS1             | CHS0             | GO/DONE         | ADON  |  |  |

| bit 7                                                                                            |                                                                                                                                                                                                                                                           |                  |                |                  |                  |                 | bit 0 |  |  |

|                                                                                                  |                                                                                                                                                                                                                                                           |                  |                |                  |                  |                 |       |  |  |

| Legend:                                                                                          |                                                                                                                                                                                                                                                           |                  |                |                  |                  |                 |       |  |  |

| R = Readable bit W = Writable bit                                                                |                                                                                                                                                                                                                                                           |                  |                | U = Unimpler     | mented bit, read | d as '0'        |       |  |  |

| -n = Value at F                                                                                  | POR                                                                                                                                                                                                                                                       | '1' = Bit is set |                | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |

| bit 7 ADFM: A/D Conversion Result Format Select bit<br>1 = Right justified<br>0 = Left justified |                                                                                                                                                                                                                                                           |                  |                |                  |                  |                 |       |  |  |

| bit 6                                                                                            | VCFG: Voltage Reference bit<br>1 = VREF pin<br>0 = VDD                                                                                                                                                                                                    |                  |                |                  |                  |                 |       |  |  |

| bit 5-4                                                                                          | Unimplemen                                                                                                                                                                                                                                                | ted: Read as '   | 0'             |                  |                  |                 |       |  |  |

| bit 3-2                                                                                          | CHS<1:0>: A                                                                                                                                                                                                                                               | nalog Channe     | el Select bits |                  |                  |                 |       |  |  |

|                                                                                                  | 00 = AN0<br>01 = AN1<br>10 = AN2<br>11 = AN3                                                                                                                                                                                                              |                  |                |                  |                  |                 |       |  |  |

| bit 1                                                                                            |                                                                                                                                                                                                                                                           | /D Conversion    |                |                  |                  |                 |       |  |  |

|                                                                                                  | <ul> <li>1 = A/D conversion cycle in progress. Setting this bit starts an A/D conversion cycle.<br/>This bit is automatically cleared by hardware when the A/D conversion has completed.</li> <li>0 = A/D conversion completed/not in progress</li> </ul> |                  |                |                  |                  |                 |       |  |  |

| bit 0                                                                                            | <ul> <li>0 = A/D conversion completed/not in progress</li> <li>ADON: ADC Enable bit</li> <li>1 = ADC is enabled</li> <li>0 = ADC is disabled and consumes no operating current</li> </ul>                                                                 |                  |                |                  |                  |                 |       |  |  |

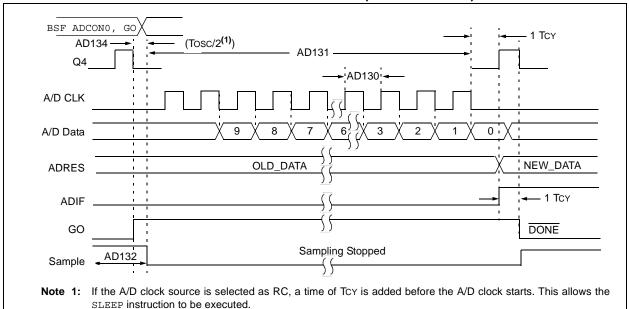

## REGISTER 9-1: ADCON0: A/D CONTROL REGISTER 0

#### 12.3.1 POWER-ON RESET

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply connect the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See **Section 15.0** "**Electrical Specifications**" for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOD (see **Section 12.3.4** "**Brown-Out Reset (BOR)**").

Note: The POR circuit does not produce an internal Reset when VDD declines. To re-enable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to the Application Note *AN607, "Power-up Trouble Shooting"* (DS00607).

#### 12.3.2 MCLR

PIC12F683 has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

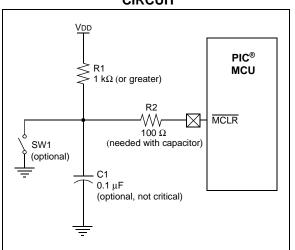

Voltages applied to the MCLR pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the  $\overline{\text{MCLRE}}$  bit in the Configuration Word register. When  $\overline{\text{MCLRE}} = 0$ , the Reset signal to the chip is generated internally. When the  $\overline{\text{MCLRE}} = 1$ , the GP3/ $\overline{\text{MCLR}}$  pin becomes an external Reset input. In this mode, the GP3/ $\overline{\text{MCLR}}$  pin has a weak pull-up to VDD.

#### FIGURE 12-2: RECOMMENDED MCLR CIRCUIT

#### 12.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the 31 kHz LFINTOSC oscillator. For more information, see **Section 3.5 "Internal Clock Modes"**. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip due to:

- VDD variation

- Temperature variation

- Process variation

See DC parameters for details (Section 15.0 "Electrical Specifications").

Note: Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

## 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

## 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 15.2 DC Characteristics: PIC12F683-I (Industrial) PIC12F683-E (Extended)

| DC CHA | ARACTERISTICS                          |     | ard Oper<br>ing temp |      | -40°C ≤ | ≤ TA ≤ +8 | <b>s otherwise stated)</b><br>35°C for industrial<br>125°C for extended |

|--------|----------------------------------------|-----|----------------------|------|---------|-----------|-------------------------------------------------------------------------|

| Param  | Device Characteristics                 | Min | Тур†                 | Max  | Units   |           | Conditions                                                              |

| No.    |                                        |     | -71-1                |      |         | Vdd       | Note                                                                    |

| D010   | Supply Current (IDD) <sup>(1, 2)</sup> | _   | 11                   | 16   | μA      | 2.0       | Fosc = 32 kHz                                                           |

|        |                                        | _   | 18                   | 28   | μA      | 3.0       | LP Oscillator mode                                                      |

|        |                                        | _   | 35                   | 54   | μA      | 5.0       |                                                                         |

| D011*  |                                        | _   | 140                  | 240  | μA      | 2.0       | Fosc = 1 MHz                                                            |

|        |                                        |     | 220                  | 380  | μA      | 3.0       | XT Oscillator mode                                                      |

|        |                                        | _   | 380                  | 550  | μΑ      | 5.0       |                                                                         |

| D012   |                                        | _   | 260                  | 360  | μA      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        |     | 420                  | 650  | μA      | 3.0       | XT Oscillator mode                                                      |

|        |                                        | _   | 0.8                  | 1.1  | mA      | 5.0       |                                                                         |

| D013*  |                                        | _   | 130                  | 220  | μA      | 2.0       | Fosc = 1 MHz                                                            |

|        |                                        | _   | 215                  | 360  | μA      | 3.0       | EC Oscillator mode                                                      |

|        |                                        | _   | 360                  | 520  | μA      | 5.0       |                                                                         |

| D014   |                                        | _   | 220                  | 340  | μA      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        | _   | 375                  | 550  | μA      | 3.0       | EC Oscillator mode                                                      |

|        |                                        | _   | 0.65                 | 1.0  | mA      | 5.0       |                                                                         |

| D015   |                                        | —   | 8                    | 20   | μA      | 2.0       | Fosc = 31 kHz                                                           |

|        |                                        | _   | 16                   | 40   | μA      | 3.0       | LFINTOSC mode                                                           |

|        |                                        | _   | 31                   | 65   | μA      | 5.0       |                                                                         |

| D016*  |                                        | —   | 340                  | 450  | μΑ      | 2.0       | Fosc = 4 MHz                                                            |

|        |                                        | _   | 500                  | 700  | μΑ      | 3.0       | HFINTOSC mode                                                           |

|        |                                        | —   | 0.8                  | 1.2  | mA      | 5.0       |                                                                         |

| D017   |                                        | —   | 410                  | 650  | μA      | 2.0       | Fosc = 8 MHz                                                            |

|        |                                        | —   | 700                  | 950  | μA      | 3.0       | HFINTOSC mode                                                           |

|        |                                        | _   | 1.30                 | 1.65 | mA      | 5.0       |                                                                         |

| D018   |                                        | —   | 230                  | 400  | μA      | 2.0       | FOSC = 4 MHz                                                            |

|        |                                        | —   | 400                  | 680  | μA      | 3.0       | EXTRC mode <sup>(3)</sup>                                               |

|        |                                        |     | 0.63                 | 1.1  | mA      | 5.0       |                                                                         |

| D019   |                                        | —   | 2.6                  | 3.25 | mA      | 4.5       | Fosc = 20 MHz                                                           |

|        |                                        | —   | 2.8                  | 3.35 | mA      | 5.0       | HS Oscillator mode                                                      |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The test conditions for all IDD measurements in active operation mode are: OSC1 = external square wave, from rail-to-rail; all I/O pins tri-stated, pulled to VDD; MCLR = VDD; WDT disabled.

2: The supply current is mainly a function of the operating voltage and frequency. Other factors, such as I/O pin loading and switching rate, oscillator type, internal code execution pattern and temperature, also have an impact on the current consumption.

**3:** For RC oscillator configurations, current through REXT is not included. The current through the resistor can be extended by the formula IR = VDD/2REXT (mA) with REXT in kΩ.

| 15.5 | DC Characteristics: | PIC12F683-I (Industrial) |  |  |

|------|---------------------|--------------------------|--|--|

|      |                     | PIC12F683-E (Extended)   |  |  |

| DC CHARACTERISTICS |                    |                                      | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |       |          |       |                                                                    |  |  |

|--------------------|--------------------|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|----------|-------|--------------------------------------------------------------------|--|--|

| Param<br>No.       | Sym Characteristic |                                      | Min                                                                                                                                                                                     | Тур†  | Мах      | Units | Conditions                                                         |  |  |

|                    | VIL                | Input Low Voltage                    |                                                                                                                                                                                         |       |          |       |                                                                    |  |  |

|                    |                    | I/O Port:                            |                                                                                                                                                                                         |       |          |       |                                                                    |  |  |

| D030               |                    | with TTL buffer                      | Vss                                                                                                                                                                                     | —     | 0.8      | V     | $4.5V \le VDD \le 5.5V$                                            |  |  |

| D030A              |                    |                                      | Vss                                                                                                                                                                                     | —     | 0.15 Vdd | V     | $2.0V \le VDD \le 4.5V$                                            |  |  |

| D031               |                    | with Schmitt Trigger buffer          | Vss                                                                                                                                                                                     | —     | 0.2 Vdd  | V     | $2.0V \le VDD \le 5.5V$                                            |  |  |

| D032               |                    | MCLR, OSC1 (RC mode) <sup>(1)</sup>  | Vss                                                                                                                                                                                     | —     | 0.2 Vdd  | V     |                                                                    |  |  |

| D033               |                    | OSC1 (XT and LP modes)               | Vss                                                                                                                                                                                     | —     | 0.3      | V     |                                                                    |  |  |

| D033A              |                    | OSC1 (HS mode) Vss                   |                                                                                                                                                                                         | —     | 0.3 Vdd  | V     |                                                                    |  |  |

|                    | Vih                | Input High Voltage                   |                                                                                                                                                                                         |       |          |       |                                                                    |  |  |

|                    |                    | I/O ports:                           |                                                                                                                                                                                         | —     |          |       |                                                                    |  |  |

| D040               |                    | with TTL buffer                      | 2.0                                                                                                                                                                                     | —     | Vdd      | V     | $4.5V \le VDD \le 5.5V$                                            |  |  |

| D040A              |                    |                                      | 0.25 VDD + 0.8                                                                                                                                                                          | —     | Vdd      | V     | $2.0V \le VDD \le 4.5V$                                            |  |  |

| D041               |                    | with Schmitt Trigger buffer          | 0.8 Vdd                                                                                                                                                                                 | —     | Vdd      | V     | $2.0V \le VDD \le 5.5V$                                            |  |  |

| D042               |                    | MCLR                                 | 0.8 Vdd                                                                                                                                                                                 | —     | Vdd      | V     |                                                                    |  |  |

| D043               |                    | OSC1 (XT and LP modes)               | 1.6                                                                                                                                                                                     | —     | Vdd      | V     |                                                                    |  |  |

| D043A              |                    | OSC1 (HS mode)                       | 0.7 Vdd                                                                                                                                                                                 | —     | Vdd      | V     |                                                                    |  |  |

| D043B              |                    | OSC1 (RC mode)                       | 0.9 Vdd                                                                                                                                                                                 | —     | Vdd      | V     | (Note 1)                                                           |  |  |

|                    | lı∟                | Input Leakage Current <sup>(2)</sup> |                                                                                                                                                                                         |       |          |       |                                                                    |  |  |

| D060               |                    | I/O ports                            | _                                                                                                                                                                                       | ±0.1  | ± 1      | μA    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                         |  |  |

| D061               |                    | MCLR <sup>(3)</sup>                  | —                                                                                                                                                                                       | ± 0.1 | $\pm 5$  | μA    | $VSS \leq VPIN \leq VDD$                                           |  |  |

| D063               |                    | OSC1                                 | —                                                                                                                                                                                       | ± 0.1 | ± 5      | μA    | Vss $\leq$ VPIN $\leq$ VDD, XT, HS and LP oscillator configuration |  |  |

| D070*              | Ipur               | GPIO Weak Pull-up Current            | 50                                                                                                                                                                                      | 250   | 400      | μA    | VDD = 5.0V, VPIN = VSS                                             |  |  |

| VoL Outp           |                    | Output Low Voltage <sup>(5)</sup>    |                                                                                                                                                                                         |       |          |       |                                                                    |  |  |

| D080               |                    | I/O ports                            | —                                                                                                                                                                                       |       | 0.6      | V     | IOL = 8.5 mA, VDD = 4.5V (Ind.)                                    |  |  |

|                    | Vон                | Output High Voltage <sup>(5)</sup>   |                                                                                                                                                                                         |       |          |       |                                                                    |  |  |

| D090               |                    | I/O ports                            | Vdd - 0.7                                                                                                                                                                               | —     | —        | V     | IOH = -3.0 mA, VDD = 4.5V (Ind.)                                   |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

2: Negative current is defined as current sourced by the pin.

3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

4: See Section 10.4.1 "Using the Data EEPROM" for additional information.

5: Including OSC2 in CLKOUT mode.

## 15.5 DC Characteristics: PIC12F683-I (Industrial) PIC12F683-E (Extended) (Continued)

| DC CH        | ARACTE | RISTICS                                                             | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for industrial $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |     |       |                                                                                                     |  |

|--------------|--------|---------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Sym    | Characteristic                                                      | Min                                                                                                                                                                                     | Тур† | Max | Units | Conditions                                                                                          |  |

| D100         | IULP   | Ultra Low-Power Wake-Up<br>Current                                  | _                                                                                                                                                                                       | 200  | _   | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |  |

|              |        | Capacitive Loading Specs on<br>Output Pins                          |                                                                                                                                                                                         |      |     |       |                                                                                                     |  |

| D101*        | COSC2  | OSC2 pin                                                            | _                                                                                                                                                                                       | -    | 15  | pF    | In XT, HS and LP modes when<br>external clock is used to drive<br>OSC1                              |  |

| D101A*       | Сю     | All I/O pins                                                        | _                                                                                                                                                                                       | —    | 50  | pF    |                                                                                                     |  |

|              |        | Data EEPROM Memory                                                  |                                                                                                                                                                                         |      |     |       |                                                                                                     |  |

| D120         | ED     | Byte Endurance                                                      | 100K                                                                                                                                                                                    | 1M   | _   | E/W   | $-40^{\circ}C \le TA \le +85^{\circ}C$                                                              |  |

| D120A        | ED     | Byte Endurance                                                      | 10K                                                                                                                                                                                     | 100K | _   | E/W   | +85°C ≤ TA ≤ +125°C                                                                                 |  |

| D121         | Vdrw   | VDD for Read/Write                                                  | VMIN                                                                                                                                                                                    | -    | 5.5 | V     | Using EECON1 to read/write<br>VMIN = Minimum operating<br>voltage                                   |  |

| D122         | TDEW   | Erase/Write Cycle Time                                              | _                                                                                                                                                                                       | 5    | 6   | ms    |                                                                                                     |  |