# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                         |

|----------------------------|-------------------------------------------------------------------------|

| Product Status             | Active                                                                  |

| Core Processor             | PIC                                                                     |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 20MHz                                                                   |

| Connectivity               | -                                                                       |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                   |

| Number of I/O              | 5                                                                       |

| Program Memory Size        | 3.5KB (2K x 14)                                                         |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | 256 x 8                                                                 |

| RAM Size                   | 128 x 8                                                                 |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                               |

| Data Converters            | A/D 4x10b                                                               |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                      |

| Mounting Type              | Through Hole                                                            |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                                  |

| Supplier Device Package    | 8-PDIP                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683-e-p |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 3.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or the internal oscillator.

| IGURE 3-7:      | TWO-SPEED START-UP |

|-----------------|--------------------|

| HFINTOSC        |                    |

|                 |                    |

| OSC1            |                    |

| OSC2            |                    |

| Program Counter | PC - N \ PC + 1    |

| System Clock    |                    |

|                 |                    |

#### F

| U-0U-0R/W-1R/W-1U-0R/W-1R/W-1R/W $ -$ WPU5WPU4 $-$ WPU2WPU1WPbit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 7-6Unimplemented: Read as '0'<br>bit 5-4WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabledUnimplemented: Read as '0'bit 3Unimplemented: Read as '0'Unimplemented: Read as '0'Unimplemented: Read as '0' |       |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|--|--|--|--|--|--|

| bit 7<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 7-6 Unimplemented: Read as '0'<br>bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                            | ·1    |  |  |  |  |  |  |

| Legend:         R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-6       Unimplemented: Read as '0'         bit 5-4       WPU<5:4>: Weak Pull-up Control bits         1 = Pull-up enabled       0 = Pull-up disabled                                                                                               | 10    |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-6       Unimplemented: Read as '0'         bit 5-4       WPU<5:4>: Weak Pull-up Control bits         1 = Pull-up enabled       0 = Pull-up disabled                                                                                                               | bit 0 |  |  |  |  |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-6       Unimplemented: Read as '0'       '0' = Bit is cleared       x = Bit is unknown         bit 5-4       WPU<5:4>: Weak Pull-up Control bits       1 = Pull-up enabled       0 = Pull-up disabled                                                             |       |  |  |  |  |  |  |

| -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 7-6       Unimplemented: Read as '0'       WPU<5:4>: Weak Pull-up Control bits         1 = Pull-up enabled       0 = Pull-up disabled                                                                                                                                                                                                                        |       |  |  |  |  |  |  |

| bit 7-6 Unimplemented: Read as '0'<br>bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                      |       |  |  |  |  |  |  |

| bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                            |       |  |  |  |  |  |  |

| bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                            |       |  |  |  |  |  |  |

| 1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                                           |       |  |  |  |  |  |  |

| 0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |  |  |  |  |  |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |  |  |  |  |  |  |

| bit 3 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |       |  |  |  |  |  |  |

| bit 2-0 WPU<2:0>: Weak Pull-up Control bits                                                                                                                                                                                                                                                                                                                                                                                                                           |       |  |  |  |  |  |  |

| 1 = Pull-up enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       |  |  |  |  |  |  |

| 0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |  |  |  |  |  |  |

| <b>Note 1:</b> Global GPPU must be enabled for individual pull-ups to be enabled.                                                                                                                                                                                                                                                                                                                                                                                     |       |  |  |  |  |  |  |

#### REGISTER 4-4: WPU: WEAK PULL-UP REGISTER

- Clobal Of FO must be enabled for individual pull-ups to be enabled.

The weak pull-up device is automatically disabled if the pin is in Output mode (TRISIO = 0).

- 3: The GP3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

- 4: WPU<5:4> always reads '1' in XT, HS and LP OSC modes.

#### REGISTER 4-5: IOC: INTERRUPT-ON-CHANGE GPIO REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | IOC5  | IOC4  | IOC3  | IOC2  | IOC1  | IOC0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOC<5:0>:** Interrupt-on-change GPIO Control bits

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOC<5:4> always reads '0' in XT, HS and LP OSC modes.

#### 4.2.4 ULTRA LOW-POWER WAKE-UP

The Ultra Low-Power Wake-up (ULPWU) on GP0 allows a slow falling voltage to generate an interrupt-on-change on GP0 without excess current consumption. The mode is selected by setting the ULPWUE bit of the PCON register. This enables a small current sink which can be used to discharge a capacitor on GP0.

To use this feature, the GP0 pin is configured to output '1' to charge the capacitor, interrupt-on-change for GP0 is enabled and GP0 is configured as an input. The ULP-WUE bit is set to begin the discharge and a SLEEP instruction is performed. When the voltage on GP0 drops below VIL, an interrupt will be generated which will cause the device to wake-up. Depending on the state of the GIE bit of the INTCON register, the device will either jump to the interrupt vector (0004h) or execute the next instruction when the interrupt event occurs. See Section 4.2.3 "Interrupt-on-Change" and Section 12.4.3 "GPIO Interrupt" for more information.

This feature provides a low-power technique for periodically waking up the device from Sleep. The time-out is dependent on the discharge time of the RC circuit on GP0. See Example 4-2 for initializing the Ultra Low-Power Wake-up module.

The series resistor provides overcurrent protection for the GP0 pin and can allow for software calibration of the time-out (see Figure 4-1). A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The Ultra Low-Power Wake-up peripheral can also be configured as a simple Programmable Low-Voltage Detect or temperature sensor.

| Note: | For more information, refer to the Applica- |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|

|       | tion Note AN879, "Using the Microchip       |  |  |  |  |  |  |  |  |

|       | Ultra Low-Power Wake-up Module"             |  |  |  |  |  |  |  |  |

|       | (DS00879).                                  |  |  |  |  |  |  |  |  |

### EXAMPLE 4-2:

#### ULTRA LOW-POWER WAKE-UP INITIALIZATION

| BANKSEL | CMCON0       | ;                   |

|---------|--------------|---------------------|

| MOVLW   | H'7'         | ;Turn off           |

| MOVWF   | CMCON0       | ;comparators        |

| BANKSEL | ANSEL        | ;                   |

| BCF     | ANSEL,0      | ;RA0 to digital I/O |

| BCF     | TRISA,0      | ;Output high to     |

| BANKSEL | PORTA        | ;                   |

| BSF     | PORTA,0      | ;charge capacitor   |

| CALL    | CapDelay     | ;                   |

| BANKSEL | PCON         | ;                   |

| BSF     | PCON, ULPWUE | ;Enable ULP Wake-up |

| BSF     | IOCA,0       | ;Select RA0 IOC     |

| BSF     | TRISA,0      | ;RA0 to input       |

| MOVLW   | B'10001000'  | ;Enable interrupt   |

| MOVWF   | INTCON       | ; and clear flag    |

| SLEEP   |              | ;Wait for IOC       |

| NOP     |              | ;                   |

|         |              |                     |

# **PIC12F683**

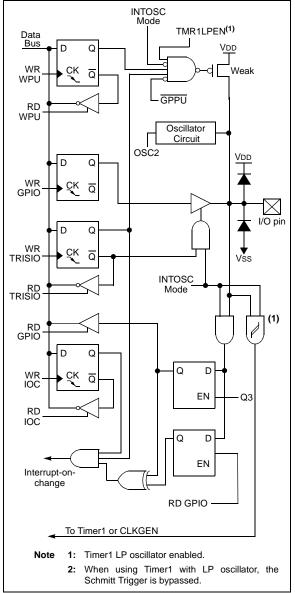

#### 4.2.5.6 GP5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

#### FIGURE 4-6:

# BLOCK DIAGRAM OF GP5

#### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH GPIO

| Name       | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|---------|---------|---------|---------|---------|---------|-------------------|---------------------------------|

| ANSEL      | _      | ADCS2  | ADCS1   | ADCS0   | ANS3    | ANS2    | ANS1    | ANS0    | -000 1111         | -000 1111                       |

| CCP1CON    | _      | _      | DC1B1   | DC1B0   | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 00 0000           | 00 0000                         |

| CMCON0     | _      | COUT   | _       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000         | -0-0 0000                       |

| PCON       | _      | _      | ULPWUE  | SBOREN  | _       | _       | POR     | BOR     | 01qq              | 0uuu                            |

| INTCON     | GIE    | PEIE   | TOIE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000         | 0000 000x                       |

| IOC        | _      | _      | IOC5    | IOC4    | IOC3    | IOC2    | IOC1    | IOC0    | 00 0000           | 00 0000                         |

| OPTION_REG | GPPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111         | 1111 1111                       |

| GPIO       | _      | _      | GP5     | GP4     | GP3     | GP2     | GP1     | GP0     | xx xxxx           | x0 x000                         |

| T1CON      | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC  | TMR1CS  | TMR10N  | 0000 0000         | 0000 0000                       |

| TRISIO     | _      | _      | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111           | 11 1111                         |

| WPU        | _      | _      | WPU5    | WPU4    | _       | WPU2    | WPU1    | WPU0    | 11 -111           | 11 -111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by GPIO.

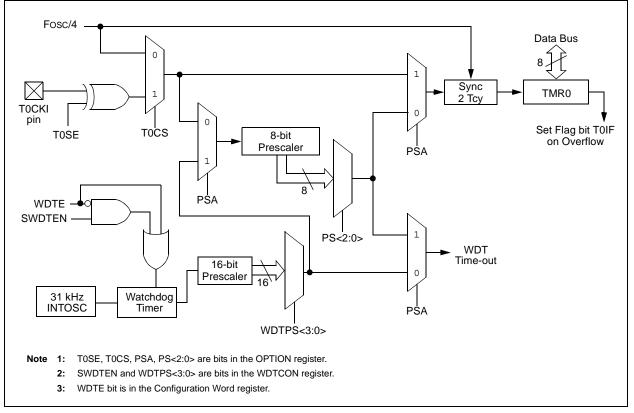

# 5.0 TIMER0 MODULE

The Timer0 module is an 8-bit timer/counter with the following features:

- 8-bit timer/counter register (TMR0)

- 8-bit prescaler (shared with Watchdog Timer)

- Programmable internal or external clock source

- · Programmable external clock edge selection

- Interrupt on overflow

Figure 5-1 is a block diagram of the Timer0 module.

# 5.1 Timer0 Operation

When used as a timer, the Timer0 module can be used as either an 8-bit timer or an 8-bit counter.

#### 5.1.1 8-BIT TIMER MODE

When used as a timer, the Timer0 module will increment every instruction cycle (without prescaler). Timer mode is selected by clearing the T0CS bit of the OPTION register to '0'.

When TMR0 is written, the increment is inhibited for two instruction cycles immediately following the write.

Note: The value written to the TMR0 register can be adjusted, in order to account for the two instruction cycle delay when TMR0 is written.

#### 5.1.2 8-BIT COUNTER MODE

When used as a counter, the Timer0 module will increment on every rising or falling edge of the T0CKI pin. The incrementing edge is determined by the T0SE bit of the OPTION register. Counter mode is selected by setting the T0CS bit of the OPTION register to '1'.

#### FIGURE 5-1: BLOCK DIAGRAM OF THE TIMER0/WDT PRESCALER

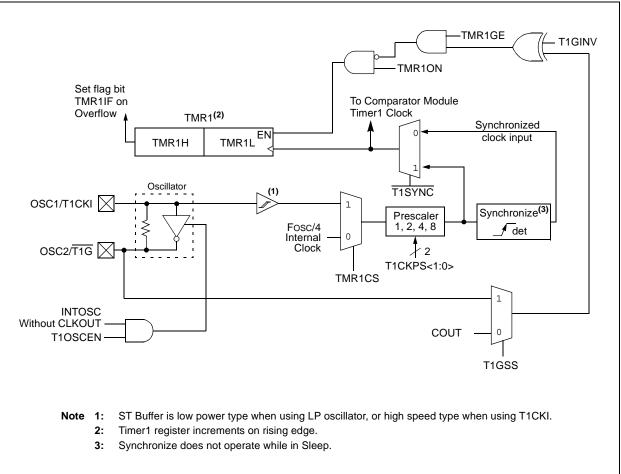

# 6.0 TIMER1 MODULE WITH GATE CONTROL

The Timer1 module is a 16-bit timer/counter with the following features:

- 16-bit timer/counter register pair (TMR1H:TMR1L)

- · Programmable internal or external clock source

- 3-bit prescaler

- Optional LP oscillator

- · Synchronous or asynchronous operation

- Timer1 gate (count enable) via comparator or T1G pin

- Interrupt on overflow

- Wake-up on overflow (external clock, Asynchronous mode only)

- Special Event Trigger (with CCP)

- Comparator output synchronization to Timer1 clock

Figure 6-1 is a block diagram of the Timer1 module.

#### FIGURE 6-1: TIMER1 BLOCK DIAGRAM

# 6.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing counter which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the counter.

When used with an internal clock source, the module is a timer. When used with an external clock source, the module can be used as either a timer or counter.

# 6.2 Clock Source Selection

The TMR1CS bit of the T1CON register is used to select the clock source. When TMR1CS = 0, the clock source is FOSC/4. When TMR1CS = 1, the clock source is supplied externally.

| Clock Source | TMR1CS |

|--------------|--------|

| Fosc/4       | 0      |

| T1CKI pin    | 1      |

# 6.11 Timer1 Control Register

The Timer1 Control register (T1CON), shown in Register 6-1, is used to control Timer1 and select the various features of the Timer1 module.

#### REGISTER 6-1: T1CON: TIMER1 CONTROL REGISTER

| R/W-0      | R/W-0                                             | R/W-0                            | R/W-0                  | R/W-0             | R/W-0           | R/W-0           | R/W-0     |

|------------|---------------------------------------------------|----------------------------------|------------------------|-------------------|-----------------|-----------------|-----------|

| T1GINV     | (1) TMR1GE <sup>(2)</sup>                         | T1CKPS1                          | T1CKPS0                | T1OSCEN           | T1SYNC          | TMR1CS          | TMR10N    |

| bit 7      | ł                                                 |                                  |                        |                   |                 |                 | bit 0     |

|            |                                                   |                                  |                        |                   |                 |                 |           |

| Legend:    |                                                   |                                  |                        |                   |                 |                 |           |

| R = Reada  | able bit                                          | W = Writable                     |                        | U = Unimplem      | nented bit, rea |                 |           |

| -n = Value | at POR                                            | '1' = Bit is set                 |                        | '0' = Bit is clea | ared            | x = Bit is unkr | nown      |

| bit 7      |                                                   | er1 Gate Invert                  | hit(1)                 |                   |                 |                 |           |

| DIL 7      |                                                   |                                  |                        | nts when gate i   | s hiah)         |                 |           |

|            |                                                   |                                  |                        | nts when gate is  |                 |                 |           |

| bit 6      | TMR1GE: Tim                                       | ner1 Gate Ena                    | ble bit <sup>(2)</sup> |                   |                 |                 |           |

|            | If TMR1ON =                                       |                                  |                        |                   |                 |                 |           |

|            | This bit is igno<br>If TMR1ON =                   |                                  |                        |                   |                 |                 |           |

|            |                                                   | <u> </u>                         | ate is not active      | е                 |                 |                 |           |

|            | 0 = Timer1 is                                     |                                  |                        |                   |                 |                 |           |

| bit 5-4    | T1CKPS<1:0                                        | >: Timer1 Inpu                   | t Clock Presca         | ale Select bits   |                 |                 |           |

|            | 11 = 1:8 Pres                                     |                                  |                        |                   |                 |                 |           |

|            | 10 = 1:4 Pres<br>01 = 1:2 Pres                    |                                  |                        |                   |                 |                 |           |

|            | 00 = 1:1 Pres                                     |                                  |                        |                   |                 |                 |           |

| bit 3      | T1OSCEN: LI                                       | P Oscillator En                  | able Control b         | it                |                 |                 |           |

|            |                                                   | hout CLKOUT                      |                        |                   |                 |                 |           |

|            | 1 = LP oscilla<br>0 = LP oscilla                  | tor is enabled f<br>tor is off   | or limer1 cloc         | CK                |                 |                 |           |

|            | <u>Else:</u>                                      |                                  |                        |                   |                 |                 |           |

|            |                                                   | ored. LP oscilla                 |                        |                   |                 |                 |           |

| bit 2      |                                                   |                                  | lock Input Syn         | chronization Co   | ontrol bit      |                 |           |

|            | $\frac{\text{TMR1CS} = 1}{1 - \text{Do not sys}}$ | nchronize exte                   | rnal clock innu        | ıt                |                 |                 |           |

|            |                                                   | ize external clo                 |                        |                   |                 |                 |           |

|            | $\frac{TMR1CS = 0}{TMR1CS}$                       |                                  |                        |                   |                 |                 |           |

| 1.1.4      | 0                                                 | ored. Timer1 u                   |                        | al clock          |                 |                 |           |

| bit 1      |                                                   | her1 Clock Sou<br>clock from T1C |                        | ricing odgo)      |                 |                 |           |

|            | 1 = External c<br>0 = Internal cl                 |                                  | Ki pin (on the         | nsing edge)       |                 |                 |           |

| bit 0      | TMR1ON: Tin                                       |                                  |                        |                   |                 |                 |           |

|            | 1 = Enables T<br>0 = Stops Tim                    |                                  |                        |                   |                 |                 |           |

| Note 1:    | T1GINV bit inverts                                | the Timer1 ga                    | te logic, regard       | dless of source.  |                 |                 |           |

| 2:         | TMR1GE bit must register, as a Time               | be set to use e                  | either T1G pin         |                   |                 | T1GSS bit of th | ne CMCON1 |

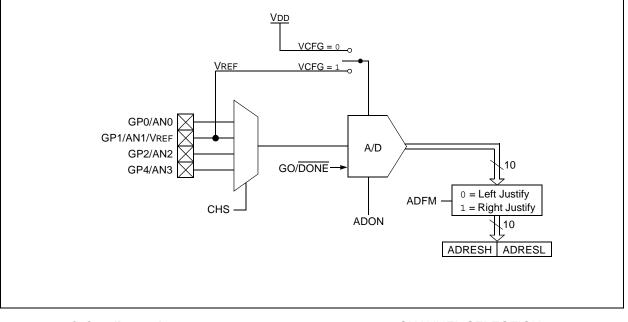

# 9.0 ANALOG-TO-DIGITAL CONVERTER (ADC) MODULE

The Analog-to-Digital Converter (ADC) allows conversion of an analog input signal to a 10-bit binary representation of that signal. This device uses analog inputs, which are multiplexed into a single sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a 10-bit binary result via successive approximation and stores the conversion result into the ADC result registers (ADRESL and ADRESH).

# The ADC voltage reference is software selectable to either VDD or a voltage applied to the external reference pins.

The ADC can generate an interrupt upon completion of a conversion. This interrupt can be used to wake-up the device from Sleep.

Figure 9-1 shows the block diagram of the ADC.

# FIGURE 9-1: ADC BLOCK DIAGRAM

# 9.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- GPIO configuration

- Channel selection

- ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- Results formatting

# 9.1.1 GPIO CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. See the corresponding GPIO section for more information.

Note: Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

# 9.1.2 CHANNEL SELECTION

The CHS bits of the ADCON0 register determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 9.2 "ADC Operation"** for more information.

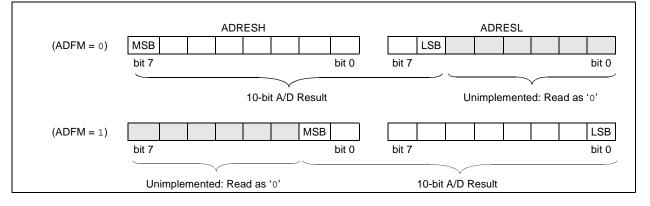

RESULT FORMATTING

the ADCON0 register controls the output format.

Figure 9-3 shows the two output formats.

The 10-bit A/D conversion result can be supplied in two

formats, left justified or right justified. The ADFM bit of

#### 9.1.5 INTERRUPTS

The ADC module allows for the ability to generate an interrupt upon completion of an Analog-to-Digital conversion. The ADC interrupt flag is the ADIF bit in the PIR1 register. The ADC interrupt enable is the ADIE bit in the PIE1 register. The ADIF bit must be cleared in software.

| Note: | The ADIF bit is set at the completion of |

|-------|------------------------------------------|

|       | every conversion, regardless of whether  |

|       | or not the ADC interrupt is enabled.     |

This interrupt can be generated while the device is operating or while in Sleep. If the device is in Sleep, the interrupt will wake-up the device. Upon waking from Sleep, the next instruction following the SLEEP instruction is always executed. If the user is attempting to wake-up from Sleep and resume in-line code execution, the global interrupt must be disabled. If the global interrupt is enabled, execution will switch to the interrupt service routine.

Please see **Section 12.4** "Interrupts" for more information.

#### FIGURE 9-3: 10-BIT A/D CONVERSION RESULT FORMAT

9.1.6

#### 9.2 ADC Operation

#### 9.2.1 STARTING A CONVERSION

To enable the ADC module, the ADON bit of the ADCON0 register must be set to a '1'. Setting the GO/DONE bit of the ADCON0 register to a '1' will start the Analog-to-Digital conversion.

#### 9.2.2 COMPLETION OF A CONVERSION

When the conversion is complete, the ADC module will:

- Clear the GO/DONE bit

- Set the ADIF flag bit

- Update the ADRESH:ADRESL registers with new conversion result

# 9.2.3 TERMINATING A CONVERSION

If a conversion must be terminated before completion, the GO/DONE bit can be cleared in software. The ADRESH:ADRESL registers will not be updated with the partially complete Analog-to-Digital conversion sample. Instead, the ADRESH:ADRESL register pair will retain the value of the previous conversion. Additionally, a 2 TAD delay is required before another acquisition can be initiated. Following this delay, an input acquisition is automatically started on the selected channel.

Note: A device Reset forces all registers to their Reset state. Thus, the ADC module is turned off and any pending conversion is terminated.

Note: The GO/DONE bit should not be set in the same instruction that turns on the ADC. Refer to Section 9.2.6 "A/D Conversion Procedure".

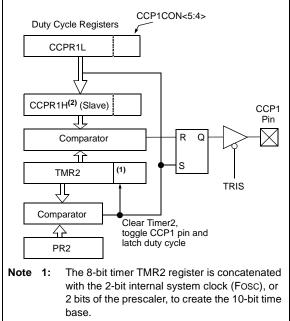

# 11.3 PWM Mode

The PWM mode generates a Pulse-Width Modulated signal on the CCP1 pin. The duty cycle, period and resolution are determined by the following registers:

- PR2

- T2CON

- CCPR1L

- CCP1CON

In Pulse-Width Modulation (PWM) mode, the CCP module produces up to a 10-bit resolution PWM output on the CCP1 pin. Since the CCP1 pin is multiplexed with the PORT data latch, the TRIS for that pin must be cleared to enable the CCP1 pin output driver.

| Note: | Clearing   | the | CCP1CON        | register | will |

|-------|------------|-----|----------------|----------|------|

|       | relinquish | CCP | 1 control of t | ne CCP1  | pin. |

Figure 11-1 shows a simplified block diagram of PWM operation.

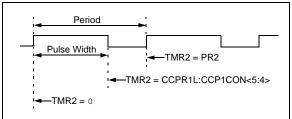

Figure 11-4 shows a typical waveform of the PWM signal.

For a step-by-step procedure on how to set up the CCP module for PWM operation, see **Section 11.3.7** "Setup for PWM Operation".

FIGURE 11-3: SIMPLIFIED PWM BLOCK DIAGRAM

2: In PWM mode, CCPR1H is a read-only register.

The PWM output (Figure 11-4) has a time base (period) and a time that the output stays high (duty cycle).

FIGURE 11-4: CCP PWM OUTPUT

|               | -                                                                    |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|---------------|----------------------------------------------------------------------|---------------------------------|---------------|------------------|------------------|-----------------|--------|--|--|--|--|--|

| U-0           | U-0                                                                  | U-0                             | R/W-0         | R/W-1            | R/W-0            | R/W-0           | R/W-0  |  |  |  |  |  |

| —             |                                                                      | —                               | WDTPS3        | WDTPS2           | WDTPS1           | WDTPS0          | SWDTEN |  |  |  |  |  |

| bit 7         |                                                                      | ·                               |               |                  |                  |                 | bit    |  |  |  |  |  |

|               |                                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

| Legend:       |                                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

| R = Readabl   | le bit                                                               | W = Writable                    | bit           | U = Unimpler     | mented bit, read | l as '0'        |        |  |  |  |  |  |

| -n = Value at | t POR                                                                | '1' = Bit is set                | :             | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |  |  |  |  |  |

|               |                                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

| bit 7-5       | Unimplemen                                                           | ted: Read as '                  | 0'            |                  |                  |                 |        |  |  |  |  |  |

| bit 4-1       | WDTPS<3:0                                                            | >: Watchdog Ti                  | mer Period Se | elect bits       |                  |                 |        |  |  |  |  |  |

|               | Bit Value = P                                                        | Bit Value = Prescale Rate       |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0000 = 1:32                                                          | 2                               |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0001 = 1:64                                                          | Ļ                               |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0010 = 1:128                                                         |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0011 = <b>1</b> :256                                                 |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0100 = 1:512 (Reset value)                                           |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               |                                                                      | 0101 = 1:1024                   |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0110 = 1:2048                                                        |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 0111 = 1:4096                                                        |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               |                                                                      | 1000 = 1:8192<br>1001 = 1:16384 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1001 = 1.10304<br>1010 = 1:32768                                     |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1010 = 1.32703<br>1011 = 1.65536                                     |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1100 = Reserved                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1101 = Reserved                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1110 = Reserved                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1111 = Reserved                                                      |                                 |               |                  |                  |                 |        |  |  |  |  |  |

| bit 0         | SWDTEN: Software Enable or Disable the Watchdog Timer <sup>(1)</sup> |                                 |               |                  |                  |                 |        |  |  |  |  |  |

|               | 1 = WDT is tu                                                        | urned on                        |               | -                |                  |                 |        |  |  |  |  |  |

|               | 0 = WDT is tu                                                        | urned off (Rese                 | t value)      |                  |                  |                 |        |  |  |  |  |  |

|               | WDTE Configuration bit =                                             |                                 |               |                  |                  |                 | f WDTE |  |  |  |  |  |

|               | C C                                                                  | •                               |               |                  |                  |                 |        |  |  |  |  |  |

# REGISTER 12-2: WDTCON: WATCHDOG TIMER CONTROL REGISTER

TABLE 12-8: SUMMARY OF REGISTERS ASSOCIATED WITH WATCHDOG TIMER

| Name       | Bit 7 | Bit 6  | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|-------|--------|-------|--------|--------|--------|--------|--------|----------------------|---------------------------------|

| WDTCON     | _     | —      | _     | WDTPS3 | WDTPS2 | WSTPS1 | WDTPS0 | SWDTEN | 0 1000               | 0 1000                          |

| OPTION_REG | GPPU  | INTEDG | TOCS  | T0SE   | PSA    | PS2    | PS1    | PS0    | 1111 1111            | 1111 1111                       |

| CONFIG     | CPD   | CP     | MCLRE | PWRTE  | WDTE   | FOSC2  | FOSC1  | FOSC0  | _                    | —                               |

Legend: Shaded cells are not used by the Watchdog Timer.

Note 1: See Register 12-1 for operation of all Configuration Word register bits.

# 13.0 INSTRUCTION SET SUMMARY

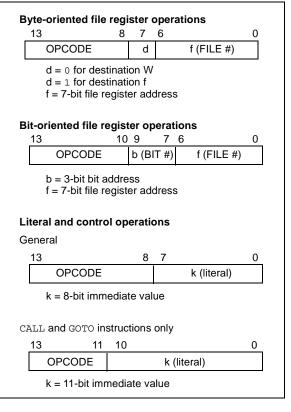

The PIC12F683 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM<sup>TM</sup> assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

# 13.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

#### TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                              |

| W     | Working register (accumulator)                                                                                                                                                    |

| b     | Bit address within an 8-bit file register                                                                                                                                         |

| k     | Literal field, constant data or label                                                                                                                                             |

| x     | Don't care location (= $0$ or 1).<br>The assembler will generate code with x = $0$ .<br>It is the recommended form of use for<br>compatibility with all Microchip software tools. |

| d     | Destination select; $d = 0$ : store result in W,<br>d = 1: store result in file register f.<br>Default is $d = 1$ .                                                               |

| PC    | Program Counter                                                                                                                                                                   |

| TO    | Time-out bit                                                                                                                                                                      |

| С     | Carry bit                                                                                                                                                                         |

| DC    | Digit carry bit                                                                                                                                                                   |

| Z     | Zero bit                                                                                                                                                                          |

| PD    | Power-down bit                                                                                                                                                                    |

# FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

| Mnem   | onic,  | Description                  | Cycles       |       | 14-Bit       | Opcode | Status | Natas         |         |

|--------|--------|------------------------------|--------------|-------|--------------|--------|--------|---------------|---------|

| Opera  | ands   | Description                  |              | MSb   |              |        | LSb    | Affected      | Notes   |

|        |        | BYTE-ORIENTED FILE REGIS     | TER OPE      | RATIC | ONS          |        |        |               |         |

| ADDWF  | f, d   | Add W and f                  | 1            | 00    | 0111         | dfff   | ffff   | C, DC, Z      | 1, 2    |

| ANDWF  | f, d   | AND W with f                 | 1            | 00    | 0101         | dfff   | ffff   | Z             | 1, 2    |

| CLRF   | f      | Clear f                      | 1            | 00    | 0001         | lfff   | ffff   | Z             | 2       |

| CLRW   | -      | Clear W                      | 1            | 00    | 0001         | 0xxx   | xxxx   | Z             |         |

| COMF   | f, d   | Complement f                 | 1            | 00    | 1001         | dfff   | ffff   | Z             | 1, 2    |

| DECF   | f, d   | Decrement f                  | 1            | 00    | 0011         | dfff   | ffff   | Z             | 1, 2    |

| DECFSZ | f, d   | Decrement f, Skip if 0       | 1 <b>(2)</b> | 00    | 1011         | dfff   | ffff   |               | 1, 2, 3 |

| INCF   | f, d   | Increment f                  | 1            | 00    | 1010         | dfff   | ffff   | Z             | 1, 2    |

| INCFSZ | f, d   | Increment f, Skip if 0       | 1 <b>(2)</b> | 00    | 1111         | dfff   | ffff   |               | 1, 2, 3 |

| IORWF  | f, d   | Inclusive OR W with f        | 1            | 00    | 0100         | dfff   | ffff   | Z             | 1, 2    |

| MOVF   | f, d   | Move f                       | 1            | 00    | 1000         | dfff   | ffff   | Z             | 1, 2    |

| MOVWF  | f      | Move W to f                  | 1            | 00    | 0000         | lfff   | ffff   |               | ,       |

| NOP    | _      | No Operation                 | 1            | 00    | 0000         | 0xx0   | 0000   |               |         |

| RLF    | f. d   | Rotate Left f through Carry  | 1            | 00    | 1101         |        | ffff   | С             | 1, 2    |

| RRF    | f, d   | Rotate Right f through Carry | 1            | 00    | 1100         |        | ffff   | Ċ             | 1, 2    |

| SUBWF  | f, d   | Subtract W from f            | 1            | 00    | 0010         |        | ffff   | C, DC, Z      | 1, 2    |

| SWAPF  | f, d   | Swap nibbles in f            | 1            | 00    | 1110         | dfff   | ffff   | 0,20,2        | 1, 2    |

| XORWF  | f, d   | Exclusive OR W with f        | 1            | 00    | 0110         |        | ffff   | Z             | 1, 2    |

|        |        | BIT-ORIENTED FILE REGIST     |              | RATIO | NS           |        |        |               |         |

| BCF    | f, b   | Bit Clear f                  | 1            | 01    | 00bb         | bfff   | ffff   |               | 1, 2    |

| BSF    | f, b   | Bit Set f                    | 1            | 01    |              | bfff   |        |               | 1, 2    |

| BTFSC  | f, b   | Bit Test f, Skip if Clear    | 1 (2)        | 01    | 10bb         |        | ffff   |               | 3       |

| BTFSS  | f, b   | Bit Test f, Skip if Set      | 1 (2)        | 01    | 11bb         | bfff   | ffff   |               | 3       |

| 51100  | 1, 5   |                              |              |       | 1100         | DIII   |        |               | Ū       |

| ADDLW  | k      | Add literal and W            | 1            | 11    | 111x         | kkkk   | kkkk   | C, DC, Z      |         |

| ANDLW  | k      | AND literal with W           | 1            | 11    |              | kkkk   |        | Z             |         |

| CALL   | k      | Call Subroutine              | 2            | 10    |              | kkkk   |        | _             |         |

| CLRWDT | _      | Clear Watchdog Timer         | 1            | 00    | 0000         | 0110   | 0100   | TO, PD        |         |

| GOTO   | k      | Go to address                | 2            | 10    |              | kkkk   |        | 10,10         |         |

| IORLW  | k      | Inclusive OR literal with W  | 1            | 11    | 1000         | kkkk   |        | Z             |         |

| MOVLW  | k      | Move literal to W            | 1            | 11    |              | kkkk   |        | _             |         |

| RETFIE | - K    | Return from interrupt        | 2            | 00    | 0000         | 0000   | 1001   |               |         |

| RETLW  | k      | Return with literal in W     | 2            | 11    |              | kkkk   |        |               |         |

| RETURN | к<br>— | Return from Subroutine       | 2            | 00    | 0000         | 0000   | 1000   |               |         |

| SLEEP  | _      | Go into Standby mode         | 1            | 00    | 0000         | 0110   | 0011   | TO, PD        |         |

| SUBLW  | –<br>k | Subtract W from literal      | 1            | 11    |              | kkkk   |        | C, DC, Z      |         |

| XORLW  | ĸ<br>k | Exclusive OR literal with W  | 1            | 11    | 1010<br>1010 | kkkk   |        | C, DC, Z<br>Z |         |

| NONLIN | N      |                              | · ·          | 11    | 1010         | VVVV   | VVVV   | ~             |         |

# TABLE 13-2: PIC12F683 INSTRUCTION SET

**Note 1:** When an I/O register is modified as a function of itself (e.g., MOVF GPIO, 1), the value used will be that value present on the pins themselves. For example, if the data latch is '1' for a pin configured as input and is driven low by an external device, the data will be written back with a '0'.

2: If this instruction is executed on the TMR0 register (and where applicable, d = 1), the prescaler will be cleared if assigned to the Timer0 module.

**3:** If the Program Counter (PC) is modified, or a conditional test is true, the instruction requires two cycles. The second cycle is executed as a NOP.

| DECFSZ           | Decrement f, Skip if 0                                                                                                                                                                                                                                                                                                                   |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] DECFSZ f,d                                                                                                                                                                                                                                                                                                              |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                          |

| Operation:       | (f) - 1 $\rightarrow$ (destination);<br>skip if result = 0                                                                                                                                                                                                                                                                               |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                     |

| Description:     | The contents of register 'f' are<br>decremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', then a NOP is<br>executed instead, making it a<br>2-cycle instruction. |

| INCFSZ           | Increment f, Skip if 0                                                                                                                                                                                                                                                                                                              |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ <i>label</i> ] INCFSZ f,d                                                                                                                                                                                                                                                                                                         |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                                                                                                                                                                                     |

| Operation:       | (f) + 1 $\rightarrow$ (destination),<br>skip if result = 0                                                                                                                                                                                                                                                                          |

| Status Affected: | None                                                                                                                                                                                                                                                                                                                                |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'.<br>If the result is '1', the next<br>instruction is executed. If the<br>result is '0', a NOP is executed<br>instead, making it a 2-cycle<br>instruction. |

| GOTO             | Unconditional Branch                                                                                                                                                                             |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] GOTO k                                                                                                                                                                          |  |  |  |  |  |

| Operands:        | $0 \le k \le 2047$                                                                                                                                                                               |  |  |  |  |  |

| Operation:       | $k \rightarrow PC<10:0>$<br>PCLATH<4:3> $\rightarrow$ PC<12:11>                                                                                                                                  |  |  |  |  |  |

| Status Affected: | None                                                                                                                                                                                             |  |  |  |  |  |

| Description:     | GOTO is an unconditional branch.<br>The eleven-bit immediate value is<br>loaded into PC bits <10:0>. The<br>upper bits of PC are loaded from<br>PCLATH<4:3>. GOTO is a<br>two-cycle instruction. |  |  |  |  |  |

| IORLW            | Inclusive OR literal with W                                                                                               |  |  |  |  |  |

|------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ <i>label</i> ] IORLW k                                                                                                  |  |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                         |  |  |  |  |  |

| Operation:       | (W) .OR. $k \rightarrow$ (W)                                                                                              |  |  |  |  |  |

| Status Affected: | Z                                                                                                                         |  |  |  |  |  |

| Description:     | The contents of the W register are<br>OR'ed with the eight-bit literal 'k'.<br>The result is placed in the<br>W register. |  |  |  |  |  |

| INCF             | Increment f                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] INCF f,d                                                                                                                                                           |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in \ [0,1] \end{array}$                                                                                                          |

| Operation:       | (f) + 1 $\rightarrow$ (destination)                                                                                                                                        |

| Status Affected: | Z                                                                                                                                                                          |

| Description:     | The contents of register 'f' are<br>incremented. If 'd' is '0', the result<br>is placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |

| IORWF            | Inclusive OR W with f                                                                                                                                                       |  |  |  |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [label] IORWF f,d                                                                                                                                                           |  |  |  |  |  |

| Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d \in [0,1] \end{array}$                                                                                                             |  |  |  |  |  |

| Operation:       | (W) .OR. (f) $\rightarrow$ (destination)                                                                                                                                    |  |  |  |  |  |

| Status Affected: | Z                                                                                                                                                                           |  |  |  |  |  |

| Description:     | Inclusive OR the W register with<br>register 'f'. If 'd' is '0', the result is<br>placed in the W register. If 'd' is<br>'1', the result is placed back in<br>register 'f'. |  |  |  |  |  |

# PIC12F683

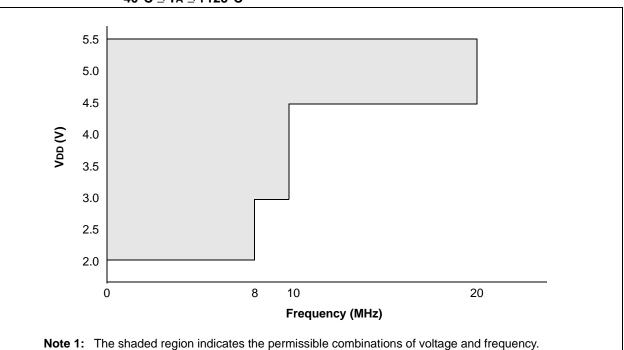

FIGURE 15-1: PIC12F683 VOLTAGE-FREQUENCY GRAPH,  $-40^{\circ}C \le Ta \le +125^{\circ}C$

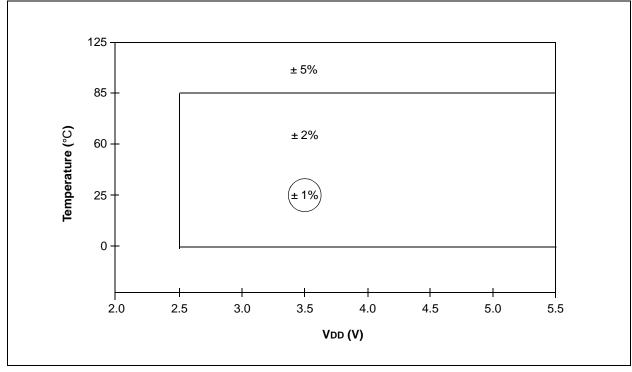

# FIGURE 15-2: HFINTOSC FREQUENCY ACCURACY OVER DEVICE VDD AND TEMPERATURE

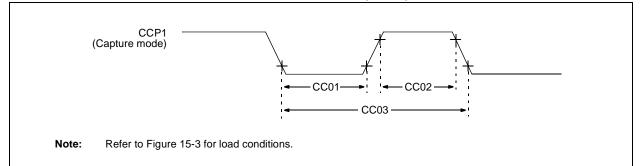

#### FIGURE 15-9: CAPTURE/COMPARE/PWM TIMINGS (ECCP)

### TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)<br>Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                      |                |                       |      |     |       |                                       |

|--------------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|-----------------------|------|-----|-------|---------------------------------------|

| Param<br>No.                                                                                                             | Sym  | Character            | istic          | Min                   | Тур† | Max | Units | Conditions                            |

| CC01*                                                                                                                    | TccL | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20           | —    | _   | ns    |                                       |

|                                                                                                                          |      |                      | With Prescaler | 20                    | _    | _   | ns    |                                       |

| CC02*                                                                                                                    | TccH | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20           | —    | _   | ns    |                                       |

|                                                                                                                          |      |                      | With Prescaler | 20                    | —    | _   | ns    |                                       |

| CC03*                                                                                                                    | TccP | CCP1 Input Period    |                | <u>3Tcy + 40</u><br>N | —    | _   | ns    | N = prescale<br>value (1, 4 or<br>16) |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

NOTES:

# **PIC12F683**

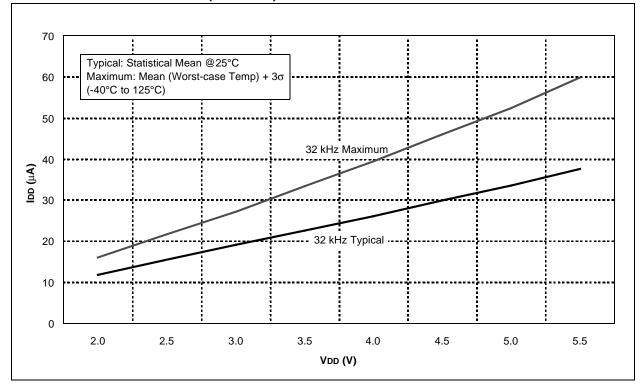

#### FIGURE 16-10: IDD vs. VDD (LP MODE)

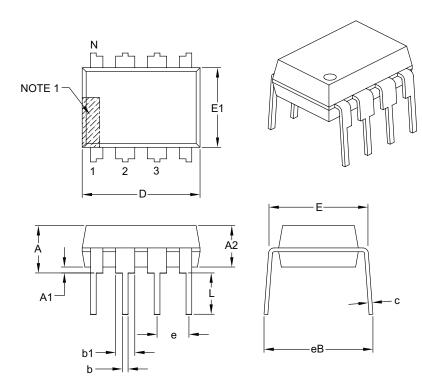

# 17.2 Package Details

The following sections give the technical details of the packages.

# 8-Lead Plastic Dual In-Line (P or PA) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |      |          | INCHES |  |  |  |

|----------------------------|----------|------|----------|--------|--|--|--|

| Dimension                  | n Limits | MIN  | NOM      | MAX    |  |  |  |

| Number of Pins             | Ν        | 8    |          |        |  |  |  |

| Pitch                      | е        |      | .100 BSC |        |  |  |  |

| Top to Seating Plane       | А        | -    | -        | .210   |  |  |  |

| Molded Package Thickness   | A2       | .115 | .130     | .195   |  |  |  |

| Base to Seating Plane      | A1       | .015 | -        | -      |  |  |  |

| Shoulder to Shoulder Width | E        | .290 | .310     | .325   |  |  |  |

| Molded Package Width       | E1       | .240 | .250     | .280   |  |  |  |

| Overall Length             | D        | .348 | .365     | .400   |  |  |  |

| Tip to Seating Plane       | L        | .115 | .130     | .150   |  |  |  |

| Lead Thickness             | С        | .008 | .010     | .015   |  |  |  |

| Upper Lead Width           | b1       | .040 | .060     | .070   |  |  |  |

| Lower Lead Width           | b        | .014 | .018     | .022   |  |  |  |

| Overall Row Spacing §      | eB       | -    | -        | .430   |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located with the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-018B

# APPENDIX A: DATA SHEET REVISION HISTORY

# **Revision A**

This is a new data sheet.

## **Revision B**

Rewrites of the Oscillator and Special Features of the CPU sections. General corrections to Figures and formatting.

# **Revision C**

Revisions throughout document. Incorporated Golden Chapters.

## **Revision D**

Replaced Package Drawings; Revised Product ID Section (SN package to 3.90 mm); Replaced PICmicro with PIC; Replaced Dev Tool Section.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other PIC devices to the PIC12F683 device.

### B.1 PIC16F676 to PIC12F683

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F676     | PIC12F683            |

|---------------------------------------|---------------|----------------------|

| Max Operating<br>Speed                | 20 MHz        | 20 MHz               |

| Max Program<br>Memory (Words)         | 1024          | 2048                 |

| SRAM (bytes)                          | 64            | 128                  |

| A/D Resolution                        | 10-bit        | 10-bit               |

| Data EEPROM<br>(Bytes)                | 128           | 256                  |

| Timers (8/16-bit)                     | 1/1           | 2/1                  |

| Oscillator Modes                      | 8             | 8                    |

| Brown-out Reset                       | Y             | Y                    |

| Internal Pull-ups                     | RA0/1/2/4/5   | GP0/1/2/4/5,<br>MCLR |

| Interrupt-on-change                   | RA0/1/2/3/4/5 | GP0/1/2/3/4/5        |

| Comparator                            | 1             | 1                    |

| ECCP                                  | N             | N                    |

| Ultra Low-Power<br>Wake-Up            | N             | Y                    |

| Extended WDT                          | N             | Y                    |

| Software Control<br>Option of WDT/BOR | N             | Y                    |

| INTOSC                                | 4 MHz         | 32 kHz-              |

| Frequencies                           |               | 8 MHz                |

| Clock Switching                       | Ν             | Y                    |

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.