# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683-e-sn |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

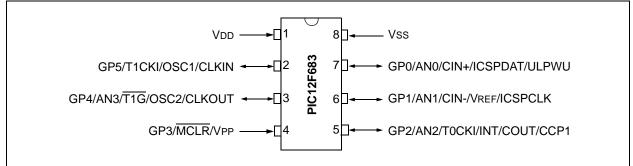

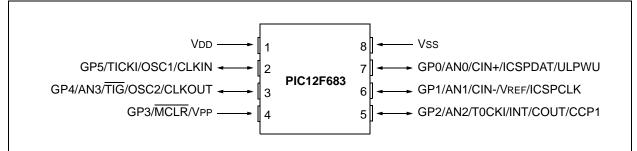

# 8-Pin Diagram (PDIP, SOIC)

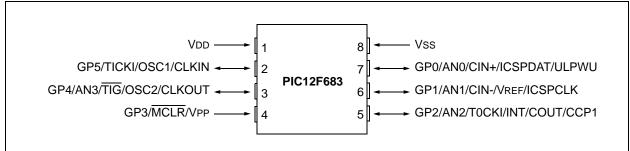

# 8-Pin Diagram (DFN)

## 8-Pin Diagram (DFN-S)

#### TABLE 1: 8-PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР  | Interrupts | Pull-ups | Basic         |

|--------------------|-----|----------|-------------|-------|------|------------|----------|---------------|

| GP0                | 7   | AN0      | CIN+        | _     | _    | IOC        | Y        | ICSPDAT/ULPWU |

| GP1                | 6   | AN1/VREF | CIN-        | —     | _    | IOC        | Y        | ICSPCLK       |

| GP2                | 5   | AN2      | COUT        | T0CKI | CCP1 | INT/IOC    | Y        | —             |

| GP3 <sup>(1)</sup> | 4   |          | —           | _     | _    | IOC        | Y(2)     | MCLR/Vpp      |

| GP4                | 3   | AN3      | —           | T1G   | -    | IOC        | Y        | OSC2/CLKOUT   |

| GP5                | 2   | _        | —           | T1CKI |      | IOC        | Y        | OSC1/CLKIN    |

| _                  | 1   |          | —           |       | _    | —          | —        | Vdd           |

|                    | 8   | _        |             | _     | _    | _          | _        | Vss           |

Note 1: Input only.

**2:** Only when pin is configured for external  $\overline{MCLR}$ .

| Addr | Name               | Bit 7              | Bit 6              | Bit 5         | Bit 4        | Bit 3               | Bit 2          | Bit 1        | Bit 0         | Value on<br>POR, BOR | Page   |

|------|--------------------|--------------------|--------------------|---------------|--------------|---------------------|----------------|--------------|---------------|----------------------|--------|

| Bank | 1                  | _                  |                    |               |              |                     |                |              |               |                      |        |

| 80h  | INDF               | Addressing         | this location      | uses conte    | nts of FSR t | o address da        | ata memory     | (not a physi | cal register) | xxxx xxxx            | 17, 90 |

| 81h  | OPTION_REG         | GPPU               | INTEDG             | TOCS          | T0SE         | PSA                 | PS2            | PS1          | PS0           | 1111 1111            | 12, 90 |

| 82h  | PCL                | Program C          | ounter's (P        | C) Least Si   | gnificant By | te                  |                |              |               | 0000 0000            | 17, 90 |

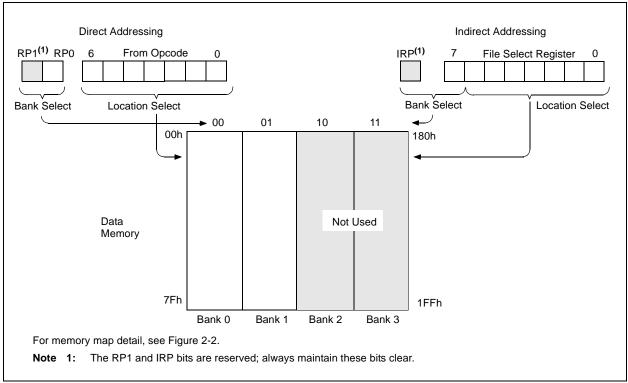

| 83h  | STATUS             | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup> | RP0           | TO           | PD                  | Z              | DC           | С             | 0001 1xxx            | 11, 90 |

| 84h  | FSR                | Indirect Da        | ta Memory          | Address Po    | ointer       |                     |                |              |               | xxxx xxxx            | 17, 90 |

| 85h  | TRISIO             | —                  | _                  | TRISIO5       | TRISIO4      | TRISIO3             | TRISIO2        | TRISIO1      | TRISIO0       | 11 1111              | 32, 90 |

| 86h  | _                  | Unimpleme          | nimplemented -     |               |              |                     |                |              |               |                      |        |

| 87h  | —                  | Unimpleme          | nimplemented       |               |              |                     |                |              |               |                      |        |

| 88h  | _                  | Unimpleme          | nimplemented       |               |              |                     |                |              |               |                      | _      |

| 89h  | _                  | Unimpleme          | ented              |               |              |                     |                |              |               | —                    | _      |

| 8Ah  | PCLATH             | _                  | _                  |               | Write Buffe  | r for upper         | 5 bits of Pro  | ogram Cou    | nter          | 0 0000               | 17, 90 |

| 8Bh  | INTCON             | GIE                | PEIE               | TOIE          | INTE         | GPIE                | TOIF           | INTF         | GPIF          | 0000 0000            | 13, 90 |

| 8Ch  | PIE1               | EEIE               | ADIE               | CCP1IE        | _            | CMIE                | OSFIE          | TMR2IE       | TMR1IE        | 000- 0000            | 14, 90 |

| 8Dh  |                    | Unimplemented      |                    |               |              |                     |                |              | —             |                      |        |

| 8Eh  | PCON               | _                  | _                  | ULPWUE        | SBOREN       | _                   | —              | POR          | BOR           | 01qq                 | 16, 90 |

| 8Fh  | OSCCON             |                    | IRCF2              | IRCF1         | IRCF0        | OSTS <sup>(2)</sup> | HTS            | LTS          | SCS           | -110 x000            | 20, 90 |

| 90h  | OSCTUNE            | —                  | —                  | _             | TUN4         | TUN3                | TUN2           | TUN1         | TUN0          | 0 0000               | 24, 90 |

| 91h  | _                  | Unimpleme          | ented              |               |              |                     |                |              |               | —                    | —      |

| 92h  | PR2                | Timer2 Mo          | dule Period        | Register      |              |                     |                |              |               | 1111 1111            | 49, 90 |

| 93h  | _                  | Unimpleme          | ented              |               |              |                     |                |              |               | —                    |        |

| 94h  | _                  | Unimpleme          | ented              |               |              |                     |                |              |               | —                    |        |

| 95h  | WPU <sup>(3)</sup> | —                  | —                  | WPU5          | WPU4         | _                   | WPU2           | WPU1         | WPU0          | 11 -111              | 34, 90 |

| 96h  | IOC                | —                  | —                  | IOC5          | IOC4         | IOC3                | IOC2           | IOC1         | IOC0          | 00 0000              | 34, 90 |

| 97h  | _                  | Unimpleme          | ented              |               |              |                     |                |              |               | —                    |        |

| 98h  | _                  | Unimpleme          | ented              |               |              |                     |                |              |               | _                    | —      |

| 99h  | VRCON              | VREN               | —                  | VRR           | —            | VR3                 | VR2            | VR1          | VR0           | 0-0- 0000            | 58, 90 |

| 9Ah  | EEDAT              | EEDAT7             | EEDAT6             | EEDAT5        | EEDAT4       | EEDAT3              | EEDAT2         | EEDAT1       | EEDAT0        | 0000 0000            | 71, 90 |

| 9Bh  | EEADR              | EEADR7             | EEADR6             | EEADR5        | EEADR4       | EEADR3              | EEADR2         | EEADR1       | EEADR0        | 0000 0000            | 71, 90 |

| 9Ch  | EECON1             | —                  | _                  | —             | —            | WRERR               | WREN           | WR           | RD            | x000                 | 72, 91 |

| 9Dh  | EECON2             |                    |                    |               | a physical   |                     |                |              |               |                      | 72, 91 |

| 9Eh  | ADRESL             | Least Sign         |                    | s of the left | shifted resu | lt or 8 bits o      | of the right s | shifted resu | lt            | xxxx xxxx            | 66, 91 |

| 9Fh  | ANSEL              | _                  | ADCS2              | ADCS1         | ADCS0        | ANS3                | ANS2           | ANS1         | ANS0          | -000 1111            | 33, 91 |

### TABLE 2-2: PIC12F683 SPECIAL FUNCTION REGISTERS SUMMARY BANK 1

Legend: -= unimplemented locations read as '0', u = unchanged, x = unknown, q = value depends on condition, shaded = unimplemented

**Note 1:** IRP and RP1 bits are reserved, always maintain these bits clear.

2: OSTS bit of the OSCCON register reset to '0' with Dual Speed Start-up and LP, HS or XT selected as the oscillator.

3: GP3 pull-up is enabled when MCLRE is '1' in the Configuration Word register.

### 2.2.2.4 PIE1 Register

The PIE1 register contains the interrupt enable bits, as shown in Register 2-4.

**Note:** Bit PEIE of the INTCON register must be set to enable any peripheral interrupt.

### REGISTER 2-4: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

| R/W-0 | R/W-0 | R/W-0  | U-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0  |

|-------|-------|--------|-----|-------|-------|--------|--------|

| EEIE  | ADIE  | CCP1IE | —   | CMIE  | OSFIE | TMR2IE | TMR1IE |

| bit 7 |       |        |     |       |       |        | bit 0  |

| Legend:    |                      |                                                                                                            |                        |                    |

|------------|----------------------|------------------------------------------------------------------------------------------------------------|------------------------|--------------------|

| R = Reada  | ble bit              | W = Writable bit                                                                                           | U = Unimplemented bit, | read as '0'        |

| -n = Value | at POR               | '1' = Bit is set                                                                                           | '0' = Bit is cleared   | x = Bit is unknown |

| bit 7      | 1 = Enab             | E Write Complete Interrupt En<br>bles the EE write complete int<br>bles the EE write complete int          | errupt                 |                    |

| bit 6      | ADIE: A/<br>1 = Enab | D Converter (ADC) Interrupt<br>bles the ADC interrupt<br>bles the ADC interrupt                            | •                      |                    |

| bit 5      | 1 = Enab             | CCP1 Interrupt Enable bit<br>bles the CCP1 interrupt<br>bles the CCP1 interrupt                            |                        |                    |

| bit 4      | Unimple              | mented: Read as '0'                                                                                        |                        |                    |

| bit 3      | 1 = Enab             | omparator Interrupt Enable bi<br>bles the Comparator 1 interrup<br>bles the Comparator 1 interru           | ot                     |                    |

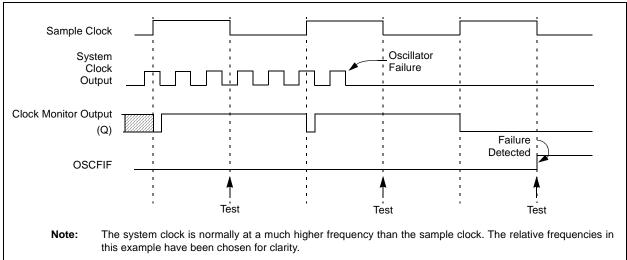

| bit 2      | 1 = Enab             | Dscillator Fail Interrupt Enable<br>les the oscillator fail interrupt<br>bles the oscillator fail interrup |                        |                    |

| bit 1      | 1 = Enab             | Timer2 to PR2 Match Interru<br>les the Timer2 to PR2 match<br>bles the Timer2 to PR2 match                 | interrupt              |                    |

| bit 0      | 1 = Enab             | Timer1 Overflow Interrupt Er<br>les the Timer1 overflow inter<br>bles the Timer1 overflow inter            | rupt                   |                    |

| TABLE 3-2: SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCE | TABLE 3-2: | SUMMARY OF REGISTERS ASSOCIATED WITH CLOCK SOURCES |

|--------------------------------------------------------------|------------|----------------------------------------------------|

|--------------------------------------------------------------|------------|----------------------------------------------------|

| Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets <sup>(1)</sup> |

|-----------------------|-------|-------|--------|-------|-------|-------|--------|--------|----------------------|------------------------------------------------|

| CONFIG <sup>(2)</sup> | CPD   | CP    | MCLRE  | PWRTE | WDTE  | FOSC2 | FOSC1  | FOSC0  | _                    | _                                              |

| INTCON                | GIE   | PEIE  | TOIE   | INTE  | GPIE  | T0IF  | INTF   | GPIF   | 0000 0000            | 0000 000x                                      |

| OSCCON                | _     | IRCF2 | IRCF1  | IRCF0 | OSTS  | HTS   | LTS    | SCS    | -110 x000            | -110 x000                                      |

| OSCTUNE               | _     | _     | —      | TUN4  | TUN3  | TUN2  | TUN1   | TUN0   | 0 0000               | u uuuu                                         |

| PIE1                  | EEIE  | ADIE  | CCP1IE | _     | CMIE  | OSFIE | TMR2IE | TMR1IE | 000- 0000            | 000- 0000                                      |

| PIR1                  | EEIF  | ADIF  | CCP1IF | _     | CMIF  | OSFIF | TMR2IF | TMR1IF | 000- 0000            | 000- 0000                                      |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by oscillators.

Note 1: Other (non Power-up) Resets include MCLR Reset and Watchdog Timer Reset during normal operation.

2: See Configuration Word register (Register 12-1) for operation of all register bits.

# 4.0 GPIO PORT

There are as many as six general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

### 4.1 GPIO and the TRISIO Registers

GPIO is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISIO. Setting a TRISIO bit (= 1) will make the corresponding GPIO pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISIO bit (= 0) will make the corresponding GPIO pin an output (i.e., put the contents of the output latch on the selected pin). An exception is GP3, which is input only and its TRISIO bit will always read as '1'. Example 4-1 shows how to initialize GPIO.

Reading the GPIO register reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. GP3 reads '0' when MCLRE = 1.

The TRISIO register controls the direction of the GPIO pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISIO register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

| Note: | The ANSEL and CMCON0 registers must         |  |  |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|--|--|

|       | be initialized to configure an analog       |  |  |  |  |  |  |  |  |  |  |

|       | channel as a digital input. Pins configured |  |  |  |  |  |  |  |  |  |  |

|       | as analog inputs will read '0'.             |  |  |  |  |  |  |  |  |  |  |

#### EXAMPLE 4-1: INITIALIZING GPIO

| BANKSEL GPIO<br>CLRF GPIO<br>MOVLW 07h<br>MOVWF CMCON0<br>BANKSEL ANSEL<br>CLRF ANSEL<br>MOVLW 0Ch<br>MOVWF TRISIO | ;<br>;Init GPIO<br>;Set GP<2:0> to<br>;digital I/O<br>;<br>;digital I/O<br>;Set GP<3:2> as inputs<br>;and set GP<5:4,1:0><br>;as outputs |

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

|--------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|

#### REGISTER 4-1: GPIO: GENERAL PURPOSE I/O REGISTER

| -n = Value at POR '1' = Bit is set |     |                 |       | '0' = Bit is cleared x = Bit is unknown |                    |       |       |  |  |

|------------------------------------|-----|-----------------|-------|-----------------------------------------|--------------------|-------|-------|--|--|

| R = Readable bit                   | t   | W = Writable bi | t     | U = Unimpleme                           | ented bit, read as | s 'O' |       |  |  |

| Legend:                            |     |                 |       |                                         |                    |       |       |  |  |

|                                    |     |                 |       |                                         |                    |       |       |  |  |

| bit 7                              |     |                 |       | 1                                       |                    |       | bit   |  |  |

|                                    |     | GP5             | GP4   | GP3                                     | GP2                | GP1   | GP0   |  |  |

| U-0                                | U-0 | R/W-x           | R/W-0 | R-x                                     | R/W-0              | R/W-0 | R/W-0 |  |  |

| G | <b>P&lt;5:0&gt;</b> : GPIO I/O Pin b | it |

|---|--------------------------------------|----|

| _ | Deater to the Mark                   |    |

bit 5-0

1 = Port pin is > VIH 0 = Port pin is < VIL

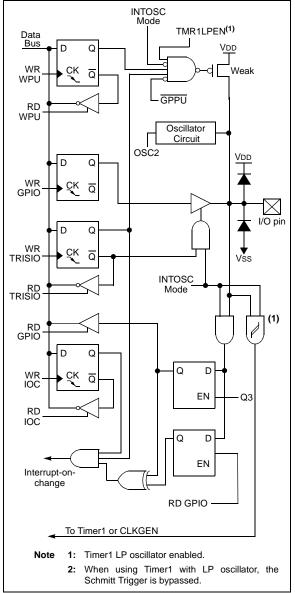

#### 4.2.5.6 GP5/T1CKI/OSC1/CLKIN

Figure 4-6 shows the diagram for this pin. The GP5 pin is configurable to function as one of the following:

- a general purpose I/O

- a Timer1 clock input

- a crystal/resonator connection

- a clock input

#### FIGURE 4-6:

# BLOCK DIAGRAM OF GP5

#### TABLE 4-1: SUMMARY OF REGISTERS ASSOCIATED WITH GPIO

| Name       | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on POR, BOR | Value on<br>all other<br>Resets |

|------------|--------|--------|---------|---------|---------|---------|---------|---------|-------------------|---------------------------------|

| ANSEL      | _      | ADCS2  | ADCS1   | ADCS0   | ANS3    | ANS2    | ANS1    | ANS0    | -000 1111         | -000 1111                       |

| CCP1CON    | _      | _      | DC1B1   | DC1B0   | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 00 0000           | 00 0000                         |

| CMCON0     | _      | COUT   | _       | CINV    | CIS     | CM2     | CM1     | CM0     | -0-0 0000         | -0-0 0000                       |

| PCON       | _      | _      | ULPWUE  | SBOREN  | _       | _       | POR     | BOR     | 01qq              | 0uuu                            |

| INTCON     | GIE    | PEIE   | TOIE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000         | 0000 000x                       |

| IOC        | _      | _      | IOC5    | IOC4    | IOC3    | IOC2    | IOC1    | IOC0    | 00 0000           | 00 0000                         |

| OPTION_REG | GPPU   | INTEDG | TOCS    | T0SE    | PSA     | PS2     | PS1     | PS0     | 1111 1111         | 1111 1111                       |

| GPIO       | _      | _      | GP5     | GP4     | GP3     | GP2     | GP1     | GP0     | xx xxxx           | x0 x000                         |

| T1CON      | T1GINV | TMR1GE | T1CKPS1 | T1CKPS0 | T1OSCEN | T1SYNC  | TMR1CS  | TMR10N  | 0000 0000         | 0000 0000                       |

| TRISIO     | _      | _      | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111           | 11 1111                         |

| WPU        | _      | _      | WPU5    | WPU4    | _       | WPU2    | WPU1    | WPU0    | 11 -111           | 11 -111                         |

Legend: x = unknown, u = unchanged, - = unimplemented locations read as '0'. Shaded cells are not used by GPIO.

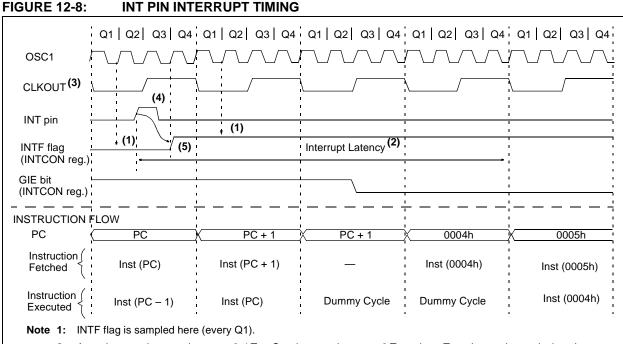

NOTES:

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

4: For minimum width of INT pulse, refer to AC specifications in Section 15.0 "Electrical Specifications".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|--------|-------|-------|-------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | T0IE   | INTE  | GPIE  | T0IF  | INTF   | GPIF   | 0000 0000            | 0000 0000                       |

| IOC    | —     | _     | IOC5   | IOC4  | IOC3  | IOC2  | IOC1   | IOC0   | 00 0000              | 00 0000                         |

| PIR1   | EEIF  | ADIF  | CCP1IF | _     | CMIF  | OSFIF | TMR2IF | TMR1IF | 000- 0000            | 000- 0000                       |

| PIE1   | EEIE  | ADIE  | CCP1IE |       | CMIE  | OSFIE | TMR2IE | TMR1IE | 000- 0000            | 000- 0000                       |

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the interrupt module.

## 12.7 Power-Down Mode (Sleep)

The Power-down mode is entered by executing a SLEEP instruction.

If the Watchdog Timer is enabled:

- WDT will be cleared but keeps running.

- PD bit in the STATUS register is cleared.

- TO bit is set.

- Oscillator driver is turned off.

- I/O ports maintain the status they had before SLEEP was executed (driving high, low or high-impedance).

For lowest current consumption in this mode, all I/O pins should be either at VDD or VSS, with no external circuitry drawing current from the I/O pin and the comparators and CVREF should be disabled. I/O pins that are high-impedance inputs should be pulled high or low externally to avoid switching currents caused by floating inputs. The TOCKI input should also be at VDD or VSs for lowest current consumption. The contribution from on-chip pull-ups on GPIO should be considered.

The MCLR pin must be at a logic high level.

| Note: | It should be noted that a Reset generated |

|-------|-------------------------------------------|

|       | by a WDT time-out does not drive MCLR     |

|       | pin low.                                  |

#### 12.7.1 WAKE-UP FROM SLEEP

The device can wake-up from Sleep through one of the following events:

- 1. External Reset input on MCLR pin.

- 2. Watchdog Timer wake-up (if WDT was enabled).

- 3. Interrupt from GP2/INT pin, GPIO change or a peripheral interrupt.

The first event will cause a device Reset. The two latter events are considered a continuation of program execution. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register can be used to determine the cause of a device Reset. The  $\overline{PD}$  bit, which is set on power-up, is cleared when Sleep is invoked. TO bit is cleared if WDT wake-up occurred.

The following peripheral interrupts can wake the device from Sleep:

- 1. Timer1 interrupt. Timer1 must be operating as an asynchronous counter.

- 2. ECCP Capture mode interrupt.

- 3. A/D conversion (when A/D clock source is FRC).

- 4. EEPROM write operation completion.

- 5. Comparator output changes state.

- 6. Interrupt-on-change.

- 7. External Interrupt from INT pin.

Other peripherals cannot generate interrupts since during Sleep, no on-chip clocks are present.

When the SLEEP instruction is being executed, the next instruction (PC + 1) is prefetched. For the device to wake-up through an interrupt event, the corresponding interrupt enable bit must be set (enabled). Wake-up occurs regardless of the state of the GIE bit. If the GIE bit is clear (disabled), the device continues execution at the instruction after the SLEEP instruction. If the GIE bit is set (enabled), the device executes the instruction after the SLEEP instruction, then branches to the interrupt address (0004h). In cases where the execution of the instruction following SLEEP is not desirable, the user should have a NOP after the SLEEP instruction.

Note: If the global interrupts are disabled (GIE is cleared) and any interrupt source has both its interrupt enable bit and the corresponding interrupt flag bits set, the device will immediately wake-up from Sleep.

The WDT is cleared when the device wakes up from Sleep, regardless of the source of wake-up.

### 12.7.2 WAKE-UP USING INTERRUPTS

When global interrupts are disabled (GIE cleared) and any interrupt source has both its interrupt enable bit and interrupt flag bit set, one of the following will occur:

- If the interrupt occurs before the execution of a SLEEP instruction, the SLEEP instruction will complete as a NOP. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will not be cleared, the TO bit will not be set and the PD bit will not be cleared.

- If the interrupt occurs during or after the execution of a SLEEP instruction, the device will Immediately wake-up from Sleep. The SLEEP instruction is executed. Therefore, the WDT and WDT prescaler and postscaler (if enabled) will be cleared, the TO bit will be set and the PD bit will be cleared.

Even if the flag bits were checked before executing a SLEEP instruction, it may be possible for flag bits to become set before the SLEEP instruction completes. To determine whether a SLEEP instruction executed, test the  $\overline{PD}$  bit. If the  $\overline{PD}$  bit is set, the SLEEP instruction was executed as a NOP.

To ensure that the WDT is cleared, a CLRWDT instruction should be executed before a SLEEP instruction. See Figure 12-10 for more details.

# 14.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers are supported with a full range of hardware and software development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Assemblers/Compilers/Linkers

- MPASM<sup>™</sup> Assembler

- MPLAB C18 and MPLAB C30 C Compilers

- MPLINK<sup>™</sup> Object Linker/

- MPLIB<sup>™</sup> Object Librarian

- MPLAB ASM30 Assembler/Linker/Library

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB ICE 2000 In-Circuit Emulator

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debugger

- MPLAB ICD 2

- Device Programmers

- PICSTART<sup>®</sup> Plus Development Programmer

- MPLAB PM3 Device Programmer

- PICkit<sup>™</sup> 2 Development Programmer

- Low-Cost Demonstration and Development Boards and Evaluation Kits

# 14.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- · A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- · A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Visual device initializer for easy register initialization

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- Extensive on-line help

- Integration of select third party tools, such as HI-TECH Software C Compilers and IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either assembly or C)

- One touch assemble (or compile) and download to PIC MCU emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (assembly or C)

- Mixed assembly and C

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

## 15.4 DC Characteristics: PIC12F683-E (Extended)

| DC CHARACTERISTICS           |                              | Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ for extended |      |      |       |            |                                               |  |  |

|------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|-----------------------------------------------|--|--|

| Param Device Characteristics |                              | Min                                                                                                                               | Typ† | Max  | Units | Conditions |                                               |  |  |

| No.                          | Device Characteristics       |                                                                                                                                   | турт | Max  | Units | Vdd        | Note                                          |  |  |

| D020E                        | Power-down Base              | -                                                                                                                                 | 0.05 | 9    | μΑ    | 2.0        | WDT, BOR, Comparators, VREF and               |  |  |

|                              | Current (IPD) <sup>(2)</sup> | _                                                                                                                                 | 0.15 | 11   | μA    | 3.0        | T1OSC disabled                                |  |  |

|                              |                              |                                                                                                                                   | 0.35 | 15   | μA    | 5.0        |                                               |  |  |

| D021E                        |                              |                                                                                                                                   | 1    | 17.5 | μA    | 2.0        | WDT Current <sup>(1)</sup>                    |  |  |

|                              |                              | _                                                                                                                                 | 2    | 19   | μA    | 3.0        |                                               |  |  |

|                              |                              |                                                                                                                                   | 3    | 22   | μA    | 5.0        |                                               |  |  |

| D022E                        |                              | _                                                                                                                                 | 42   | 65   | μA    | 3.0        | BOR Current <sup>(1)</sup>                    |  |  |

|                              |                              | _                                                                                                                                 | 85   | 127  | μA    | 5.0        |                                               |  |  |

| D023E                        |                              | _                                                                                                                                 | 32   | 45   | μA    | 2.0        | Comparator Current <sup>(1)</sup> , both      |  |  |

|                              |                              | _                                                                                                                                 | 60   | 78   | μA    | 3.0        | comparators enabled                           |  |  |

|                              |                              |                                                                                                                                   | 120  | 160  | μA    | 5.0        |                                               |  |  |

| D024E                        |                              |                                                                                                                                   | 30   | 70   | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |  |  |

|                              |                              |                                                                                                                                   | 45   | 90   | μΑ    | 3.0        |                                               |  |  |

|                              |                              |                                                                                                                                   | 75   | 120  | μΑ    | 5.0        |                                               |  |  |

| D025E*                       |                              | _                                                                                                                                 | 39   | 91   | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |  |  |

|                              |                              |                                                                                                                                   | 59   | 117  | μΑ    | 3.0        |                                               |  |  |

|                              |                              |                                                                                                                                   | 98   | 156  | μΑ    | 5.0        |                                               |  |  |

| D026E                        |                              |                                                                                                                                   | 4.5  | 25   | μΑ    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |  |  |

|                              |                              | _                                                                                                                                 | 5    | 30   | μA    | 3.0        |                                               |  |  |

|                              |                              | —                                                                                                                                 | 6    | 40   | μA    | 5.0        |                                               |  |  |

| D027E                        |                              | _                                                                                                                                 | 0.30 | 12   | μA    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |  |  |

|                              |                              |                                                                                                                                   | 0.36 | 16   | μΑ    | 5.0        | progress                                      |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

2: The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

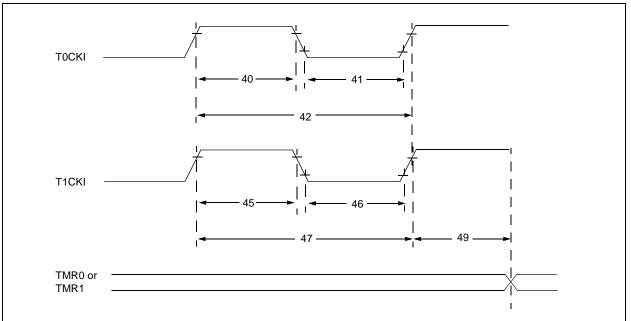

#### TIMER0 AND TIMER1 EXTERNAL CLOCK TIMINGS **FIGURE 15-8:**

#### TABLE 15-5: TIMER0 AND TIMER1 EXTERNAL CLOCK REQUIREMENTS

| Param<br>No. | Sym       |                                                      | Characteristic                                               |                | Min                                       | Тур†   | Max | Units                  | Conditions                         |

|--------------|-----------|------------------------------------------------------|--------------------------------------------------------------|----------------|-------------------------------------------|--------|-----|------------------------|------------------------------------|

| 40*          | Тт0Н      | T0CKI High Pulse Width No Prescaler                  |                                                              |                | 0.5 Tcy + 20                              | —      | _   | ns                     |                                    |

|              |           | With Pres                                            |                                                              | With Prescaler | 10                                        | —      | _   | ns                     |                                    |

| 41* TTOL     |           | T0CKI Low Pulse Width No Prescaler<br>With Prescaler |                                                              | 0.5 TCY + 20   | —                                         | _      | ns  |                        |                                    |

|              |           |                                                      |                                                              | 10             | —                                         | _      | ns  |                        |                                    |

| 42*          | Тт0Р      | T0CKI Period                                         | 1                                                            |                | Greater of:<br>20 or <u>Tcy + 40</u><br>N | —      | _   | ns                     | N = prescale value<br>(2, 4,, 256) |

| 45* T        | T⊤1H      | T1CKI High<br>Time                                   | Synchronous, No Prescaler                                    |                | 0.5 TCY + 20                              | —      | _   | ns                     |                                    |

|              |           |                                                      | Synchronous,<br>with Prescaler                               |                | 15                                        | —      | _   | ns                     |                                    |

|              |           |                                                      | Asynchronous                                                 |                | 30                                        | —      | _   | ns                     |                                    |

| 46*          | T⊤1L      | T1CKI Low<br>Time                                    | Synchronous, No Prescaler                                    |                | 0.5 TCY + 20                              | —      | _   | ns                     |                                    |

|              |           |                                                      | Synchronous,<br>with Prescaler                               |                | 15                                        | —      | _   | ns                     |                                    |

|              |           |                                                      | Asynchronous                                                 |                | 30                                        | —      | _   | ns                     |                                    |

| 47*          | TT1P      | T1CKI Input<br>Period                                | Synchronous                                                  |                | Greater of:<br>30 or <u>Tcy + 40</u><br>N | —      | _   | ns                     | N = prescale value<br>(1, 2, 4, 8) |

|              |           |                                                      | Asynchronous                                                 |                | 60                                        |        |     | ns                     |                                    |

| 48           | F⊤1       |                                                      | lator Input Frequency Range<br>abled by setting bit T1OSCEN) |                | _                                         | 32.768 | _   | kHz                    |                                    |

| 49*          | TCKEZTMR1 | Delay from E<br>Increment                            | xternal Clock E                                              | 2 Tosc         | —                                         | 7 Tosc | —   | Timers in Sync<br>mode |                                    |

Standard Operating Conditions (unless otherwise stated)

These parameters are characterized but not tested.

t Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 15-9: PIC12F683 A/D CONVERTER (ADC) CHARACTERISTICS

| Standard Operating Conditions (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |      |                                                      |            |      |         |       |                                                                     |  |  |

|----------------------------------------------------------------------------------------------------------------------|------|------------------------------------------------------|------------|------|---------|-------|---------------------------------------------------------------------|--|--|

| Param<br>No.                                                                                                         | Sym  | Characteristic                                       | Min        | Тур† | Мах     | Units | Conditions                                                          |  |  |

| AD01                                                                                                                 | NR   | Resolution                                           | —          | _    | 10 bits | bit   |                                                                     |  |  |

| AD02                                                                                                                 | E⊫   | Integral Error                                       | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |  |  |

| AD03                                                                                                                 | Edl  | Differential Error                                   | _          | —    | ±1      | LSb   | No missing codes to 10 bits<br>VREF = 5.12V                         |  |  |

| AD04                                                                                                                 | EOFF | Offset Error                                         | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |  |  |

| AD07                                                                                                                 | Egn  | Gain Error                                           | —          | _    | ±1      | LSb   | VREF = 5.12V                                                        |  |  |

| AD06<br>AD06A                                                                                                        | Vref | Reference Voltage <sup>(3)</sup>                     | 2.2<br>2.7 | _    | <br>Vdd | V     | Absolute minimum to ensure 1 LSb accuracy                           |  |  |

| AD07                                                                                                                 | VAIN | Full-Scale Range                                     | Vss        | _    | VREF    | V     |                                                                     |  |  |

| AD08                                                                                                                 | ZAIN | Recommended<br>Impedance of Analog<br>Voltage Source | —          | _    | 10      | kΩ    |                                                                     |  |  |

| AD09*                                                                                                                | IREF | VREF Input Current <sup>(3)</sup>                    | 10         | —    | 1000    | μA    | During VAIN acquisition.<br>Based on differential of VHOLD to VAIN. |  |  |

|                                                                                                                      |      |                                                      | _          | _    | 50      | μΑ    | During A/D conversion cycle.                                        |  |  |

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

**Note 1:** Total Absolute Error includes integral, differential, offset and gain errors.

2: The A/D conversion result never decreases with an increase in the input voltage and has no missing codes.

3: ADC VREF is from external VREF or VDD pin, whichever is selected as reference input.

4: When ADC is off, it will not consume any current other than leakage current. The power-down current specification includes any such leakage from the ADC module.

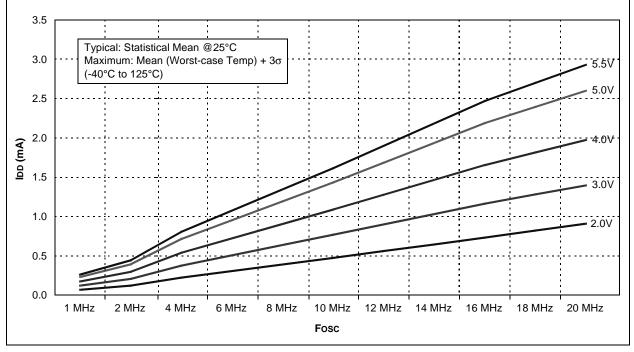

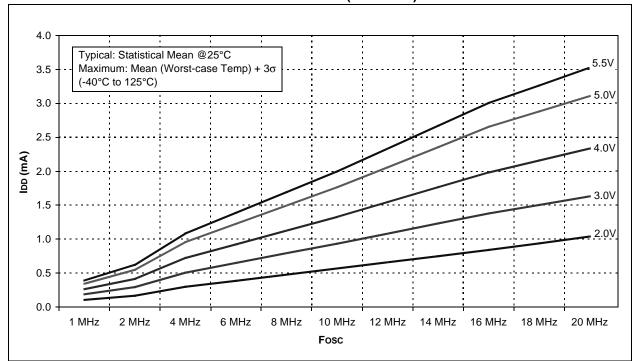

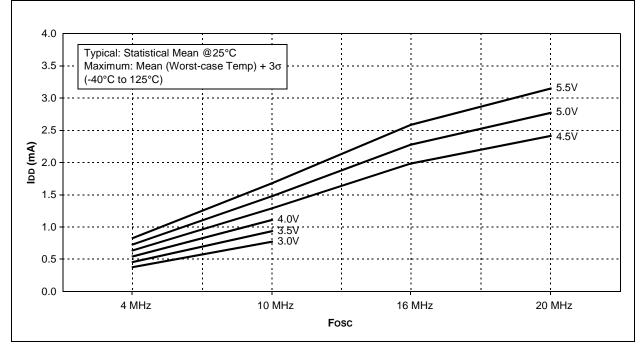

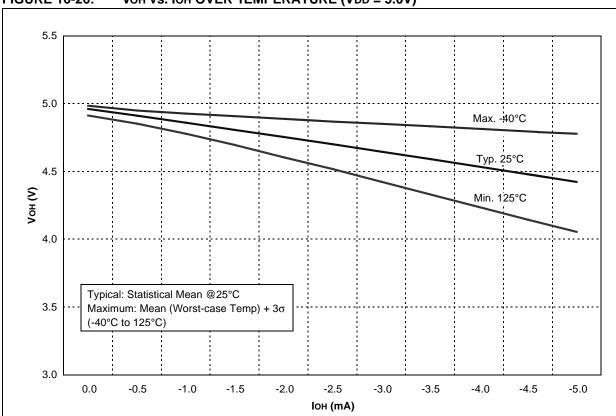

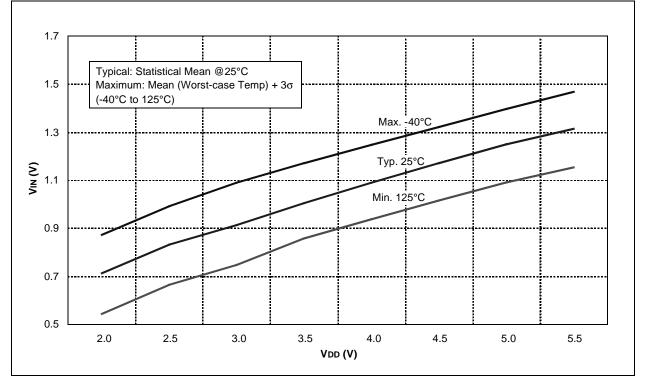

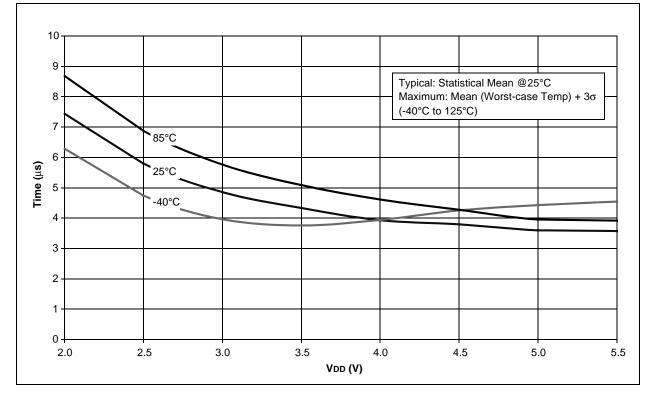

# 16.0 DC AND AC CHARACTERISTICS GRAPHS AND TABLES

The graphs and tables provided in this section are for design guidance and are not tested.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "Maximum" or "minimum" represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

FIGURE 16-27: TTL INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

FIGURE 16-36: MINIMUM HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

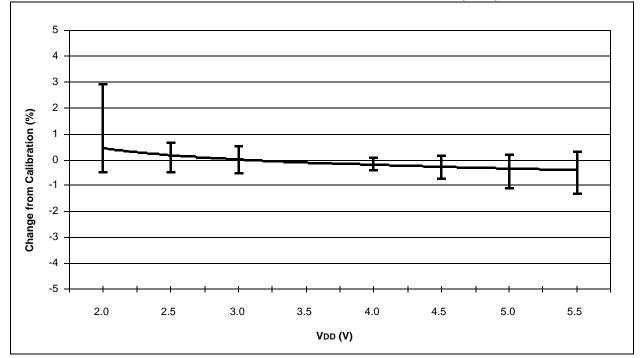

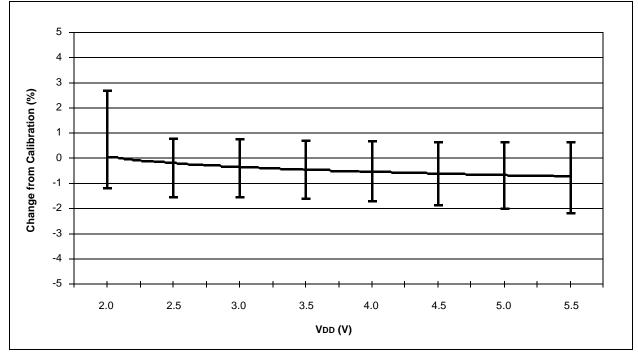

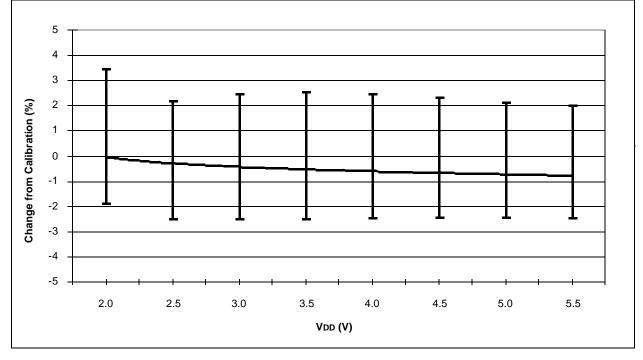

FIGURE 16-37: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

# APPENDIX A: DATA SHEET REVISION HISTORY

## **Revision A**

This is a new data sheet.

### **Revision B**

Rewrites of the Oscillator and Special Features of the CPU sections. General corrections to Figures and formatting.

## **Revision C**

Revisions throughout document. Incorporated Golden Chapters.

### **Revision D**

Replaced Package Drawings; Revised Product ID Section (SN package to 3.90 mm); Replaced PICmicro with PIC; Replaced Dev Tool Section.

# APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other PIC devices to the PIC12F683 device.

#### B.1 PIC16F676 to PIC12F683

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F676     | PIC12F683            |

|---------------------------------------|---------------|----------------------|

| Max Operating<br>Speed                | 20 MHz        | 20 MHz               |

| Max Program<br>Memory (Words)         | 1024          | 2048                 |

| SRAM (bytes)                          | 64            | 128                  |

| A/D Resolution                        | 10-bit        | 10-bit               |

| Data EEPROM<br>(Bytes)                | 128           | 256                  |

| Timers (8/16-bit)                     | 1/1           | 2/1                  |

| Oscillator Modes                      | 8             | 8                    |

| Brown-out Reset                       | Y             | Y                    |

| Internal Pull-ups                     | RA0/1/2/4/5   | GP0/1/2/4/5,<br>MCLR |

| Interrupt-on-change                   | RA0/1/2/3/4/5 | GP0/1/2/3/4/5        |

| Comparator                            | 1             | 1                    |

| ECCP                                  | N             | N                    |

| Ultra Low-Power<br>Wake-Up            | N             | Y                    |

| Extended WDT                          | N             | Y                    |

| Software Control<br>Option of WDT/BOR | N             | Y                    |

| INTOSC                                | 4 MHz         | 32 kHz-              |

| Frequencies                           |               | 8 MHz                |

| Clock Switching                       | Ν             | Y                    |

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.