Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                          |

|----------------------------|--------------------------------------------------------------------------|

| Product Status             | Active                                                                   |

| Core Processor             | PIC                                                                      |

| Core Size                  | 8-Bit                                                                    |

| Speed                      | 20MHz                                                                    |

| Connectivity               | -                                                                        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                    |

| Number of I/O              | 5                                                                        |

| Program Memory Size        | 3.5KB (2K x 14)                                                          |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 256 x 8                                                                  |

| RAM Size                   | 128 x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                |

| Data Converters            | A/D 4x10b                                                                |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                        |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                            |

| Supplier Device Package    | 8-SOIC                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683-i-sn |

#### 4.0 GPIO PORT

There are as many as six general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

### 4.1 GPIO and the TRISIO Registers

GPIO is a 6-bit wide, bidirectional port. The corresponding data direction register is TRISIO. Setting a TRISIO bit (= 1) will make the corresponding GPIO pin an input (i.e., put the corresponding output driver in a High-Impedance mode). Clearing a TRISIO bit (= 0) will make the corresponding GPIO pin an output (i.e., put the contents of the output latch on the selected pin). An exception is GP3, which is input only and its TRISIO bit will always read as '1'. Example 4-1 shows how to initialize GPIO.

Reading the GPIO register reads the status of the pins, whereas writing to it will write to the PORT latch. All write operations are read-modify-write operations.

Therefore, a write to a port implies that the port pins are read, this value is modified and then written to the PORT data latch. GP3 reads '0' when MCLRE = 1.

The TRISIO register controls the direction of the GPIO pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISIO register are maintained set when using them as analog inputs. I/O pins configured as analog input always read '0'.

**Note:** The ANSEL and CMCON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0'.

#### **EXAMPLE 4-1: INITIALIZING GPIO**

| п |         |        |                        |

|---|---------|--------|------------------------|

|   | BANKSEL | GPIO   | ;                      |

|   | CLRF    | GPIO   | ;Init GPIO             |

|   | MOVLW   | 07h    | ;Set GP<2:0> to        |

|   | MOVWF   | CMCON0 | digital I/0;           |

|   | BANKSEL | ANSEL  | ;                      |

|   | CLRF    | ANSEL  | ;digital I/O           |

|   | MOVLW   | 0Ch    | ;Set GP<3:2> as inputs |

|   | MOVWF   | TRISIO | ;and set GP<5:4,1:0>   |

|   |         |        | ;as outputs            |

| ı |         |        |                        |

#### REGISTER 4-1: GPIO: GENERAL PURPOSE I/O REGISTER

| U-0   | U-0 | R/W-x | R/W-0 | R-x | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-----|-------|-------|-------|

| _     | _   | GP5   | GP4   | GP3 | GP2   | GP1   | GP0   |

| bit 7 |     |       |       |     |       |       | bit 0 |

| Legend:           |                  |                                |                    |

|-------------------|------------------|--------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as | '0'                |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared           | x = Bit is unknown |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 GP<5:0>: GPIO I/O Pin bit

1 = Port pin is > VIH

0 = Port pin is < VIL

#### 4.2.5.2 GP1/AN1/CIN-/VREF/ICSPCLK

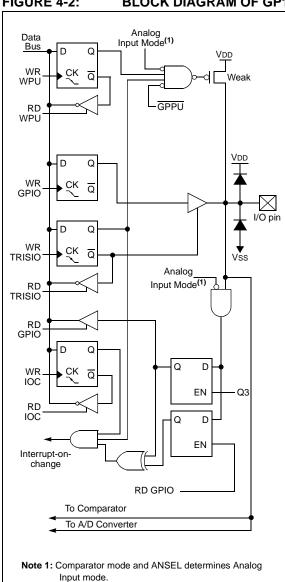

Figure 4-2 shows the diagram for this pin. The GP1 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a analog input to the comparator

- · a voltage reference input for the ADC

- In-Circuit Serial Programming clock

#### FIGURE 4-2: **BLOCK DIAGRAM OF GP1**

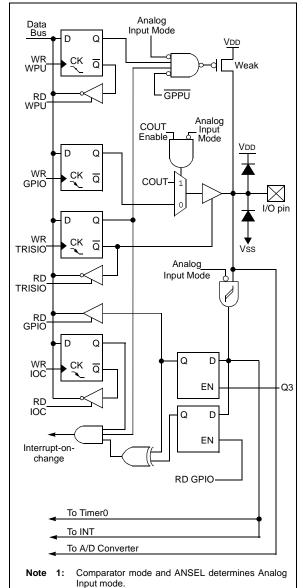

#### 4.2.5.3 GP2/AN2/T0CKI/INT/COUT/CCP1

Figure 4-3 shows the diagram for this pin. The GP2 pin is configurable to function as one of the following:

- · a general purpose I/O

- an analog input for the ADC

- the clock input for Timer0

- an external edge triggered interrupt

- a digital output from the Comparator

- a digital input/output for the CCP (refer to Section 11.0 "Capture/Compare/PWM (CCP) Module").

#### FIGURE 4-3: **BLOCK DIAGRAM OF GP2**

### 8.3 Comparator Configuration

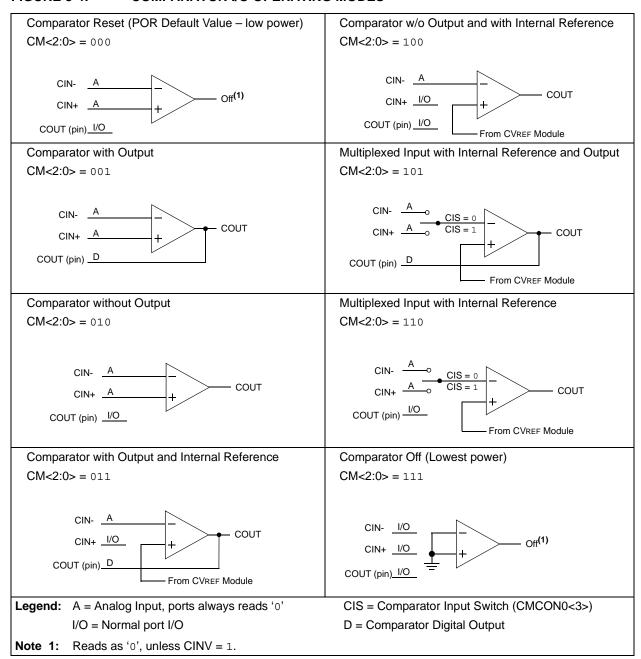

There are eight modes of operation for the comparator. The CM<2:0> bits of the CMCON0 register are used to select these modes as shown in Figure 8-4.

- Analog function (A): digital input buffer is disabled

- Digital function (D): comparator digital output, overrides port function

- Normal port function (I/O): independent of comparator

The port pins denoted as "A" will read as a '0' regardless of the state of the I/O pin or the I/O control TRIS bit. Pins used as analog inputs should also have the corresponding TRIS bit set to '1' to disable the digital output driver. Pins denoted as "D" should have the corresponding TRIS bit set to '0' to enable the digital output driver.

**Note:** Comparator interrupts should be disabled during a Comparator mode change to prevent unintended interrupts.

#### FIGURE 8-4: COMPARATOR I/O OPERATING MODES

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

| Name   | Bit 7                              | Bit 6 | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1     | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|------------------------------------|-------|---------|---------|---------|---------|-----------|-----------|----------------------|---------------------------------|

| ADCON0 | ADFM                               | VCFG  | _       | _       | CHS1    | CHS0    | GO/DONE   | ADON      | 00 0000              | 0000 0000                       |

| ANSEL  | _                                  | ADCS2 | ADCS1   | ADCS0   | ANS3    | ANS2    | ANS1      | ANS0      | -000 1111            | -000 1111                       |

| ADRESH | A/D Result Register High Byte xxxx |       |         |         |         |         | xxxx xxxx | uuuu uuuu |                      |                                 |

| ADRESL | A/D Result Register Low Byte       |       |         |         |         |         | xxxx xxxx | uuuu uuuu |                      |                                 |

| INTCON | GIE                                | PEIE  | TOIE    | INTE    | GPIE    | TOIF    | INTF      | GPIF      | 0000 0000            | 0000 000x                       |

| PIE1   | EEIE                               | ADIE  | CCP1IE  | _       | CMIE    | OSFIE   | TMR2IE    | TMR1IE    | 000- 0000            | 0000 0000                       |

| PIR1   | EEIF                               | ADIF  | CCP1IF  | _       | CMIF    | OSFIF   | TMR2IF    | TMR1IF    | 000- 0000            | 000- 0000                       |

| GPIO   | _                                  | _     | GP5     | GP4     | GP3     | GP2     | GP1       | GP0       | xx xxxx              | uu uuuu                         |

| TRISIO | _                                  | _     | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1   | TRISIO0   | 11 1111              | 11 1111                         |

$\textbf{Legend:} \quad x = \text{unknown, } u = \text{unchanged,} - = \text{unimplemented read as '0'}. \text{ Shaded cells are not used for ADC module.}$

## 12.0 SPECIAL FEATURES OF THE CPU

The PIC12F683 has a host of features intended to maximize system reliability, minimize cost through elimination of external components, provide power saving features and offer code protection.

These features are:

- Reset

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR)

- Interrupts

- Watchdog Timer (WDT)

- · Oscillator Selection

- Sleep

- Code Protection

- ID Locations

- In-Circuit Serial Programming™

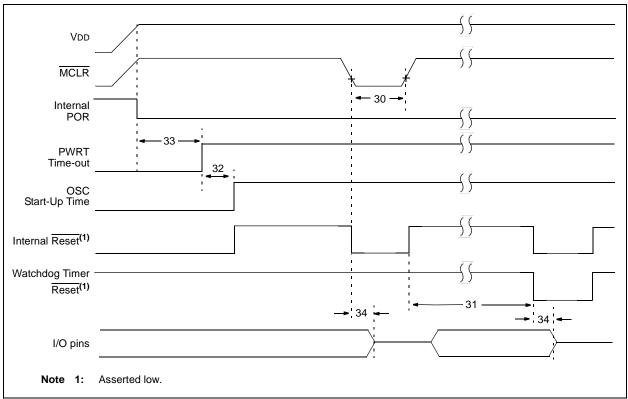

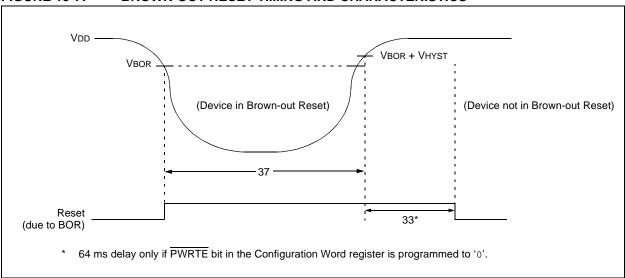

The PIC12F683 has two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in Reset until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 64 ms (nominal) on power-up only, designed to keep the part in Reset while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can use the Power-up Timer to provide at least a 64 ms Reset. With these three functions on-chip, most applications need no external Reset circuitry.

The Sleep mode is designed to offer a very low-current Power-down mode. The user can wake-up from Sleep through:

- External Reset

- · Watchdog Timer Wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power. A set of Configuration bits are used to select various options (see Register 12-1).

Note: Address 2007h is beyond the user program memory space. It belongs to the special configuration memory space (2000h-3FFFh), which can be accessed only during programming. See "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information.

### 12.1 Configuration Bits

The Configuration bits can be programmed (read as '0'), or left unprogrammed (read as '1') to select various device configurations as shown in Register 12-1. These bits are mapped in program memory location 2007h.

## PIC12F683

| MOVF             | Move f                                                                                                                                                                                                                                                    |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVF f,d                                                                                                                                                                                                                                        |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                                                        |

| Operation:       | $(f) \to (dest)$                                                                                                                                                                                                                                          |

| Status Affected: | Z                                                                                                                                                                                                                                                         |

| Description:     | The contents of register f is moved to a destination dependent upon the status of d. If $d=0$ , destination is W register. If $d=1$ , the destination is file register f itself. $d=1$ is useful to test a file register since status flag Z is affected. |

| Words:           | 1                                                                                                                                                                                                                                                         |

| Cycles:          | 1                                                                                                                                                                                                                                                         |

| Example:         | MOVF FSR, 0                                                                                                                                                                                                                                               |

|                  | After Instruction  W = value in FSR  register  Z = 1                                                                                                                                                                                                      |

| Syntax:          | [ label ] MOVWF f                          |

|------------------|--------------------------------------------|

| Operands:        | 0 ≤ f ≤ 127                                |

| Operation:       | $(W) \rightarrow (f)$                      |

| Status Affected: | None                                       |

| Description:     | Move data from W register to register 'f'. |

| Words:           | 1                                          |

| Cycles:          | 1                                          |

| Example:         | MOVW OPTION<br>F                           |

|                  | Before Instruction                         |

|                  | OPTION = 0xFF                              |

|                  | W = 0x4F                                   |

|                  | After Instruction  OPTION = 0x4F           |

|                  | W = 0x4F                                   |

| MOVLW            | Move literal to W                                                                             |

|------------------|-----------------------------------------------------------------------------------------------|

| Syntax:          | [ label ] MOVLW k                                                                             |

| Operands:        | $0 \le k \le 255$                                                                             |

| Operation:       | $k \rightarrow (W)$                                                                           |

| Status Affected: | None                                                                                          |

| Description:     | The eight-bit literal 'k' is loaded into W register. The "don't cares" will assemble as '0's. |

| Words:           | 1                                                                                             |

| Cycles:          | 1                                                                                             |

| Example:         | MOVLW 0x5A                                                                                    |

|                  | After Instruction W = 0x5A                                                                    |

| NOP              | No Operation  |

|------------------|---------------|

| Syntax:          | [label] NOP   |

| Operands:        | None          |

| Operation:       | No operation  |

| Status Affected: | None          |

| Description:     | No operation. |

| Words:           | 1             |

| Cycles:          | 1             |

| Example:         | NOP           |

|                  |               |

|                  |               |

| RETFIE           | Return from Interrupt                                                                                                                                                                                                |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETFIE                                                                                                                                                                                                       |

| Operands:        | None                                                                                                                                                                                                                 |

| Operation:       | $\begin{array}{l} TOS \to PC, \\ 1 \to GIE \end{array}$                                                                                                                                                              |

| Status Affected: | None                                                                                                                                                                                                                 |

| Description:     | Return from Interrupt. Stack is<br>POPed and Top-of-Stack (TOS) is<br>loaded in the PC. Interrupts are<br>enabled by setting Global<br>Interrupt Enable bit, GIE<br>(INTCON<7>). This is a two-cycle<br>instruction. |

| Words:           | 1                                                                                                                                                                                                                    |

| Cycles:          | 2                                                                                                                                                                                                                    |

| Example:         | RETFIE                                                                                                                                                                                                               |

|                  | After Interrupt  PC = TOS  GIE = 1                                                                                                                                                                                   |

| RETLW            | Return with literal in W                                                                                                                                                |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] RETLW k                                                                                                                                                         |

| Operands:        | $0 \le k \le 255$                                                                                                                                                       |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                            |

| Status Affected: | None                                                                                                                                                                    |

| Description:     | The W register is loaded with the eight bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a two-cycle instruction. |

| Words:           | 1                                                                                                                                                                       |

| Cycles:          | 2                                                                                                                                                                       |

| Example:         | CALL TABLE;W contains table ;offset value                                                                                                                               |

| TABLE            | <pre>* ;W now has table value  ADDWF PC ;W = offset RETLW k1 ;Begin table RETLW k2 ;  RETLW k1 ; End of table</pre>                                                     |

|                  | Before Instruction  W = 0x07  After Instruction  W = value of k8                                                                                                        |

#### **RETURN Return from Subroutine** Syntax: [label] RETURN Operands: None $\mathsf{TOS} \to \mathsf{PC}$ Operation: Status Affected: None Description: Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a two-cycle instruction.

| RLF              | Rotate Left f through Carry                                                                                                                                                                           |  |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Syntax:          | [ label ] RLF f,d                                                                                                                                                                                     |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                    |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                 |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                     |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the left through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is stored back in register 'f'. |  |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                     |  |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                     |  |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                            |  |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                    |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                      |  |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                 |  |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                     |  |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                      |  |  |  |  |  |

|                  | $W = 1100 \ 1100$<br>C = 1                                                                                                                                                                            |  |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                 |  |  |  |  |  |

| SLEEP            | Enter Sleep mode                                                                                                                                                                                                                           |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Syntax:          | [label] SLEEP                                                                                                                                                                                                                              |

| Operands:        | None                                                                                                                                                                                                                                       |

| Operation:       | $\begin{array}{l} \text{00h} \rightarrow \text{WDT,} \\ \text{0} \rightarrow \underline{\text{WDT}} \text{ prescaler,} \\ \text{1} \rightarrow \overline{\underline{\text{TO}}}, \\ \text{0} \rightarrow \overline{\text{PD}} \end{array}$ |

| Status Affected: | TO, PD                                                                                                                                                                                                                                     |

| Description:     | The power-down Status bit, PD is cleared. Time-out Status bit, TO is set. Watchdog Timer and its prescaler are cleared. The processor is put into Sleep mode with the oscillator stopped.                                                  |

|                  |                                                                                                                                                                                                                                            |

| RRF              | Rotate Right f through Carry                                                                                                                                                                           |  |  |  |  |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Syntax:          | [ label ] RRF f,d                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                     |  |  |  |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                  |  |  |  |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                      |  |  |  |  |  |  |  |

| Description:     | The contents of register 'f' are rotated one bit to the right through the Carry flag. If 'd' is '0', the result is placed in the W register. If 'd' is '1', the result is placed back in register 'f'. |  |  |  |  |  |  |  |

|                  | C Register f                                                                                                                                                                                           |  |  |  |  |  |  |  |

| SUBLW            | Subtract W from literal                                                                                                      |                 |  |  |  |  |

|------------------|------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|--|--|

| Syntax:          | [ label ] SUBLW k                                                                                                            |                 |  |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                            |                 |  |  |  |  |

| Operation:       | $k - (W) \rightarrow (W)$                                                                                                    |                 |  |  |  |  |

| Status Affected: | C, DC, Z                                                                                                                     |                 |  |  |  |  |

| Description:     | The W register is subtracted (2's complement method) from the eight-bit literal 'k'. The result is placed in the W register. |                 |  |  |  |  |

|                  | <b>C</b> = 0                                                                                                                 | W > k           |  |  |  |  |

|                  | C = 1                                                                                                                        | $W \le k$       |  |  |  |  |

|                  | <b>DC</b> = 0                                                                                                                | W<3:0> > k<3:0> |  |  |  |  |

|                  | DC = 1                                                                                                                       | W<3:0> ≤ k<3:0> |  |  |  |  |

# 15.1 DC Characteristics: PIC12F683-I (Industrial) PIC12F683-E (Extended)

| DC CHARACTERISTICS     |      |                                                                  | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |             |                          |             |                                                                                  |

|------------------------|------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------------------------|-------------|----------------------------------------------------------------------------------|

| Param<br>No.           | Sym  | Characteristic                                                   | Min                                                                                                                                                                                                                                | Тур†        | Max                      | Units       | Conditions                                                                       |

| D001<br>D001C<br>D001D | VDD  | Supply Voltage                                                   | 2.0<br>2.0<br>3.0<br>4.5                                                                                                                                                                                                           | _<br>_<br>_ | 5.5<br>5.5<br>5.5<br>5.5 | V<br>V<br>V | FOSC <= 8 MHz: HFINTOSC, EC<br>FOSC <= 4 MHz<br>FOSC <= 10 MHz<br>FOSC <= 20 MHz |

| D002*                  | VDR  | RAM Data Retention Voltage <sup>(1)</sup>                        | 1.5                                                                                                                                                                                                                                | _           | _                        | V           | Device in Sleep mode                                                             |

| D003                   | VPOR | VDD Start Voltage to<br>ensure internal Power-on<br>Reset signal | _                                                                                                                                                                                                                                  | Vss         | _                        | V           | See Section 12.3.1 "Power-on Reset" for details.                                 |

| D004*                  | SVDD | VDD Rise Rate to ensure internal Power-on Reset signal           | 0.05                                                                                                                                                                                                                               | _           | _                        | V/ms        | See Section 12.3.1 "Power-on Reset" for details.                                 |

<sup>\*</sup> These parameters are characterized but not tested.

**Note 1:** This is the limit to which VDD can be lowered in Sleep mode without losing RAM data.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

### 15.4 DC Characteristics: PIC12F683-E (Extended)

| DC CHA                       | Standard Operating Conditions (unless otherwise stated) Operating temperature -40°C ≤ TA ≤ +125°C for extended |     |      |      |       |            |                                               |

|------------------------------|----------------------------------------------------------------------------------------------------------------|-----|------|------|-------|------------|-----------------------------------------------|

| Param Device Characteristics |                                                                                                                | N   |      |      |       | Conditions |                                               |

| No.                          | Device Characteristics                                                                                         | Min | Тур† | Max  | Units | VDD        | Note                                          |

| D020E                        | Power-down Base                                                                                                | _   | 0.05 | 9    | μΑ    | 2.0        | WDT, BOR, Comparators, VREF and               |

|                              | Current (IPD) <sup>(2)</sup>                                                                                   | _   | 0.15 | 11   | μΑ    | 3.0        | T1OSC disabled                                |

|                              |                                                                                                                | _   | 0.35 | 15   | μΑ    | 5.0        |                                               |

| D021E                        |                                                                                                                | _   | 1    | 17.5 | μΑ    | 2.0        | WDT Current <sup>(1)</sup>                    |

|                              |                                                                                                                | _   | 2    | 19   | μΑ    | 3.0        |                                               |

|                              |                                                                                                                | _   | 3    | 22   | μΑ    | 5.0        |                                               |

| D022E                        |                                                                                                                | _   | 42   | 65   | μΑ    | 3.0        | BOR Current <sup>(1)</sup>                    |

|                              |                                                                                                                | _   | 85   | 127  | μΑ    | 5.0        |                                               |

| D023E                        |                                                                                                                | _   | 32   | 45   | μΑ    | 2.0        | Comparator Current <sup>(1)</sup> , both      |

|                              |                                                                                                                | _   | 60   | 78   | μΑ    | 3.0        | comparators enabled                           |

|                              |                                                                                                                | _   | 120  | 160  | μΑ    | 5.0        |                                               |

| D024E                        |                                                                                                                | _   | 30   | 70   | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (high range)     |

|                              |                                                                                                                | _   | 45   | 90   | μΑ    | 3.0        |                                               |

|                              |                                                                                                                | _   | 75   | 120  | μΑ    | 5.0        |                                               |

| D025E*                       |                                                                                                                | _   | 39   | 91   | μΑ    | 2.0        | CVREF Current <sup>(1)</sup> (low range)      |

|                              |                                                                                                                | _   | 59   | 117  | μΑ    | 3.0        |                                               |

|                              |                                                                                                                | _   | 98   | 156  | μΑ    | 5.0        |                                               |

| D026E                        |                                                                                                                | _   | 4.5  | 25   | μΑ    | 2.0        | T1OSC Current <sup>(1)</sup> , 32.768 kHz     |

|                              |                                                                                                                | _   | 5    | 30   | μΑ    | 3.0        |                                               |

|                              |                                                                                                                | _   | 6    | 40   | μΑ    | 5.0        |                                               |

| D027E                        |                                                                                                                | _   | 0.30 | 12   | μΑ    | 3.0        | A/D Current <sup>(1)</sup> , no conversion in |

|                              |                                                                                                                | _   | 0.36 | 16   | μΑ    | 5.0        | progress                                      |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

Note 1: The peripheral current is the sum of the base IDD or IPD and the additional current consumed when this peripheral is enabled. The peripheral  $\Delta$  current can be determined by subtracting the base IDD or IPD current from this limit. Max values should be used when calculating total current consumption.

<sup>2:</sup> The power-down current in Sleep mode does not depend on the oscillator type. Power-down current is measured with the part in Sleep mode, with all I/O pins in high-impedance state and tied to VDD.

FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

FIGURE 15-7: BROWN-OUT RESET TIMING AND CHARACTERISTICS

## PIC12F683

NOTES:

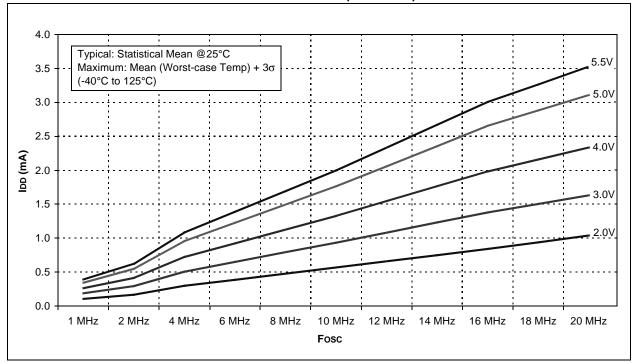

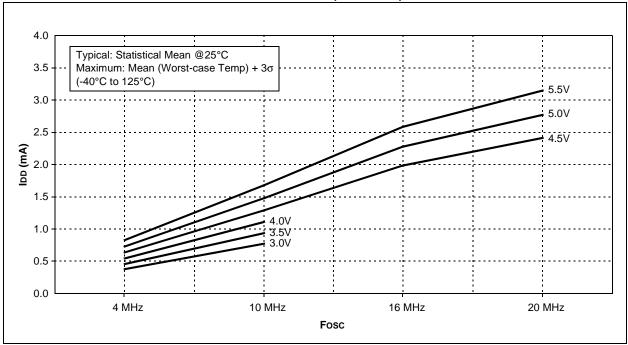

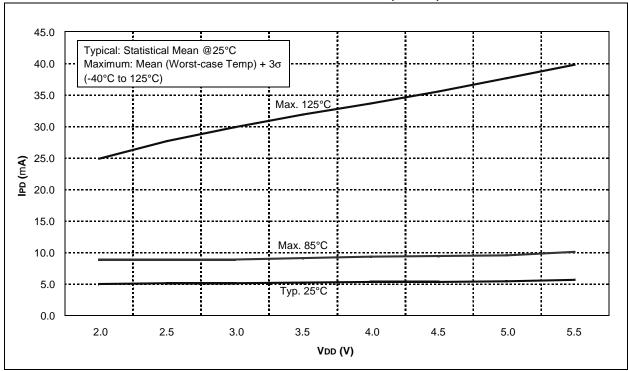

FIGURE 16-2: MAXIMUM IDD vs. Fosc OVER VDD (EC MODE)

FIGURE 16-3: TYPICAL IDD vs. FOSC OVER VDD (HS MODE)

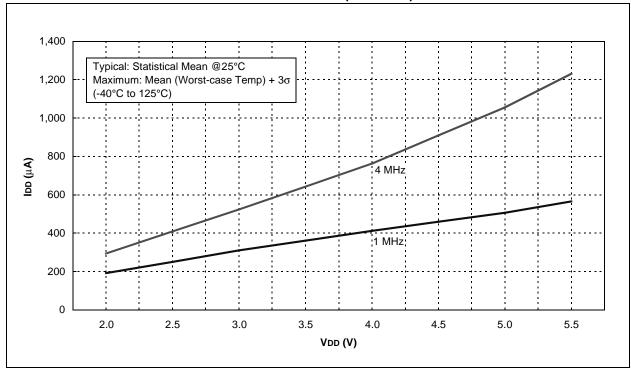

FIGURE 16-6: MAXIMUM IDD vs. VDD OVER FOSC (XT MODE)

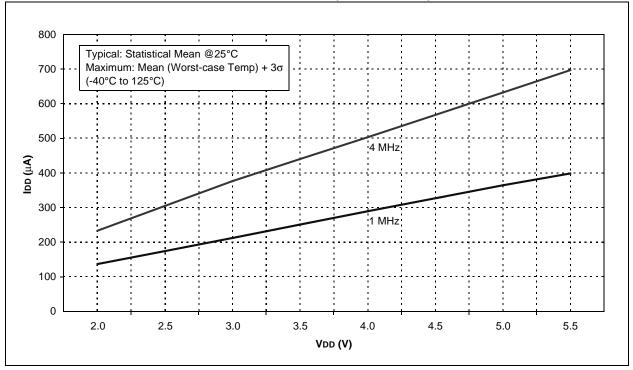

FIGURE 16-7: TYPICAL IDD vs. VDD OVER FOSC (EXTRC MODE)

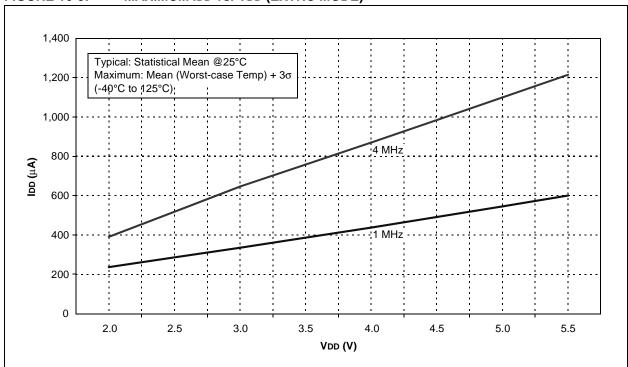

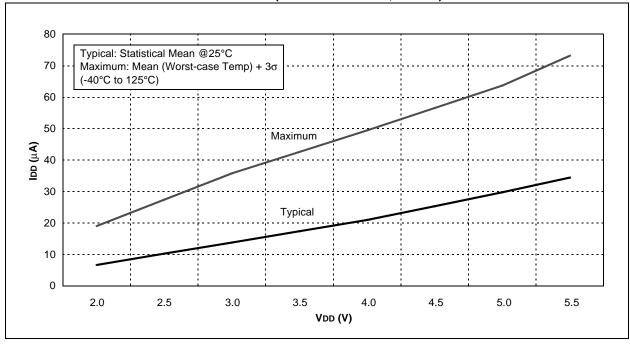

FIGURE 16-8: MAXIMUM IDD vs. VDD (EXTRC MODE)

FIGURE 16-9: IDD vs. VDD OVER FOSC (LFINTOSC MODE, 31 kHz)

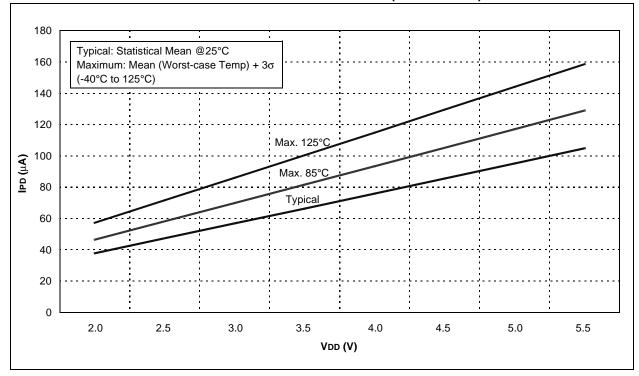

FIGURE 16-22: CVREF IPD vs. VDD OVER TEMPERATURE (LOW RANGE)

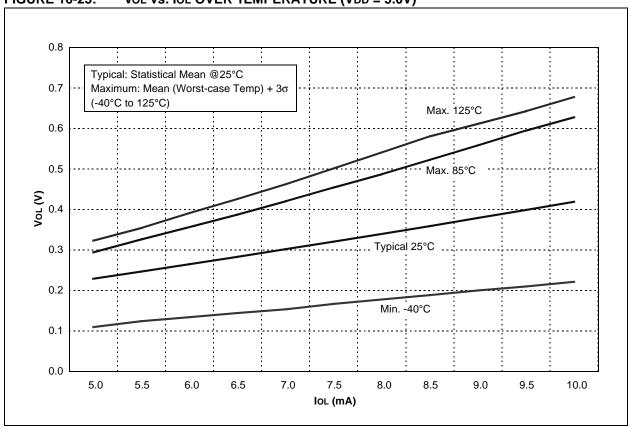

FIGURE 16-23: Vol vs. Iol OVER TEMPERATURE (VDD = 3.0V)

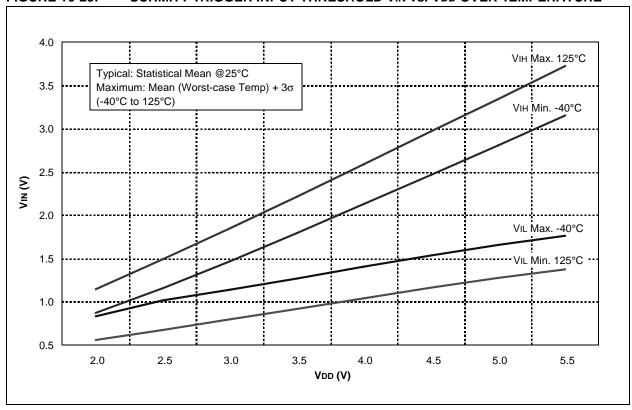

FIGURE 16-28: SCHMITT TRIGGER INPUT THRESHOLD VIN vs. VDD OVER TEMPERATURE

FIGURE 16-29: T1OSC IPD vs. VDD OVER TEMPERATURE (32 kHz)

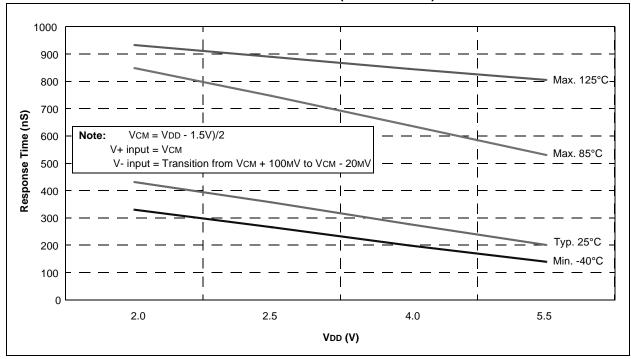

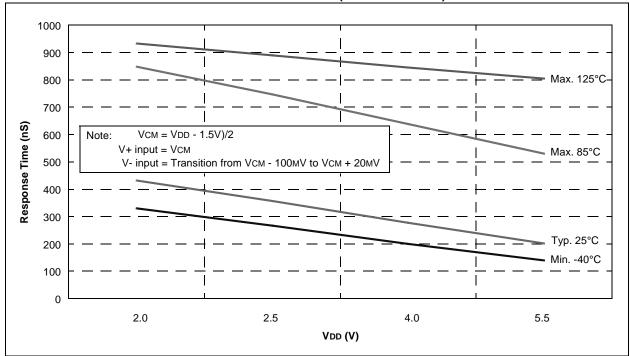

FIGURE 16-30: COMPARATOR RESPONSE TIME (RISING EDGE)

## WORLDWIDE SALES AND SERVICE

#### **AMERICAS**

**Corporate Office**

2355 West Chandler Blvd. Chandler, AZ 85224-6199 Tel: 480-792-7200 Fax: 480-792-7277

Technical Support:

http://support.microchip.com

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Dallas

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

Detroit

Farmington Hills, MI Tel: 248-538-2250 Fax: 248-538-2260

Kokomo

Kokomo, IN Tel: 765-864-8360 Fax: 765-864-8387

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

Santa Clara

Santa Clara, CA Tel: 408-961-6444 Fax: 408-961-6445

**Toronto**

Mississauga, Ontario, Canada

Tel: 905-673-0699 Fax: 905-673-6509

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Habour City, Kowloon Hong Kong

Tel: 852-2401-1200 Fax: 852-2401-3431

Australia - Sydney

Tel: 61-2-9868-6733 Fax: 61-2-9868-6755

China - Beijing

Tel: 86-10-8528-2100 Fax: 86-10-8528-2104

China - Chengdu

Tel: 86-28-8665-5511 Fax: 86-28-8665-7889

China - Fuzhou

Tel: 86-591-8750-3506 Fax: 86-591-8750-3521

China - Hong Kong SAR

Tel: 852-2401-1200 Fax: 852-2401-3431

China - Qingdao

Tel: 86-532-8502-7355 Fax: 86-532-8502-7205

China - Shanghai Tel: 86-21-5407-5533

Fax: 86-21-5407-5066

China - Shenyang

Tel: 86-24-2334-2829 Fax: 86-24-2334-2393

China - Shenzhen

Tel: 86-755-8203-2660 Fax: 86-755-8203-1760

China - Shunde

Tel: 86-757-2839-5507 Fax: 86-757-2839-5571

China - Wuhan

Tel: 86-27-5980-5300 Fax: 86-27-5980-5118

China - Xian

Tel: 86-29-8833-7250 Fax: 86-29-8833-7256

#### ASIA/PACIFIC

India - Bangalore

Tel: 91-80-4182-8400 Fax: 91-80-4182-8422

India - New Delhi

Tel: 91-11-4160-8631 Fax: 91-11-4160-8632

India - Pune

Tel: 91-20-2566-1512 Fax: 91-20-2566-1513

Japan - Yokohama

Tel: 81-45-471- 6166 Fax: 81-45-471-6122

Korea - Gumi

Tel: 82-54-473-4301 Fax: 82-54-473-4302

Korea - Seoul

Tel: 82-2-554-7200 Fax: 82-2-558-5932 or 82-2-558-5934

Malaysia - Penang Tel: 60-4-646-8870 Fax: 60-4-646-5086

Philippines - Manila

Tel: 63-2-634-9065 Fax: 63-2-634-9069

Singapore

Tel: 65-6334-8870 Fax: 65-6334-8850 Taiwan - Hsin Chu

Tel: 886-3-572-9526 Fax: 886-3-572-6459

Taiwan - Kaohsiung Tel: 886-7-536-4818

Fax: 886-7-536-4803

Taiwan - Taipei

Tel: 886-2-2500-6610 Fax: 886-2-2508-0102

Thailand - Bangkok

Tel: 66-2-694-1351 Fax: 66-2-694-1350

#### **EUROPE**

Austria - Wels

Tel: 43-7242-2244-39 Fax: 43-7242-2244-393 Denmark - Copenhagen

Tel: 45-4450-2828 Fax: 45-4485-2829

France - Paris

Tel: 33-1-69-53-63-20 Fax: 33-1-69-30-90-79

Germany - Munich

Tel: 49-89-627-144-0 Fax: 49-89-627-144-44

Italy - Milan

Tel: 39-0331-742611 Fax: 39-0331-466781

Netherlands - Drunen

Tel: 31-416-690399 Fax: 31-416-690340

Spain - Madrid

Tel: 34-91-708-08-90 Fax: 34-91-708-08-91 **UK - Wokingham**

Tel: 44-118-921-5869 Fax: 44-118-921-5820

12/08/06