# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683t-i-md |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| IADL   | E Z-1:  | FIGIZE             | -003 3FE                                                           |               | GISTER        | 5 SUIVIIVIA   |                | r u            |               |         |             | 0      |

|--------|---------|--------------------|--------------------------------------------------------------------|---------------|---------------|---------------|----------------|----------------|---------------|---------|-------------|--------|

| Addr   | Name    | Bit 7              | Bit 6                                                              | Bit 5         | Bit 4         | Bit 3         | Bit 2          | Bit 1          | Bit 0         |         | e on<br>BOR | Page   |

| Bank ( | )       | _                  |                                                                    |               |               |               |                |                |               |         |             |        |

| 00h    | INDF    | Addressin          | g this locatio                                                     | on uses conte | ents of FSR   | to address d  | ata memory     | / (not a physi | cal register) | xxxx    | xxxx        | 17, 90 |

| 01h    | TMR0    | Timer0 M           | Fimer0 Module Register xxxx xxxx                                   |               |               |               |                |                |               |         |             |        |

| 02h    | PCL     | Program (          | Counter's (F                                                       | PC) Least S   | ignificant By | ⁄te           |                |                |               | 0000    | 0000        | 17, 90 |

| 03h    | STATUS  | IRP <sup>(1)</sup> | RP1 <sup>(1)</sup>                                                 | RP0           | TO            | PD            | Z              | DC             | С             | 0001    | 1xxx        | 11, 90 |

| 04h    | FSR     | Indirect D         | ata Memory                                                         | Address P     | ointer        |               |                |                |               | xxxx    | xxxx        | 17, 90 |

| 05h    | GPIO    | _                  | _                                                                  | GP5           | GP4           | GP3           | GP2            | GP1            | GP0           | xx      | xxxx        | 31, 90 |

| 06h    | _       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           | _      |

| 07h    | _       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           |        |

| 08h    | _       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           |        |

| 09h    | _       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           |        |

| 0Ah    | PCLATH  | _                  | _                                                                  | _             | Write Buffe   | r for upper 5 | 5 bits of Pro  | gram Count     | er            | 0       | 0000        | 17, 90 |

| 0Bh    | INTCON  | GIE                | PEIE                                                               | T0IE          | INTE          | GPIE          | T0IF           | INTF           | GPIF          | 0000    | 0000        | 13, 90 |

| 0Ch    | PIR1    | EEIF               | ADIF                                                               | CCP1IF        | _             | CMIF          | OSFIF          | TMR2IF         | TMR1IF        | 000-    | 0000        | 15, 90 |

| 0Dh    | _       | Unimplem           | nented                                                             |               |               | •             |                |                |               | -       | _           |        |

| 0Eh    | TMR1L   | Holding R          | Holding Register for the Least Significant Byte of the 16-bit TMR1 |               |               |               |                |                |               |         |             | 44, 90 |

| 0Fh    | TMR1H   | Holding R          | egister for t                                                      | he Most Sig   | nificant Byt  | e of the 16-b | bit TMR1       |                |               | xxxx    | xxxx        | 44, 90 |

| 10h    | T1CON   | T1GINV             | TMR1GE                                                             | T1CKPS1       | T1CKPS0       | T1OSCEN       | T1SYNC         | TMR1CS         | TMR10N        | 0000    | 0000        | 47, 90 |

| 11h    | TMR2    | Timer2 M           | odule Regis                                                        | ter           |               |               |                |                | J             | 0000    | 0000        | 49, 90 |

| 12h    | T2CON   | —                  | TOUTPS3                                                            | TOUTPS2       | TOUTPS1       | TOUTPS0       | TMR2ON         | T2CKPS1        | T2CKPS0       | -000    | 0000        | 50, 90 |

| 13h    | CCPR1L  | Capture/C          | Compare/PV                                                         | VM Register   | 1 Low Byte    | 9             |                |                | J             | xxxx    | xxxx        | 76, 90 |

| 14h    | CCPR1H  | Capture/C          | Compare/PV                                                         | VM Register   | r 1 High Byt  | е             |                |                |               | xxxx    | xxxx        | 76, 90 |

| 15h    | CCP1CON | _                  | —                                                                  | DC1B1         | DC1B0         | CCP1M3        | CCP1M2         | CCP1M1         | CCP1M0        | 00      | 0000        | 75, 90 |

| 16h    | _       | Unimplem           | nented                                                             |               |               | •             |                |                |               | -       | _           | _      |

| 17h    | _       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           |        |

| 18h    | WDTCON  | _                  | —                                                                  | —             | WDTPS3        | WDTPS2        | WDTPS1         | WDTPS0         | SWDTEN        | 0       | 1000        | 97, 90 |

| 19h    | CMCON0  | _                  | COUT                                                               | _             | CINV          | CIS           | CM2            | CM1            | CM0           | - 0 - 0 | 0000        | 56, 90 |

| 1Ah    | CMCON1  | _                  | _                                                                  | _             | _             | _             | _              | T1GSS          | CMSYNC        |         | 10          | 57, 90 |

| 1Bh    | _       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           | _      |

| 1Ch    | —       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           | _      |

| 1Dh    | —       | Unimplem           | nented                                                             |               |               |               |                |                |               | -       | _           | _      |

| 1Eh    | ADRESH  | Most Sign          | nificant 8 bits                                                    | s of the left | shifted A/D   | result or 2 b | its of right s | hifted result  |               | xxxx    | xxxx        | 61,90  |

| 1Fh    | ADCON0  | ADFM               | VCFG                                                               | _             | _             | CHS1          | CHS0           | GO/DONE        | ADON          | 00      | 0000        | 65,90  |

| 0000   |         |                    | tod logotion                                                       |               |               | 1             | 1              |                |               |         |             |        |

Note 1: IRP and RP1 bits are reserved, always maintain these bits clear.

#### 2.2.2.3 INTCON Register

The INTCON register is a readable and writable register, which contains the various enable and flag bits for TMR0 register overflow, GPIO change and external GP2/INT pin interrupts.

| Note: | Interrupt flag bits are set when an interrupt |

|-------|-----------------------------------------------|

|       | condition occurs, regardless of the state of  |

|       | its corresponding enable bit or the global    |

|       | enable bit, GIE of the INTCON register.       |

|       | User software should ensure the appropri-     |

|       | ate interrupt flag bits are clear prior to    |

|       | enabling an interrupt.                        |

## REGISTER 2-3: INTCON: INTERRUPT CONTROL REGISTER

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| GIE   | PEIE  | TOIE  | INTE  | GPIE  | T0IF  | INTF  | GPIF  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | l as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

| bit 7 | <b>GIE:</b> Global Interrupt Enable bit<br>1 = Enables all unmasked interrupts<br>0 = Disables all interrupts                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | <b>PEIE:</b> Peripheral Interrupt Enable bit<br>1 = Enables all unmasked peripheral interrupts<br>0 = Disables all peripheral interrupts                                                      |

| bit 5 | <b>TolE:</b> Timer0 Overflow Interrupt Enable bit<br>1 = Enables the Timer0 interrupt<br>0 = Disables the Timer0 interrupt                                                                    |

| bit 4 | INTE: GP2/INT External Interrupt Enable bit<br>1 = Enables the GP2/INT external interrupt<br>0 = Disables the GP2/INT external interrupt                                                      |

| bit 3 | <b>GPIE:</b> GPIO Change Interrupt Enable bit <sup>(1)</sup><br>1 = Enables the GPIO change interrupt<br>0 = Disables the GPIO change interrupt                                               |

| bit 2 | <b>T0IF:</b> Timer0 Overflow Interrupt Flag bit <sup>(2)</sup><br>1 = Timer0 register has overflowed (must be cleared in software)<br>0 = Timer0 register did not overflow                    |

| bit 1 | INTF: GP2/INT External Interrupt Flag bit<br>1 = The GP2/INT external interrupt occurred (must be cleared in software)<br>0 = The GP2/INT external interrupt did not occur                    |

| bit 0 | <b>GPIF:</b> GPIO Change Interrupt Flag bit<br>1 = When at least one of the GPIO <5:0> pins changed state (must be cleared in software)<br>0 = None of the GPIO <5:0> pins have changed state |

- Note 1: IOC register must also be enabled.

- 2: T0IF bit is set when TMR0 rolls over. TMR0 is unchanged on Reset and should be initialized before clearing T0IF bit.

## 2.2.2.6 PCON Register

The Power Control (PCON) register contains flag bits (see Table 12-2) to differentiate between a:

- Power-on Reset (POR)

- Brown-out Reset (BOR)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The PCON register also controls the Ultra Low-Power Wake-up and software enable of the BOR.

The PCON register bits are shown in Register 2-6.

## REGISTER 2-6: PCON: POWER CONTROL REGISTER

| U-0   | U-0 | R/W-0  | R/W-1  | U-0 | U-0 | R/W-0 | R/W-x |

|-------|-----|--------|--------|-----|-----|-------|-------|

| —     | —   | ULPWUE | SBOREN | —   | —   | POR   | BOR   |

| bit 7 |     |        |        |     |     |       | bit 0 |

| W = Writable bit                                                                      | U = Unimplemented bit,            | read as '0'                                                                                |  |  |  |  |  |

|---------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------|--|--|--|--|--|

| '1' = Bit is set                                                                      | '0' = Bit is cleared              | x = Bit is unknown                                                                         |  |  |  |  |  |

| plemented: Read as '0'                                                                |                                   |                                                                                            |  |  |  |  |  |

|                                                                                       | la Eachta bh                      |                                                                                            |  |  |  |  |  |

| ULPWUE: Ultra Low-Power Wake-Up Enable bit                                            |                                   |                                                                                            |  |  |  |  |  |

| = Ultra Low-Power Wake-up enabled                                                     |                                   |                                                                                            |  |  |  |  |  |

| tra Low-Power Wake-up disab                                                           |                                   |                                                                                            |  |  |  |  |  |

| SBOREN: Software BOR Enable bit <sup>(1)</sup>                                        |                                   |                                                                                            |  |  |  |  |  |

| 1 = BOR enabled                                                                       |                                   |                                                                                            |  |  |  |  |  |

| OR disabled                                                                           |                                   |                                                                                            |  |  |  |  |  |

| plemented: Read as '0'                                                                |                                   |                                                                                            |  |  |  |  |  |

| POR: Power-on Reset Status bit                                                        |                                   |                                                                                            |  |  |  |  |  |

| 1 = No Power-on Reset occurred                                                        |                                   |                                                                                            |  |  |  |  |  |

| 0 = A Power-on Reset occurred (must be set in software after a Power-on Reset occurs) |                                   |                                                                                            |  |  |  |  |  |

| BOR: Brown-out Reset Status bit                                                       |                                   |                                                                                            |  |  |  |  |  |

| 1 = No Brown-out Reset occurred                                                       |                                   |                                                                                            |  |  |  |  |  |

|                                                                                       | ist be set in software after a Po | wer-on Reset or Brown-out Rese                                                             |  |  |  |  |  |

| 0                                                                                     | o Brown-out Reset occurred        | o Brown-out Reset occurred<br>Brown-out Reset occurred (must be set in software after a Po |  |  |  |  |  |

**Note 1:** Set BOREN<1:0> = 01 in the Configuration Word register for this bit to control the  $\overline{\text{BOR}}$ .

## 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4** "**Frequency Select Bits (IRCF)**" for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

## 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

| Note: | Following any Reset, the IRCF<2:0> bits of |

|-------|--------------------------------------------|

|       | the OSCCON register are set to '110' and   |

|       | the frequency selection is set to 4 MHz.   |

|       | The user can modify the IRCF bits to       |

|       | select a different frequency.              |

## 3.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- 1. IRCF<2:0> bits of the OSCCON register are modified.

- 2. If the new clock is shut down, a clock start-up delay is started.

- 3. Clock switch circuitry waits for a falling edge of the current clock.

- 4. CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the *Electrical Specifications Chapter of this data sheet, under AC Specifications (Oscillator Module).*

| U-0              | R/W-0                                                                                                                                                                                                                                                                | R/W-0            | R/W-0 | R/W-1             | R/W-1             | R/W-1              | R/W-1 |  |  |  |

|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-------------------|-------------------|--------------------|-------|--|--|--|

| _                | ADCS2                                                                                                                                                                                                                                                                | ADCS1            | ADCS0 | ANS3              | ANS2              | ANS1               | ANS0  |  |  |  |

| bit 7            | ·                                                                                                                                                                                                                                                                    |                  |       | ·                 |                   | ·                  | bit 0 |  |  |  |

| Legend:          |                                                                                                                                                                                                                                                                      |                  |       |                   |                   |                    |       |  |  |  |

| R = Readable     | e bit                                                                                                                                                                                                                                                                | W = Writable bit | t     | U = Unimplem      | ented bit, read a | s '0'              |       |  |  |  |

| -n = Value at    | POR                                                                                                                                                                                                                                                                  | '1' = Bit is set |       | '0' = Bit is clea | ired              | x = Bit is unknown |       |  |  |  |

| bit 7<br>bit 6-4 | Unimplemented: Read as '0'<br>ADCS<2:0>: A/D Conversion Clock Select bits<br>000 = Fosc/2<br>001 = Fosc/8<br>010 = Fosc/32<br>x11 = FRC (clock derived from a dedicated internal oscillator = 500 kHz max)<br>100 = Fosc/4<br>101 = Fosc/16<br>110 = Fosc/64         |                  |       |                   |                   |                    |       |  |  |  |

| bit 3-0          | <b>ANS&lt;3:0&gt;</b> : Analog Select bits<br>Analog select between analog or digital function on pins AN<3:0>, respectively.<br>1 = Analog input. Pin is assigned as analog input <sup>(1)</sup> .<br>0 = Digital I/O. Pin is assigned to port or special function. |                  |       |                   |                   |                    |       |  |  |  |

|                  | Setting a pin to an a<br>available. The cor                                                                                                                                                                                                                          | 0 1              |       | <b>o</b> 1        |                   |                    |       |  |  |  |

## REGISTER 4-3: ANSEL: ANALOG SELECT REGISTER

the pin.

| U-0U-0R/W-1R/W-1U-0R/W-1R/W-1R/W $ -$ WPU5WPU4 $-$ WPU2WPU1WPbit 7Legend:<br>R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'<br>-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknownbit 7-6Unimplemented: Read as '0'<br>bit 5-4WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabledUnimplemented: Read as '0'bit 3Unimplemented: Read as '0'Unimplemented: Read as '0'Unimplemented: Read as '0'Unimplemented: Read as '0' |       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| bit 7<br>Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 7-6 Unimplemented: Read as '0'<br>bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                      | ·1    |

| Legend:      R = Readable bit    W = Writable bit    U = Unimplemented bit, read as '0'      -n = Value at POR    '1' = Bit is set    '0' = Bit is cleared    x = Bit is unknown      bit 7-6    Unimplemented: Read as '0'      bit 5-4    WPU<5:4>: Weak Pull-up Control bits      1 = Pull-up enabled    0 = Pull-up disabled                                                                                                                                                                | 10    |

| R = Readable bit    W = Writable bit    U = Unimplemented bit, read as '0'      -n = Value at POR    '1' = Bit is set    '0' = Bit is cleared    x = Bit is unknown      bit 7-6    Unimplemented: Read as '0'      bit 5-4    WPU<5:4>: Weak Pull-up Control bits      1 = Pull-up enabled    0 = Pull-up disabled                                                                                                                                                                             | bit 0 |

| R = Readable bit    W = Writable bit    U = Unimplemented bit, read as '0'      -n = Value at POR    '1' = Bit is set    '0' = Bit is cleared    x = Bit is unknown      bit 7-6    Unimplemented: Read as '0'    '0' = Bit is cleared    x = Bit is unknown      bit 5-4    WPU<5:4>: Weak Pull-up Control bits    1 = Pull-up enabled    0 = Pull-up disabled                                                                                                                                 |       |

| -n = Value at POR    '1' = Bit is set    '0' = Bit is cleared    x = Bit is unknown      bit 7-6    Unimplemented: Read as '0'    WPU<5:4>: Weak Pull-up Control bits      1 = Pull-up enabled    0 = Pull-up disabled                                                                                                                                                                                                                                                                          |       |

| bit 7-6 Unimplemented: Read as '0'<br>bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                |       |

| bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| bit 5-4 WPU<5:4>: Weak Pull-up Control bits<br>1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                      |       |

| 1 = Pull-up enabled<br>0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |

| bit 3 Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       |

| bit 2-0 WPU<2:0>: Weak Pull-up Control bits                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |

| 1 = Pull-up enabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       |

| 0 = Pull-up disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |

| <b>Note 1:</b> Global GPPU must be enabled for individual pull-ups to be enabled.                                                                                                                                                                                                                                                                                                                                                                                                               |       |

#### REGISTER 4-4: WPU: WEAK PULL-UP REGISTER

- Clobal Of FO must be enabled for individual pull-ups to be enabled.

The weak pull-up device is automatically disabled if the pin is in Output mode (TRISIO = 0).

- 3: The GP3 pull-up is enabled when configured as MCLR and disabled as an I/O in the Configuration Word.

- 4: WPU<5:4> always reads '1' in XT, HS and LP OSC modes.

#### REGISTER 4-5: IOC: INTERRUPT-ON-CHANGE GPIO REGISTER

| U-0   | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-------|-------|-------|-------|-------|

| _     | —   | IOC5  | IOC4  | IOC3  | IOC2  | IOC1  | IOC0  |

| bit 7 |     |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                                    |  |  |  |

|-------------------|------------------|-----------------------|------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |  |

bit 7-6 Unimplemented: Read as '0'

bit 5-0 **IOC<5:0>:** Interrupt-on-change GPIO Control bits

1 = Interrupt-on-change enabled

0 = Interrupt-on-change disabled

Note 1: Global Interrupt Enable (GIE) must be enabled for individual interrupts to be recognized.

2: IOC<5:4> always reads '0' in XT, HS and LP OSC modes.

## 4.2.4 ULTRA LOW-POWER WAKE-UP

The Ultra Low-Power Wake-up (ULPWU) on GP0 allows a slow falling voltage to generate an interrupt-on-change on GP0 without excess current consumption. The mode is selected by setting the ULPWUE bit of the PCON register. This enables a small current sink which can be used to discharge a capacitor on GP0.

To use this feature, the GP0 pin is configured to output '1' to charge the capacitor, interrupt-on-change for GP0 is enabled and GP0 is configured as an input. The ULP-WUE bit is set to begin the discharge and a SLEEP instruction is performed. When the voltage on GP0 drops below VIL, an interrupt will be generated which will cause the device to wake-up. Depending on the state of the GIE bit of the INTCON register, the device will either jump to the interrupt vector (0004h) or execute the next instruction when the interrupt event occurs. See Section 4.2.3 "Interrupt-on-Change" and Section 12.4.3 "GPIO Interrupt" for more information.

This feature provides a low-power technique for periodically waking up the device from Sleep. The time-out is dependent on the discharge time of the RC circuit on GP0. See Example 4-2 for initializing the Ultra Low-Power Wake-up module.

The series resistor provides overcurrent protection for the GP0 pin and can allow for software calibration of the time-out (see Figure 4-1). A timer can be used to measure the charge time and discharge time of the capacitor. The charge time can then be adjusted to provide the desired interrupt delay. This technique will compensate for the affects of temperature, voltage and component accuracy. The Ultra Low-Power Wake-up peripheral can also be configured as a simple Programmable Low-Voltage Detect or temperature sensor.

| Note: | For more information, refer to the Applica- |  |  |  |  |  |  |  |  |

|-------|---------------------------------------------|--|--|--|--|--|--|--|--|

|       | tion Note AN879, "Using the Microchip       |  |  |  |  |  |  |  |  |

|       | Ultra Low-Power Wake-up Module"             |  |  |  |  |  |  |  |  |

|       | (DS00879).                                  |  |  |  |  |  |  |  |  |

## EXAMPLE 4-2:

#### ULTRA LOW-POWER WAKE-UP INITIALIZATION

| BANKSEL | CMCON0       | ;                   |

|---------|--------------|---------------------|

| MOVLW   | H'7'         | ;Turn off           |

| MOVWF   | CMCON0       | ;comparators        |

| BANKSEL | ANSEL        | ;                   |

| BCF     | ANSEL,0      | ;RA0 to digital I/O |

| BCF     | TRISA,0      | ;Output high to     |

| BANKSEL | PORTA        | ;                   |

| BSF     | PORTA,0      | ;charge capacitor   |

| CALL    | CapDelay     | ;                   |

| BANKSEL | PCON         | ;                   |

| BSF     | PCON, ULPWUE | ;Enable ULP Wake-up |

| BSF     | IOCA,0       | ;Select RA0 IOC     |

| BSF     | TRISA,0      | ;RA0 to input       |

| MOVLW   | B'10001000'  | ;Enable interrupt   |

| MOVWF   | INTCON       | ; and clear flag    |

| SLEEP   |              | ;Wait for IOC       |

| NOP     |              | ;                   |

|         |              |                     |

| R/W-x            | R/W-x                             | R/W-x  | R/W-x  | R/W-x                               | R/W-x  | R/W-x  | R/W-x  |  |

|------------------|-----------------------------------|--------|--------|-------------------------------------|--------|--------|--------|--|

| ADRES9           | ADRES8                            | ADRES7 | ADRES6 | ADRES5                              | ADRES4 | ADRES3 | ADRES2 |  |

| bit 7            | •                                 | •      |        | •                                   |        | •      | bit 0  |  |

|                  |                                   |        |        |                                     |        |        |        |  |

| Legend:          |                                   |        |        |                                     |        |        |        |  |

| R = Readable bi  | R = Readable bit W = Writable bit |        |        | U = Unimplemented bit, read as '0'  |        |        |        |  |

| -n = Value at PC | n = Value at POR '1' = Bit is set |        |        | '0' = Bit is cleared x = Bit is unk |        |        | wn     |  |

#### **REGISTER 9-2:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 0

bit 7-0 ADRES<9:2>: ADC Result Register bits Upper 8 bits of 10-bit conversion result

#### **REGISTER 9-3:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 0

| R/W-x                                                                | R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|----------------------------------------------------------------------|--------|-------|-------|-------|-------|-------|-------|

| ADRES1                                                               | ADRES0 | —     | —     | —     | —     | —     | —     |

| bit 7                                                                |        |       |       |       |       |       | bit 0 |

|                                                                      |        |       |       |       |       |       |       |

| Legend:                                                              |        |       |       |       |       |       |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |        |       |       |       |       |       |       |

'0' = Bit is cleared

| bit 7-6 | ADRES<1:0>: ADC Result Register bits     |

|---------|------------------------------------------|

|         | Lower 2 bits of 10-bit conversion result |

'1' = Bit is set

bit 5-0 **Reserved**: Do not use.

-n = Value at POR

#### **REGISTER 9-4:** ADRESH: ADC RESULT REGISTER HIGH (ADRESH) ADFM = 1

| R/W-x  | R/W-x  |

|-------|-------|-------|-------|-------|-------|--------|--------|

| —     | _     | —     | —     | —     | _     | ADRES9 | ADRES8 |

| bit 7 |       |       |       |       |       |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-2 Reserved: Do not use.

bit 1-0 ADRES<9:8>: ADC Result Register bits Upper 2 bits of 10-bit conversion result

#### **REGISTER 9-5:** ADRESL: ADC RESULT REGISTER LOW (ADRESL) ADFM = 1

| R/W-x  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| ADRES7 | ADRES6 | ADRES5 | ADRES4 | ADRES3 | ADRES2 | ADRES1 | ADRES0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 7-0 ADRES<7:0>: ADC Result Register bits Lower 8 bits of 10-bit conversion result x = Bit is unknown

## 12.2 Calibration Bits

Brown-out Reset (BOR), Power-on Reset (POR) and 8 MHz internal oscillator (HFINTOSC) are factory calibrated. These calibration values are stored in fuses located in the Calibration Word (2009h). The Calibration Word is not erased when using the specified bulk erase sequence in the "*PIC12F6XX/16F6XX Memory Programming Specification*" (DS41244) and thus, does not require reprogramming.

## 12.3 Reset

The PIC12F683 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

WDT wake-up does not cause register resets in the same manner as a WDT Reset since wake-up is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations, as indicated in Table 12-2. Software can use these bits to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

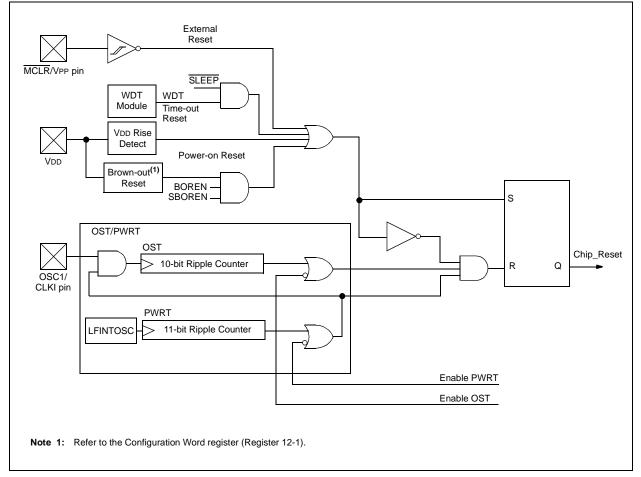

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse-width specifications.

## FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

## 12.3.1 POWER-ON RESET

The on-chip POR circuit holds the chip in Reset until VDD has reached a high enough level for proper operation. To take advantage of the POR, simply connect the MCLR pin through a resistor to VDD. This will eliminate external RC components usually needed to create Power-on Reset. A maximum rise time for VDD is required. See **Section 15.0** "**Electrical Specifications**" for details. If the BOR is enabled, the maximum rise time specification does not apply. The BOR circuitry will keep the device in Reset until VDD reaches VBOD (see **Section 12.3.4** "**Brown-Out Reset (BOR)**").

Note: The POR circuit does not produce an internal Reset when VDD declines. To re-enable the POR, VDD must reach Vss for a minimum of 100 μs.

When the device starts normal operation (exits the Reset condition), device operating parameters (i.e., voltage, frequency, temperature, etc.) must be met to ensure operation. If these conditions are not met, the device must be held in Reset until the operating conditions are met.

For additional information, refer to the Application Note *AN607, "Power-up Trouble Shooting"* (DS00607).

## 12.3.2 MCLR

PIC12F683 has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

It should be noted that a WDT Reset does not drive  $\overline{\text{MCLR}}$  pin low.

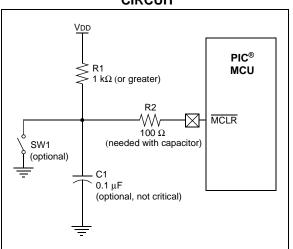

Voltages applied to the MCLR pin that exceed its specification can result in both MCLR Resets and excessive current beyond the device specification during the ESD event. For this reason, Microchip recommends that the MCLR pin no longer be tied directly to VDD. The use of an RC network, as shown in Figure 12-2, is suggested.

An internal  $\overline{\text{MCLR}}$  option is enabled by clearing the  $\overline{\text{MCLRE}}$  bit in the Configuration Word register. When  $\overline{\text{MCLRE}} = 0$ , the Reset signal to the chip is generated internally. When the  $\overline{\text{MCLRE}} = 1$ , the GP3/ $\overline{\text{MCLR}}$  pin becomes an external Reset input. In this mode, the GP3/ $\overline{\text{MCLR}}$  pin has a weak pull-up to VDD.

#### FIGURE 12-2: RECOMMENDED MCLR CIRCUIT

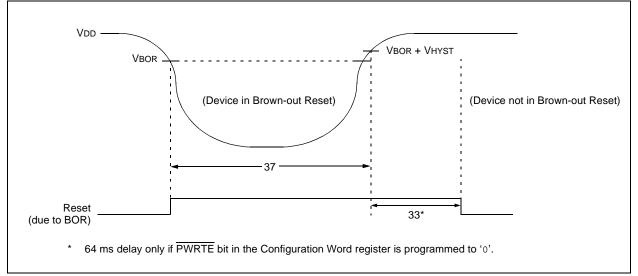

#### 12.3.3 POWER-UP TIMER (PWRT)

The Power-up Timer provides a fixed 64 ms (nominal) time-out on power-up only, from POR or Brown-out Reset. The Power-up Timer operates from the 31 kHz LFINTOSC oscillator. For more information, see **Section 3.5 "Internal Clock Modes"**. The chip is kept in Reset as long as PWRT is active. The PWRT delay allows the VDD to rise to an acceptable level. A Configuration bit, PWRTE, can disable (if set) or enable (if cleared or programmed) the Power-up Timer. The Power-up Timer should be enabled when Brown-out Reset is enabled, although it is not required.

The Power-up Timer delay will vary from chip-to-chip due to:

- VDD variation

- Temperature variation

- · Process variation

See DC parameters for details (Section 15.0 "Electrical Specifications").

**Note:** Voltage spikes below Vss at the  $\overline{\text{MCLR}}$  pin, inducing currents greater than 80 mA, may cause latch-up. Thus, a series resistor of 50-100  $\Omega$  should be used when applying a "low" level to the  $\overline{\text{MCLR}}$  pin, rather than pulling this pin directly to Vss.

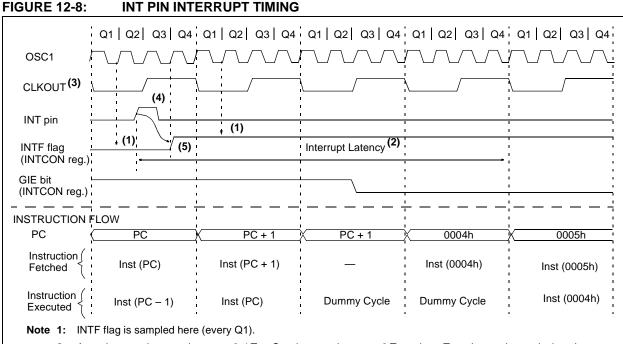

- 2: Asynchronous interrupt latency = 3-4 TCY. Synchronous latency = 3 TCY, where TCY = instruction cycle time. Latency is the same whether Inst (PC) is a single cycle or a 2-cycle instruction.

- 3: CLKOUT is available only in INTOSC and RC Oscillator modes.

4: For minimum width of INT pulse, refer to AC specifications in Section 15.0 "Electrical Specifications".

5: INTF is enabled to be set any time during the Q4-Q1 cycles.

| Name   | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1  | Bit 0  | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-------|-------|--------|-------|-------|-------|--------|--------|----------------------|---------------------------------|

| INTCON | GIE   | PEIE  | T0IE   | INTE  | GPIE  | T0IF  | INTF   | GPIF   | 0000 0000            | 0000 0000                       |

| IOC    | _     |       | IOC5   | IOC4  | IOC3  | IOC2  | IOC1   | IOC0   | 00 0000              | 00 0000                         |

| PIR1   | EEIF  | ADIF  | CCP1IF | _     | CMIF  | OSFIF | TMR2IF | TMR1IF | 000- 0000            | 000- 0000                       |

| PIE1   | EEIE  | ADIE  | CCP1IE |       | CMIE  | OSFIE | TMR2IE | TMR1IE | 000- 0000            | 000- 0000                       |

#### TABLE 12-6: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPTS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0', q = value depends upon condition. Shaded cells are not used by the interrupt module.

| ; Q1   Q2   Q3   Q4; G<br>OSC1 ///////_     | 21   Q2   Q3   Q4 ¦ Q |                     | Q1  Q2   Q3   Q4 | Q1 Q2 Q3 Q4       | Q1 Q2 Q3 Q4;   | Q1 Q2 Q3 Q4; |

|---------------------------------------------|-----------------------|---------------------|------------------|-------------------|----------------|--------------|

|                                             | /\                    | Tost(2)             |                  | \/                | \\             |              |

| INT pin                                     | 1                     |                     |                  | I I               | 1<br>1         |              |

| INTF flag<br>(INTCON<1>)                    |                       |                     | Interrupt Laten  | <sub>CV</sub> (3) |                |              |

| GIE bit<br>(INTCON<7>)                      | Pri                   | ocessor in<br>Sleep |                  | ·                 |                |              |

| Instruction Flow<br>PC X PC X               | PC + 1 X              | PC + 2              | PC + 2           | X PC + 2          | X <u>0004h</u> | (0005h       |

| Instruction [<br>Fetched ] Inst(PC) = Sleep | Inst(PC + 1)          |                     | Inst(PC + 2)     | 1 i<br>1 i        | Inst(0004h)    | Inst(0005h)  |

| Instruction Inst(PC – 1)                    | Sleep                 | 1<br> <br>          | Inst(PC + 1)     | Dummy Cycle       | Dummy Cycle    | Inst(0004h)  |

|                                             |                       |                     |                  |                   |                |              |

Note 1: XT, HS or LP Oscillator mode assumed.

- **2**: TOST = 1024 TOSC (drawing not to scale). This delay does not apply to EC and RCIO Oscillator modes.

- 3: GIE = 1 assumed. In this case after wake-up, the processor jumps to 0004h. If GIE = 0, execution will continue in-line.

- 4: CLKOUT is not available in XT, HS, LP or EC Oscillator modes, but shown here for timing reference.

## 12.8 Code Protection

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out using  $ICSP^{TM}$  for verification purposes.

Note: The entire data EEPROM and Flash program memory will be erased when the code protection is turned off. See the "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information.

## 12.9 ID Locations

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution, but are readable and writable during Program/Verify mode. Only the Least Significant 7 bits of the ID locations are used.

## 14.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

## 14.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC<sup>®</sup> and MCU devices. It debugs and programs PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high speed, noise tolerant, lowvoltage differential signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 14.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers costeffective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

## 14.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP™ cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

## TABLE 15-2: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated)Operating Temperature $-40^{\circ}C \le TA \le +125^{\circ}C$ |       |                                                        |                    |      |      |      |       |                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------|-------|--------------------------------------------------------|--------------------|------|------|------|-------|-------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                         | Sym   | Characteristic                                         | Freq.<br>Tolerance | Min  | Тур† | Max  | Units | Conditions                                                                                            |

| OS06                                                                                                                 | Twarm | Internal Oscillator Switch when running <sup>(3)</sup> | _                  | —    | —    | 2    | Tosc  | Slowest clock                                                                                         |

| OS07                                                                                                                 | Tsc   | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | —                  | —    | 21   | —    | ms    | LFINTOSC/64                                                                                           |

| OS08                                                                                                                 | HFosc | Internal Calibrated                                    | ±1%                | 7.92 | 8.0  | 8.08 | MHz   | VDD = 3.5V, 25°C                                                                                      |

|                                                                                                                      |       | HFINTOSC Frequency <sup>(2)</sup>                      | ±2%                | 7.84 | 8.0  | 8.16 | MHz   | $2.5V \le VDD \le 5.5V$ ,<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                     |

|                                                                                                                      |       |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz   | $2.0V \le VDD \le 5.5V$ ,<br>-40°C $\le$ TA $\le$ +85°C (Ind.),<br>-40°C $\le$ TA $\le$ +125°C (Ext.) |

| OS09*                                                                                                                | LFosc | Internal Uncalibrated<br>LFINTOSC Frequency            | —                  | 15   | 31   | 45   | kHz   |                                                                                                       |

| OS10*                                                                                                                | Tiosc | HFINTOSC Oscillator                                    | _                  | 5.5  | 12   | 24   | μs    | VDD = 2.0V, -40°C to +85°C                                                                            |

|                                                                                                                      | ST    | Wake-up from Sleep                                     | —                  | 3.5  | 7    | 14   | μs    | VDD = 3.0V, -40°C to +85°C                                                                            |

|                                                                                                                      |       | Start-up Time                                          | —                  | 3    | 6    | 11   | μs    | VDD = 5.0V, -40°C to +85°C                                                                            |

Standard Operating Conditions (unless otherwise stated)

\* These parameters are characterized but not tested.

† Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- **Note 1:** Instruction cycle period (TCY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible. 0.1  $\mu$ F and 0.01  $\mu$ F values in parallel are recommended.

3: By design.

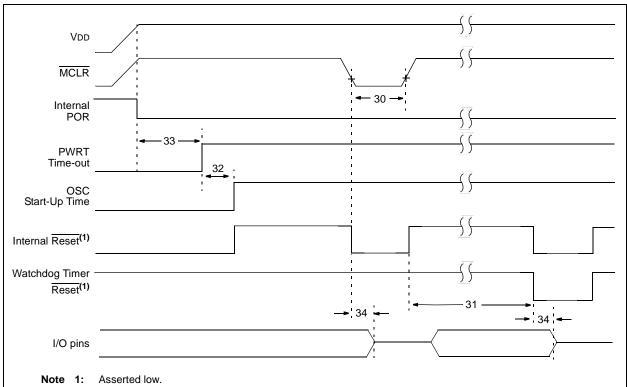

# FIGURE 15-6: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER AND POWER-UP TIMER TIMING

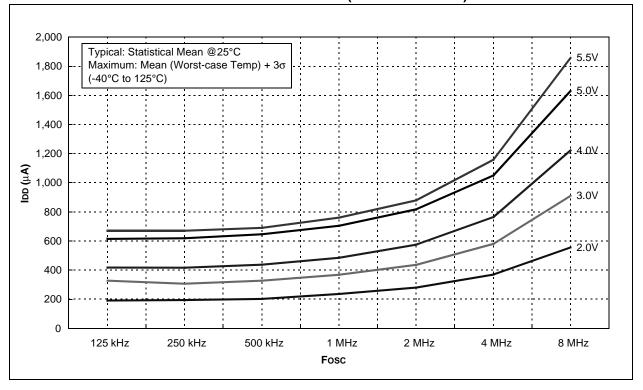

FIGURE 16-12: MAXIMUM IDD vs. Fosc OVER VDD (HFINTOSC MODE)

NOTES:

## APPENDIX A: DATA SHEET REVISION HISTORY

## **Revision A**

This is a new data sheet.

## **Revision B**

Rewrites of the Oscillator and Special Features of the CPU sections. General corrections to Figures and formatting.

## **Revision C**

Revisions throughout document. Incorporated Golden Chapters.

## **Revision D**

Replaced Package Drawings; Revised Product ID Section (SN package to 3.90 mm); Replaced PICmicro with PIC; Replaced Dev Tool Section.

## APPENDIX B: MIGRATING FROM OTHER PIC® DEVICES

This discusses some of the issues in migrating from other PIC devices to the PIC12F683 device.

## B.1 PIC16F676 to PIC12F683

#### TABLE B-1: FEATURE COMPARISON

| Feature                               | PIC16F676     | PIC12F683            |

|---------------------------------------|---------------|----------------------|

| Max Operating<br>Speed                | 20 MHz        | 20 MHz               |

| Max Program<br>Memory (Words)         | 1024          | 2048                 |

| SRAM (bytes)                          | 64            | 128                  |

| A/D Resolution                        | 10-bit        | 10-bit               |

| Data EEPROM<br>(Bytes)                | 128           | 256                  |

| Timers (8/16-bit)                     | 1/1           | 2/1                  |

| Oscillator Modes                      | 8             | 8                    |

| Brown-out Reset                       | Y             | Y                    |

| Internal Pull-ups                     | RA0/1/2/4/5   | GP0/1/2/4/5,<br>MCLR |

| Interrupt-on-change                   | RA0/1/2/3/4/5 | GP0/1/2/3/4/5        |

| Comparator                            | 1             | 1                    |

| ECCP                                  | N             | N                    |

| Ultra Low-Power<br>Wake-Up            | N             | Y                    |

| Extended WDT                          | N             | Y                    |

| Software Control<br>Option of WDT/BOR | N             | Y                    |

| INTOSC                                | 4 MHz         | 32 kHz-              |

| Frequencies                           |               | 8 MHz                |

| Clock Switching                       | Ν             | Y                    |

**Note:** This device has been designed to perform to the parameters of its data sheet. It has been tested to an electrical specification designed to determine its conformance with these parameters. Due to process differences in the manufacture of this device, this device may have different performance characteristics than its earlier version. These differences may cause this device to perform differently in your application than the earlier version of this device.

# PIC12F683

| SUBLW      108        SUBWF      109        SWAPF      109        XORLW      109        XORWF      109        INTCON Register      14        Internal Oscillator Block      INTOSC |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Specifications126, 127                                                                                                                                                             |

| Internal Sampling Switch (RSS) IMPEDANCE                                                                                                                                           |

| Internet Address                                                                                                                                                                   |

| Interrupts                                                                                                                                                                         |

| ADC64                                                                                                                                                                              |

| Associated Registers94                                                                                                                                                             |

| Comparator55                                                                                                                                                                       |

| Context Saving95                                                                                                                                                                   |

| Data EEPROM Memory Write72                                                                                                                                                         |

| GP2/INT                                                                                                                                                                            |

| GPIO Interrupt-on-change                                                                                                                                                           |

| Interrupt-on-Change32                                                                                                                                                              |

| Timer0                                                                                                                                                                             |

| TMR1                                                                                                                                                                               |

| INTOSC Specifications                                                                                                                                                              |

| IOC Register                                                                                                                                                                       |

## L

| Load Conditions 1 | 24 |

|-------------------|----|

|-------------------|----|

## Μ

| MCLR                                              | . 86 |

|---------------------------------------------------|------|

| Internal                                          | . 86 |

| Memory Organization                               |      |

| Data EEPROM Memory                                | . 71 |

| Microchip Internet Web Site                       | 171  |

| Migrating from other PIC Devices                  | 165  |

| MPLAB ASM30 Assembler, Linker, Librarian          | 112  |

| MPLAB ICD 2 In-Circuit Debugger                   | 113  |

| MPLAB ICE 2000 High-Performance Universal         |      |

| In-Circuit Emulator                               | 113  |

| MPLAB ICE 4000 High-Performance Universal         |      |

| In-Circuit Emulator                               | 113  |

| MPLAB Integrated Development Environment Software | 111  |

| MPLAB PM3 Device Programmer                       | 113  |

| MPLINK Object Linker/MPLIB Object Librarian       | 112  |

## 0

| OPCODE Field Descriptions       |  |

|---------------------------------|--|

| OPTION Register                 |  |

| OSCCON Register                 |  |

| Oscillator                      |  |

| Associated registers            |  |

| Oscillator Module               |  |

| EC                              |  |

| HFINTOSC                        |  |

| HS                              |  |

| INTOSC                          |  |

| INTOSCIO                        |  |

| LFINTOSC                        |  |

| LP                              |  |

| RC                              |  |

| RCIO                            |  |

| XT                              |  |

| Oscillator Parameters           |  |

| Oscillator Specifications       |  |

| Oscillator Start-up Timer (OST) |  |

| Specifications                  |  |

|                                 |  |

| Oscillator Switching                         |

|----------------------------------------------|

| Fail-Safe Clock Monitor 29                   |

| Two-Speed Clock Start-up 27                  |

| OSCTUNE Register                             |

| Ρ                                            |

| Packaging                                    |

| Details                                      |

| Marking 159                                  |

| PCL and PCLATH 18                            |

| Computed GOTO 18                             |

| Stack                                        |

| PCON Register 17, 88                         |

| PICSTART Plus Development Programmer 114     |

| PIE1 Register                                |

| Pin Diagram                                  |

| Pinout Descriptions                          |

| PIC12F6836                                   |

| PIR1 Register 16                             |

| Power-Down Mode (Sleep)                      |

| Power-On Reset (POR)                         |

| Power-up Timer (PWRT) 86                     |

| Specifications 129                           |

| Precision Internal Oscillator Parameters 127 |

| Prescaler                                    |

| Shared WDT/Timer0 42                         |

| Switching Prescaler Assignment 42            |

| Program Memory Organization7                 |

| Map and Stack for the PIC12F6837             |

| Programming, Device Instructions 101         |

| R                                            |

| Reader Response                              |

| Read-Modify-Write Operations                 |

| Registers                                    |

| ~ | intorn                                  |    |

|---|-----------------------------------------|----|

| g |                                         | 05 |

|   | ADCON0 (ADC Control 0)                  |    |

|   | ADRESH (ADC Result High) with ADFM = 0) |    |

|   | ADRESH (ADC Result High) with ADFM = 1) |    |

|   | ADRESL (ADC Result Low) with ADFM = 0)  |    |

|   | ADRESL (ADC Result Low) with ADFM = 1)  |    |

|   | ANSEL (Analog Select)                   |    |

|   | CCP1CON (CCP1 Control)                  | 75 |

|   | CMCON0 (Comparator Control) Register    |    |

|   | CMCON1 (Comparator Control) Register    |    |

|   | CONFIG (Configuration Word)             |    |

|   | EEADR (EEPROM Address)                  |    |

|   | EECON1 (EEPROM Control 1)               | 72 |

|   | EECON2 (EEPROM Control 2)               | 72 |

|   | EEDAT (EEPROM Data)                     | 71 |

|   | GPIO                                    |    |

|   | INTCON (Interrupt Control)              | 14 |

|   | IOC (Interrupt-on-Change GPIO)          | 34 |

|   | OPTION_REG (OPTION)                     |    |

|   | OSCCON (Oscillator Control)             | 20 |

|   | OSCTUNE (Oscillator Tuning)             | 24 |

|   | PCON (Power Control Register)           |    |

|   | PCON (Power Control)                    | 88 |

|   | PIE1 (Peripheral Interrupt Enable 1)    | 15 |

|   | PIR1 (Peripheral Interrupt Register 1)  | 16 |

|   | Reset Values                            |    |

|   | Reset Values (Special Registers)        | 91 |

|   | STATUS                                  |    |

|   | T1CON                                   | 47 |

|   | T2CON                                   | 50 |

|   | TRISIO (Tri-State GPIO)                 | 32 |

|   | VRCON (Voltage Reference Control)       |    |

|   | · · · · · · · · · · · · · · · · · · ·   |    |

| WDTCON (Watchdog Timer Control) | 97 |

|---------------------------------|----|

| WPU (Weak Pull-Up GPIO)         |    |

| Resets                          | 85 |

| Brown-out Reset (BOR)           | 85 |

| MCLR Reset, Normal Operation    | 85 |

| MCLR Reset, Sleep               | 85 |

| Power-on Reset (POR)            | 85 |

| WDT Reset, Normal Operation     | 85 |

| WDT Reset, Sleep                | 85 |

| Revision History                |    |

# S

| Sleep                          |    |

|--------------------------------|----|

| Power-Down Mode                |    |

| Wake-up                        |    |

| Wake-up Using Interrupts       |    |