# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-VDFN Exposed Pad                                                        |

| Supplier Device Package    | 8-DFN-S (6x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683t-i-mf |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION, QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

## QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, microID, MPLAB, PIC, PICmicro, PICSTART, PRO MATE, PowerSmart, rfPIC, and SmartShunt are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

AmpLab, FilterLab, Linear Active Thermistor, Migratable Memory, MXDEV, MXLAB, PS logo, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, ECAN, ECONOMONITOR, FanSense, FlexROM, fuzzyLAB, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, PICkit, PICDEM, PICDEM.net, PICLAB, PICtail, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, rfPICDEM, Select Mode, Smart Serial, SmartTel, Total Endurance, UNI/O, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

SQTP is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2007, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona, Gresham, Oregon and Mountain View, California. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

# **PIC12F683**

## 8-Pin Flash-Based, 8-Bit CMOS Microcontrollers with nanoWatt Technology

#### **High-Performance RISC CPU:**

- Only 35 instructions to learn:

- All single-cycle instructions except branches

- Operating speed:

- DC 20 MHz oscillator/clock input

- DC 200 ns instruction cycle

- Interrupt capability

- 8-level deep hardware stack

- Direct, Indirect and Relative Addressing modes

#### **Special Microcontroller Features:**

- Precision Internal Oscillator:

- Factory calibrated to ±1%, typical

- Software selectable frequency range of

- 8 MHz to 125 kHz

- Software tunable

- Two-Speed Start-up mode

- Crystal fail detect for critical applications

- Clock mode switching during operation for power savings

- Power-Saving Sleep mode

- Wide operating voltage range (2.0V-5.5V)

- Industrial and Extended temperature range

- Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Reset (BOR) with software control option

- Enhanced Low-Current Watchdog Timer (WDT) with on-chip oscillator (software selectable nominal 268 seconds with full prescaler) with software enable

- Multiplexed Master Clear with pull-up/input pin

- Programmable code protection

- High Endurance Flash/EEPROM cell:

- 100,000 write Flash endurance

- 1,000,000 write EEPROM endurance

- Flash/Data EEPROM Retention: > 40 years

#### Low-Power Features:

- Standby Current:

- 50 nA @ 2.0V, typical

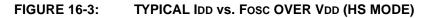

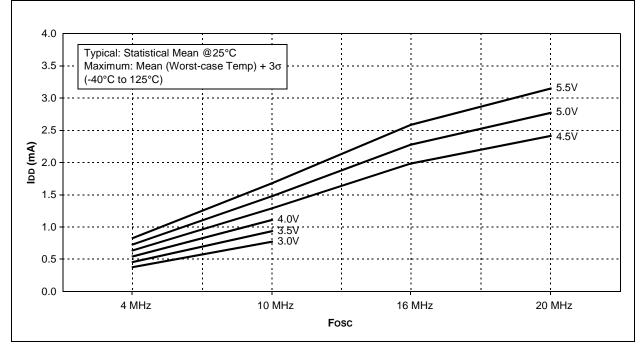

- Operating Current:

- 11 μA @ 32 kHz, 2.0V, typical

- 220 μA @ 4 MHz, 2.0V, typical

- Watchdog Timer Current:

- 1 μA @ 2.0V, typical

#### **Peripheral Features:**

- 6 I/O pins with individual direction control:

- High current source/sink for direct LED drive

- Interrupt-on-pin change

- Individually programmable weak pull-ups

- Ultra Low-Power Wake-up on GP0

- Analog Comparator module with:

- One analog comparator

- Programmable on-chip voltage reference (CVREF) module (% of VDD)

- Comparator inputs and output externally accessible

- A/D Converter:

- 10-bit resolution and 4 channels

- Timer0: 8-bit timer/counter with 8-bit programmable prescaler

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Timer1 Gate (count enable)

- Option to use OSC1 and OSC2 in LP mode as Timer1 oscillator if INTOSC mode selected

- Timer2: 8-bit timer/counter with 8-bit period register, prescaler and postscaler

- Capture, Compare, PWM module:

- 16-bit Capture, max resolution 12.5 ns

- Compare, max resolution 200 ns

- 10-bit PWM, max frequency 20 kHz

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via two pins

| Device    | Program Memory | Data         | Data Memory SRAM (bytes) EEPROM (bytes) |   | 10-bit A/D (ch) | Comparators | Timers   |

|-----------|----------------|--------------|-----------------------------------------|---|-----------------|-------------|----------|

| Device    | Flash (words)  | SRAM (bytes) |                                         |   |                 | Comparators | 8/16-bit |

| PIC12F683 | 2048           | 128          | 256                                     | 6 | 4               | 1           | 2/1      |

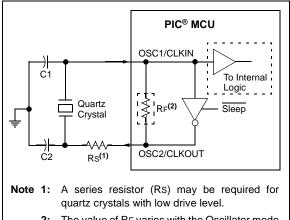

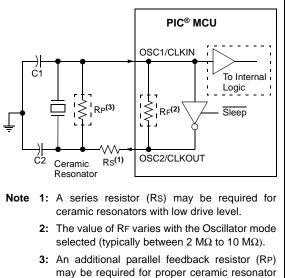

#### 3.4.3 LP, XT, HS MODES

The LP, XT and HS modes support the use of quartz crystal resonators or ceramic resonators connected to OSC1 and OSC2 (Figure 3-3). The mode selects a low, medium or high gain setting of the internal inverter-amplifier to support various resonator types and speed.

**LP** Oscillator mode selects the lowest gain setting of the internal inverter-amplifier. LP mode current consumption is the least of the three modes. This mode is designed to drive only 32.768 kHz tuning-fork type crystals (watch crystals).

**XT** Oscillator mode selects the intermediate gain setting of the internal inverter-amplifier. XT mode current consumption is the medium of the three modes. This mode is best suited to drive resonators with a medium drive level specification.

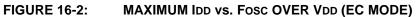

**HS** Oscillator mode selects the highest gain setting of the internal inverter-amplifier. HS mode current consumption is the highest of the three modes. This mode is best suited for resonators that require a high drive setting.

Figure 3-3 and Figure 3-4 show typical circuits for quartz crystal and ceramic resonators, respectively.

2: The value of RF varies with the Oscillator mode selected (typically between 2 M $\Omega$  to 10 M $\Omega$ ).

- Note 1: Quartz crystal characteristics vary according to type, package and manufacturer. The user should consult the manufacturer data sheets for specifications and recommended application.

- 2: Always verify oscillator performance over the VDD and temperature range that is expected for the application.

- **3:** For oscillator design assistance, reference the following Microchip Applications Notes:

- AN826, "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>®</sup> and PIC<sup>®</sup> Devices" (DS00826)

- AN849, "Basic PIC<sup>®</sup> Oscillator Design" (DS00849)

- AN943, "Practical PIC<sup>®</sup> Oscillator Analysis and Design" (DS00943)

- AN949, "Making Your Oscillator Work" (DS00949)

operation.

#### 3.5.2.1 OSCTUNE Register

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| —     | _   | —   | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 7-5 | Unimplemented: Read as '0'                                        |

|---------|-------------------------------------------------------------------|

| bit 4-0 | TUN<4:0>: Frequency Tuning bits                                   |

|         | 01111 = Maximum frequency                                         |

|         | 01110 =                                                           |

|         | •                                                                 |

|         | •                                                                 |

|         | •                                                                 |

|         | 00001 =                                                           |

|         | 00000 = Oscillator module is running at the calibrated frequency. |

|         | 11111 =                                                           |

|         | •                                                                 |

|         | •                                                                 |

|         | •                                                                 |

|         | 10000 = Minimum frequency                                         |

## PIC12F683

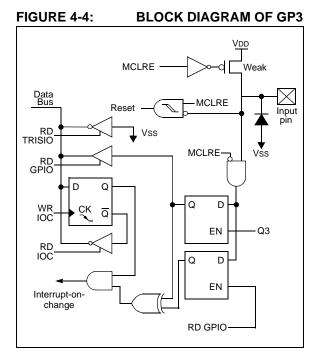

#### 4.2.5.4 GP3/MCLR/VPP

Figure 4-4 shows the diagram for this pin. The GP3 pin is configurable to function as one of the following:

- a general purpose input

- as Master Clear Reset with weak pull-up

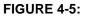

#### 4.2.5.5 GP4/AN3/T1G/OSC2/CLKOUT

Figure 4-5 shows the diagram for this pin. The GP4 pin is configurable to function as one of the following:

- a general purpose I/O

- an analog input for the ADC

- a Timer1 gate input

- a crystal/resonator connection

- a clock output

#### BLOCK DIAGRAM OF GP4

| R/W-1        | R/W-1                     | R/W-1              | R/W-1           | R/W-1            | R/W-1           | R/W-1           | R/W-1 |

|--------------|---------------------------|--------------------|-----------------|------------------|-----------------|-----------------|-------|

| GPPU         | INTEDG                    | TOCS               | TOSE            | PSA              | PS2             | PS1             | PS0   |

| bit 7        | ·                         |                    |                 |                  |                 | •               | bit   |

|              |                           |                    |                 |                  |                 |                 |       |

| Legend:      |                           |                    |                 |                  |                 |                 |       |

| R = Readab   | le bit                    | W = Writable       | bit             | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value a | t POR                     | '1' = Bit is set   |                 | '0' = Bit is cle | ared            | x = Bit is unki | nown  |

|              |                           |                    |                 |                  |                 |                 |       |

| bit 7        | GPPU: GPIO                | Pull-up Enable     | e bit           |                  |                 |                 |       |

|              | 1 = GPIO pul              | l-ups are disab    | led             |                  |                 |                 |       |

|              | 0 = GPIO pul              | l-ups are enab     | ed by individu  | ual PORT latch   | values in WPl   | J register      |       |

| bit 6        | INTEDG: Inte              | errupt Edge Se     | ect bit         |                  |                 |                 |       |

|              |                           | on rising edge     |                 |                  |                 |                 |       |

|              | 0 = Interrupt             | on falling edge    | of INT pin      |                  |                 |                 |       |

| bit 5        | TOCS: Timer               | Clock Source       | Select bit      |                  |                 |                 |       |

|              |                           | n on T0CKI pin     |                 |                  |                 |                 |       |

|              | 0 = Internal ir           | nstruction cycle   | clock (Fosc/    | (4)              |                 |                 |       |

| bit 4        | TOSE: Timer(              | ) Source Edge      | Select bit      |                  |                 |                 |       |

|              | 1 = Incremen              | t on high-to-lov   | v transition or | n T0CKI pin      |                 |                 |       |

|              | 0 = Incremen              | t on low-to-hig    | n transition or | n T0CKI pin      |                 |                 |       |

| bit 3        | PSA: Prescal              | ler Assignment     | bit             |                  |                 |                 |       |

|              | 1 = Prescaler             | is assigned to     | the WDT         |                  |                 |                 |       |

|              | 0 = Prescaler             | is assigned to     | the Timer0 m    | nodule           |                 |                 |       |

| bit 2-0      | <b>PS&lt;2:0&gt;:</b> Pre | escaler Rate Se    | elect bits      |                  |                 |                 |       |

|              | BIT                       | VALUE TIMER0       | RATE WDT RA     | TE               |                 |                 |       |

|              | 0                         | 000 1:2            | 1:1             |                  |                 |                 |       |

|              | 0                         | 01 1:4             | 1:2             |                  |                 |                 |       |

|              |                           | 10 1:8             | 1:4             |                  |                 |                 |       |

|              |                           | 1 1 : 10           | -               |                  |                 |                 |       |

|              |                           | 00 1:32<br>01 1:64 | -               |                  |                 |                 |       |

|              |                           | 01 1:64<br>10 1:12 |                 |                  |                 |                 |       |

|              |                           | 11 1:2             |                 | ,<br>,           |                 |                 |       |

#### REGISTER 5-1: OPTION\_REG: OPTION REGISTER

Note 1: A dedicated 16-bit WDT postscaler is available. See Section 12.6 "Watchdog Timer (WDT)" for more information.

#### TABLE 5-1: SUMMARY OF REGISTERS ASSOCIATED WITH TIMER0

| Name       | Bit 7    | Bit 6       | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|------------|----------|-------------|---------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

| TMR0       | Timer0 M | odule Regis | ster    |         |         |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON     | GIE      | PEIE        | TOIE    | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000            | 0000 000x                       |

| OPTION_REG | GPPU     | INTEDG      | TOCS    | TOSE    | PSA     | PS2     | PS1     | PS0     | 1111 1111            | 1111 1111                       |

| TRISIO     | _        | —           | TRISIO5 | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Timer0 module.

| U-0        | R/W-0                        | R/W-0                           | R/W-0         | R/W-0             | R/W-0            | R/W-0           | R/W-0   |  |  |  |  |  |  |

|------------|------------------------------|---------------------------------|---------------|-------------------|------------------|-----------------|---------|--|--|--|--|--|--|

| _          | TOUTPS3                      | TOUTPS2                         | TOUTPS1       | TOUTPS0           | TMR2ON           | T2CKPS1         | T2CKPS0 |  |  |  |  |  |  |

| bit 7      |                              |                                 |               |                   |                  |                 | bit     |  |  |  |  |  |  |

| Lonondi    |                              |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

| Legend:    |                              |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

| R = Reada  |                              | W = Writable                    |               | -                 | nented bit, read |                 |         |  |  |  |  |  |  |

| -n = Value | at POR                       | '1' = Bit is set                |               | '0' = Bit is clea | ared             | x = Bit is unkr | nown    |  |  |  |  |  |  |

| bit 7      | Unimplemen                   | ited: Read as '                 | o'            |                   |                  |                 |         |  |  |  |  |  |  |

| bit 6-3    | -                            | Ited. Read as )>: Timer2 Output |               | Select hits       |                  |                 |         |  |  |  |  |  |  |

| DIL 0-3    | 0000 = 1:1 P                 |                                 |               | Select bits       |                  |                 |         |  |  |  |  |  |  |

|            | 0000 = 1:1 P                 |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 0010 = 1:3 P                 |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            |                              | 0011 = 1:4 Postscaler           |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 0100 = 1:5 P                 | 0100 = 1:5 Postscaler           |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 0101 = 1:6 Postscaler        |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 0110 = <b>1</b> :7 P         | ostscaler                       |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 0111 <b>= 1:8 P</b>          | ostscaler                       |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1000 <b>= 1:9 P</b>          |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1001 = 1:10                  |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1010 = 1:11 I                |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1011 = 1:12                  |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1100 = 1:13                  |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1101 = 1:14                  |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1110 = 1:15  <br>1111 = 1:16 |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

| L:4 0      | -                            |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

| bit 2      | TMR2ON: Tir                  |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1 = Timer2 is                |                                 |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 0 = Timer2 is                | s off                           |               |                   |                  |                 |         |  |  |  |  |  |  |

| bit 1-0    | T2CKPS<1:0                   | >: Timer2 Cloc                  | k Prescale Se | lect bits         |                  |                 |         |  |  |  |  |  |  |

|            | 00 = Prescale                | er is 1                         |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 01 = Prescale                | er is 4                         |               |                   |                  |                 |         |  |  |  |  |  |  |

|            | 1x = Prescale                | er is 16                        |               |                   |                  |                 |         |  |  |  |  |  |  |

#### REGISTER 7-1: T2CON: TIMER 2 CONTROL REGISTER

#### TABLE 7-1: SUMMARY OF ASSOCIATED TIMER2 REGISTERS

| Name   | Bit 7                                        | Bit 6         | Bit 5    | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0     | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|----------------------------------------------|---------------|----------|---------|---------|--------|---------|-----------|----------------------|---------------------------------|

| INTCON | GIE                                          | PEIE          | T0IE     | INTE    | GPIE    | T0IF   | INTF    | GPIF      | 0000 0000            | x000 0000x                      |

| PIE1   | EEIE                                         | ADIE          | CCP1IE   | _       | CMIE    | OSFIE  | TMR2IE  | TMR1IE    | 000- 0000            | 000- 0000                       |

| PIR1   | EEIF                                         | ADIF          | CCP1IF   | _       | CMIF    | OSFIF  | TMR2IF  | TMR1IF    | 000- 0000            | 000- 0000                       |

| PR2    | Timer2 M                                     | lodule Period | Register |         |         |        |         |           | 1111 1111            | 1111 1111                       |

| TMR2   | Holding Register for the 8-bit TMR2 Register |               |          |         |         |        |         | 0000 0000 | 0000 0000            |                                 |

| T2CON  | _                                            | TOUTPS3       | TOUTPS2  | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0   | -000 0000            | -000 0000                       |

| 1      |                                              |               |          |         |         |        |         |           |                      |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for Timer2 module.

| Name   | Bit 7     | Bit 6        | Bit 5     | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|--------|-----------|--------------|-----------|---------|---------|---------|---------|---------|----------------------|---------------------------------|

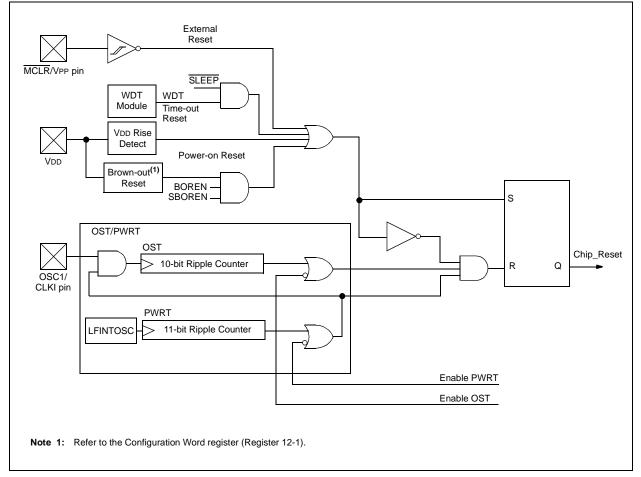

| ADCON0 | ADFM      | VCFG         | —         | —       | CHS1    | CHS0    | GO/DONE | ADON    | 00 0000              | 0000 0000                       |

| ANSEL  | —         | ADCS2        | ADCS1     | ADCS0   | ANS3    | ANS2    | ANS1    | ANS0    | -000 1111            | -000 1111                       |

| ADRESH | A/D Resul | t Register H | ligh Byte |         |         |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| ADRESL | A/D Resul | t Register L | ow Byte   |         |         |         |         |         | xxxx xxxx            | uuuu uuuu                       |

| INTCON | GIE       | PEIE         | TOIE      | INTE    | GPIE    | T0IF    | INTF    | GPIF    | 0000 0000            | 0000 000x                       |

| PIE1   | EEIE      | ADIE         | CCP1IE    | _       | CMIE    | OSFIE   | TMR2IE  | TMR1IE  | 000- 0000            | 0000 0000                       |

| PIR1   | EEIF      | ADIF         | CCP1IF    | —       | CMIF    | OSFIF   | TMR2IF  | TMR1IF  | 000- 0000            | 000- 0000                       |

| GPIO   | —         | —            | GP5       | GP4     | GP3     | GP2     | GP1     | GP0     | xx xxxx              | uu uuuu                         |

| TRISIO |           | _            | TRISI05   | TRISIO4 | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

TABLE 9-2: SUMMARY OF ASSOCIATED ADC REGISTERS

**Legend:** x = unknown, u = unchanged, - = unimplemented read as '0'. Shaded cells are not used for ADC module.

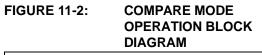

#### 11.2 Compare Mode

In Compare mode, the 16-bit CCPR1 register value is constantly compared against the TMR1 register pair value. When a match occurs, the CCP1 module may:

- Toggle the CCP1 output.

- Set the CCP1 output.

- Clear the CCP1 output.

- Generate a Special Event Trigger.

- Generate a Software Interrupt.

The action on the pin is based on the value of the CCP1M<3:0> control bits of the CCP1CON register.

All Compare modes can generate an interrupt.

- Clear TMR1H and TMR1L registers.

- NOT set interrupt flag bit TMR1IF of the PIR1 register.

- Set the GO/DONE bit to start the ADC conversion.

#### 11.2.1 CCP1 PIN CONFIGURATION

The user must configure the CCP1 pin as an output by clearing the associated TRIS bit.

| Note: | Clearing the CCP1CON register will force    |

|-------|---------------------------------------------|

|       | the CCP1 compare output latch to the        |

|       | default low level. This is not the GPIO I/O |

|       | data latch.                                 |

#### 11.2.2 TIMER1 MODE SELECTION

In Compare mode, Timer1 must be running in either Timer mode or Synchronized Counter mode. The compare operation may not work in Asynchronous Counter mode.

#### 11.2.3 SOFTWARE INTERRUPT MODE

When Generate Software Interrupt mode is chosen (CCP1M<3:0> = 1010), the CCP1 module does not assert control of the CCP1 pin (see the CCP1CON register).

#### 11.2.4 SPECIAL EVENT TRIGGER

When Special Event Trigger mode is chosen (CCP1M<3:0> = 1011), the CCP1 module does the following:

- Resets Timer1

- Starts an ADC conversion if ADC is enabled

The CCP1 module does not assert control of the CCP1 pin in this mode (see the CCP1CON register).

The Special Event Trigger output of the CCP occurs immediately upon a match between the TMR1H, TMR1L register pair and the CCPR1H, CCPR1L register pair. The TMR1H, TMR1L register pair is not reset until the next rising edge of the Timer1 clock. This allows the CCPR1H, CCPR1L register pair to effectively provide a 16-bit programmable period register for Timer1.

Note 1: The Special Event Trigger from the CCP module does not set interrupt flag bit TMRxIF of the PIR1 register.

2: Removing the match condition by changing the contents of the CCPR1H and CCPR1L register pair, between the clock edge that generates the Special Event Trigger and the clock edge that generates the Timer1 Reset, will preclude the Reset from occurring. NOTES:

#### 12.2 Calibration Bits

Brown-out Reset (BOR), Power-on Reset (POR) and 8 MHz internal oscillator (HFINTOSC) are factory calibrated. These calibration values are stored in fuses located in the Calibration Word (2009h). The Calibration Word is not erased when using the specified bulk erase sequence in the "*PIC12F6XX/16F6XX Memory Programming Specification*" (DS41244) and thus, does not require reprogramming.

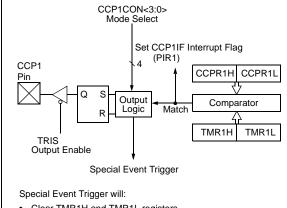

#### 12.3 Reset

The PIC12F683 differentiates between various kinds of Reset:

- a) Power-on Reset (POR)

- b) WDT Reset during normal operation

- c) WDT Reset during Sleep

- d) MCLR Reset during normal operation

- e) MCLR Reset during Sleep

- f) Brown-out Reset (BOR)

Some registers are not affected in any Reset condition; their status is unknown on POR and unchanged in any other Reset. Most other registers are reset to a "Reset state" on:

- Power-on Reset

- MCLR Reset

- MCLR Reset during Sleep

- WDT Reset

- Brown-out Reset (BOR)

WDT wake-up does not cause register resets in the same manner as a WDT Reset since wake-up is viewed as the resumption of normal operation.  $\overline{\text{TO}}$  and  $\overline{\text{PD}}$  bits are set or cleared differently in different Reset situations, as indicated in Table 12-2. Software can use these bits to determine the nature of the Reset. See Table 12-4 for a full description of Reset states of all registers.

A simplified block diagram of the On-Chip Reset Circuit is shown in Figure 12-1.

The MCLR Reset path has a noise filter to detect and ignore small pulses. See **Section 15.0** "**Electrical Specifications**" for pulse-width specifications.

#### FIGURE 12-1: SIMPLIFIED BLOCK DIAGRAM OF ON-CHIP RESET CIRCUIT

#### 12.4 Interrupts

The PIC12F683 has multiple interrupt sources:

- External Interrupt GP2/INT

- Timer0 Overflow Interrupt

- GPIO Change Interrupts

- Comparator Interrupt

- A/D Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

- EEPROM Data Write Interrupt

- Fail-Safe Clock Monitor Interrupt

- CCP Interrupt

The Interrupt Control register (INTCON) and Peripheral Interrupt Request Register 1 (PIR1) record individual interrupt requests in flag bits. The INTCON register also has individual and global interrupt enable bits.

The Global Interrupt Enable bit, GIE of the INTCON register, enables (if set) all unmasked interrupts, or disables (if cleared) all interrupts. Individual interrupts can be disabled through their corresponding enable bits in the INTCON register and PIE1 register. GIE is cleared on Reset.

When an interrupt is serviced, the following actions occur automatically:

- The GIE is cleared to disable any further interrupt.

- The return address is pushed onto the stack.

- The PC is loaded with 0004h.

The Return from Interrupt instruction, RETFIE, exits the interrupt routine, as well as sets the GIE bit, which re-enables unmasked interrupts.

The following interrupt flags are contained in the INTCON register:

- INT Pin Interrupt

- GPIO Change Interrupt

- Timer0 Overflow Interrupt

The peripheral interrupt flags are contained in the PIR1 register. The corresponding interrupt enable bit is contained in the PIE1 register.

The following interrupt flags are contained in the PIR1 register:

- EEPROM Data Write Interrupt

- A/D Interrupt

- Comparator Interrupt

- Timer1 Overflow Interrupt

- Timer2 Match Interrupt

- Fail-Safe Clock Monitor Interrupt

- CCP Interrupt

For external interrupt events, such as the INT pin or GPIO change interrupt, the interrupt latency will be three or four instruction cycles. The exact latency depends upon when the interrupt event occurs (see Figure 12-8). The latency is the same for one or two-cycle instructions. Once in the Interrupt Service Routine, the source(s) of the interrupt can be determined by polling the interrupt flag bits. The interrupt flag bit(s) must be cleared in software before re-enabling interrupts to avoid multiple interrupt requests.

- Note 1: Individual interrupt flag bits are set, regardless of the status of their corresponding mask bit or the GIE bit.

- 2: When an instruction that clears the GIE bit is executed, any interrupts that were pending for execution in the next cycle are ignored. The interrupts, which were ignored, are still pending to be serviced when the GIE bit is set again.

For additional information on Timer1, Timer2, comparators, ADC, data EEPROM or Enhanced CCP modules, refer to the respective peripheral section.

#### 12.4.1 GP2/INT INTERRUPT

The external interrupt on the GP2/INT pin is edge-triggered; either on the rising edge if the INTEDG bit of the OPTION register is set, or the falling edge, if the INTEDG bit is clear. When a valid edge appears on the GP2/INT pin, the INTF bit of the INTCON register is set. This interrupt can be disabled by clearing the INTE control bit of the INTCON register. The INTF bit must be cleared by software in the Interrupt Service Routine before re-enabling this interrupt. The GP2/INT interrupt can wake-up the processor from Sleep, if the INTE bit was set prior to going into Sleep. See **Section 12.7** "**Power-Down Mode (Sleep)**" for details on Sleep and Figure 12-10 for timing of wake-up from Sleep through GP2/INT interrupt.

Note: The ANSEL and CMCON0 registers must be initialized to configure an analog channel as a digital input. Pins configured as analog inputs will read '0' and cannot generate an interrupt.

#### 12.5 Context Saving During Interrupts

During an interrupt, only the return PC value is saved on the stack. Typically, users may wish to save key registers during an interrupt (e.g., W and STATUS registers). This must be implemented in software.

Since the lower 16 bytes of all banks are common in the PIC12F683 (see Figure 2-2), temporary holding registers, W\_TEMP and STATUS\_TEMP, should be placed in here. These 16 locations do not require banking and therefore, makes it easier to context save and restore. The same code shown in Example 12-1 can be used to:

- Store the W register.

- Store the STATUS register.

- Execute the ISR code.

- Restore the Status (and Bank Select Bit register).

- Restore the W register.

Note: The PIC12F683 normally does not require saving the PCLATH. However, if computed GOTO's are used in the ISR and the main code, the PCLATH must be saved and restored in the ISR.

| EXAMPLE 12-1: | SAVING STATUS AND W REGISTERS IN RAM |

|---------------|--------------------------------------|

|---------------|--------------------------------------|

| MOVWF<br>SWAPF   | W_TEMP<br>STATUS,W | ;Copy W to TEMP register<br>;Swap status to be saved into W<br>;Swaps are used because they do not affect the status bits |

|------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------|

| MOVWF            | STATUS_TEMP        | ;Save status to bank zero STATUS_TEMP register                                                                            |

| :<br>:(ISR)<br>: |                    | ;Insert user code here                                                                                                    |

| SWAPF            | STATUS_TEMP,W      | ;Swap STATUS_TEMP register into W                                                                                         |

|                  |                    | ;(sets bank to original state)                                                                                            |

| MOVWF            | STATUS             | ;Move W into STATUS register                                                                                              |

| SWAPF            | W_TEMP,F           | ;Swap W_TEMP                                                                                                              |

| SWAPF            | W_TEMP,W           | ;Swap W_TEMP into W                                                                                                       |

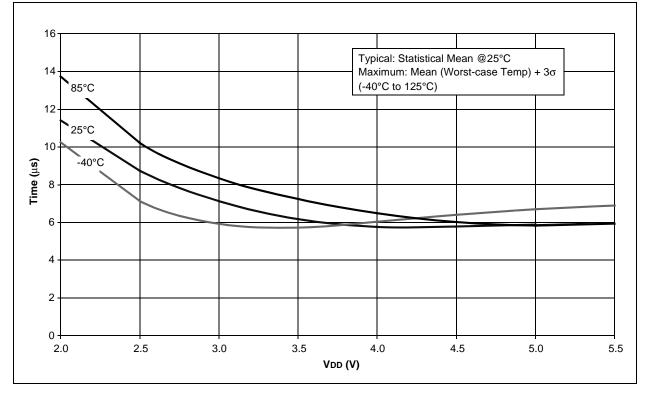

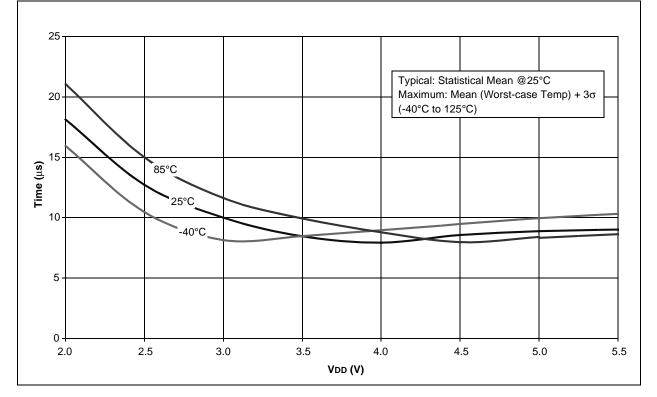

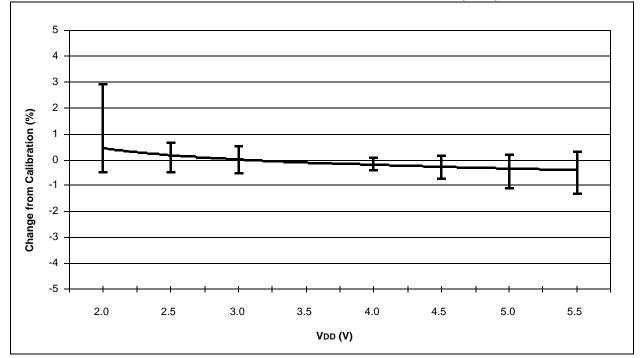

FIGURE 16-36: MINIMUM HFINTOSC START-UP TIMES vs. VDD OVER TEMPERATURE

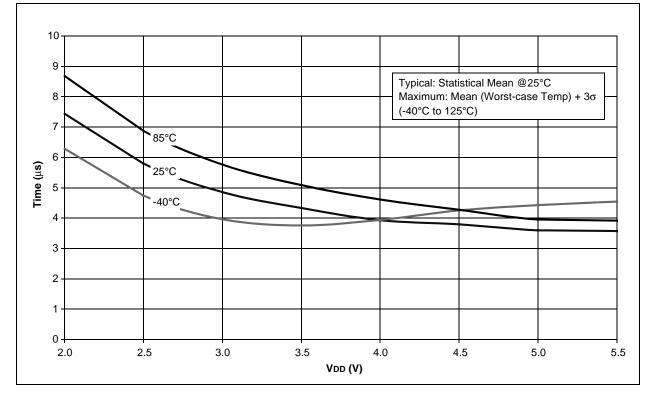

FIGURE 16-37: TYPICAL HFINTOSC FREQUENCY CHANGE vs. VDD (25°C)

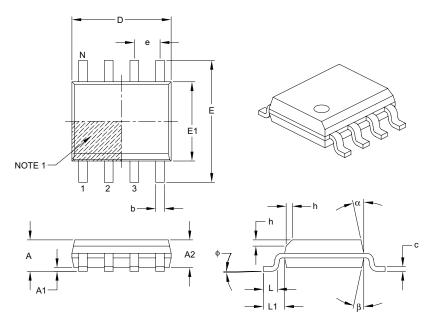

#### 8-Lead Plastic Small Outline (SN or OA) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | MILLIMETERS |      |          |      |

|--------------------------|-------------|------|----------|------|

| Dimens                   | sion Limits | MIN  | NOM      | MAX  |

| Number of Pins           | Ν           |      | 8        |      |

| Pitch                    | е           |      | 1.27 BSC |      |

| Overall Height           | А           | -    | -        | 1.75 |

| Molded Package Thickness | A2          | 1.25 | -        | -    |

| Standoff §               | A1          | 0.10 | -        | 0.25 |

| Overall Width            | E           |      | 6.00 BSC |      |

| Molded Package Width     | E1          |      | 3.90 BSC |      |

| Overall Length           | D           |      | 4.90 BSC |      |

| Chamfer (optional)       | h           | 0.25 | -        | 0.50 |

| Foot Length              | L           | 0.40 | -        | 1.27 |

| Footprint                | L1          |      | 1.04 REF |      |

| Foot Angle               | φ           | 0°   | -        | 8°   |

| Lead Thickness           | С           | 0.17 | -        | 0.25 |

| Lead Width               | b           | 0.31 | _        | 0.51 |

| Mold Draft Angle Top     | α           | 5°   | -        | 15°  |

| Mold Draft Angle Bottom  | β           | 5°   | -        | 15°  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

NOTES:

#### **READER RESPONSE**

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| To:       | Technical Publications Manager                                                       | Total Pages Sent                                        |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|

| RE:       | Reader Response                                                                      |                                                         |  |  |  |  |  |

| From      | : Name                                                                               |                                                         |  |  |  |  |  |

|           | Company                                                                              |                                                         |  |  |  |  |  |

|           |                                                                                      |                                                         |  |  |  |  |  |

|           | City / State / ZIP / Country                                                         |                                                         |  |  |  |  |  |

|           | Telephone: ()                                                                        | FAX: ()                                                 |  |  |  |  |  |

| Appli     | cation (optional):                                                                   |                                                         |  |  |  |  |  |

| Woul      | ld you like a reply?YN                                                               |                                                         |  |  |  |  |  |

| Devi      | ce: PIC12F683                                                                        | Literature Number: DS41211D                             |  |  |  |  |  |

| Ques      | stions:                                                                              |                                                         |  |  |  |  |  |

| 1. V      | What are the best features of this do                                                | ocument?                                                |  |  |  |  |  |

|           |                                                                                      |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

| 2. ⊦      | How does this document meet your hardware and software development needs?            |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

| 3. E      | Do you find the organization of this document easy to follow? If not, why?           |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

| 4. V      | What additions to the document do you think would enhance the structure and subject? |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

|           |                                                                                      |                                                         |  |  |  |  |  |

| 5. V      | What deletions from the document c                                                   | could be made without affecting the overall usefulness? |  |  |  |  |  |

| -         |                                                                                      |                                                         |  |  |  |  |  |

| -<br>-    | le there any incorrect or micloading information (what and where)?                   |                                                         |  |  |  |  |  |

| 6. I      | Is there any incorrect or misleading information (what and where)?                   |                                                         |  |  |  |  |  |

| _         |                                                                                      |                                                         |  |  |  |  |  |

| -<br>7. F | How would you improve this document?                                                 |                                                         |  |  |  |  |  |

|           |                                                                                      |                                                         |  |  |  |  |  |

|           |                                                                                      |                                                         |  |  |  |  |  |

| -         |                                                                                      |                                                         |  |  |  |  |  |