Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                           |

|----------------------------|---------------------------------------------------------------------------|

| Product Status             | Active                                                                    |

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 20MHz                                                                     |

| Connectivity               | -                                                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 5                                                                         |

| Program Memory Size        | 3.5KB (2K x 14)                                                           |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 128 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 5.5V                                                                 |

| Data Converters            | A/D 4x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                                             |

| Supplier Device Package    | 8-SOIC                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic12f683t-i-sn |

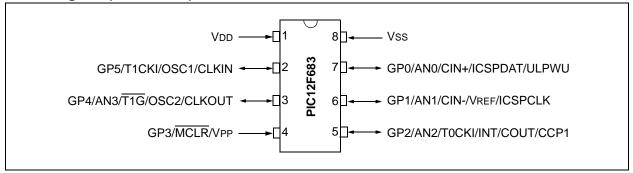

### 8-Pin Diagram (PDIP, SOIC)

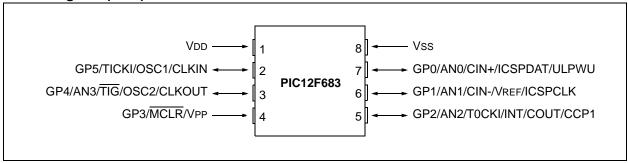

## 8-Pin Diagram (DFN)

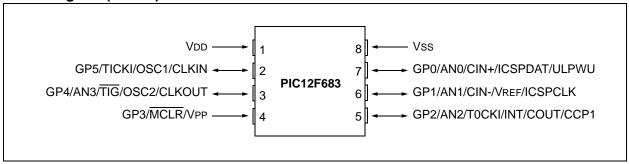

## 8-Pin Diagram (DFN-S)

TABLE 1: 8-PIN SUMMARY

| I/O                | Pin | Analog   | Comparators | Timer | ССР  | Interrupts | Pull-ups | Basic         |

|--------------------|-----|----------|-------------|-------|------|------------|----------|---------------|

| GP0                | 7   | AN0      | CIN+        | _     | _    | IOC        | Υ        | ICSPDAT/ULPWU |

| GP1                | 6   | AN1/VREF | CIN-        |       | _    | IOC        | Υ        | ICSPCLK       |

| GP2                | 5   | AN2      | COUT        | T0CKI | CCP1 | INT/IOC    | Υ        | _             |

| GP3 <sup>(1)</sup> | 4   | _        | _           | _     | _    | IOC        | Y(2)     | MCLR/VPP      |

| GP4                | 3   | AN3      | _           | T1G   | _    | IOC        | Υ        | OSC2/CLKOUT   |

| GP5                | 2   | _        | _           | T1CKI | _    | IOC        | Υ        | OSC1/CLKIN    |

| _                  | 1   | 1        | _           |       | 1    | 1          |          | VDD           |

| _                  | 8   | 1        | _           |       | 1    | 1          |          | Vss           |

Note 1: Input only.

2: Only when pin is configured for external MCLR.

TABLE 1-1: PIC12F683 PINOUT DESCRIPTION

| Name                        | Function | Input<br>Type | Output<br>Type | Description                                         |

|-----------------------------|----------|---------------|----------------|-----------------------------------------------------|

| VDD                         | VDD      | Power         | _              | Positive supply                                     |

| GP5/T1CKI/OSC1/CLKIN        | GP5      | TTL           | CMOS           | GPIO I/O with prog. pull-up and interrupt-on-change |

|                             | T1CKI    | ST            | _              | Timer1 clock                                        |

|                             | OSC1     | XTAL          | _              | Crystal/Resonator                                   |

|                             | CLKIN    | ST            |                | External clock input/RC oscillator connection       |

| GP4/AN3/T1G/OSC2/CLKOUT     | GP4      | TTL           | CMOS           | GPIO I/O with prog. pull-up and interrupt-on-change |

|                             | AN3      | AN            | _              | A/D Channel 3 input                                 |

|                             | T1G      | ST            | _              | Timer1 gate                                         |

|                             | OSC2     | _             | XTAL           | Crystal/Resonator                                   |

|                             | CLKOUT   | _             | CMOS           | Fosc/4 output                                       |

| GP3/MCLR/VPP                | GP3      | TTL           | _              | GPIO input with interrupt-on-change                 |

|                             | MCLR     | ST            | _              | Master Clear with internal pull-up                  |

|                             | VPP      | HV            | _              | Programming voltage                                 |

| GP2/AN2/T0CKI/INT/COUT/CCP1 | GP2      | ST            | CMOS           | GPIO I/O with prog. pull-up and interrupt-on-change |

|                             | AN2      | AN            | _              | A/D Channel 2 input                                 |

|                             | T0CKI    | ST            | _              | Timer0 clock input                                  |

|                             | INT      | ST            | _              | External Interrupt                                  |

|                             | COUT     | _             | CMOS           | Comparator 1 output                                 |

|                             | CCP1     | ST            | CMOS           | Capture input/Compare output/PWM output             |

| GP1/AN1/CIN-/VREF/ICSPCLK   | GP1      | TTL           | CMOS           | GPIO I/O with prog. pull-up and interrupt-on-change |

|                             | AN1      | AN            |                | A/D Channel 1 input                                 |

|                             | CIN-     | AN            |                | Comparator 1 input                                  |

|                             | VREF     | AN            | _              | External Voltage Reference for A/D                  |

|                             | ICSPCLK  | ST            |                | Serial Programming Clock                            |

| GP0/AN0/CIN+/ICSPDAT/ULPWU  | GP0      | TTL           | CMOS           | GPIO I/O with prog. pull-up and interrupt-on-change |

|                             | AN0      | AN            | _              | A/D Channel 0 input                                 |

|                             | CIN+     | AN            | _              | Comparator 1 input                                  |

|                             | ICSPDAT  | ST            | CMOS           | Serial Programming Data I/O                         |

|                             | ULPWU    | AN            | _              | Ultra Low-Power Wake-up input                       |

| Vss                         | Vss      | Power         |                | Ground reference                                    |

**Legend:** AN = Analog input or output

TTL = TTL compatible input

HV = High Voltage

CMOS = CMOS compatible input or output

T = Schmitt Trigger input with CMOS levels

XTAL = Crystal

#### 3.5.2.1 OSCTUNE Register

The HFINTOSC is factory calibrated but can be adjusted in software by writing to the OSCTUNE register (Register 3-2).

The default value of the OSCTUNE register is '0'. The value is a 5-bit two's complement number.

When the OSCTUNE register is modified, the HFINTOSC frequency will begin shifting to the new frequency. Code execution continues during this shift. There is no indication that the shift has occurred.

OSCTUNE does not affect the LFINTOSC frequency. Operation of features that depend on the LFINTOSC clock source frequency, such as the Power-up Timer (PWRT), Watchdog Timer (WDT), Fail-Safe Clock Monitor (FSCM) and peripherals, are *not* affected by the change in frequency.

#### REGISTER 3-2: OSCTUNE: OSCILLATOR TUNING REGISTER

| U-0   | U-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-----|-------|-------|-------|-------|-------|

| _     | _   | _   | TUN4  | TUN3  | TUN2  | TUN1  | TUN0  |

| bit 7 |     |     |       |       |       |       | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7-5 **Unimplemented:** Read as '0'

bit 4-0 **TUN<4:0>:** Frequency Tuning bits

01111 = Maximum frequency

01110 =

•

•

00001 =

00000 = Oscillator module is running at the calibrated frequency.

11111 =

•

•

10000 = Minimum frequency

#### 3.5.3 LFINTOSC

The Low-Frequency Internal Oscillator (LFINTOSC) is an uncalibrated 31 kHz internal clock source.

The output of the LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). Select 31 kHz, via software, using the IRCF<2:0> bits of the OSCCON register. See **Section 3.5.4 "Frequency Select Bits (IRCF)"** for more information. The LFINTOSC is also the frequency for the Power-up Timer (PWRT), Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The LFINTOSC is enabled by selecting 31 kHz (IRCF<2:0> bits of the OSCCON register = 000) as the system clock source (SCS bit of the OSCCON register = 1), or when any of the following are enabled:

- Two-Speed Start-up IESO bit of the Configuration Word register = 1 and IRCF<2:0> bits of the OSCCON register = 000

- Power-up Timer (PWRT)

- Watchdog Timer (WDT)

- Fail-Safe Clock Monitor (FSCM)

The LF Internal Oscillator (LTS) bit of the OSCCON register indicates whether the LFINTOSC is stable or not.

#### 3.5.4 FREQUENCY SELECT BITS (IRCF)

The output of the 8 MHz HFINTOSC and 31 kHz LFINTOSC connects to a postscaler and multiplexer (see Figure 3-1). The Internal Oscillator Frequency Select bits IRCF<2:0> of the OSCCON register select the frequency output of the internal oscillators. One of eight frequencies can be selected via software:

- 8 MHz

- 4 MHz (Default after Reset)

- 2 MHz

- 1 MHz

- 500 kHz

- 250 kHz

- 125 kHz

- 31 kHz (LFINTOSC)

Note:

Following any Reset, the IRCF<2:0> bits of the OSCCON register are set to '110' and the frequency selection is set to 4 MHz. The user can modify the IRCF bits to select a different frequency.

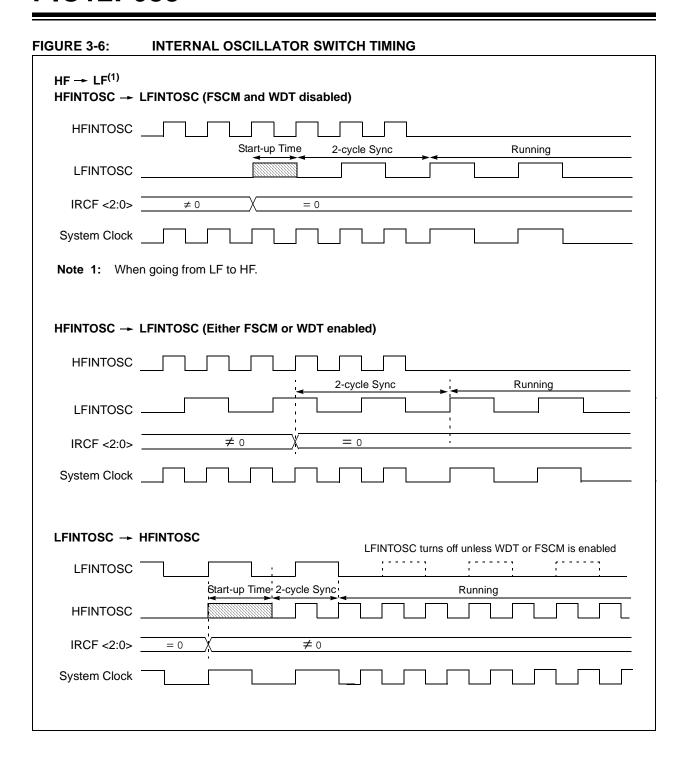

# 3.5.5 HF AND LF INTOSC CLOCK SWITCH TIMING

When switching between the LFINTOSC and the HFINTOSC, the new oscillator may already be shut down to save power (see Figure 3-6). If this is the case, there is a delay after the IRCF<2:0> bits of the OSCCON register are modified before the frequency selection takes place. The LTS and HTS bits of the OSCCON register will reflect the current active status of the LFINTOSC and HFINTOSC oscillators. The timing of a frequency selection is as follows:

- IRCF<2:0> bits of the OSCCON register are modified.

- If the new clock is shut down, a clock start-up delay is started.

- Clock switch circuitry waits for a falling edge of the current clock.

- CLKOUT is held low and the clock switch circuitry waits for a rising edge in the new clock.

- CLKOUT is now connected with the new clock. LTS and HTS bits of the OSCCON register are updated as required.

- 6. Clock switch is complete.

See Figure 3-1 for more details.

If the internal oscillator speed selected is between 8 MHz and 125 kHz, there is no start-up delay before the new frequency is selected. This is because the old and new frequencies are derived from the HFINTOSC via the postscaler and multiplexer.

Start-up delay specifications are located in the *Electrical Specifications Chapter of this data sheet, under AC Specifications (Oscillator Module)*.

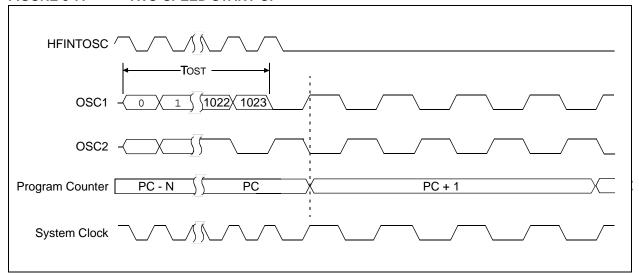

# 3.7.3 CHECKING TWO-SPEED CLOCK STATUS

Checking the state of the OSTS bit of the OSCCON register will confirm if the microcontroller is running from the external clock source, as defined by the FOSC<2:0> bits in the Configuration Word register (CONFIG), or the internal oscillator.

FIGURE 3-7: TWO-SPEED START-UP

#### 8.7 Operation During Sleep

The comparator, if enabled before entering Sleep mode, remains active during Sleep. The additional current consumed by the comparator is shown separately in **Section 15.0** "**Electrical Specifications**". If the comparator is not used to wake the device, power consumption can be minimized while in Sleep mode by turning off the comparator. The comparator is turned off by selecting mode CM<2:0> = 000 or CM<2:0> = 111 of the CMCON0 register.

A change to the comparator output can wake-up the device from Sleep. To enable the comparator to wake the device from Sleep, the CMIE bit of the PIE1 register and the PEIE bit of the INTCON register must be set. The instruction following the Sleep instruction always executes following a wake from Sleep. If the GIE bit of the INTCON register is also set, the device will then execute the Interrupt Service Routine.

#### 8.8 Effects of a Reset

A device Reset forces the CMCON0 and CMCON1 registers to their Reset states. This forces the Comparator module to be in the Comparator Reset mode (CM<2:0> = 000). Thus, all comparator inputs are analog inputs with the comparator disabled to consume the smallest current possible.

#### REGISTER 8-1: CMCON0: COMPARATOR CONFIGURATION REGISTER

| U-0   | R-0  | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|------|-----|-------|-------|-------|-------|-------|

| _     | COUT |     | CINV  | CIS   | CM2   | CM1   | CM0   |

| bit 7 | .7   |     |       |       |       |       | bit 0 |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 7 **Unimplemented:** Read as '0'

bit 6

COUT: Comparator Output bit

When CINV = 0:

1 = VIN+ > VIN-

0 = VIN+ < VIN-When CINV = 1: 1 = VIN+ < VIN-0 = VIN+ > VIN-

bit 5 **Unimplemented:** Read as '0'

bit 4 CINV: Comparator Output Inversion bit

1 = Output inverted0 = Output not inverted

bit 3 CIS: Comparator Input Switch bit

When CM<2:0> = 110 or 101: 1 = CIN+ connects to VIN-0 = CIN- connects to VIN-

When CM<2:0> = 0xx or 100 or 111:

CIS has no effect.

bit 2-0 CM<2:0>: Comparator Mode bits (See Figure 8-5)

$\verb| 000 = CIN pins are configured as analog, COUT pin configured as I/O, Comparator output turned off$

001 = CIN pins are configured as analog, COUT pin configured as Comparator output

010 = CIN pins are configured as analog, COUT pin configured as I/O, Comparator output available internally

011 = CIN- pin is configured as analog, CIN+ pin is configured as I/O, COUT pin configured as Comparator output, CVREF is non-inverting input

100 = CIN- pin is configured as analog, CIN+ pin is configured as I/O, COUT pin is configured as I/O, Comparator output available internally, CVREF is non-inverting input

101 = CIN pins are configured as analog and multiplexed, COUT pin is configured as Comparator output, CVREF is non-inverting input

110 = CIN pins are configured as analog and multiplexed, COUT pin is configured as I/O, Comparator output available internally, CVREF is non-inverting input

${\tt 111} = {\sf CIN} \ {\sf pins} \ {\sf are} \ {\sf configured} \ {\sf as} \ {\sf I/O}, \ {\sf COUT} \ {\sf pin} \ {\sf is} \ {\sf configured} \ {\sf as} \ {\sf I/O}, \ {\sf Comparator} \ {\sf output} \ {\sf disabled}, \ {\sf Comparator} \ {\sf off}.$

#### 8.11 Comparator Voltage Reference

The Comparator Voltage Reference module provides an internally generated voltage reference for the comparators. The following features are available:

- · Independent from Comparator operation

- Two 16-level voltage ranges

- · Output clamped to Vss

- · Ratiometric with VDD

The VRCON register (Register 8-3) controls the Voltage Reference module shown in Figure 8-7.

#### 8.11.1 INDEPENDENT OPERATION

The comparator voltage reference is independent of the comparator configuration. Setting the VREN bit of the VRCON register will enable the voltage reference.

#### 8.11.2 OUTPUT VOLTAGE SELECTION

The CVREF voltage reference has 2 ranges with 16 voltage levels in each range. Range selection is controlled by the VRR bit of the VRCON register. The 16 levels are set with the VR<3:0> bits of the VRCON register.

The CVREF output voltage is determined by the following equations:

#### **EQUATION 8-1: CVREF OUTPUT VOLTAGE**

VRR = 1 (low range):  $CVREF = (VR < 3:0 > /24) \times VDD$  VRR = 0 (high range):  $CVREF = (VDD/4) + (VR < 3:0 > \times VDD/32)$

The full range of Vss to VDD cannot be realized due to the construction of the module. See Figure 8-1.

#### 8.11.3 OUTPUT CLAMPED TO Vss

The CVREF output voltage can be set to Vss with no power consumption by configuring VRCON as follows:

- VREN = 0

- VRR = 1

- VR<3:0> = 0000

This allows the comparator to detect a zero-crossing while not consuming additional CVREF module current.

#### 8.11.4 OUTPUT RATIOMETRIC TO VDD

The comparator voltage reference is VDD derived and therefore, the CVREF output changes with fluctuations in VDD. The tested absolute accuracy of the Comparator Voltage Reference can be found in **Section 15.0** "**Electrical Specifications**".

#### REGISTER 8-3: VRCON: VOLTAGE REFERENCE CONTROL REGISTER

| R/W-0 | U-0 | R/W-0 | U-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 |

|-------|-----|-------|-----|-------|-------|-------|-------|

| VREN  | _   | VRR   | _   | VR3   | VR2   | VR1   | VR0   |

| bit 7 |     |       |     |       |       |       | bit 0 |

| l ea | er | าฯ |   |

|------|----|----|---|

| Leg  | CI | IU | • |

bit 4

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7 **VREN:** CVREF Enable bit

1 = CVREF circuit powered on

0 = CVREF circuit powered down, no IDD drain and CVREF = VSS.

bit 6 Unimplemented: Read as '0' bit 5 VRR: CVREF Range Selection

**VRR:** CVREF Range Selection bit 1 = Low range

0 = High range

Unimplemented: Read as '0'

bit 3-0 **VR<3:0>:** CVREF Value Selection  $0 \le VR<3:0> \le 15$

When VRR = 1: CVREF = (VR < 3:0 > /24) \* VDD

When VRR = 0: CVREF = VDD/4 + (VR<3:0>/32) \* VDD

#### 9.2.4 ADC OPERATION DURING SLEEP

The ADC module can operate during Sleep. This requires the ADC clock source to be set to the FRC option. When the FRC clock source is selected, the ADC waits one additional instruction before starting the conversion. This allows the SLEEP instruction to be executed, which can reduce system noise during the conversion. If the ADC interrupt is enabled, the device will wake-up from Sleep when the conversion completes. If the ADC interrupt is disabled, the ADC module is turned off after the conversion completes, although the ADON bit remains set.

When the ADC clock source is something other than FRC, a SLEEP instruction causes the present conversion to be aborted and the ADC module is turned off, although the ADON bit remains set.

#### 9.2.5 SPECIAL EVENT TRIGGER

The CCP Special Event Trigger allows periodic ADC measurements without software intervention. When this trigger occurs, the GO/DONE bit is set by hardware and the Timer1 counter resets to zero.

Using the Special Event Trigger does not assure proper ADC timing. It is the user's responsibility to ensure that the ADC timing requirements are met.

See Section 11.0 "Capture/Compare/PWM (CCP) Module" for more information.

#### 9.2.6 A/D CONVERSION PROCEDURE

This is an example procedure for using the ADC to perform an Analog-to-Digital conversion:

- 1. Configure GPIO Port:

- Disable pin output driver (See TRIS register)

- · Configure pin as analog

- 2. Configure the ADC module:

- Select ADC conversion clock

- · Configure voltage reference

- · Select ADC input channel

- · Select result format

- Turn on ADC module

- 3. Configure ADC interrupt (optional):

- · Clear ADC interrupt flag

- · Enable ADC interrupt

- Enable peripheral interrupt

- Enable global interrupt<sup>(1)</sup>

- 4. Wait the required acquisition time<sup>(2)</sup>.

- Start conversion by setting the GO/DONE bit.

- Wait for ADC conversion to complete by one of the following:

- Polling the GO/DONE bit

- Waiting for the ADC interrupt (interrupts enabled)

- 7. Read ADC Result

- Clear the ADC interrupt flag (required if interrupt is enabled).

- Note 1: The global interrupt can be disabled if the user is attempting to wake-up from Sleep and resume in-line code execution.

- 2: See Section 9.3 "A/D Acquisition Requirements".

#### **EXAMPLE 9-1:** A/D CONVERSION

```

;This code block configures the ADC

; for polling, Vdd reference, Frc clock

; and GPO input.

;Conversion start & polling for completion

; are included.

BANKSEL TRISIO

BSF

TRISIO,0

;Set GP0 to input

BANKSEL ANSEL

MOVLW

B'01110001'

; ADC Frc clock,

; and GPO as analog

IORWF

ANSEL

BANKSEL ADCONO

MOVLW

B'10000001' ; Right justify,

MOVWF

ADCON0

;Vdd Vref, ANO, On

CALL

SampleTime

;Acquisiton delay

BSF

ADCON0,GO

;Start conversion

BTFSC

ADCON0,GO

; Is conversion done?

COTO

$-1

;No, test again

BANKSEL

ADRESH

MOVF

ADRESH, W

;Read upper 2 bits

MOVWF

RESULTHI

;Store in GPR space

BANKSEL

ADRESL

;

MOVF

ADRESL, W

;Read lower 8 bits

MOVWE

RESULTIO

:Store in GPR space

```

#### 9.2.7 ADC REGISTER DEFINITIONS

The following registers are used to control the operation of the ADC.

TABLE 11-4: REGISTERS ASSOCIATED WITH CAPTURE, COMPARE AND TIMER1

| Name    | Bit 7                                                                        | Bit 6       | Bit 5          | Bit 4        | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|------------------------------------------------------------------------------|-------------|----------------|--------------|---------|---------|---------|---------|----------------------|---------------------------------|

| CCP1CON | _                                                                            | _           | DC1B1          | DC1B0        | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCPR1L  | Capture/Cor                                                                  | mpare/PWM F | Register 1 Lov | v Byte (LSB) |         |         |         |         | xxxx xxxx            | xxxx xxxx                       |

| CCPR1H  | Capture/Cor                                                                  | mpare/PWM F | Register 1 Hig | h Byte (MSB) | )       |         |         |         | xxxx xxxx            | xxxx xxxx                       |

| CMCON1  | _                                                                            | _           | _              | _            | _       | _       | T1GSS   | CMSYNC  | 10                   | 10                              |

| INTCON  | GIE                                                                          | PEIE        | TOIE           | INTE         | GPIE    | TOIF    | INTF    | GPIF    | 0000 0000            | 0000 000x                       |

| PIE1    | EEIE                                                                         | ADIE        | CCP1IE         | _            | CMIE    | OSFIE   | TMR2IE  | TMR1IE  | 000- 0000            | 000- 0000                       |

| PIR1    | EEIF                                                                         | ADIF        | CCP1IF         | _            | CMIF    | OSFIF   | TMR2IF  | TMR1IF  | 000- 0000            | 000- 0000                       |

| T1CON   | T1GINV                                                                       | TMR1GE      | T1CKPS1        | T1CKPS0      | T10SCEN | T1SYNC  | TMR1CS  | TMR10N  | 0000 0000            | 0000 0000                       |

| TMR1L   | Holding Register for the Least Significant Byte of the 16-bit TMR1 Register  |             |                |              |         |         |         |         | xxxx xxxx            | xxxx xxxx                       |

| TMR1H   | H Holding Register for the Most Significant Byte of the 16-bit TMR1 Register |             |                |              |         |         |         |         | xxxx xxxx            | xxxx xxxx                       |

| TRISIO  | _                                                                            | _           | TRISIO5        | TRISIO4      | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

Legend: -= Unimplemented locations, read as '0', u = unchanged, x = unknown. Shaded cells are not used by the Capture and Compare.

#### TABLE 11-5: REGISTERS ASSOCIATED WITH PWM AND TIMER2

| Name    | Bit 7                     | Bit 6       | Bit 5          | Bit 4        | Bit 3   | Bit 2   | Bit 1   | Bit 0   | Value on<br>POR, BOR | Value on<br>all other<br>Resets |

|---------|---------------------------|-------------|----------------|--------------|---------|---------|---------|---------|----------------------|---------------------------------|

| CCP1CON | _                         | _           | DC1B1          | DC1B0        | CCP1M3  | CCP1M2  | CCP1M1  | CCP1M0  | 00 0000              | 00 0000                         |

| CCPR1L  | Capture/Cor               | mpare/PWM F | Register 1 Lov | v Byte (LSB) |         |         |         |         | xxxx xxxx            | xxxx xxxx                       |

| CCPR1H  | Capture/Cor               | mpare/PWM F | Register 1 Hig | h Byte (MSB) | )       |         |         |         | xxxx xxxx            | xxxx xxxx                       |

| INTCON  | GIE                       | PEIE        | TOIE           | INTE         | GPIE    | TOIF    | INTF    | GPIF    | 0000 0000            | 0000 000x                       |

| PIE1    | EEIE                      | ADIE        | CCP1IE         | -            | CMIE    | OSFIE   | TMR2IE  | TMR1IE  | 000- 0000            | -000 0000                       |

| PIR1    | EEIF                      | ADIF        | CCP1IF         | -            | CMIF    | OSFIF   | TMR2IF  | TMR1IF  | 000- 0000            | -000 0000                       |

| PR2     | Timer2 Perio              | od Register |                |              |         |         |         |         | 1111 1111            | 1111 1111                       |

| T2CON   | _                         | TOUTPS3     | TOUTPS2        | TOUTPS1      | TOUTPS0 | TMR2ON  | T2CKPS1 | T2CKPS0 | -000 0000            | -000 0000                       |

| TMR2    | R2 Timer2 Module Register |             |                |              |         |         |         |         |                      | 0000 0000                       |

| TRISIO  | _                         | _           | TRISIO5        | TRISIO4      | TRISIO3 | TRISIO2 | TRISIO1 | TRISIO0 | 11 1111              | 11 1111                         |

$\textbf{Legend:} \quad - = \text{Unimplemented locations, read as `0', u = unchanged, } \\ x = \text{unknown. Shaded cells are not used by the PWM.}$

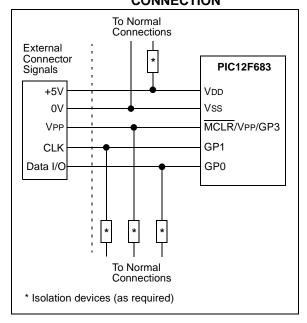

#### 12.10 In-Circuit Serial Programming™

The PIC12F683 microcontrollers can be serially programmed while in the end application circuit. This is simply done with five connections for:

- clock

- data

- power

- ground

- · programming voltage

This allows customers to manufacture boards with unprogrammed devices and then program the micro-controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

The device is placed into a Program/Verify mode by holding the GP0 and GP1 pins low, while raising the MCLR (VPP) pin from VIL to VIHH. See the "PIC12F6XX/16F6XX Memory Programming Specification" (DS41204) for more information. GP0 becomes the programming data and GP1 becomes the programming clock. Both GP0 and GP1 are Schmitt Trigger inputs in Program/Verify mode.

A typical In-Circuit Serial Programming connection is shown in Figure 12-11.

FIGURE 12-11: TYPICAL IN-CIRCUIT SERIAL PROGRAMMING CONNECTION

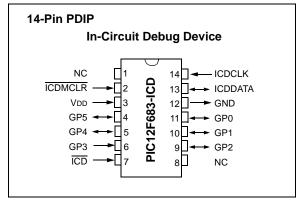

### 12.11 In-Circuit Debugger

Since in-circuit debugging requires access to three pins, MPLAB® ICD 2 development with a 14-pin device is not practical. A special 14-pin PIC12F683 ICD device is used with MPLAB ICD 2 to provide separate clock, data and MCLR pins and frees all normally available pins to the user.

A special debugging adapter allows the ICD device to be used in place of a PIC12F683 device. The debugging adapter is the only source of the ICD device.

When the ICD pin on the PIC12F683 ICD device is held low, the In-Circuit Debugger functionality is enabled. This function allows simple debugging functions when used with MPLAB ICD 2. When the microcontroller has this feature enabled, some of the resources are not available for general use. Table 12-9 shows which features are consumed by the background debugger.

TABLE 12-9: DEBUGGER RESOURCES

| Resource       | Description                         |

|----------------|-------------------------------------|

| Stack          | 1 level                             |

| Program Memory | Address 0h must be NOP<br>700h-7FFh |

For more information, see "MPLAB® ICD 2 In-Circuit Debugger User's Guide" (DS51331), available on Microchip's web site (www.microchip.com).

FIGURE 12-12: 14-PIN ICD PINOUT

#### 13.0 INSTRUCTION SET SUMMARY

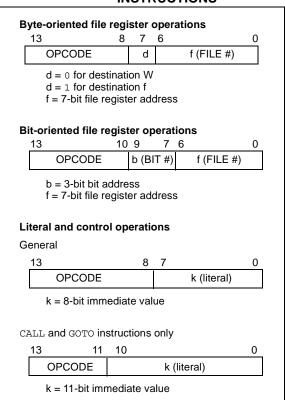

The PIC12F683 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- · Bit-oriented operations

- · Literal and control operations

Each PIC16 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type and one or more **operands**, which further specify the operation of the instruction. The formats for each of the categories is presented in Figure 13-1, while the various opcode fields are summarized in Table 13-1.

Table 13-2 lists the instructions recognized by the MPASM $^{TM}$  assembler.

For **byte-oriented** instructions, 'f' represents a file register designator and 'd' represents a destination designator. The file register designator specifies which file register is to be used by the instruction.

The destination designator specifies where the result of the operation is to be placed. If 'd' is zero, the result is placed in the W register. If 'd' is one, the result is placed in the file register specified in the instruction.

For **bit-oriented** instructions, 'b' represents a bit field designator, which selects the bit affected by the operation, while 'f' represents the address of the file in which the bit is located.

For **literal and control** operations, 'k' represents an 8-bit or 11-bit constant, or literal value.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a nominal instruction execution time of 1  $\mu s$ . All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

All instruction examples use the format '0xhh' to represent a hexadecimal number, where 'h' signifies a hexadecimal digit.

#### 13.1 Read-Modify-Write Operations

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

For example, a CLRF PORTA instruction will read PORTA, clear all the data bits, then write the result back to PORTA. This example would have the unintended consequence of clearing the condition that set the RAIF flag.

TABLE 13-1: OPCODE FIELD DESCRIPTIONS

| Field | Description                                                                                                                                                           |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| f     | Register file address (0x00 to 0x7F)                                                                                                                                  |

| W     | Working register (accumulator)                                                                                                                                        |

| b     | Bit address within an 8-bit file register                                                                                                                             |

| k     | Literal field, constant data or label                                                                                                                                 |

| х     | Don't care location (= 0 or 1).  The assembler will generate code with x = 0.  It is the recommended form of use for compatibility with all Microchip software tools. |

| d     | Destination select; d = 0: store result in W,<br>d = 1: store result in file register f.<br>Default is d = 1.                                                         |

| PC    | Program Counter                                                                                                                                                       |

| TO    | Time-out bit                                                                                                                                                          |

| С     | Carry bit                                                                                                                                                             |

| DC    | Digit carry bit                                                                                                                                                       |

| Z     | Zero bit                                                                                                                                                              |

| PD    | Power-down bit                                                                                                                                                        |

# FIGURE 13-1: GENERAL FORMAT FOR INSTRUCTIONS

## 15.0 ELECTRICAL SPECIFICATIONS

# Absolute Maximum Ratings(†)

| Ambient temperature under bias                                                             | 40° to +125°C                                                |

|--------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| Storage temperature                                                                        | 65°C to +150°C                                               |

| Voltage on VDD with respect to Vss                                                         | -0.3V to +6.5V                                               |

| Voltage on MCLR with respect to Vss                                                        | 0.3V to +13.5V                                               |

| Voltage on all other pins with respect to Vss                                              | 0.3V to (VDD + 0.3V)                                         |

| Total power dissipation <sup>(1)</sup>                                                     | 800 mW                                                       |

| Maximum current out of Vss pin                                                             | 95 mA                                                        |

| Maximum current into VDD pin                                                               | 95 mA                                                        |

| Input clamp current, Iik (VI < 0 or VI > VDD)                                              | ± 20 mA                                                      |

| Output clamp current, loκ (Vo < 0 or Vo >VDD)                                              | ± 20 mA                                                      |

| Maximum output current sunk by any I/O pin                                                 | 25 mA                                                        |

| Maximum output current sourced by any I/O pin                                              | 25 mA                                                        |

| Maximum current sunk by GPIO                                                               | 90 mA                                                        |

| Maximum current sourced GPIO                                                               | 90 mA                                                        |

| <b>Note 1:</b> Power dissipation is calculated as follows: PDIS = VDD x {IDD $-\sum IOH$ } | + $\sum \{(VDD - VOH) \times IOH\} + \sum (VOI \times IOL).$ |

† NOTICE: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure above maximum rating conditions for extended periods may affect device reliability.

# 15.5 DC Characteristics: PIC12F683-I (Industrial) PIC12F683-E (Extended) (Continued)

| DC CH        | ARACTE | RISTICS                                                          | Standard Operating Conditions (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for extended |      |     |       |                                                                                                     |  |

|--------------|--------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-----------------------------------------------------------------------------------------------------|--|

| Param<br>No. | Sym    | Characteristic                                                   | Min                                                                                                                                                                                                                                | Тур† | Max | Units | Conditions                                                                                          |  |

| D100         | lulp   | Ultra Low-Power Wake-Up<br>Current                               | _                                                                                                                                                                                                                                  | 200  | _   | nA    | See Application Note AN879,<br>"Using the Microchip Ultra<br>Low-Power Wake-up Module"<br>(DS00879) |  |

|              |        | Capacitive Loading Specs on<br>Output Pins                       |                                                                                                                                                                                                                                    |      |     |       |                                                                                                     |  |

| D101*        | COSC2  | OSC2 pin                                                         | _                                                                                                                                                                                                                                  | _    | 15  | pF    | In XT, HS and LP modes when external clock is used to drive OSC1                                    |  |

| D101A*       | Cio    | All I/O pins                                                     | _                                                                                                                                                                                                                                  | _    | 50  | pF    |                                                                                                     |  |

|              |        | Data EEPROM Memory                                               |                                                                                                                                                                                                                                    |      |     |       |                                                                                                     |  |

| D120         | ED     | Byte Endurance                                                   | 100K                                                                                                                                                                                                                               | 1M   | _   | E/W   | -40°C ≤ TA ≤ +85°C                                                                                  |  |

| D120A        | ED     | Byte Endurance                                                   | 10K                                                                                                                                                                                                                                | 100K | _   | E/W   | +85°C ≤ TA ≤ +125°C                                                                                 |  |

| D121         | VDRW   | VDD for Read/Write                                               | VMIN                                                                                                                                                                                                                               | _    | 5.5 | V     | Using EECON1 to read/write VMIN = Minimum operating voltage                                         |  |

| D122         | TDEW   | Erase/Write Cycle Time                                           | _                                                                                                                                                                                                                                  | 5    | 6   | ms    |                                                                                                     |  |

| D123         | TRETD  | Characteristic Retention                                         | 40                                                                                                                                                                                                                                 | _    | _   | Year  | Provided no other specifications are violated                                                       |  |

| D124         | TREF   | Number of Total Erase/Write Cycles before Refresh <sup>(4)</sup> | 1M                                                                                                                                                                                                                                 | 10M  | _   | E/W   | -40°C ≤ TA ≤ +85°C                                                                                  |  |

|              |        | Program Flash Memory                                             |                                                                                                                                                                                                                                    |      |     |       |                                                                                                     |  |

| D130         | Ep     | Cell Endurance                                                   | 10K                                                                                                                                                                                                                                | 100K | _   | E/W   | -40°C ≤ TA ≤ +85°C                                                                                  |  |

| D130A        | ED     | Cell Endurance                                                   | 1K                                                                                                                                                                                                                                 | 10K  | _   | E/W   | +85°C ≤ TA ≤ +125°C                                                                                 |  |

| D131         | VPR    | VDD for Read                                                     | VMIN                                                                                                                                                                                                                               |      | 5.5 | V     | VMIN = Minimum operating voltage                                                                    |  |

| D132         | VPEW   | VDD for Erase/Write                                              | 4.5                                                                                                                                                                                                                                |      | 5.5 | V     |                                                                                                     |  |

| D133         | TPEW   | Erase/Write cycle time                                           | _                                                                                                                                                                                                                                  | 2    | 2.5 | ms    |                                                                                                     |  |

| D134         | TRETD  | Characteristic Retention                                         | 40                                                                                                                                                                                                                                 |      | _   | Year  | Provided no other specifications are violated                                                       |  |

<sup>\*</sup> These parameters are characterized but not tested.

Note 1: In RC oscillator configuration, the OSC1/CLKIN pin is a Schmitt Trigger input. It is not recommended to use an external clock in RC mode.

- 2: Negative current is defined as current sourced by the pin.

- 3: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 4: See Section 10.4.1 "Using the Data EEPROM" for additional information.

- 5: Including OSC2 in CLKOUT mode.

<sup>†</sup> Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

#### TABLE 15-2: OSCILLATOR PARAMETERS

| Standard Operating Conditions (unless otherwise stated) Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |                                   |                                                        |                    |      |      |      |                  |                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------------------------------------------|--------------------|------|------|------|------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Param<br>No.                                                                                                                               | Sym                               | Characteristic                                         | Freq.<br>Tolerance | Min  | Тур† | Max  | Units            | Conditions                                                                                                                      |

| OS06                                                                                                                                       | TWARM                             | Internal Oscillator Switch when running <sup>(3)</sup> | _                  | _    | _    | 2    | Tosc             | Slowest clock                                                                                                                   |

| OS07                                                                                                                                       | Tsc                               | Fail-Safe Sample Clock<br>Period <sup>(1)</sup>        | _                  | _    | 21   | _    | ms               | LFINTOSC/64                                                                                                                     |

| OS08 HFosc Internal Calibrated                                                                                                             |                                   | ±1%                                                    | 7.92               | 8.0  | 8.08 | MHz  | VDD = 3.5V, 25°C |                                                                                                                                 |

|                                                                                                                                            | HFINTOSC Frequency <sup>(2)</sup> |                                                        | ±2%                | 7.84 | 8.0  | 8.16 | MHz              | $2.5V \le VDD \le 5.5V$ ,<br>$0^{\circ}C \le TA \le +85^{\circ}C$                                                               |

|                                                                                                                                            |                                   |                                                        | ±5%                | 7.60 | 8.0  | 8.40 | MHz              | $2.0V \le VDD \le 5.5V$ ,<br>- $40^{\circ}C \le TA \le +85^{\circ}C$ (Ind.),<br>- $40^{\circ}C \le TA \le +125^{\circ}C$ (Ext.) |

| OS09*                                                                                                                                      | LFosc                             | Internal Uncalibrated LFINTOSC Frequency               | _                  | 15   | 31   | 45   | kHz              |                                                                                                                                 |

| OS10*                                                                                                                                      | Tiosc                             | HFINTOSC Oscillator                                    | _                  | 5.5  | 12   | 24   | μs               | $VDD = 2.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                             |

|                                                                                                                                            | ST                                | Wake-up from Sleep<br>Start-up Time                    | _                  | 3.5  | 7    | 14   | μs               | $VDD = 3.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                             |

|                                                                                                                                            |                                   |                                                        | _                  | 3    | 6    | 11   | μs               | $VDD = 5.0V, -40^{\circ}C \text{ to } +85^{\circ}C$                                                                             |

- \* These parameters are characterized but not tested.

- † Data in "Typ" column is at 5.0V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

- Note 1: Instruction cycle period (TcY) equals four times the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min" values with an external clock applied to the OSC1 pin. When an external clock input is used, the "max" cycle time limit is "DC" (no clock) for all devices.

- 2: To ensure these oscillator frequency tolerances, VDD and Vss must be capacitively decoupled as close to the device as possible.  $0.1~\mu F$  and  $0.01~\mu F$  values in parallel are recommended.

- 3: By design.

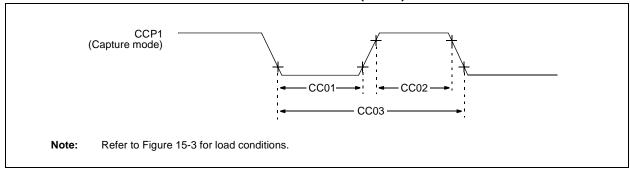

## FIGURE 15-9: CAPTURE/COMPARE/PWM TIMINGS (ECCP)

## TABLE 15-6: CAPTURE/COMPARE/PWM REQUIREMENTS (ECCP)

| Standard Operating Conditions (unless otherwise stated)  Operating Temperature $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ |      |                      |                |                |      |     |       |                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------|------|----------------------|----------------|----------------|------|-----|-------|---------------------------------------|

| Param<br>No.                                                                                                                                | Sym  | Characteristic       |                | Min            | Тур† | Max | Units | Conditions                            |

| CC01*                                                                                                                                       | TccL | CCP1 Input Low Time  | No Prescaler   | 0.5Tcy + 20    | _    | _   | ns    |                                       |

|                                                                                                                                             |      |                      | With Prescaler | 20             | _    | _   | ns    |                                       |

| CC02*                                                                                                                                       | TccH | CCP1 Input High Time | No Prescaler   | 0.5Tcy + 20    | _    | _   | ns    |                                       |

|                                                                                                                                             |      |                      | With Prescaler | 20             | _    | _   | ns    |                                       |

| CC03*                                                                                                                                       | TccP | CCP1 Input Period    |                | 3Tcy + 40<br>N | _    | _   | ns    | N = prescale<br>value (1, 4 or<br>16) |

<sup>\*</sup> These parameters are characterized but not tested.

<sup>†</sup> Data in "Typ" column is at 5V, 25°C unless otherwise stated. These parameters are for design guidance only and are not tested.

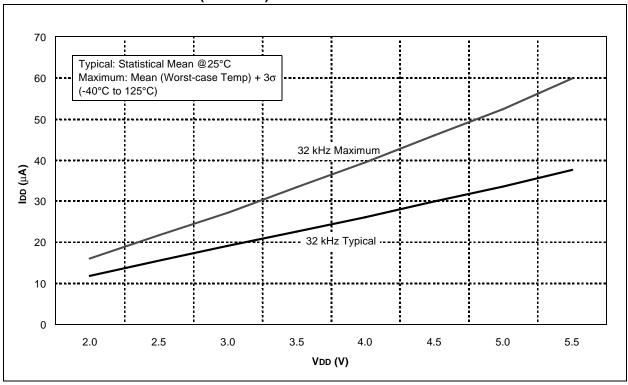

FIGURE 16-10: IDD vs. VDD (LP MODE)

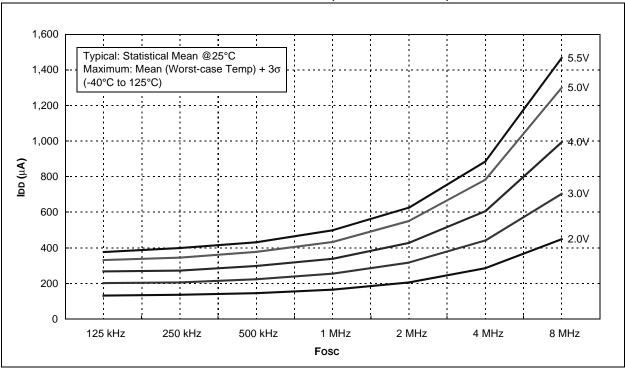

FIGURE 16-11: TYPICAL IDD vs. FOSC OVER VDD (HFINTOSC MODE)

NOTES:

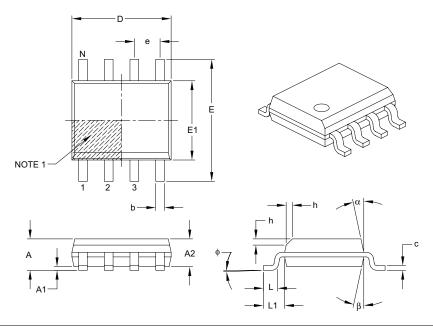

## 8-Lead Plastic Small Outline (SN or OA) - Narrow, 3.90 mm Body [SOIC]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units            | MILLIMETERS |          |      |  |  |

|--------------------------|------------------|-------------|----------|------|--|--|

|                          | Dimension Limits | MIN         | NOM      | MAX  |  |  |

| Number of Pins           | N                |             | 8        |      |  |  |

| Pitch                    | е                |             | 1.27 BSC |      |  |  |

| Overall Height           | А                | _           | _        | 1.75 |  |  |

| Molded Package Thickness | A2               | 1.25        | -        | _    |  |  |

| Standoff §               | A1               | 0.10        | -        | 0.25 |  |  |

| Overall Width            | E                | 6.00 BSC    |          |      |  |  |

| Molded Package Width     | E1               | 3.90 BSC    |          |      |  |  |

| Overall Length           | D                | 4.90 BSC    |          |      |  |  |

| Chamfer (optional)       | h                | 0.25        | -        | 0.50 |  |  |

| Foot Length              | L                | 0.40        | -        | 1.27 |  |  |

| Footprint                | L1               | 1.04 REF    |          |      |  |  |

| Foot Angle               | ф                | 0°          | -        | 8°   |  |  |

| Lead Thickness           | С                | 0.17        | _        | 0.25 |  |  |

| Lead Width               | b                | 0.31        | _        | 0.51 |  |  |

| Mold Draft Angle Top     | α                | 5°          | _        | 15°  |  |  |

| Mold Draft Angle Bottom  | β                | 5°          | -        | 15°  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. § Significant Characteristic.

- 3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.15 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-057B

### **READER RESPONSE**

то.

It is our intention to provide you with the best documentation possible to ensure successful use of your Microchip product. If you wish to provide your comments on organization, clarity, subject matter, and ways in which our documentation can better serve you, please FAX your comments to the Technical Publications Manager at (480) 792-4150.

Please list the following information, and use this outline to provide us with your comments about this document.

| RE: | Reader Response                                                            | Total Pages Sent                                        |  |  |  |  |  |

|-----|----------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|--|--|

|     | m: Name                                                                    |                                                         |  |  |  |  |  |

|     | Telephone: ()                                                              | FAX: ()                                                 |  |  |  |  |  |

|     | lication (optional):                                                       |                                                         |  |  |  |  |  |

| Wou | uld you like a reply?YN                                                    |                                                         |  |  |  |  |  |

| Dev | rice: PIC12F683                                                            | Literature Number: DS41211D                             |  |  |  |  |  |

| Que | estions:                                                                   |                                                         |  |  |  |  |  |

| 1.  | What are the best features of this do                                      | ocument?                                                |  |  |  |  |  |

| 2.  | How does this document meet your                                           | hardware and software development needs?                |  |  |  |  |  |

| 3.  | Do you find the organization of this document easy to follow? If not, why? |                                                         |  |  |  |  |  |

| 4.  | What additions to the document do                                          | you think would enhance the structure and subject?      |  |  |  |  |  |

| 5.  | What deletions from the document of                                        | could be made without affecting the overall usefulness? |  |  |  |  |  |

|     |                                                                            |                                                         |  |  |  |  |  |

| 6.  | Is there any incorrect or misleading                                       | information (what and where)?                           |  |  |  |  |  |

| 7.  | How would you improve this docum                                           | ent?                                                    |  |  |  |  |  |

|     |                                                                            |                                                         |  |  |  |  |  |