Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Active                                                      |

| Number of LABs/CLBs            | 3840                                                        |

| Number of Logic Elements/Cells | 38400                                                       |

| Total RAM Bits                 | 327680                                                      |

| Number of I/O                  | 708                                                         |

| Number of Gates                | 1772000                                                     |

| Voltage - Supply               | 1.71V ~ 1.89V                                               |

| Mounting Type                  | Surface Mount                                               |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                             |

| Package / Case                 | 1020-BBGA                                                   |

| Supplier Device Package        | 1020-FBGA (33x33)                                           |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k1000cf33c9n |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Advanced interconnect structure

- Copper interconnect for high performance

- Four-level hierarchical FastTrack® interconnect structure providing fast, predictable interconnect delays

- Dedicated carry chain that implements arithmetic functions such as fast adders, counters, and comparators (automatically used by software tools and megafunctions)

- Dedicated cascade chain that implements high-speed, high-fan-in logic functions (automatically used by software tools and megafunctions)

- Interleaved local interconnect allows one LE to drive 29 other LEs through the fast local interconnect

- Advanced software support

- Software design support and automatic place-and-route provided by the Altera® Quartus<sup>TM</sup> II development system for Windows-based PCs, Sun SPARCstations, and HP 9000 Series 700/800 workstations

- Altera MegaCore® functions and Altera Megafunction Partners Program (AMPPSM) megafunctions optimized for APEX 20KC architecture available

- NativeLink<sup>TM</sup> integration with popular synthesis, simulation, and timing analysis tools

- Quartus II SignalTap® embedded logic analyzer simplifies in-system design evaluation by giving access to internal nodes during device operation

- Supports popular revision-control software packages including PVCS, RCS, and SCCS

| Table 3. APE | X 20KC QFP & BC | GA Package Option | ons & I/O Count | Notes (1), (2) |

|--------------|-----------------|-------------------|-----------------|----------------|

| Device       | 208-Pin PQFP    | 240-Pin PQFP      | 356-Pin BGA     | 652-Pin BGA    |

| EP20K200C    | 136             | 168               | 271             |                |

| EP20K400C    |                 |                   |                 | 488            |

| EP20K600C    |                 |                   |                 | 488            |

| EP20K1000C   |                 |                   |                 | 488            |

APEX 20KC devices include additional features such as enhanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. Table 7 shows the features included in APEX 20KC devices.

| Table 7. APEX 20KC Device Fea  | tures (Part 1 of 2)                                                                                                                                                                                     |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feature                        | APEX 20KC Devices                                                                                                                                                                                       |

| MultiCore system integration   | Full support                                                                                                                                                                                            |

| Hot-socketing support          | Full support                                                                                                                                                                                            |

| SignalTap logic analysis       | Full support                                                                                                                                                                                            |

| 32-/64-bit, 33-MHz PCI         | Full compliance                                                                                                                                                                                         |

| 32-/64-bit, 66-MHz PCI         | Full compliance in -7 and -8 speed grades in selected devices                                                                                                                                           |

| MultiVolt I/O                  | 1.8-V, 2.5-V, or 3.3-V V <sub>CCIO</sub> V <sub>CCIO</sub> selected bank by bank 5.0-V tolerant with use of external resistor                                                                           |

| ClockLock support              | Clock delay reduction  m/(n × v) clock multiplication  Drive ClockLock output off-chip  External clock feedback  ClockShift circuitry  LVDS support  Up to four PLLs  ClockShift clock phase adjustment |

| Dedicated clock and input pins | Eight                                                                                                                                                                                                   |

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Row Interconnect

MegaLAB Interconnect

Column Interconnect

Interconnect

Figure 11. Driving the FastTrack Interconnect

APEX 20KC devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow<sup>TM</sup> interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. The FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K400C and larger devices, the FastRow interconnect drives the two MegaLAB structures in the top left corner, the two MegaLAB structures in the two right corner, the two MegaLAB structures in the bottom left corner, and the two MegaLAB structures in the bottom right corner. On EP20K200C and smaller devices, FastRow interconnect drives the two MegaLAB structures on the top and the two MegaLAB structures on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLAB structures except the end local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

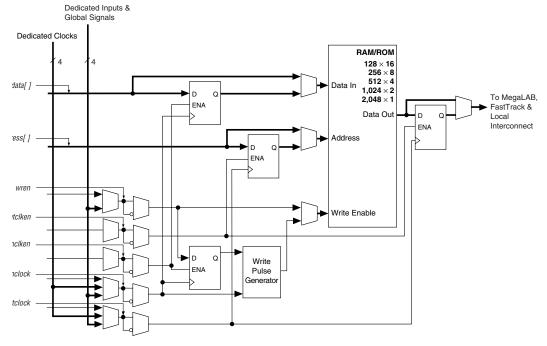

The programmable register also supports an asynchronous clear function. Within the ESB, two asynchronous clears are generated from global signals and the local interconnect. Each macrocell can either choose between the two asynchronous clear signals or choose to not be cleared. Either of the two clear signals can be inverted within the ESB. Figure 15 shows the ESB control logic when implementing product-terms.

Dedicated Clocks Global Signals Local Interconnect Local Interconnect Local Interconnect Local Interconnect CLKENA2 CLK1 CLKENA1 CLR<sub>1</sub>

Figure 15. ESB Product-Term Mode Control Logic

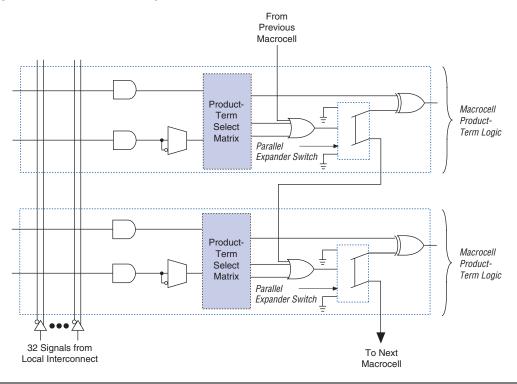

#### Parallel Expanders

Parallel expanders are unused product terms that can be allocated to a neighboring macrocell to implement fast, complex logic functions. Parallel expanders allow up to 32 product terms to feed the macrocell OR logic directly, with two product terms provided by the macrocell and 30 parallel expanders provided by the neighboring macrocells in the ESB.

The Quartus II Compiler can allocate up to 15 sets of up to two parallel expanders per set to the macrocells automatically. Each set of two parallel expanders incurs a small, incremental timing delay. Figure 16 shows the APEX 20KC parallel expanders.

Figure 16. APEX 20KC Parallel Expanders

# Embedded System Block

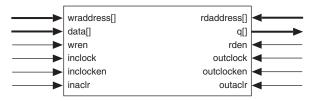

The ESB can implement various types of memory blocks, including dual-port RAM, ROM, FIFO, and CAM blocks. The ESB includes input and output registers; the input registers synchronize writes, and the output registers can pipeline designs to improve system performance. The ESB offers a dual-port mode, which supports simultaneous reads and writes at two different clock frequencies. Figure 17 shows the ESB block diagram.

Figure 17. ESB Block Diagram

#### Read/Write Clock Mode

The read/write clock mode contains two clocks. One clock controls all registers associated with writing: data input, WE, and write address. The other clock controls all registers associated with reading: read enable (RE), read address, and data output. The ESB also supports clock enable and asynchronous clear signals; these signals also control the read and write registers independently. Read/write clock mode is commonly used for applications where reads and writes occur at different system frequencies. Figure 20 shows the ESB in read/write clock mode.

Figure 20. ESB in Read/Write Clock Mode Note (1)

Note to Figure 20:

(1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

CAM is used for high-speed search operations. When searching for data within a RAM block, the search is performed serially. Thus, finding a particular data word can take many cycles. CAM searches all addresses in parallel and outputs the address storing a particular word. When a match is found, a match flag is set high. Figure 23 shows the CAM block diagram.

### Implementing Logic in ROM

In addition to implementing logic with product terms, the ESB can implement logic functions when it is programmed with a read-only pattern during configuration, creating a large LUT. With LUTs, combinatorial functions are implemented by looking up the results, rather than by computing them. This implementation of combinatorial functions can be faster than using algorithms implemented in general logic, a performance advantage that is further enhanced by the fast access times of ESBs. The large capacity of ESBs enables designers to implement complex functions in one logic level without the routing delays associated with linked LEs or distributed RAM blocks. Parameterized functions such as LPM functions can take advantage of the ESB automatically. Further, the Quartus II software can implement portions of a design with ESBs where appropriate.

### **Programmable Speed/Power Control**

APEX 20KC ESBs offer a high-speed mode that supports very fast operation on an ESB-by-ESB basis. When high speed is not required, this feature can be turned off to reduce the ESB's power dissipation by up to 50%. ESBs that run at low power incur a nominal timing delay adder. This Turbo Bit<sup>TM</sup> option is available for ESBs that implement product-term logic or memory functions. An ESB that is not used will be powered down so that it does not consume DC current.

Designers can program each ESB in the APEX 20KC device for either high-speed or low-power operation. As a result, speed-critical paths in the design can run at high speed, while the remaining paths operate at reduced power.

## I/O Structure

The APEX 20KC IOE contains a bidirectional I/O buffer and a register that can be used either as an input register for external data requiring fast setup times or as an output register for data requiring fast clock-to-output performance. IOEs can be used as input, output, or bidirectional pins.

| Table 12. Al            | PEX 20KC Clock Input & Outp | ut Parameters (Pa | rt 2 of 2) | Note (  | 1)      |         |       |

|-------------------------|-----------------------------|-------------------|------------|---------|---------|---------|-------|

| Symbol                  | Parameter                   | I/O Standard      | -7 Spee    | d Grade | -8 Spee | d Grade | Units |

|                         |                             |                   | Min        | Max     | Min     | Max     |       |

| f <sub>CLOCK1_EXT</sub> | Output clock frequency for  | 3.3-V LVTTL       | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         | external clock1 output      | 2.5-V LVTTL       | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | 1.8-V LVTTL       | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | GTL+              | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-2 Class I    | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-2 Class II   | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-3 Class I    | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-3 Class II   | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | LVDS              | (5)        | (5)     | (5)     | (5)     | MHz   |

| $f_{IN}$                | Input clock frequency       | 3.3-V LVTTL       | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | 2.5-V LVTTL       | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | 1.8-V LVTTL       | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | GTL+              | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-2 Class I    | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-2 Class II   | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-3 Class I    | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | SSTL-3 Class II   | (5)        | (5)     | (5)     | (5)     | MHz   |

|                         |                             | LVDS              | (5)        | (5)     | (5)     | (5)     | MHz   |

#### Notes to Tables 11 and 12:

- All input clock specifications must be met. The PLL may not lock onto an incoming clock if the clock specifications

are not met, creating an erroneous clock within the device.

- (2) The maximum lock time is  $40 \mu s$  or 2,000 input clock cycles, whichever occurs first.

- (3) Before configuration, the PLL circuits are disable and powered down. During configuration, the PLLs remain disabled. The PLLs begin to lock once the device is in the user mode. If the clock enable feature is used, lock begins once the CLKLK ENA pin goes high in user mode.

- (4) The PLL VCO operating range is 200 MHz  $\leq f_{VCO} \leq$  840 MHz for LVDS mode.

- (5) Contact Altera Applications for information on these parameters.

# SignalTap Embedded Logic Analyzer

APEX 20KC devices include device enhancements to support the SignalTap embedded logic analyzer. By including this circuitry, the APEX 20KC device provides the ability to monitor design operation over a period of time through the IEEE Std. 1149.1 (JTAG) circuitry; a designer can analyze internal logic at speed without bringing internal signals to the I/O pins. This feature is particularly important for advanced packages such as FineLine BGA packages because adding a connection to a pin during the debugging process can be difficult after a board is designed and manufactured.

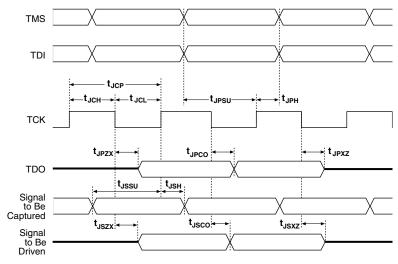

Figure 30. APEX 20KC JTAG Waveforms

Table 16 shows the JTAG timing parameters and values for APEX 20KC devices.

| Table 1           | 6. APEX 20KC JTAG Timing Parameters & Values   | •   |     |      |

|-------------------|------------------------------------------------|-----|-----|------|

| Symbol            | Parameter                                      | Min | Max | Unit |

| t <sub>JCP</sub>  | TCK clock period                               | 100 |     | ns   |

| t <sub>JCH</sub>  | TCK clock high time                            | 50  |     | ns   |

| t <sub>JCL</sub>  | TCK clock low time                             | 50  |     | ns   |

| t <sub>JPSU</sub> | JTAG port setup time                           | 20  |     | ns   |

| t <sub>JPH</sub>  | JTAG port hold time                            | 45  |     | ns   |

| t <sub>JPCO</sub> | JTAG port clock to output                      |     | 25  | ns   |

| t <sub>JPZX</sub> | JTAG port high impedance to valid output       |     | 25  | ns   |

| t <sub>JPXZ</sub> | JTAG port valid output to high impedance       |     | 25  | ns   |

| t <sub>JSSU</sub> | Capture register setup time                    | 20  |     | ns   |

| t <sub>JSH</sub>  | Capture register hold time                     | 45  |     | ns   |

| t <sub>JSCO</sub> | Update register clock to output                |     | 35  | ns   |

| t <sub>JSZX</sub> | Update register high impedance to valid output |     | 35  | ns   |

| t <sub>JSXZ</sub> | Update register valid output to high impedance |     | 35  | ns   |

For more information, see the following documents:

Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

| Table 32. SS      | TL-3 Class II Specifica   | tions                               |                         |                  |                         |       |

|-------------------|---------------------------|-------------------------------------|-------------------------|------------------|-------------------------|-------|

| Symbol            | Parameter                 | Conditions                          | Minimum                 | Typical          | Maximum                 | Units |

| V <sub>CCIO</sub> | I/O supply voltage        |                                     | 3.0                     | 3.3              | 3.6                     | V     |

| V <sub>TT</sub>   | Termination voltage       |                                     | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V     |

| V <sub>REF</sub>  | Reference voltage         |                                     | 1.3                     | 1.5              | 1.7                     | V     |

| V <sub>IH</sub>   | High-level input voltage  |                                     | V <sub>REF</sub> + 0.2  |                  | V <sub>CCIO</sub> + 0.3 | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                                     | -0.3                    |                  | V <sub>REF</sub> – 0.2  | V     |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OH</sub> = -16 mA <i>(1)</i> | V <sub>TT</sub> + 0.8   |                  |                         | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 16 mA (2)         |                         |                  | V <sub>TT</sub> – 0.8   | V     |

| Table 33. HS      | TL Class I I/O Specific   | ations                        |                         |                  |                         |       |

|-------------------|---------------------------|-------------------------------|-------------------------|------------------|-------------------------|-------|

| Symbol            | Parameter                 | Conditions                    | Minimum                 | Typical          | Maximum                 | Units |

| V <sub>CCIO</sub> | I/O supply voltage        |                               | 1.71                    | 1.8              | 1.89                    | ٧     |

| V <sub>TT</sub>   | Termination voltage       |                               | V <sub>REF</sub> - 0.05 | V <sub>REF</sub> | V <sub>REF</sub> + 0.05 | V     |

| V <sub>REF</sub>  | Reference voltage         |                               | 0.68                    | 0.75             | 0.90                    | V     |

| V <sub>IH</sub>   | High-level input voltage  |                               | V <sub>REF</sub> + 0.1  |                  | V <sub>CCIO</sub> + 0.3 | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                               | -0.3                    |                  | V <sub>REF</sub> – 0.1  | V     |

| V <sub>OH</sub>   | High-level output voltage | $I_{OH} = -8 \text{ mA } (1)$ | V <sub>CCIO</sub> - 0.4 |                  |                         | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OL</sub> = 8 mA (2)    |                         |                  | 0.4                     | V     |

| Symbol            | Parameter                 | Conditions                              | Minimum                 | Typical | Maximum                  | Units |

|-------------------|---------------------------|-----------------------------------------|-------------------------|---------|--------------------------|-------|

| V <sub>CCIO</sub> | I/O supply voltage        |                                         | 3.15                    | 3.3     | 3.45                     | V     |

| V <sub>REF</sub>  | Reference voltage         |                                         | $0.39 \times V_{CCIO}$  |         | 0.41 × V <sub>CCIO</sub> | ٧     |

| V <sub>IH</sub>   | High-level input voltage  |                                         | 0.5 × V <sub>CCIO</sub> |         | V <sub>CCIO</sub> + 0.5  | V     |

| V <sub>IL</sub>   | Low-level input voltage   |                                         |                         |         | 0.3 × V <sub>CCIO</sub>  | V     |

| V <sub>OH</sub>   | High-level output voltage | I <sub>OUT</sub> = -500 μA              | 0.9 × V <sub>CCIO</sub> |         | 3.6                      | V     |

| V <sub>OL</sub>   | Low-level output voltage  | I <sub>OUT</sub> = 1,500 μA             |                         |         | 0.1 × V <sub>CCIO</sub>  | V     |

| I <sub>I</sub>    | Input pin leakage current | 0 < V <sub>IN</sub> < V <sub>CCIO</sub> | -10                     |         | 10                       | μΑ    |

| Table 35. CT                          | T I/O Specifications                           |                                         |                        |         |                        |       |

|---------------------------------------|------------------------------------------------|-----------------------------------------|------------------------|---------|------------------------|-------|

| Symbol                                | Parameter                                      | Conditions                              | Minimum                | Typical | Maximum                | Units |

| V <sub>CCIO</sub>                     | I/O supply voltage                             |                                         | 3.0                    | 3.3     | 3.6                    | V     |

| V <sub>TT</sub> /V <sub>REF</sub> (3) | Termination and reference voltage              |                                         | 1.35                   | 1.5     | 1.65                   | V     |

| V <sub>IH</sub>                       | High-level input voltage                       |                                         | V <sub>REF</sub> + 0.2 |         |                        | V     |

| V <sub>IL</sub>                       | Low-level input voltage                        |                                         |                        |         | V <sub>REF</sub> – 0.2 | V     |

| I <sub>I</sub>                        | Input pin leakage current                      | 0 < V <sub>IN</sub> < V <sub>CCIO</sub> | -10                    |         | 10                     | μА    |

| V <sub>OH</sub>                       | High-level output voltage                      | $I_{OH} = -8 \text{ mA } (1)$           | V <sub>REF</sub> + 0.4 |         |                        | V     |

| V <sub>OL</sub>                       | Low-level output voltage                       | I <sub>OL</sub> = 8 mA (2)              |                        |         | V <sub>REF</sub> – 0.4 | V     |

| I <sub>O</sub>                        | Output leakage current (when output is high Z) | $GND \le V_{OUT} \le V_{CCIO}$          | -10                    |         | 10                     | μА    |

#### Notes to Tables 21 through 35:

- (1) The I<sub>OH</sub> parameter refers to high-level output current.

- (2) The  $I_{OL}$  parameter refers to low-level output current. This parameter applies to open-drain pins as well as output pins.

- (3)  $\hat{V}_{REF}$  specifies center point of switching range.

Figure 31 shows the output drive characteristics of APEX 20KC devices.

# **Timing Model**

The high-performance FastTrack and MegaLAB interconnect routing resources ensure predictable performance, accurate simulation, and accurate timing analysis. This predictable performance contrasts with that of FPGAs, which use a segmented connection scheme and therefore have unpredictable performance.

Figure 32 shows the  $f_{MAX}$  timing model for APEX 20KC devices.

<sup>t</sup>su Routing Delay  $t_H$ t<sub>F1-4</sub> <sup>t</sup>co <sup>t</sup> F5—20  $^t$ LUT <sup>t</sup> F20+ ESB t<sub>ESBARC</sub> t<sub>ESBSRC</sub> <sup>t</sup>ESBAWC <sup>t</sup>ESBSWC <sup>t</sup>ESBWASU <sup>t</sup>ESBWDSU ESBSRASU <sup>t</sup>ESBWESU ESBDATASU <sup>t</sup>ESBWADDRSU ESBRADDRSU ESBDATACO1 ESBDATACO2 ESBDD <sup>t</sup>PD <sup>t</sup>PTERMSU <sup>t</sup>PTERMCO

Figure 32. f<sub>MAX</sub> Timing Model

Figures 33 and 34 show the asynchronous and synchronous timingwaveforms, respectively, for the ESB macroparameters in Table 37.

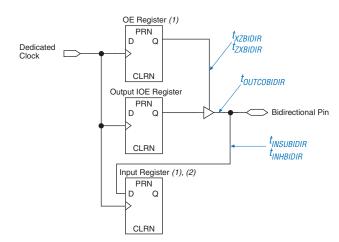

Figure 35. Synchronous Bidirectional Pin External Timing

#### *Notes to Figure 35:*

- (1) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin. Use the "Output Enable Routing = Single-Pin" option in the Quartus II software to set the output enable register.

- (2) Use the "Decrease Input Delay to Internal Cells = OFF" option in the Quartus II software to set the LAB-adjacent input register. This maintains a zero hold time for LAB-adjacent registers while giving a fast, position-independent setup time. Set "Decrease Input Delay to Internal Cells = ON" and move the input register farther away from the bidirectional pin for a faster setup time with zero hold time. The exact position where zero hold occurs with the minimum setup time varies with device density and speed grade.

Tables 36 to 38 describes the  $f_{MAX}$  timing parameters shown in Figure 32. Table 39 describes the functional timing parameters.

| Table 36. APEX 2 | OKC f <sub>MAX</sub> LE Timing Parameters |

|------------------|-------------------------------------------|

| Symbol           | Parameter                                 |

| $t_{SU}$         | LE register setup time before clock       |

| $t_H$            | LE register hold time before clock        |

| $t_{CO}$         | LE register clock-to-output delay         |

| $t_{LUT}$        | LUT delay for data-in to data-out         |

| Symbol                     | Parameter                                                                          | Condition |

|----------------------------|------------------------------------------------------------------------------------|-----------|

| t <sub>INSUBIDIR</sub>     | Setup time for bidirectional pins with global clock at LAB-adjacent input register |           |

| <sup>t</sup> INHBIDIR      | Hold time for bidirectional pins with global clock at LAB-adjacent input register  |           |

| <sup>t</sup> OUTCOBIDIR    | Clock-to-output delay for bidirectional pins with global clock at IOE register     | (2)       |

| t <sub>XZBIDIR</sub>       | Synchronous output enable register to output buffer disable delay                  | (2)       |

| t <sub>ZXBIDIR</sub>       | Synchronous output enable register to output buffer enable delay                   | (2)       |

| <sup>t</sup> INSUBIDIRPLL  | Setup time for bidirectional pins with PLL clock at LAB-adjacent input register    |           |

| <sup>t</sup> INHBIDIRPLL   | Hold time for bidirectional pins with PLL clock at LAB-adjacent input register     |           |

| t <sub>OUTCOBIDIRPLL</sub> | Clock-to-output delay for bidirectional pins with PLL clock at IOE register        | (2)       |

| t <sub>XZBIDIRPLL</sub>    | Synchronous output enable register to output buffer disable delay with PLL         | (2)       |

| t <sub>ZXBIDIRPLL</sub>    | Synchronous output enable register to output buffer enable delay with PLL          | (2)       |

#### Notes to Tables 40 and 41:

- (1) These timing parameters are sample-tested only.

- (2) For more information, refer to Table 43.

Tables 42 and 43 define the timing delays for each I/O standard. Some output standards require test load circuits for AC timing measurements as shown in Figures 36 through 38.

| Table 42. APEX 20KC Selectable I/O Standard Input Adder Delays (Part 1 of 2) Note (1) |                                                         |           |  |  |

|---------------------------------------------------------------------------------------|---------------------------------------------------------|-----------|--|--|

| Symbol                                                                                | Parameter                                               | Condition |  |  |

| LVCMOS                                                                                | Input adder delay for the LVCMOS I/O standard           |           |  |  |

| LVTTL                                                                                 | Input adder delay for the LVTTL I/O standard            |           |  |  |

| 2.5 V                                                                                 | Input adder delay for the 2.5-V I/O standard            |           |  |  |

| 1.8 V                                                                                 | Input adder delay for the 1.8-V I/O standard            |           |  |  |

| PCI                                                                                   | Input adder delay for the PCI I/O standard              |           |  |  |

| GTI+                                                                                  | Input adder delay for the GTL+ I/O standard             |           |  |  |

| SSTL-3 Class I                                                                        | Input adder delay for the SSTL-3 Class I I/O standard   |           |  |  |

| SSTL-3 Class II                                                                       | Input adder delay for the SSTL-3 Class II I/O standard  |           |  |  |

| SSTL-2 Class I                                                                        | Input adder delay for the SSTL -2 Class I I/O standard  |           |  |  |

| SSTL-2 Class II                                                                       | Input adder delay for the SSTL -2 Class II I/O standard |           |  |  |

| Table 42. APEX 20KC Selectable I/O Standard Input Adder Delays (Part 2 of 2) Note (1) |                                             |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|---------------------------------------------|--|--|--|--|--|--|

| Symbol                                                                                | Condition                                   |  |  |  |  |  |  |

| LVDS                                                                                  | Input adder delay for the LVDS I/O standard |  |  |  |  |  |  |

| CTT                                                                                   | Input adder delay for the CTT I/O standard  |  |  |  |  |  |  |

| AGP                                                                                   | Input adder delay for the AGP I/O standard  |  |  |  |  |  |  |

| Symbol          | Parameter                                               | Condition                                                       |

|-----------------|---------------------------------------------------------|-----------------------------------------------------------------|

| LVCMOS          | Output adder delay for the LVCMOS I/O standard          |                                                                 |

| LVTTL           | Output adder delay for the LVTTL I/O standard           | Cload = 35 pF<br>Rup = 564.5 $\Omega$<br>Rdn = 430 $\Omega$ (2) |

| 2.5 V           | Output adder delay for the 2.5-V I/O standard           | Cload = 35 pF<br>Rup = 450 $\Omega$<br>Rdn = 450 $\Omega$ (2)   |

| 1.8 V           | Output adder delay for the 1.8-V I/O standard           | Cload = 35 pF<br>Rup = 520 $\Omega$<br>Rdn = 480 $\Omega$ (2)   |

| PCI             | Output adder delay for the PCI I/O standard             | Cload = 10 pF<br>Rup = 1M $\Omega$<br>Rdn = 25 $\Omega$ (2)     |

| GTI+            | Output adder delay for the GTL+ I/O standard            | Cload = 30 pF<br>Rup = 25 Ω (2)                                 |

| SSTL-3 Class I  | Output adder delay for the SSTL-3 Class I I/O standard  | Cload1 = 0 pF<br>Cload2 = 30 pF<br>R = 25 $\Omega$ (2)          |

| SSTL-3 Class II | Output adder delay for the SSTL-3 Class II I/O standard | Cload1 = 0 pF<br>Cload2 = 30 pF<br>R = 25 $\Omega$ (2)          |

| SSTL-2 Class I  | Output adder delay for the SSTL-2 Class I I/O standard  |                                                                 |

| SSTL-2 Class II | Output adder delay for the SSTL-2 Class II I/O standard |                                                                 |

| LVDS            | Output adder delay for the LVDS I/O standard            | Cload = 4 pF<br>R=100 Ω (2)                                     |

| СТТ             | Output adder delay for the CTT I/O standard             |                                                                 |

| AGP             | Output adder delay for the AGP I/O standard             |                                                                 |

#### Note to Tables 42 and 43:

<sup>(1)</sup> These delays report the differences in delays for different I/O standards. Add the delay for the I/O standard that is used to the external timing parameters.

<sup>(2)</sup> See Figure 36 for more information.

| Symbol                    | -7 Speed Grade |      | -8 Spee | -8 Speed Grade |      | ed Grade | Unit |

|---------------------------|----------------|------|---------|----------------|------|----------|------|

|                           | Min            | Max  | Min     | Max            | Min  | Max      | 1    |

| t <sub>INSUBIDIR</sub>    | 1.38           |      | 1.78    |                | 1.99 |          | ns   |

| t <sub>INHBIDIR</sub>     | 0.00           |      | 0.00    |                | 0.00 |          | ns   |

| t <sub>OUTCOBIDIR</sub>   | 2.00           | 3.79 | 2.00    | 4.31           | 2.00 | 4.70     | ns   |

| t <sub>XZBIDIR</sub>      |                | 6.12 |         | 6.51           |      | 7.89     | ns   |

| t <sub>ZXBIDIR</sub>      |                | 6.12 |         | 6.51           |      | 7.89     | ns   |

| t <sub>INSUBIDIRPLL</sub> | 2.82           |      | 3.47    |                | -    |          | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00           |      | 0.00    |                | -    |          | ns   |

| †OUTCOBIDIRPLL            | 0.50           | 2.36 | 0.50    | 2.62           | -    | -        | ns   |

| t <sub>XZBIDIRPLL</sub>   |                | 4.69 |         | 4.82           |      | -        | ns   |

| t <sub>ZXBIDIRPLL</sub>   |                | 4.69 |         | 4.82           |      | -        | ns   |

| Table 50. EP20K400C f <sub>MAX</sub> LE Timing Parameters |         |         |         |         |         |      |    |  |  |

|-----------------------------------------------------------|---------|---------|---------|---------|---------|------|----|--|--|

| Symbol                                                    | -7 Spee | d Grade | -8 Spec | d Grade | -9 Spee | Unit |    |  |  |

|                                                           | Min     | Max     | Min     | Max     | Min     | Max  | 1  |  |  |

| $t_{SU}$                                                  | 0.01    |         | 0.01    |         | 0.01    |      | ns |  |  |

| t <sub>H</sub>                                            | 0.10    |         | 0.10    |         | 0.10    |      | ns |  |  |

| $t_{CO}$                                                  |         | 0.27    |         | 0.30    |         | 0.32 | ns |  |  |

| $t_{LUT}$                                                 |         | 0.65    |         | 0.78    |         | 0.92 | ns |  |  |

| Table 51. EP20K400C f <sub>MAX</sub> ESB Timing Parameters |                |      |                |      |                |      |      |  |  |

|------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|--|--|

| Symbol                                                     | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |  |  |

|                                                            | Min            | Max  | Min            | Max  | Min            | Max  |      |  |  |

| t <sub>ESBARC</sub>                                        |                | 1.30 |                | 1.51 |                | 1.69 | ns   |  |  |

| t <sub>ESBSRC</sub>                                        |                | 2.35 |                | 2.49 |                | 2.72 | ns   |  |  |

| t <sub>ESBAWC</sub>                                        |                | 2.92 |                | 3.46 |                | 3.86 | ns   |  |  |

| t <sub>ESBSWC</sub>                                        |                | 3.05 |                | 3.44 |                | 3.85 | ns   |  |  |

| t <sub>ESBWASU</sub>                                       | 0.45           |      | 0.50           |      | 0.54           |      | ns   |  |  |

| t <sub>ESBWAH</sub>                                        | 0.44           |      | 0.50           |      | 0.55           |      | ns   |  |  |

| t <sub>ESBWDSU</sub>                                       | 0.57           |      | 0.63           |      | 0.68           |      | ns   |  |  |

| t <sub>ESBWDH</sub>                                        | 0.44           |      | 0.50           |      | 0.55           |      | ns   |  |  |

| t <sub>ESBRASU</sub>                                       | 1.25           |      | 1.43           |      | 1.56           |      | ns   |  |  |

| t <sub>ESBRAH</sub>                                        | 0.00           |      | 0.03           |      | 0.11           |      | ns   |  |  |

| t <sub>ESBWESU</sub>                                       | 0.00           |      | 0.00           |      | 0.00           |      | ns   |  |  |

| t <sub>ESBDATASU</sub>                                     | 2.01           |      | 2.27           |      | 2.45           |      | ns   |  |  |

| t <sub>ESBWADDRSU</sub>                                    | -0.20          |      | -0.24          |      | -0.28          |      | ns   |  |  |

| t <sub>ESBRADDRSU</sub>                                    | 0.02           |      | 0.00           |      | -0.02          |      | ns   |  |  |

| t <sub>ESBDATACO1</sub>                                    |                | 1.09 |                | 1.28 |                | 1.43 | ns   |  |  |

| t <sub>ESBDATACO2</sub>                                    |                | 2.10 |                | 2.52 |                | 2.82 | ns   |  |  |

| t <sub>ESBDD</sub>                                         |                | 2.50 |                | 2.97 |                | 3.32 | ns   |  |  |

| $t_{PD}$                                                   |                | 1.48 |                | 1.78 |                | 2.00 | ns   |  |  |

| t <sub>PTERMSU</sub>                                       | 0.58           |      | 0.72           |      | 0.81           |      | ns   |  |  |

| t <sub>PTERMCO</sub>                                       |                | 1.10 |                | 1.29 |                | 1.45 | ns   |  |  |

| Table 52. EP20K400C f <sub>MAX</sub> Routing Delays |         |                |     |         |                |      |      |  |  |

|-----------------------------------------------------|---------|----------------|-----|---------|----------------|------|------|--|--|

| Symbol                                              | -7 Spec | -7 Speed Grade |     | d Grade | -9 Speed Grade |      | Unit |  |  |

|                                                     | Min     | Max            | Min | Max     | Min            | Max  |      |  |  |

| t <sub>F1-4</sub>                                   |         | 0.15           |     | 0.17    |                | 0.19 | ns   |  |  |

| t <sub>F5-20</sub>                                  |         | 0.94           |     | 1.06    |                | 1.25 | ns   |  |  |

| t <sub>F20+</sub>                                   |         | 1.73           |     | 1.96    |                | 2.30 | ns   |  |  |

| Symbol             | -7 Spee | -7 Speed Grade |      | -8 Speed Grade |      | d Grade | Unit |

|--------------------|---------|----------------|------|----------------|------|---------|------|

|                    | Min     | Max            | Min  | Max            | Min  | Max     | 1    |

| t <sub>CH</sub>    | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>CL</sub>    | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>CLRP</sub>  | 0.20    |                | 0.20 |                | 0.20 |         | ns   |

| t <sub>PREP</sub>  | 0.20    |                | 0.20 |                | 0.20 |         | ns   |

| t <sub>ESBCH</sub> | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>ESBCL</sub> | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>ESBWP</sub> | 1.05    |                | 1.28 |                | 1.44 |         | ns   |

| t <sub>ESBRP</sub> | 0.87    |                | 1.06 |                | 1.19 |         | ns   |

| Table 54. EP20K400C External Timing Parameters |         |                |      |                |      |                |    |  |  |

|------------------------------------------------|---------|----------------|------|----------------|------|----------------|----|--|--|

| Symbol                                         | -7 Spee | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |    |  |  |

|                                                | Min     | Max            | Min  | Max            | Min  | Max            |    |  |  |

| t <sub>INSU</sub>                              | 1.37    |                | 1.52 |                | 1.64 |                | ns |  |  |

| t <sub>INH</sub>                               | 0.00    |                | 0.00 |                | 0.00 |                | ns |  |  |

| t <sub>outco</sub>                             | 2.00    | 4.25           | 2.00 | 4.61           | 2.00 | 5.03           | ns |  |  |

| t <sub>INSUPLL</sub>                           | 0.80    |                | 0.91 |                | -    |                | ns |  |  |

| t <sub>INHPLL</sub>                            | 0.00    |                | 0.00 |                | -    |                | ns |  |  |

| t <sub>OUTCOPLL</sub>                          | 0.50    | 2.27           | 0.50 | 2.55           | -    | -              | ns |  |  |

| Symbol             | -7 Spee | -7 Speed Grade |      | -8 Speed Grade |      | d Grade | Unit |

|--------------------|---------|----------------|------|----------------|------|---------|------|

|                    | Min     | Max            | Min  | Max            | Min  | Max     | 1    |

| t <sub>CH</sub>    | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>CL</sub>    | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>CLRP</sub>  | 0.20    |                | 0.20 |                | 0.20 |         | ns   |

| t <sub>PREP</sub>  | 0.20    |                | 0.20 |                | 0.20 |         | ns   |

| t <sub>ESBCH</sub> | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>ESBCL</sub> | 1.33    |                | 1.66 |                | 2.00 |         | ns   |

| t <sub>ESBWP</sub> | 1.05    |                | 1.28 |                | 1.44 |         | ns   |

| t <sub>ESBRP</sub> | 0.87    |                | 1.06 |                | 1.19 |         | ns   |

| Table 60. EP20K600C External Timing Parameters |               |      |                 |      |                |      |      |  |  |

|------------------------------------------------|---------------|------|-----------------|------|----------------|------|------|--|--|

| Symbol                                         | Symbol -7 Spe |      | d Grade -8 Spec |      | -9 Speed Grade |      | Unit |  |  |

|                                                | Min           | Max  | Min             | Max  | Min            | Max  |      |  |  |

| t <sub>INSU</sub>                              | 1.28          |      | 1.40            |      | 1.45           |      | ns   |  |  |

| t <sub>INH</sub>                               | 0.00          |      | 0.00            |      | 0.00           |      | ns   |  |  |

| tоитсо                                         | 2.00          | 4.29 | 2.00            | 4.77 | 2.00           | 5.11 | ns   |  |  |

| t <sub>INSUPLL</sub>                           | 0.80          |      | 0.91            |      | =              |      | ns   |  |  |

| t <sub>INHPLL</sub>                            | 0.00          |      | 0.00            |      | -              |      | ns   |  |  |

| †OUTCOPLL                                      | 0.50          | 2.37 | 0.50            | 2.63 | -              | -    | ns   |  |  |