Welcome to **E-XFL.COM**

# Understanding <u>Embedded - FPGAs (Field Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Obsolete                                                     |

| Number of LABs/CLBs            | 1664                                                         |

| Number of Logic Elements/Cells | 16640                                                        |

| Total RAM Bits                 | 212992                                                       |

| Number of I/O                  | 488                                                          |

| Number of Gates                | 1052000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 672-BBGA                                                     |

| Supplier Device Package        | 672-FBGA (27x27)                                             |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep20k400cf672c9es |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

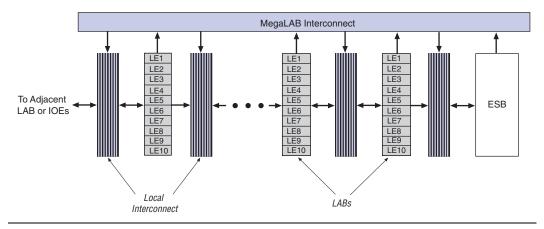

## MegaLAB Structure

APEX 20KC devices are constructed from a series of MegaLAB<sup>TM</sup> structures. Each MegaLAB structure contains 16 logic array blocks (LABs), one ESB, and a MegaLAB interconnect, which routes signals within the MegaLAB structure. In EP20K1000C devices, MegaLAB structures contain 24 LABs. Signals are routed between MegaLAB structures and I/O pins via the FastTrack interconnect. In addition, edge LABs can be driven by I/O pins through the local interconnect. Figure 2 shows the MegaLAB structure.

Figure 2. MegaLAB Structure

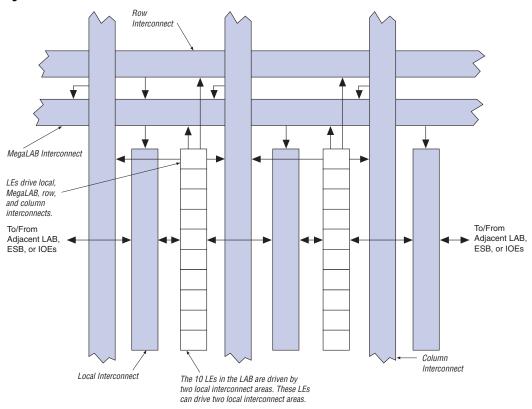

## **Logic Array Block**

Each LAB consists of 10 LEs, the LEs' associated carry and cascade chains, LAB control signals, and the local interconnect. The local interconnect transfers signals between LEs in the same or adjacent LABs, IOEs, or ESBs. The Quartus II Compiler places associated logic within an LAB or adjacent LABs, allowing the use of a fast local interconnect for high performance. Figure 3 shows the APEX 20KC LAB.

APEX 20KC devices use an interleaved LAB structure. This structure allows each LE to drive two local interconnect areas, minimizing the use of the MegaLAB and FastTrack interconnect and providing higher performance and flexibility. Each LE can drive 29 other LEs through the fast local interconnect.

Figure 3. LAB Structure

Each LAB contains dedicated logic for driving control signals to its LEs and ESBs. The control signals include clock, clock enable, asynchronous clear, asynchronous preset, asynchronous load, synchronous clear, and synchronous load signals. A maximum of six control signals can be used at a time. Although synchronous load and clear signals are generally used when implementing counters, they can also be used with other functions.

Each LAB can use two clocks and two clock enable signals. Each LAB's clock and clock enable signals are linked (e.g., any LE in a particular LAB using CLK1 will also use CLKENA1). LEs with the same clock but different clock enable signals either use both clock signals in one LAB or are placed into separate LABs.

If both the rising and falling edges of a clock are used in a LAB, both LAB-wide clock signals are used.

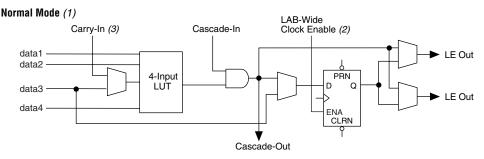

Figure 8. APEX 20KC LE Operating Modes

#### Notes to Figure 8:

- (1) LEs in normal mode support register packing.

- (2) There are two LAB-wide clock enables per LAB.

- (3) When using the carry-in in normal mode, the packed register feature is unavailable.

- (4) A register feedback multiplexer is available on LE1 of each LAB.

- (5) The DATA1 and DATA2 input signals can supply counter enable, up or down control, or register feedback signals for LEs other than the second LE in an LAB.

- (6) The LAB-wide synchronous clear and LAB wide synchronous load affect all registers in an LAB.

#### Normal Mode

The normal mode is suitable for general logic applications, combinatorial functions, or wide decoding functions that can take advantage of a cascade chain. In normal mode, four data inputs from the LAB local interconnect and the carry-in are inputs to a four-input LUT. The Quartus II Compiler automatically selects the carry-in or the DATA3 signal as one of the inputs to the LUT. The LUT output can be combined with the cascade-in signal to form a cascade chain through the cascade-out signal. LEs in normal mode support packed registers.

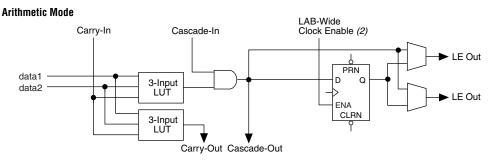

#### Arithmetic Mode

The arithmetic mode is ideal for implementing adders, accumulators, and comparators. An LE in arithmetic mode uses two 3-input LUTs. One LUT computes a three-input function; the other generates a carry output. As shown in Figure 8, the first LUT uses the carry-in signal and two data inputs from the LAB local interconnect to generate a combinatorial or registered output. For example, when implementing an adder, this output is the sum of three signals: DATA1, DATA2, and carry-in. The second LUT uses the same three signals to generate a carry-out signal, thereby creating a carry chain. The arithmetic mode also supports simultaneous use of the cascade chain. LEs in arithmetic mode can drive out registered and unregistered versions of the LUT output.

The Quartus II software implements parameterized functions that use the arithmetic mode automatically where appropriate; the designer does not need to specify how the carry chain will be used.

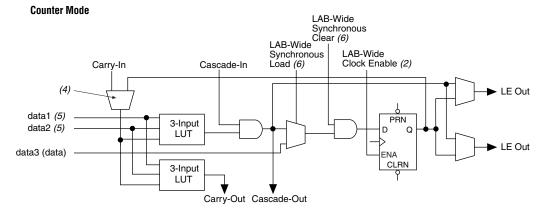

#### Counter Mode

The counter mode offers clock enable, counter enable, synchronous up/down control, synchronous clear, and synchronous load options. The counter enable and synchronous up/down control signals are generated from the data inputs of the LAB local interconnect. The synchronous clear and synchronous load options are LAB-wide signals that affect all registers in the LAB. Consequently, if any of the LEs in an LAB use the counter mode, other LEs in that LAB must be used as part of the same counter or be used for a combinatorial function. The Quartus II software automatically places any registers that are not used by the counter into other LABs.

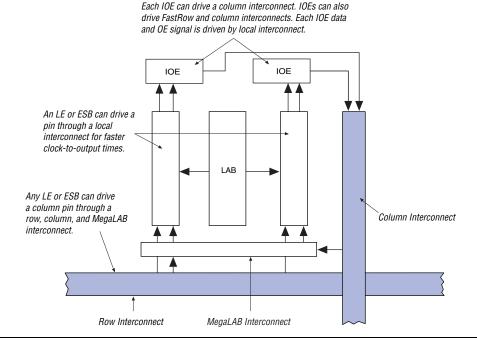

Figure 11 shows the intersection of a row and column interconnect, and how these forms of interconnects and LEs drive each other.

Row Interconnect

MegaLAB Interconnect

Column Interconnect

Interconnect

Figure 11. Driving the FastTrack Interconnect

APEX 20KC devices include an enhanced interconnect structure for faster routing of input signals with high fan-out. Column I/O pins can drive the FastRow<sup>TM</sup> interconnect, which routes signals directly into the local interconnect without having to drive through the MegaLAB interconnect. The FastRow lines traverse two MegaLAB structures. Also, these pins can drive the local interconnect directly for fast setup times. On EP20K400C and larger devices, the FastRow interconnect drives the two MegaLAB structures in the top left corner, the two MegaLAB structures in the two right corner, the two MegaLAB structures in the bottom left corner, and the two MegaLAB structures in the bottom right corner. On EP20K200C and smaller devices, FastRow interconnect drives the two MegaLAB structures on the top and the two MegaLAB structures on the bottom of the device. On all devices, the FastRow interconnect drives all local interconnect in the appropriate MegaLAB structures except the end local interconnect on the side of the MegaLAB opposite the ESB. Pins using the FastRow interconnect achieve a faster set-up time, as the signal does not need to use a MegaLAB interconnect line to reach the destination LE. Figure 12 shows the FastRow interconnect.

ESBs can implement synchronous RAM, which is easier to use than asynchronous RAM. A circuit using asynchronous RAM must generate the RAM write enable (WE) signal, while ensuring that its data and address signals meet setup and hold time specifications relative to the WE signal. In contrast, the ESB's synchronous RAM generates its own WE signal and is self-timed with respect to the global clock. Circuits using the ESB's self-timed RAM must only meet the setup and hold time specifications of the global clock.

ESB inputs are driven by the adjacent local interconnect, which in turn can be driven by the FastTrack or MegaLAB interconnect. Because the ESB can be driven by the local interconnect, an adjacent LE can drive it directly for fast memory access. ESB outputs drive the FastTrack and MegaLAB interconnects. In addition, ten ESB outputs, nine of which are unique output lines, drive the local interconnect for fast connection to adjacent LEs or for fast feedback product-term logic.

When implementing memory, each ESB can be configured in any of the following sizes:  $128 \times 16$ ,  $256 \times 8$ ,  $512 \times 4$ ,  $1,024 \times 2$ , or  $2,048 \times 1$ . By combining multiple ESBs, the Quartus II software implements larger memory blocks automatically. For example, two  $128 \times 16$  RAM blocks can be combined to form a  $128 \times 32$  RAM block, and two  $512 \times 4$  RAM blocks can be combined to form a  $512 \times 8$  RAM block. Memory performance does not degrade for memory blocks up to 2,048 words deep. Each ESB can implement a 2,048-word-deep memory; the ESBs are used in parallel, eliminating the need for any external control logic and its associated delays.

To create a high-speed memory block that is more than 2,048 words deep, ESBs drive tri-state lines. Each tri-state line connects all ESBs in a column of MegaLAB structures, and drives the MegaLAB interconnect and row and column FastTrack interconnect throughout the column. Each ESB incorporates a programmable decoder to activate the tri-state driver appropriately. For instance, to implement 8,192-word-deep memory, four ESBs are used. Eleven address lines drive the ESB memory, and two more drive the tri-state decoder. Depending on which 2,048-word memory page is selected, the appropriate ESB driver is turned on, driving the output to the tri-state line. The Quartus II software automatically combines ESBs with tri-state lines to form deeper memory blocks. The internal tri-state control logic is designed to avoid internal contention and floating lines. See Figure 18.

For more information on APEX 20KC devices and CAM, see *Application Note 119 (Implementing High-Speed Search Applications with APEX CAM).*

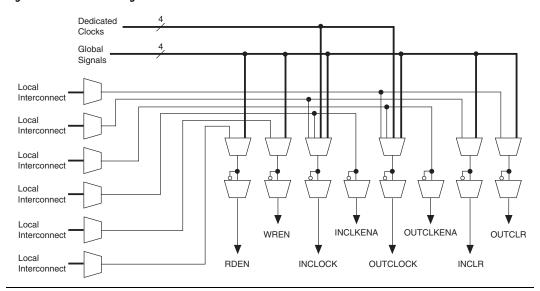

## **Driving Signals to the ESB**

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

Figure 24. ESB Control Signal Generation

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

#### Notes to Figure 25:

- (1) This programmable delay has four settings: off and three levels of delay.

- (2) The output enable and input registers are LE registers in the LAB adjacent to the bidirectional pin.

Each IOE drives a row, column, MegaLAB, or local interconnect when used as an input or bidirectional pin. A row IOE can drive a local, MegaLAB, row, and column interconnect; a column IOE can drive the column interconnect. Figure 26 shows how a row IOE connects to the interconnect.

Row Interconnect MegaLAB Interconnect Any LE can drive a pin through the row. cclumn, and MegaLAB in erconnect. Each IOE can drive local, IOE MegaLAB, row, and column interconnect. Each IOE data LAB and OE signal is driven by the local interconnect. IOE An LE can drive a pin through the local interconnect for faster clock-to-output times.

Figure 26. Row IOE Connection to the Interconnect

Figure 27 shows how a column IOE connects to the interconnect.

Figure 27. Column IOE Connection to the Interconnect

## **Dedicated Fast I/O Pins**

APEX 20KC devices incorporate an enhancement to support bidirectional pins with high internal fan-out such as PCI control signals. These pins are called dedicated fast I/O pins (FAST1, FAST2, FAST3, and FAST4) and replace dedicated inputs. These pins can be used for fast clock, clear, or high fan-out logic signal distribution. They also can drive out. The dedicated fast I/O pin data output and tri-state control are driven by local interconnect from the adjacent MegaLAB for high speed.

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All APEX 20KC devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. APEX 20KC devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Files (.jam) or Jam Byte-Code Files (.jbc). Finally, APEX 20KC devices use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. APEX 20KC devices support the JTAG instructions shown in Table 13.

| Table 13. APEX 20KC JTAG Instructions |                                                                                                                                                                                                                                      |  |  |  |

|---------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| JTAG Instruction                      | Description                                                                                                                                                                                                                          |  |  |  |

| SAMPLE/PRELOAD                        | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap embedded logic analyzer. |  |  |  |

| EXTEST                                | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                               |  |  |  |

| BYPASS                                | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                          |  |  |  |

| USERCODE                              | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                            |  |  |  |

| IDCODE                                | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                |  |  |  |

| ICR Instructions                      | Used when configuring an APEX 20KC device via the JTAG port with a MasterBlaster <sup>TM</sup> or ByteBlasterMV <sup>TM</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.              |  |  |  |

| SignalTap<br>Instructions             | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                       |  |  |  |

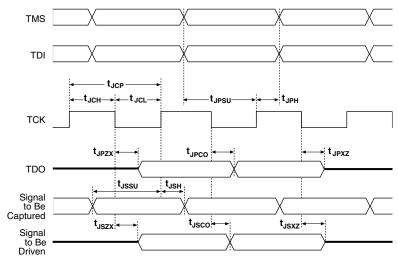

Figure 30. APEX 20KC JTAG Waveforms

Table 16 shows the JTAG timing parameters and values for APEX 20KC devices.

| Table 16. APEX 20KC JTAG Timing Parameters & Values |                                                |     |     |      |  |  |

|-----------------------------------------------------|------------------------------------------------|-----|-----|------|--|--|

| Symbol                                              | Parameter                                      | Min | Max | Unit |  |  |

| t <sub>JCP</sub>                                    | TCK clock period                               | 100 |     | ns   |  |  |

| t <sub>JCH</sub>                                    | TCK clock high time                            | 50  |     | ns   |  |  |

| t <sub>JCL</sub>                                    | TCK clock low time                             | 50  |     | ns   |  |  |

| t <sub>JPSU</sub>                                   | JTAG port setup time                           | 20  |     | ns   |  |  |

| t <sub>JPH</sub>                                    | JTAG port hold time                            | 45  |     | ns   |  |  |

| t <sub>JPCO</sub>                                   | JTAG port clock to output                      |     | 25  | ns   |  |  |

| t <sub>JPZX</sub>                                   | JTAG port high impedance to valid output       |     | 25  | ns   |  |  |

| t <sub>JPXZ</sub>                                   | JTAG port valid output to high impedance       |     | 25  | ns   |  |  |

| t <sub>JSSU</sub>                                   | Capture register setup time                    | 20  |     | ns   |  |  |

| t <sub>JSH</sub>                                    | Capture register hold time                     | 45  |     | ns   |  |  |

| t <sub>JSCO</sub>                                   | Update register clock to output                |     | 35  | ns   |  |  |

| t <sub>JSZX</sub>                                   | Update register high impedance to valid output |     | 35  | ns   |  |  |

| t <sub>JSXZ</sub>                                   | Update register valid output to high impedance |     | 35  | ns   |  |  |

For more information, see the following documents:

Application Note 39 (IEEE Std. 1149.1 (JTAG) Boundary-Scan Testing in Altera Devices)

Jam Programming & Test Language Specification

# **Generic Testing**

Each APEX 20KC device is functionally tested. Complete testing of each configurable SRAM bit and all logic functionality ensures 100% yield. AC test measurements for APEX 20KC devices are made under conditions equivalent to those defined in the "Timing Model" section on page 65. Multiple test patterns can be used to configure devices during all stages of the production flow. AC test criteria include:

- Power supply transients can affect AC measurements.

- Simultaneous transitions of multiple outputs should be avoided for accurate measurement.

- Threshold tests must not be performed under AC conditions.

- Large-amplitude, fast-ground-current transients normally occur as the device outputs discharge the load capacitances. When these transients flow through the parasitic inductance between the device ground pin and the test system ground, significant reductions in observable noise immunity can result.

# Operating Conditions

Tables 17 through 20 provide information on absolute maximum ratings, recommended operating conditions, DC operating conditions, and capacitance for 1.8-V APEX 20KC devices.

| Table 17. APEX 20KC Device Absolute Maximum Ratings   Note (1) |                            |                                                |      |     |      |  |  |

|----------------------------------------------------------------|----------------------------|------------------------------------------------|------|-----|------|--|--|

| Symbol                                                         | Parameter                  | Conditions                                     | Min  | Max | Unit |  |  |

| V <sub>CCINT</sub>                                             | Supply voltage             | With respect to ground (2)                     | -0.5 | 2.5 | V    |  |  |

| V <sub>CCIO</sub>                                              |                            |                                                | -0.5 | 4.6 | V    |  |  |

| V <sub>I</sub>                                                 | DC input voltage           |                                                | -0.5 | 4.6 | ٧    |  |  |

| I <sub>OUT</sub>                                               | DC output current, per pin |                                                | -25  | 25  | mA   |  |  |

| T <sub>STG</sub>                                               | Storage temperature        | No bias                                        | -65  | 150 | ° C  |  |  |

| T <sub>AMB</sub>                                               | Ambient temperature        | Under bias                                     | -65  | 135 | ° C  |  |  |

| TJ                                                             | Junction temperature       | PQFP, RQFP, TQFP, and BGA packages, under bias |      | 135 | ° C  |  |  |

|                                                                |                            | Ceramic PGA packages, under bias               |      | 150 | °C   |  |  |

| Table 18. APEX 20KC Device Recommended Operating Conditions |                                                     |                    |                  |                   |      |  |  |

|-------------------------------------------------------------|-----------------------------------------------------|--------------------|------------------|-------------------|------|--|--|

| Symbol                                                      | Parameter                                           | Conditions         | Min              | Max               | Unit |  |  |

| V <sub>CCINT</sub>                                          | Supply voltage for internal logic and input buffers | (3), (4)           | 1.71<br>(1.71)   | 1.89<br>(1.89)    | V    |  |  |

| V <sub>CCIO</sub>                                           | Supply voltage for output buffers, 3.3-V operation  | (3), (4)           | 3.00<br>(3.00)   | 3.60<br>(3.60)    | V    |  |  |

|                                                             | Supply voltage for output buffers, 2.5-V operation  | (3), (4)           | 2.375<br>(2.375) | 2.625<br>(2.625)  | V    |  |  |

|                                                             | Supply voltage for output buffers, 1.8-V operation  | (3), (4)           | 1.71<br>(1.71)   | 1.89<br>(1.89)    | V    |  |  |

| V <sub>I</sub>                                              | Input voltage                                       | (2), (5)           | -0.5             | 4.1               | V    |  |  |

| v <sub>o</sub>                                              | Output voltage                                      |                    | 0                | V <sub>CCIO</sub> | ٧    |  |  |

| TJ                                                          | Operating junction temperature                      | For commercial use | 0                | 85                | ° C  |  |  |

|                                                             |                                                     | For industrial use | -40              | 100               | °C   |  |  |

| t <sub>R</sub>                                              | Input rise time (10% to 90%)                        |                    |                  | 40                | ns   |  |  |

| t <sub>F</sub>                                              | Input fall time (90% to 10%)                        |                    |                  | 40                | ns   |  |  |

| Table 19. APEX 20KC Device DC Operating Conditions       Notes (6), (7) |                                                                              |                                                                                 |     |     |     |      |  |

|-------------------------------------------------------------------------|------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----|-----|-----|------|--|

| Symbol                                                                  | Parameter                                                                    | Conditions                                                                      | Min | Тур | Max | Unit |  |

| I <sub>I</sub>                                                          | Input pin leakage current (8)                                                | V <sub>I</sub> = 3.6 to 0.0 V                                                   | -10 |     | 10  | μА   |  |

| I <sub>OZ</sub>                                                         | Tri-stated I/O pin leakage current (8)                                       | $V_O = 4.1 \text{ to } -0.5 \text{ V}$                                          | -10 |     | 10  | μА   |  |

| I <sub>CC0</sub>                                                        | V <sub>CC</sub> supply current (standby)<br>(All ESBs in power-down<br>mode) | V <sub>I</sub> = ground, no load,<br>no toggling inputs,<br>-7 speed grade      |     | 10  |     | mA   |  |

|                                                                         |                                                                              | V <sub>I</sub> = ground, no load,<br>no toggling inputs,<br>-8, -9 speed grades |     | 5   |     | mA   |  |

| R <sub>CONF</sub>                                                       | Value of I/O pin pull-up                                                     | V <sub>CCIO</sub> = 3.0 V (9)                                                   | 20  |     | 50  | kΩ   |  |

|                                                                         | resistor before and during                                                   | V <sub>CCIO</sub> = 2.375 V (9)                                                 | 30  |     | 80  | kΩ   |  |

|                                                                         | configuration                                                                | V <sub>CCIO</sub> = 1.71 V (9)                                                  | 60  |     | 150 | kΩ   |  |

DC operating specifications on APEX 20KC I/O standards are listed in Tables 21 to 35.

| Table 2                               | Table 20. APEX 20KC Device Capacitance   Note (10) |                                     |  |    |    |  |  |  |

|---------------------------------------|----------------------------------------------------|-------------------------------------|--|----|----|--|--|--|

| Symbol Parameter Conditions Min Max U |                                                    |                                     |  |    |    |  |  |  |

| C <sub>IN</sub>                       | Input capacitance                                  | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |  | 8  | pF |  |  |  |

| C <sub>INCLK</sub>                    | Input capacitance on dedicated clock pin           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |  | 12 | pF |  |  |  |

| C <sub>OUT</sub>                      | Output capacitance                                 | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |  | 8  | pF |  |  |  |

#### Notes to Tables 17 through 20:

- (1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 4.6 V for input currents less than 100 mA and time periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^{\circ}$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (7) These values are specified under the APEX 20KC device recommended operating conditions, shown in Table 18 on page 55.

- (8) This value is specified for normal device operation. The value may vary during power-up.

- (9) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Capacitance is sample-tested only.

Tables 21 through 35 list the DC operating specifications for the supported I/O standards. These tables list minimal specifications only; APEX 20KC devices may exceed these specifications.

| Table 21. LVTTL I/O Specifications |                           |                                                               |         |                         |       |  |  |

|------------------------------------|---------------------------|---------------------------------------------------------------|---------|-------------------------|-------|--|--|

| Symbol                             | Parameter                 | Conditions                                                    | Minimum | Maximum                 | Units |  |  |

| V <sub>CCIO</sub>                  | Output supply voltage     |                                                               | 3.0     | 3.6                     | V     |  |  |

| V <sub>IH</sub>                    | High-level input voltage  |                                                               | 2.0     | V <sub>CCIO</sub> + 0.3 | V     |  |  |

| V <sub>IL</sub>                    | Low-level input voltage   |                                                               | -0.3    | 0.8                     | V     |  |  |

| I <sub>I</sub>                     | Input pin leakage current | V <sub>IN</sub> = 0 V or 3.3 V                                | -10     | 10                      | μΑ    |  |  |

| V <sub>OH</sub>                    | High-level output voltage | $I_{OH} = -12 \text{ mA},$<br>$V_{CCIO} = 3.0 \text{ V } (1)$ | 2.4     |                         | V     |  |  |

| V <sub>OL</sub>                    | Low-level output voltage  | I <sub>OL</sub> = 12 mA,<br>V <sub>CCIO</sub> = 3.0 V (2)     |         | 0.4                     | V     |  |  |

| Table 28. GTL+ I/O Specifications |                          |                                    |                        |         |                        |       |  |

|-----------------------------------|--------------------------|------------------------------------|------------------------|---------|------------------------|-------|--|

| Symbol                            | Parameter                | Conditions                         | Minimum                | Typical | Maximum                | Units |  |

| V <sub>TT</sub>                   | Termination voltage      |                                    | 1.35                   | 1.5     | 1.65                   | V     |  |

| V <sub>REF</sub>                  | Reference voltage        |                                    | 0.88                   | 1.0     | 1.12                   | V     |  |

| V <sub>IH</sub>                   | High-level input voltage |                                    | V <sub>REF</sub> + 0.1 |         |                        | V     |  |

| V <sub>IL</sub>                   | Low-level input voltage  |                                    |                        |         | V <sub>REF</sub> – 0.1 | V     |  |

| V <sub>OL</sub>                   | Low-level output voltage | I <sub>OL</sub> = 36 mA <i>(2)</i> |                        |         | 0.65                   | V     |  |

| Table 29. SSTL-2 Class I Specifications |                           |                                 |                         |           |                         |       |  |

|-----------------------------------------|---------------------------|---------------------------------|-------------------------|-----------|-------------------------|-------|--|

| Symbol                                  | Parameter                 | Conditions                      | Minimum                 | Typical   | Maximum                 | Units |  |

| V <sub>CCIO</sub>                       | I/O supply voltage        |                                 | 2.375                   | 2.5       | 2.625                   | V     |  |

| V <sub>TT</sub>                         | Termination voltage       |                                 | V <sub>REF</sub> - 0.04 | $V_{REF}$ | V <sub>REF</sub> + 0.04 | V     |  |

| V <sub>REF</sub>                        | Reference voltage         |                                 | 1.15                    | 1.25      | 1.35                    | V     |  |

| V <sub>IH</sub>                         | High-level input voltage  |                                 | V <sub>REF</sub> + 0.18 |           | V <sub>CCIO</sub> + 0.3 | V     |  |

| V <sub>IL</sub>                         | Low-level input voltage   |                                 | -0.3                    |           | V <sub>REF</sub> – 0.18 | V     |  |

| V <sub>OH</sub>                         | High-level output voltage | $I_{OH} = -7.6 \text{ mA } (1)$ | V <sub>TT</sub> + 0.57  |           |                         | V     |  |

| V <sub>OL</sub>                         | Low-level output voltage  | I <sub>OL</sub> = 7.6 mA (2)    |                         |           | V <sub>TT</sub> – 0.57  | V     |  |

| Table 39. APEX 20KC Minimum Pulse Width Timing Parameters |                                        |  |  |  |

|-----------------------------------------------------------|----------------------------------------|--|--|--|

| Symbol                                                    | Parameter                              |  |  |  |

| t <sub>CH</sub>                                           | Minimum clock high time from clock pin |  |  |  |

| $t_{CL}$                                                  | Minimum clock low time from clock pin  |  |  |  |

| t <sub>CLRP</sub>                                         | LE clear pulse width                   |  |  |  |

| t <sub>PREP</sub>                                         | LE preset pulse width                  |  |  |  |

| t <sub>ESBCH</sub>                                        | Clock high time                        |  |  |  |

| t <sub>ESBCL</sub>                                        | Clock low time                         |  |  |  |

| t <sub>ESBWP</sub>                                        | Write pulse width                      |  |  |  |

| t <sub>ESBRP</sub>                                        | Read pulse width                       |  |  |  |

Tables 40 and 41 describe APEX 20KC external timing parameters. The timing values for these pin-to-pin delays are reported for all pins using the 3.3-V LVTTL I/O standard.

| Table 40. APEX 20KC External Timing Parameters Note (1) |                                                                |            |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------|------------|--|--|--|

| Symbol                                                  | Clock Parameter                                                | Conditions |  |  |  |

| t <sub>INSU</sub>                                       | Setup time with global clock at IOE register                   |            |  |  |  |

| t <sub>INH</sub>                                        | Hold time with global clock at IOE register                    |            |  |  |  |

| t <sub>оитсо</sub>                                      | Clock-to-output delay with global clock at IOE output register | (2)        |  |  |  |

| t <sub>INSUPLL</sub>                                    | Setup time with PLL clock at IOE input register                |            |  |  |  |

| t <sub>INHPLL</sub>                                     | Hold time with PLL clock at IOE input register                 |            |  |  |  |

| tOUTCOPLL                                               | Clock-to-output delay with PLL clock at IOE output register    | (2)        |  |  |  |

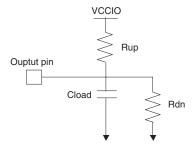

Figure 36. AC Test Conditions for LVTTL, 2.5 V, 1.8 V, PCI & GTL+ I/O Standards

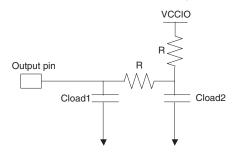

Figure 37. AC Test Conditions for SSTL-3 Class I & II I/O Standards

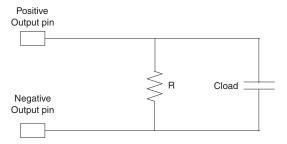

Figure 38. AC Test Conditions for the LVDS I/O Standard

| Symbol                    | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|---------------------------|----------------|------|----------------|------|----------------|------|------|

|                           | Min            | Max  | Min            | Max  | Min            | Max  |      |

| t <sub>INSUBIDIR</sub>    | 1.38           |      | 1.78           |      | 1.99           |      | ns   |

| t <sub>INHBIDIR</sub>     | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>OUTCOBIDIR</sub>   | 2.00           | 3.79 | 2.00           | 4.31 | 2.00           | 4.70 | ns   |

| t <sub>XZBIDIR</sub>      |                | 6.12 |                | 6.51 |                | 7.89 | ns   |

| t <sub>ZXBIDIR</sub>      |                | 6.12 |                | 6.51 |                | 7.89 | ns   |

| t <sub>INSUBIDIRPLL</sub> | 2.82           |      | 3.47           |      | -              |      | ns   |

| t <sub>INHBIDIRPLL</sub>  | 0.00           |      | 0.00           |      | -              |      | ns   |

| †OUTCOBIDIRPLL            | 0.50           | 2.36 | 0.50           | 2.62 | -              | -    | ns   |

| t <sub>XZBIDIRPLL</sub>   |                | 4.69 |                | 4.82 |                | -    | ns   |

| t <sub>ZXBIDIRPLL</sub>   |                | 4.69 |                | 4.82 |                | -    | ns   |

| Table 50. EP20K400C f <sub>MAX</sub> LE Timing Parameters |                |      |                |      |                |      |      |

|-----------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                    | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|                                                           | Min            | Max  | Min            | Max  | Min            | Max  |      |

| $t_{SU}$                                                  | 0.01           |      | 0.01           |      | 0.01           |      | ns   |

| t <sub>H</sub>                                            | 0.10           |      | 0.10           |      | 0.10           |      | ns   |

| $t_{CO}$                                                  |                | 0.27 |                | 0.30 |                | 0.32 | ns   |

| $t_{LUT}$                                                 |                | 0.65 |                | 0.78 |                | 0.92 | ns   |

| Table 61. EP20K600C External Bidirectional Timing Parameters |                |      |                |      |                |      |      |

|--------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                       | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|                                                              | Min            | Max  | Min            | Max  | Min            | Max  | =    |

| t <sub>INSUBIDIR</sub>                                       | 2.03           |      | 2.57           |      | 2.97           |      | ns   |

| t <sub>INHBIDIR</sub>                                        | 0.00           |      | 0.00           |      | 0.00           |      | ns   |

| t <sub>OUTCOBIDIR</sub>                                      | 2.00           | 4.29 | 2.00           | 4.77 | 2.00           | 5.11 | ns   |

| t <sub>XZBIDIR</sub>                                         |                | 8.31 |                | 9.14 |                | 9.76 | ns   |

| t <sub>ZXBIDIR</sub>                                         |                | 8.31 |                | 9.14 |                | 9.76 | ns   |

| t <sub>INSUBIDIRPLL</sub>                                    | 3.99           |      | 4.77           |      | -              |      | ns   |

| t <sub>INHBIDIRPLL</sub>                                     | 0.00           |      | 0.00           |      | -              |      | ns   |

| t <sub>OUTCOBIDIRPLL</sub>                                   | 0.50           | 2.37 | 0.50           | 2.63 | -              | -    | ns   |

| t <sub>XZBIDIRPLL</sub>                                      |                | 6.35 |                | 6.94 |                | -    | ns   |

| t <sub>ZXBIDIRPI I</sub>                                     |                | 6.35 |                | 6.94 |                | -    | ns   |

| Table 62. EP20K1000C f <sub>MAX</sub> LE Timing Microparameters |                |      |                |      |                |      |      |

|-----------------------------------------------------------------|----------------|------|----------------|------|----------------|------|------|

| Symbol                                                          | -7 Speed Grade |      | -8 Speed Grade |      | -9 Speed Grade |      | Unit |

|                                                                 | Min            | Max  | Min            | Max  | Min            | Max  |      |

| $t_{SU}$                                                        | 0.01           |      | 0.01           |      | 0.01           |      | ns   |

| t <sub>H</sub>                                                  | 0.10           |      | 0.10           |      | 0.10           |      | ns   |

| $t_{CO}$                                                        |                | 0.27 |                | 0.30 |                | 0.32 | ns   |

| $t_{LUT}$                                                       |                | 0.66 |                | 0.79 |                | 0.92 | ns   |

SRAM configuration elements allow APEX 20KC devices to be reconfigured in-circuit by loading new configuration data into the device. Real-time reconfiguration is performed by forcing the device into command mode with a device pin, loading different configuration data, reinitializing the device, and resuming user-mode operation. In-field upgrades can be performed by distributing new configuration files.

## **Configuration Schemes**

The configuration data for an APEX 20KC device can be loaded with one of five configuration schemes (see Table 70), chosen on the basis of the target application. An EPC16, EPC2, or EPC1 configuration device, intelligent controller, or the JTAG port can be used to control the configuration of an APEX 20KC device. When a configuration device is used, the system can configure automatically at system power-up.

Multiple APEX 20KC devices can be configured in any of five configuration schemes by connecting the configuration enable (nCE) and configuration enable output (nCEO) pins on each device.

| Table 70. Data Sources for Configuration |                                                                                                                                         |  |  |  |  |

|------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Configuration Scheme                     | Data Source                                                                                                                             |  |  |  |  |

| Configuration device                     | EPC16, EPC8, EPC4, EPC2, or EPC1 configuration device                                                                                   |  |  |  |  |

| Passive serial (PS)                      | MasterBlaster or ByteBlasterMV download cable or serial data source                                                                     |  |  |  |  |

| Passive parallel asynchronous (PPA)      | Parallel data source                                                                                                                    |  |  |  |  |

| Passive parallel synchronous (PPS)       | Parallel data source                                                                                                                    |  |  |  |  |

| JTAG                                     | MasterBlaster or ByteBlasterMV download cable or a microprocessor with a Jam Standard Test and Programming Language (STAPL) or JBC File |  |  |  |  |

For more information on configuration, see *Application Note 116* (*Configuring SRAM-Based LUT Devices*).

# Device Pin-Outs

See the Altera web site (http://www.altera.com) or the *Altera Digital Library* for pin-out information.

# Ordering Information

Figure 39 describes the ordering codes for Stratix devices. For more information on a specific package, refer to the *Altera Device Package Information Data Sheet*.