# E·XFL

# Altera - EP20K600CB652C7 Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

### Details

| Details                        |                                                              |

|--------------------------------|--------------------------------------------------------------|

| Product Status                 | Active                                                       |

| Number of LABs/CLBs            | 2432                                                         |

| Number of Logic Elements/Cells | 24320                                                        |

| Total RAM Bits                 | 311296                                                       |

| Number of I/O                  | 488                                                          |

| Number of Gates                | 1537000                                                      |

| Voltage - Supply               | 1.71V ~ 1.89V                                                |

| Mounting Type                  | Surface Mount                                                |

| Operating Temperature          | 0°C ~ 85°C (TJ)                                              |

| Package / Case                 | 652-BGA                                                      |

| Supplier Device Package        | 652-BGA (45x45)                                              |

| Purchase URL                   | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=ep20k600cb652c7 |

|                                |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Table 4. APEX 20KC FineLine BGA Package Options & I/O Count Notes (1), (2) |     |                |     |  |  |  |  |

|----------------------------------------------------------------------------|-----|----------------|-----|--|--|--|--|

| Device 484 Pin 672 Pin 1,020 Pin                                           |     |                |     |  |  |  |  |

| EP20K200C                                                                  | 376 |                |     |  |  |  |  |

| EP20K400C                                                                  |     | 488 (3)        |     |  |  |  |  |

| EP20K600C                                                                  |     | 508 (3)        | 588 |  |  |  |  |

| EP20K1000C                                                                 |     | 508 <i>(3)</i> | 708 |  |  |  |  |

#### Notes to Tables 3 and 4:

- (1) I/O counts include dedicated input and clock pins.

- (2) APEX 20KC device package types include plastic quad flat pack (PQFP), 1.27-mm pitch ball-grid array (BGA), and 1.00-mm pitch FineLine BGA<sup>™</sup> packages.

- (3) This device uses a thermally enhanced package, which is taller than the regular package. Consult the *Altera Device Package Information Data Sheet* for detailed package size information.

| Table 5. APEX 20KC QFP & BGA Package Sizes |                                      |                                      |             |                 |  |  |

|--------------------------------------------|--------------------------------------|--------------------------------------|-------------|-----------------|--|--|

| Feature                                    | 208-Pin PQFP                         | 240-Pin PQFP                         | 356-Pin BGA | 652-Pin BGA     |  |  |

| Pitch (mm)                                 | 0.50                                 | 0.50                                 | 1.27        | 1.27            |  |  |

| Area (mm <sup>2</sup> )                    | 924                                  | 1,218                                | 1,225       | 2,025           |  |  |

| Length $\times$ Width (mm $\times$ mm)     | $\textbf{30.4} \times \textbf{30.4}$ | $\textbf{34.9} \times \textbf{34.9}$ | 35.0 × 35.0 | 45.0 	imes 45.0 |  |  |

| Table 6. APEX 20KC FineLine BGA Package Sizes |         |         |         |  |  |

|-----------------------------------------------|---------|---------|---------|--|--|

| Feature484 Pin672 Pin1,020 Pin                |         |         |         |  |  |

| Pitch (mm)                                    | 1.00    | 1.00    | 1.00    |  |  |

| Area (mm <sup>2</sup> )                       | 529     | 729     | 1,089   |  |  |

| Length $\times$ Width (mm $\times$ mm)        | 23 × 23 | 27 × 27 | 33 × 33 |  |  |

# General Description

Similar to APEX 20K and APEX 20KE devices, APEX 20KC devices offer the MultiCore architecture, which combines the strengths of LUT-based and product-term-based devices with an enhanced memory structure. LUT-based logic provides optimized performance and efficiency for datapath, register-intensive, mathematical, or digital signal processing (DSP) designs. Product-term-based logic is optimized for complex combinatorial paths, such as complex state machines. LUT- and productterm-based logic combined with memory functions and a wide variety of MegaCore and AMPP functions make the APEX 20KC architecture uniquely suited for SOPC designs. Applications historically requiring a combination of LUT-, product-term-, and memory-based devices can now be integrated into one APEX 20KC device. APEX 20KC devices include additional features such as enhanced I/O standard support, CAM, additional global clocks, and enhanced ClockLock clock circuitry. Table 7 shows the features included in APEX 20KC devices.

| Table 7. APEX 20KC Device Features (Part 1 of 2) |                                                                                                                                                                                                                              |  |  |  |

|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Feature                                          | APEX 20KC Devices                                                                                                                                                                                                            |  |  |  |

| MultiCore system integration                     | Full support                                                                                                                                                                                                                 |  |  |  |

| Hot-socketing support                            | Full support                                                                                                                                                                                                                 |  |  |  |

| SignalTap logic analysis                         | Full support                                                                                                                                                                                                                 |  |  |  |

| 32-/64-bit, 33-MHz PCI                           | Full compliance                                                                                                                                                                                                              |  |  |  |

| 32-/64-bit, 66-MHz PCI                           | Full compliance in -7 and -8 speed grades in selected devices                                                                                                                                                                |  |  |  |

| MultiVolt I/O                                    | 1.8-V, 2.5-V, or 3.3-V $V_{CCIO}$<br>V <sub>CCIO</sub> selected bank by bank<br>5.0-V tolerant with use of external resistor                                                                                                 |  |  |  |

| ClockLock support                                | Clock delay reduction<br>$m/(n \times v)$ clock multiplication<br>Drive ClockLock output off-chip<br>External clock feedback<br>ClockShift circuitry<br>LVDS support<br>Up to four PLLs<br>ClockShift clock phase adjustment |  |  |  |

| Dedicated clock and input pins                   | Eight                                                                                                                                                                                                                        |  |  |  |

| Feature              | APEX 20KC Devices                               |

|----------------------|-------------------------------------------------|

| I/O standard support | 1.8-V, 2.5-V, 3.3-V, 5.0-V I/O                  |

|                      | 3.3-V PCI and PCI-X                             |

|                      | 3.3-V AGP                                       |

|                      | CTT                                             |

|                      | GTL+                                            |

|                      | LVCMOS                                          |

|                      | LVTTL                                           |

|                      | True-LVDS <sup>™</sup> and LVPECL data pins (in |

|                      | EP20K400C and larger devices)                   |

|                      | LVDS and LVPECL clock pins (in all devices      |

|                      | LVDS and LVPECL data pins up to 156 Mbp         |

|                      | (in EP20K200C devices)                          |

|                      | HSTL Class I                                    |

|                      | PCI-X                                           |

|                      | SSTL-2 Class I and II                           |

|                      | SSTL-3 Class I and II                           |

| Memory support       | CAM                                             |

|                      | Dual-port RAM                                   |

|                      | FIFO                                            |

|                      | RAM                                             |

|                      | ROM                                             |

All APEX 20KC devices are reconfigurable and are 100% tested prior to shipment. As a result, test vectors do not have to be generated for fault-coverage purposes. Instead, the designer can focus on simulation and design verification. In addition, the designer does not need to manage inventories of different application-specific integrated circuit (ASIC) designs; APEX 20KC devices can be configured on the board for the specific functionality required.

APEX 20KC devices are configured at system power-up with data stored in an Altera serial configuration device or provided by a system controller. Altera offers in-system programmability (ISP)-capable EPC16, EPC8, EPC4, EPC2, and EPC1 configuration devices and one-time programmable (OTP) EPC1 configuration devices, which configure APEX 20KC devices via a serial data stream. Moreover, APEX 20KC devices contain an optimized interface that permits microprocessors to configure APEX 20KC devices serially or in parallel, and synchronously or asynchronously. The interface also enables microprocessors to treat APEX 20KC devices as memory and configure the device by writing to a virtual memory location, making reconfiguration easy.

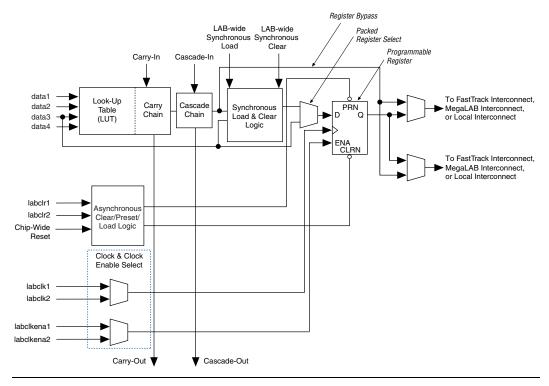

## Figure 5. APEX 20KC Logic Element

Each LE's programmable register can be configured for D, T, JK, or SR operation. The register's clock and clear control signals can be driven by global signals, general-purpose I/O pins, or any internal logic. For combinatorial functions, the register is bypassed and the output of the LUT drives the outputs of the LE.

Each LE has two outputs that drive the local, MegaLAB, or FastTrack interconnect routing structure. Each output can be driven independently by the LUT's or register's output. For example, the LUT can drive one output while the register drives the other output. This feature, called register packing, improves device utilization because the register and the LUT can be used for unrelated functions. The LE can also drive out registered and unregistered versions of the LUT output.

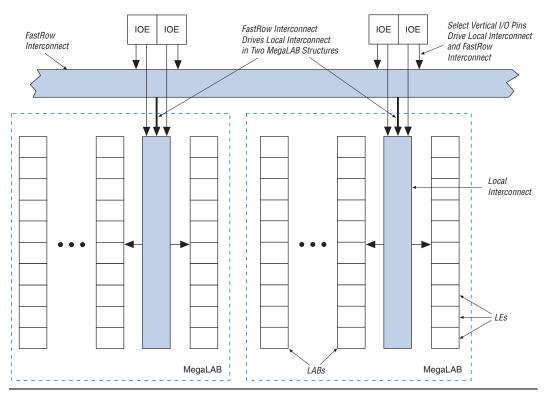

Figure 12. APEX 20KC FastRow Interconnect

Table 8 summarizes how various elements of the APEX 20KC architecture drive each other.

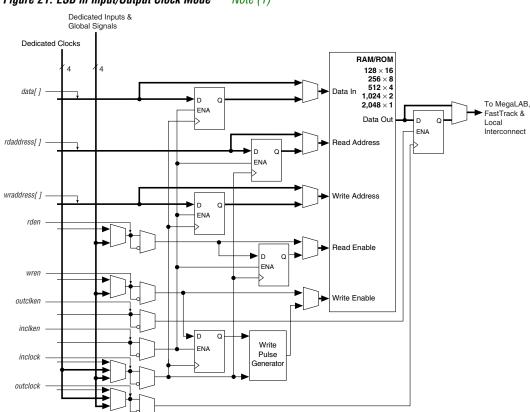

# Input/Output Clock Mode

The input/output clock mode contains two clocks. One clock controls all registers for inputs into the ESB: data input, WE, RE, read address, and write address. The other clock controls the ESB data output registers. The ESB also supports clock enable and asynchronous clear signals; these signals also control the reading and writing of registers independently. Input/output clock mode is commonly used for applications where the reads and writes occur at the same system frequency, but require different clock enable signals for the input and output registers. Figure 21 shows the ESB in input/output clock mode.

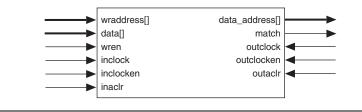

Figure 21. ESB in Input/Output Clock Mode Note (1)

## Note to Figure 21:

(1) All registers can be cleared asynchronously by ESB local interconnect signals, global signals, or the chip-wide reset.

CAM is used for high-speed search operations. When searching for data within a RAM block, the search is performed serially. Thus, finding a particular data word can take many cycles. CAM searches all addresses in parallel and outputs the address storing a particular word. When a match is found, a match flag is set high. Figure 23 shows the CAM block diagram.

#### Figure 23. APEX 20KC CAM Block Diagram

CAM can be used in any application requiring high-speed searches, such as networking, communications, data compression, and cache management.

The APEX 20KC on-chip CAM provides faster system performance than traditional discrete CAM. Integrating CAM and logic into the APEX 20KC device eliminates off-chip and on-chip delays, improving system performance.

When in CAM mode, the ESB implements 32-word, 32-bit CAM. Wider or deeper CAM can be implemented by combining multiple CAMs with some ancillary logic implemented in LEs. The Quartus II software combines ESBs and LEs automatically to create larger CAMs.

CAM supports writing "don't care" bits into words of the memory. The "don't care" bit can be used as a mask for CAM comparisons; any bit set to "don't care" has no effect on matches.

The output of the CAM can be encoded or unencoded. When encoded, the ESB outputs an encoded address of the data's location. For instance, if the data is located in address 12, the ESB output is 12. When unencoded, the ESB uses its 16 outputs to show the location of the data over two clock cycles. In this case, if the data is located in address 12, the 12th output line goes high. When using unencoded outputs, two clock cycles are required to read the output because a 16-bit output bus is used to show the status of 32 words.

The encoded output is better suited for designs that ensure duplicate data is not written into the CAM. If duplicate data is written into two locations, the CAM's output will be incorrect. If the CAM may contain duplicate data, the unencoded output is a better solution; CAM with unencoded outputs can distinguish multiple data locations.

CAM can be pre-loaded with data during configuration, or it can be written during system operation. In most cases, two clock cycles are required to write each word into CAM. When "don't care" bits are used, a third clock cycle is required.

For more information on APEX 20KC devices and CAM, see *Application* Note 119 (Implementing High-Speed Search Applications with APEX CAM).

# Driving Signals to the ESB

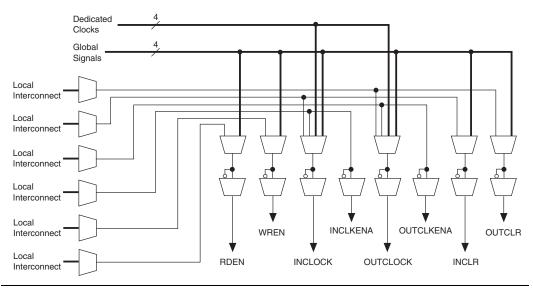

ESBs provide flexible options for driving control signals. Different clocks can be used for the ESB inputs and outputs. Registers can be inserted independently on the data input, data output, read address, write address, WE, and RE signals. The global signals and the local interconnect can drive the WE and RE signals. The global signals, dedicated clock pins, and local interconnect can drive the ESB clock signals. Because the LEs drive the local interconnect, the LEs can control the WE and RE signals and the ESB clock, clock enable, and asynchronous clear signals. Figure 24 shows the ESB control signal generation logic.

Figure 24. ESB Control Signal Generation

An ESB is fed by the local interconnect, which is driven by adjacent LEs (for high-speed connection to the ESB) or the MegaLAB interconnect. The ESB can drive the local, MegaLAB, or FastTrack interconnect routing structure to drive LEs and IOEs in the same MegaLAB structure or anywhere in the device.

The register in the APEX 20KC IOE can be programmed to power-up high or low after configuration is complete. If it is programmed to power-up low, an asynchronous clear can control the register. If it is programmed to power-up high, an asynchronous preset can control the register. This feature is useful for cases where the APEX 20KC device controls an activelow input or another device; it prevents inadvertent activation of the input upon power-up.

Figure 25 shows how fast bidirectional I/O pins are implemented in APEX 20KC devices. This feature is useful for cases where the APEX 20KC device controls an active-low input or another device; it prevents inadvertent activation of the input upon power-up.

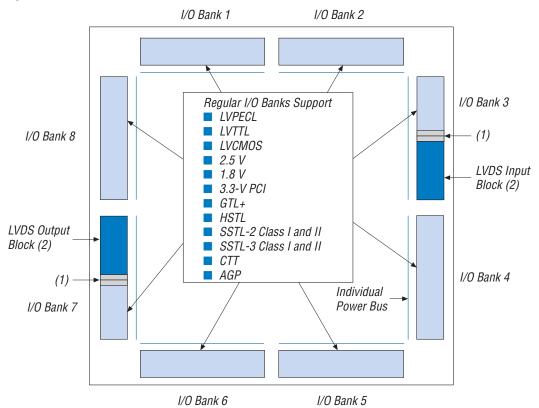

#### Figure 28. APEX 20KC I/O Banks

#### Notes to Figure 28:

- For more information on placing I/O pins in LVDS blocks, refer to the "Guidelines for Using LVDS Blocks" section in Application Note 120 (Using LVDS in APEX 20KE Devices).

- (2) If the LVDS input and output blocks are not used for LVDS, they can support all of the I/O standards and can be used as input, output, or bidirectional pins with V<sub>CCIO</sub> set to 3.3 V, 2.5 V, or 1.8 V.

## **Power Sequencing & Hot Socketing**

Because APEX 20KC devices can be used in a mixed-voltage environment, they have been designed specifically to tolerate any possible power-up sequence. Therefore, the  $V_{CCIO}$  and  $V_{CCINT}$  power supplies may be powered in any order.

Signals can be driven into APEX 20KC devices before and during powerup without damaging the device. In addition, APEX 20KC devices do not drive out during power-up. Once operating conditions are reached and the device is configured, APEX 20KC devices operate as specified by the user.

# MultiVolt I/O Interface

The APEX architecture supports the MultiVolt I/O interface feature, which allows APEX devices in all packages to interface with systems of different supply voltages. The devices have one set of VCC pins for internal operation and input buffers (VCCINT), and another set for I/O output drivers (VCCIO).

APEX 20KC devices support the MultiVolt I/O interface feature. The APEX 20KC VCCINT pins must always be connected to a 1.8-V power supply. With a 1.8-V V<sub>CCINT</sub> level, input pins are 1.8-V, 2.5-V, and 3.3-V tolerant. The VCCIO pins can be connected to either a 1.8-V, 2.5-V, or 3.3-V power supply, depending on the I/O standard requirements. When the VCCIO pins are connected to a 1.8-V power supply, the output levels are compatible with 1.8-V systems. When VCCIO pins are connected to a 2.5-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output levels are compatible with 2.5-V systems. When VCCIO pins are connected to a 3.3-V power supply, the output high is 3.3 V and compatible with 3.3-V or 5.0-V systems. An APEX 20KC device is 5.0-V tolerant with the addition of a resistor and the PCI clamp diode enabled.

For more information on 5.0-V tolerance, refer to the "5.0-V Tolerance in APEX 20KE Devices White Paper," as the information found therein also applies to APEX 20KC devices.

| Table 10. APEX 20KC MultiVolt I/O Support                                  |     |              |                       |                         |              |                      |              |              |  |

|----------------------------------------------------------------------------|-----|--------------|-----------------------|-------------------------|--------------|----------------------|--------------|--------------|--|

| V <sub>CCIO</sub> (V)         Input Signals (V)         Output Signals (V) |     |              |                       |                         |              |                      |              |              |  |

|                                                                            | 1.8 | 2.5          | 3.3                   | 5.0                     | 1.8          | 2.5                  | 3.3          | 5.0          |  |

| 1.8                                                                        | ~   | ✓ (1)        | 🗸 (1)                 |                         | $\checkmark$ |                      |              |              |  |

| 2.5                                                                        |     | ~            | <ul><li>(1)</li></ul> |                         |              | <ul> <li></li> </ul> |              |              |  |

| 3.3                                                                        |     | $\checkmark$ | $\checkmark$          | <ul> <li>(2)</li> </ul> |              | ✓ (3)                | $\checkmark$ | $\checkmark$ |  |

Table 10 summarizes APEX 20KC MultiVolt I/O support.

#### Notes to Table 10:

The PCI clamping diode must be disabled to drive an input with voltages higher than V<sub>CCIO</sub>, except for the 5.0-V input case.

(2) An APEX 20KC device can be made 5.0-V tolerant with the addition of an external resistor and the PCI clamp diode enabled.

(3) When V<sub>CCIO</sub> = 3.3 V, an APEX 20KC device can drive a 2.5-V device with 3.3-V tolerant inputs.

#### Altera Corporation

#### Clock Multiplication

The APEX 20KC ClockBoost circuit can multiply or divide clocks by a programmable number. The clock can be multiplied by  $m/(n \times k)$ , where m and k range from 2 to 160 and n ranges from 1 to 16. Clock multiplication and division can be used for time-domain multiplexing and other functions, which can reduce design LE requirements.

#### Clock Phase & Delay Adjustment

The APEX 20KC ClockShift feature allows the clock phase and delay to be adjusted. The clock phase can be adjusted by 90° steps. The clock delay can be adjusted to increase or decrease the clock delay by an arbitrary amount, up to one clock period.

#### LVDS Support

All APEX 20KC devices support differential LVDS buffers on the input and output clock signals that interface with external devices. This is controlled in the Quartus II software by assigning the clock pins with an LVDS I/O standard assignment.

Two high-speed PLLs are designed to support the LVDS interface. When using LVDS, the I/O clock runs at a slower rate than the data transfer rate. Thus, PLLs are used to multiply the I/O clock internally to capture the LVDS data. For example, an I/O clock may run at 105 MHz to support 840 Mbps LVDS data transfer. In this example, the PLL multiplies the incoming clock by eight to support the high-speed data transfer. You can use PLLs in EP20K400C and larger devices for high-speed LVDS interfacing.

#### Lock Signals

The APEX 20KC ClockLock circuitry supports individual LOCK signals. The LOCK signal drives high when the ClockLock circuit has locked onto the input clock. The LOCK signals are optional for each ClockLock circuit; when not used, they are I/O pins. Tables 11 and 12 summarize the ClockLock and ClockBoost parameters for APEX 20KC devices.

| Symbol                        | Parameter                                                    | Condition   | Min    | Tun | Max                          | Unit |

|-------------------------------|--------------------------------------------------------------|-------------|--------|-----|------------------------------|------|

| Symbol                        | Falameter                                                    | Contraction | IVIIII | Тур | IVIAX                        | Unit |

| t <sub>R</sub>                | Input rise time                                              |             |        |     | 5                            | ns   |

| t <sub>F</sub>                | Input fall time                                              |             |        |     | 5                            | ns   |

| t <sub>INDUTY</sub>           | Input duty cycle                                             |             | 40     |     | 60                           | %    |

| t <sub>INJITTER</sub>         | Input jitter peak-to-peak                                    |             |        |     | 2% of input<br>period        | %    |

| t <sub>OUTJITTER</sub>        | RMS jitter on ClockLock or<br>ClockBoost-generated clock     |             |        |     | 0.35% of<br>output<br>period | %    |

| <sup>t</sup> ουτ <i>D</i> UTY | Duty cycle for ClockLock or<br>ClockBoost-generated clock    |             | 45     |     | 55                           | %    |

| $t_{LOCK}(2)_{,}(3)$          | Time required for ClockLock or<br>ClockBoost to acquire lock |             |        |     | 40                           | μS   |

| Table 12. APEX 20KC Clock Input & Output Parameters (Part 1 of 2)       Note (1) |                                               |                             |     |                |     |       |     |  |

|----------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------|-----|----------------|-----|-------|-----|--|

| Symbol                                                                           | Parameter                                     | I/O Standard -7 Speed Grade |     | -8 Speed Grade |     | Units |     |  |

|                                                                                  |                                               |                             | Min | Max            | Min | Max   |     |  |

| f <sub>VCO</sub> (4)                                                             | Voltage controlled oscillator operating range |                             | 200 | 500            | 200 | 500   | MHz |  |

| f <sub>CLOCK0</sub>                                                              | Clock0 PLL output frequency for internal use  |                             | 1.5 | 335            | 1.5 | 200   | MHz |  |

| f <sub>CLOCK1</sub>                                                              | Clock1 PLL output frequency for internal use  |                             | 20  | 335            | 20  | 200   | MHz |  |

| f <sub>CLOCK0_EXT</sub>                                                          | Output clock frequency for                    | 3.3-V LVTTL                 | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  | external clock0 output                        | 2.5-V LVTTL                 | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | 1.8-V LVTTL                 | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | GTL+                        | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | SSTL-2 Class I              | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | SSTL-2 Class II             | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | SSTL-3 Class I              | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | SSTL-3 Class II             | (5) | (5)            | (5) | (5)   | MHz |  |

|                                                                                  |                                               | LVDS                        | (5) | (5)            | (5) | (5)   | MHz |  |

# IEEE Std. 1149.1 (JTAG) Boundary-Scan Support

All APEX 20KC devices provide JTAG BST circuitry that complies with the IEEE Std. 1149.1-1990 specification. JTAG boundary-scan testing can be performed before or after configuration, but not during configuration. APEX 20KC devices can also use the JTAG port for configuration with the Quartus II software or with hardware using either Jam Files (**.jam**) or Jam Byte-Code Files (**.jbc**). Finally, APEX 20KC devices use the JTAG port to monitor the logic operation of the device with the SignalTap embedded logic analyzer. APEX 20KC devices support the JTAG instructions shown in Table 13.

| Table 13. APEX 20k        | Table 13. APEX 20KC JTAG Instructions                                                                                                                                                                                                |  |  |  |  |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| JTAG Instruction          | Description                                                                                                                                                                                                                          |  |  |  |  |  |

| SAMPLE/PRELOAD            | Allows a snapshot of signals at the device pins to be captured and examined during normal device operation, and permits an initial data pattern to be output at the device pins. Also used by the SignalTap embedded logic analyzer. |  |  |  |  |  |

| EXTEST                    | Allows the external circuitry and board-level interconnections to be tested by forcing a test pattern at the output pins and capturing test results at the input pins.                                                               |  |  |  |  |  |

| BYPASS                    | Places the 1-bit bypass register between the TDI and TDO pins, which allows the BST data to pass synchronously through selected devices to adjacent devices during normal device operation.                                          |  |  |  |  |  |

| USERCODE                  | Selects the 32-bit USERCODE register and places it between the TDI and TDO pins, allowing the USERCODE to be serially shifted out of TDO.                                                                                            |  |  |  |  |  |

| IDCODE                    | Selects the IDCODE register and places it between TDI and TDO, allowing the IDCODE to be serially shifted out of TDO.                                                                                                                |  |  |  |  |  |

| ICR Instructions          | Used when configuring an APEX 20KC device via the JTAG port with a MasterBlaster <sup>TM</sup> or ByteBlasterMV <sup>TM</sup> download cable, or when using a Jam File or Jam Byte-Code File via an embedded processor.              |  |  |  |  |  |

| SignalTap<br>Instructions | Monitors internal device operation with the SignalTap embedded logic analyzer.                                                                                                                                                       |  |  |  |  |  |

#### APEX 20KC Programmable Logic Device Data Sheet

| Table 20. APEX 20KC Device CapacitanceNote (10) |                                             |                                     |     |     |      |  |  |

|-------------------------------------------------|---------------------------------------------|-------------------------------------|-----|-----|------|--|--|

| Symbol                                          | Parameter                                   | Conditions                          | Min | Max | Unit |  |  |

| C <sub>IN</sub>                                 | Input capacitance                           | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 8   | pF   |  |  |

| CINCLK                                          | Input capacitance on<br>dedicated clock pin | V <sub>IN</sub> = 0 V, f = 1.0 MHz  |     | 12  | pF   |  |  |

| C <sub>OUT</sub>                                | Output capacitance                          | V <sub>OUT</sub> = 0 V, f = 1.0 MHz |     | 8   | pF   |  |  |

#### Notes to Tables 17 through 20:

(1) See the Operating Requirements for Altera Devices Data Sheet.

- (2) Minimum DC input is -0.5 V. During transitions, the inputs may undershoot to -2.0 V or overshoot to 4.6 V for input currents less than 100 mA and time periods shorter than 20 ns.

- (3) Numbers in parentheses are for industrial-temperature-range devices.

- (4) Maximum  $V_{CC}$  rise time is 100 ms, and  $V_{CC}$  must rise monotonically.

- (5) All pins, including dedicated inputs, clock, I/O, and JTAG pins, may be driven before V<sub>CCINT</sub> and V<sub>CCIO</sub> are powered.

- (6) Typical values are for  $T_A = 25^\circ$  C,  $V_{CCINT} = 1.8$  V, and  $V_{CCIO} = 1.8$  V, 2.5 V or 3.3 V.

- (7) These values are specified under the APEX 20KC device recommended operating conditions, shown in Table 18 on page 55.

- (8) This value is specified for normal device operation. The value may vary during power-up.

- (9) Pin pull-up resistance values will be lower if an external source drives the pin higher than V<sub>CCIO</sub>.

- (10) Capacitance is sample-tested only.

Tables 21 through 35 list the DC operating specifications for the supported I/O standards. These tables list minimal specifications only; APEX 20KC devices may exceed these specifications.

| Table 21. LVTTL I/O Specifications |                           |                                                                  |         |                         |       |  |  |  |

|------------------------------------|---------------------------|------------------------------------------------------------------|---------|-------------------------|-------|--|--|--|

| Symbol                             | Parameter                 | Conditions                                                       | Minimum | Maximum                 | Units |  |  |  |

| V <sub>CCIO</sub>                  | Output supply voltage     |                                                                  | 3.0     | 3.6                     | V     |  |  |  |

| V <sub>IH</sub>                    | High-level input voltage  |                                                                  | 2.0     | V <sub>CCIO</sub> + 0.3 | V     |  |  |  |

| V <sub>IL</sub>                    | Low-level input voltage   |                                                                  | -0.3    | 0.8                     | V     |  |  |  |

| I <sub>I</sub>                     | Input pin leakage current | V <sub>IN</sub> = 0 V or 3.3 V                                   | -10     | 10                      | μA    |  |  |  |

| V <sub>OH</sub>                    | High-level output voltage | I <sub>OH</sub> = -12 mA,<br>V <sub>CCIO</sub> = 3.0 V (1)       | 2.4     |                         | V     |  |  |  |

| V <sub>OL</sub>                    | Low-level output voltage  | I <sub>OL</sub> = 12 mA,<br>V <sub>CCIO</sub> = 3.0 V <i>(2)</i> |         | 0.4                     | V     |  |  |  |

| Table 22. LVCMOS I/O Specifications |                              |                                                                  |                         |                         |       |  |

|-------------------------------------|------------------------------|------------------------------------------------------------------|-------------------------|-------------------------|-------|--|

| Symbol                              | Parameter                    | Conditions                                                       | Minimum                 | Maximum                 | Units |  |

| V <sub>CCIO</sub>                   | Power supply voltage range   |                                                                  | 3.0                     | 3.6                     | V     |  |

| V <sub>IH</sub>                     | High-level input voltage     |                                                                  | 2.0                     | V <sub>CCIO</sub> + 0.3 | V     |  |

| V <sub>IL</sub>                     | Low-level input voltage      |                                                                  | -0.3                    | 0.8                     | V     |  |

| I                                   | Input pin leakage<br>current | V <sub>IN</sub> = 0 V or 3.3 V                                   | -10                     | 10                      | μA    |  |

| V <sub>OH</sub>                     | High-level output voltage    | $V_{CCIO} = 3.0 V$<br>$I_{OH} = -0.1 \text{ mA} (1)$             | V <sub>CCIO</sub> – 0.2 |                         | V     |  |

| V <sub>OL</sub>                     | Low-level output voltage     | V <sub>CCIO</sub> = 3.0 V<br>I <sub>OL</sub> = 0.1 mA <i>(2)</i> |                         | 0.2                     | V     |  |

| Table 23. 2.5-V I/O Specifications |                              |                                     |         |                         |       |  |  |

|------------------------------------|------------------------------|-------------------------------------|---------|-------------------------|-------|--|--|

| Symbol                             | Parameter                    | Conditions                          | Minimum | Maximum                 | Units |  |  |

| V <sub>CCIO</sub>                  | Output supply voltage        |                                     | 2.375   | 2.625                   | V     |  |  |

| V <sub>IH</sub>                    | High-level input voltage     |                                     | 1.7     | V <sub>CCIO</sub> + 0.3 | V     |  |  |

| V <sub>IL</sub>                    | Low-level input voltage      |                                     | -0.3    | 0.8                     | V     |  |  |

| lı                                 | Input pin leakage current    | V <sub>IN</sub> = 0 V or 3.3 V      | -10     | 10                      | μA    |  |  |

| V <sub>OH</sub>                    | High-level output<br>voltage | I <sub>OH</sub> = -0.1 mA (1)       | 2.1     |                         | V     |  |  |

|                                    |                              | I <sub>OH</sub> = -1 mA (1)         | 2.0     |                         | V     |  |  |

|                                    |                              | $I_{OH} = -2 \text{ mA} (1)$        | 1.7     |                         | V     |  |  |

| V <sub>OL</sub>                    | Low-level output<br>voltage  | I <sub>OL</sub> = 0.1 mA <i>(2)</i> |         | 0.2                     | V     |  |  |

|                                    |                              | I <sub>OL</sub> = 1 mA <i>(2)</i>   |         | 0.4                     | V     |  |  |

|                                    |                              | I <sub>OL</sub> = 2 mA <i>(2)</i>   |         | 0.7                     | V     |  |  |

| Table 34. 3.3-V AGP I/O Specifications |                              |                             |                        |         |                         |            |  |

|----------------------------------------|------------------------------|-----------------------------|------------------------|---------|-------------------------|------------|--|

| Symbol                                 | Parameter                    | Conditions                  | Minimum                | Typical | Maximum                 | Units      |  |

| V <sub>CCIO</sub>                      | I/O supply voltage           |                             | 3.15                   | 3.3     | 3.45                    | V          |  |

| V <sub>REF</sub>                       | Reference voltage            |                             | $0.39 \times V_{CCIO}$ |         | $0.41 \times V_{CCIO}$  | V          |  |

| V <sub>IH</sub>                        | High-level input voltage     |                             | $0.5 	imes V_{CCIO}$   |         | V <sub>CCIO</sub> + 0.5 | V          |  |

| V <sub>IL</sub>                        | Low-level input voltage      |                             |                        |         | $0.3 \times V_{CCIO}$   | V          |  |

| V <sub>OH</sub>                        | High-level output voltage    | I <sub>OUT</sub> = -500 μA  | $0.9 	imes V_{CCIO}$   |         | 3.6                     | V          |  |

| V <sub>OL</sub>                        | Low-level output voltage     | l <sub>OUT</sub> = 1,500 μA |                        |         | $0.1 \times V_{CCIO}$   | V          |  |

| lı                                     | Input pin leakage<br>current | $0 < V_{IN} < V_{CCIO}$     | -10                    |         | 10                      | μ <b>A</b> |  |

| Table 35. CTT I/O Specifications      |                                                      |                                   |                        |         |                        |       |

|---------------------------------------|------------------------------------------------------|-----------------------------------|------------------------|---------|------------------------|-------|

| Symbol                                | Parameter                                            | Conditions                        | Minimum                | Typical | Maximum                | Units |

| V <sub>CCIO</sub>                     | I/O supply voltage                                   |                                   | 3.0                    | 3.3     | 3.6                    | V     |

| V <sub>TT</sub> /V <sub>REF</sub> (3) | Termination and reference voltage                    |                                   | 1.35                   | 1.5     | 1.65                   | V     |

| V <sub>IH</sub>                       | High-level input voltage                             |                                   | V <sub>REF</sub> + 0.2 |         |                        | V     |

| V <sub>IL</sub>                       | Low-level input voltage                              |                                   |                        |         | V <sub>REF</sub> – 0.2 | V     |

| I <sub>I</sub>                        | Input pin leakage<br>current                         | $0 < V_{IN} < V_{CCIO}$           | -10                    |         | 10                     | μA    |

| V <sub>OH</sub>                       | High-level output voltage                            | I <sub>OH</sub> = -8 mA (1)       | V <sub>REF</sub> + 0.4 |         |                        | V     |

| V <sub>OL</sub>                       | Low-level output voltage                             | I <sub>OL</sub> = 8 mA <i>(2)</i> |                        |         | V <sub>REF</sub> – 0.4 | V     |

| Ι <sub>Ο</sub>                        | Output leakage<br>current (when output<br>is high Z) | $GND \leq V_{OUT} \leq V_{CCIO}$  | -10                    |         | 10                     | μA    |

Notes to Tables 21 through 35:

(1) The I<sub>OH</sub> parameter refers to high-level output current.

(2) The I<sub>OL</sub> parameter refers to low-level output current. This parameter applies to open-drain pins as well as output pins.

(3)  $V_{\text{REF}}$  specifies center point of switching range.

Figure 31 shows the output drive characteristics of APEX 20KC devices.

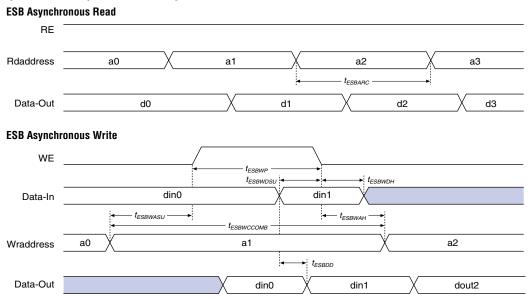

## Figure 33. ESB Asynchronous Timing Waveforms

a2

dout1

t<sub>ESBDATASU</sub>

t<sub>ESBDATAH</sub>

t<sub>ESBSWC</sub>

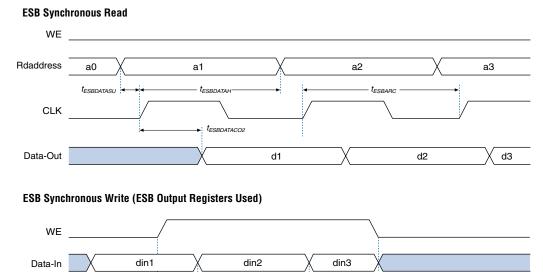

Figure 34. ESB Synchronous Timing Waveforms

Figure 35 shows the timing model for bidirectional I/O pin timing.

din1

a3

$t_{ESBWEH} \longrightarrow$

t<sub>ESBDATACO1</sub>

din2

a2

din3

din2

Wraddress

CLK

Data-Out

a0

a1

dout0

t<sub>ESBWESU</sub>