# E·XFL

#### NXP USA Inc. - MC9RS08KA2CPC Datasheet

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | -                                                                     |

| Core Size                  | -                                                                     |

| Speed                      | -                                                                     |

| Connectivity               | -                                                                     |

| Peripherals                | -                                                                     |

| Number of I/O              | -                                                                     |

| Program Memory Size        | -                                                                     |

| Program Memory Type        | -                                                                     |

| EEPROM Size                | -                                                                     |

| RAM Size                   |                                                                       |

| Voltage - Supply (Vcc/Vdd) | -                                                                     |

| Data Converters            | -                                                                     |

| Oscillator Type            | -                                                                     |

| Operating Temperature      | -                                                                     |

| Mounting Type              | -                                                                     |

| Package / Case             | -                                                                     |

| Supplier Device Package    | · · · · · · · · · · · · · · · · · · ·                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc9rs08ka2cpc |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# MC9RS08KA2 Features

#### 8-Bit RS08 Central Processor Unit (CPU)

- Simplified S08 instruction set with added high-performance instructions

- LDA, STA, and CLR instructions support the short addressing mode; address \$0000 to \$001F can be accessed via a single-byte instruction

- ADD, SUB, INC, and DEC instructions support the tiny addressing mode; address \$0000 to \$000F can be accessed via a single-byte instruction with reduced instruction cycle

- Shadow PC register instructions: SHA and SLA

- Pending interrupt indication

- Index addressing via D[X] and X register

- Direct page access to the entire memory map through paging window

#### Memory

- On-chip Flash EEPROM

- MC9RS08KA2: 2048 bytes

- MC9RS08KA1: 1024 bytes

- 63 bytes on-chip RAM

#### **Power-Saving Modes**

- Wait and stop

- Wakeup from power-saving modes using real-time interrupt (RTI), KBI, or ACMP

#### **Clock Source**

- ICS Trimmable 20-MHz internal clock source

- Up to 10-MHz internal bus operation

- 0.2% trimmable resolution, 2% deviation over temperature and voltage range

#### **System Protection**

- Computer operating properly (COP) reset running off bus-independent clock source

- Low-voltage detection with reset or stop wakeup

#### Peripherals

- MTIM 8-bit modulo timer

- ACMP Analog comparator

- Full rail-to-rail supply operation

- Option to compare to fixed internal bandgap reference voltage

- Can operate in stop mode

- **KBI** Keyboard interrupt ports

- Three KBI ports in 6-pin package

- Five KBI ports in 8-pin package

#### **Development Support**

- Background debug system

- Breakpoint capability to allow single breakpoint setting during in-circuit debug

#### **Package Options**

- 6-pin dual flat no lead (DFN) package

- Two general-purpose input/output (I/O) pins

- One general-purpose input pin

- One general-purpose output pin

- 8-pin plastic dual in-line pin (PDIP) package

- Four general-purpose input/output (I/O) pins

- One general-purpose input pin

- One general-purpose output pin

- 8-pin narrow body SOIC package

- Four general-purpose input/output (I/O) pins

- One general-purpose input pin

- One general-purpose output pin

## Chapter 1 MC9RS08KA2 Series Device Overview

### 1.1 Overview

The MC9RS08KA2 Series microcontroller unit (MCU) is an extremely low-cost, small pin count device for home appliances, toys, and small geometry applications. This device is composed of standard on-chip modules including, a very small and highly efficient RS08 CPU core, 63 bytes RAM, 2K bytes Flash, an 8-bit modulo timer, keyboard interrupt, and analog comparator. The device is available in small 6- and 8-pin packages.

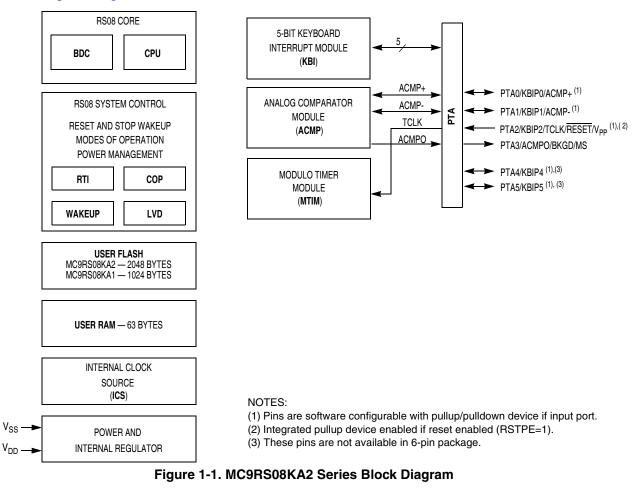

### 1.2 MCU Block Diagram

The block diagram, Figure 1-1, shows the structure of the MC9RS08KA2 Series MCU.

Chapter 4 Memory

- Up to 1000 program/erase cycles at typical voltage and temperature

- Security feature for Flash

### 4.6.2 Flash Programming Procedure

Programming of Flash memory is done on a row basis. A row consists of 64 consecutive bytes starting from addresses \$3X00, \$3X40, \$3X80, or \$3XC0. Use the following procedure to program a row of Flash memory:

- 1. Apply external V<sub>PP</sub>.

- 2. Set the PGM bit. This configures the memory for program operation and enables the latching of address and data for programming.

- 3. Write any data to any Flash location, via the high page accessing window \$00C0-\$00FF, within the address range of the row to be programmed. (Prior to the data writing operation, the PAGESEL register must be configured correctly to map the high page accessing window to the corresponding Flash row).

- 4. Wait for a time,  $t_{nvs}$ .

- 5. Set the HVEN bit.

- 6. Wait for a time,  $t_{pgs}$ .

- 7. Write data to the Flash location to be programmed.

- 8. Wait for a time, t<sub>prog</sub>.

- 9. Repeat steps 7 and 8 until all bytes within the row are programmed.

- 10. Clear the PGM bit.

- 11. Wait for a time, t<sub>nvh</sub>.

- 12. Clear the HVEN bit.

- 13. After time,  $t_{rcv}$ , the memory can be accessed in read mode again.

- 14. Remove external V<sub>PP</sub>.

This program sequence is repeated throughout the memory until all data is programmed.

#### NOTE

Flash memory cannot be programmed or erased by software code executed from Flash locations. To program or erase Flash, commands must be executed from RAM or BDC commands. User code should not enter wait or stop during erase or program sequence.

These operations must be performed in the order shown; other unrelated operations may occur between the steps.

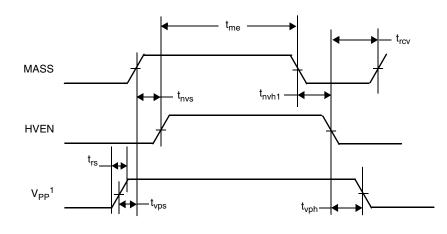

### 4.6.3 Flash Mass Erase Operation

Use the following procedure to mass erase the entire Flash memory:

- 1. Apply external V<sub>PP</sub>.

- 2. Set the MASS bit in the Flash control register.

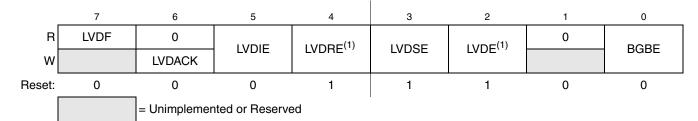

# 5.8.5 System Power Management Status and Control 1 Register (SPMSC1)

This high page register contains status and control bits to support the low voltage detect function, and to enable the bandgap voltage reference for use by the ACMP and the LVD module.

<sup>1</sup> This bit can be written only one time after reset. Additional writes are ignored.

#### Figure 5-6. System Power Management Status and Control 1 Register (SPMSC1)

| Field       | Description                                                                                                                                                                                                                                                                                            |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7<br>LVDF   | Low-Voltage Detect Flag — Provided LVDE = 1, this read-only status bit indicates a low-voltage detect event.                                                                                                                                                                                           |

| 6<br>LVDACK | <b>Low-Voltage Detect Acknowledge</b> — This write-only bit is used to acknowledge low voltage detection errors (write 1 to clear LVDF). Reads always return 0.                                                                                                                                        |

| 5<br>LVDIE  | <ul> <li>Low-Voltage Detect Interrupt Enable — This bit enables hardware interrupt requests for LVDF.</li> <li>0 Hardware interrupt disabled (use polling).</li> <li>1 Request a hardware interrupt when LVDF = 1.</li> </ul>                                                                          |

| 4<br>LVDRE  | <ul> <li>Low-Voltage Detect Reset Enable — This write-once bit enables low-voltage detect events to generate a hardware reset (provided LVDE = 1).</li> <li>0 LVDF does not generate hardware resets.</li> <li>1 Force an MCU reset when LVDF = 1.</li> </ul>                                          |

| 3<br>LVDSE  | <ul> <li>Low-Voltage Detect Stop Enable — Provided LVDE = 1, this read/write bit determines whether the low-voltage detect function operates when the MCU is in stop mode.</li> <li>0 Low-voltage detect disabled during stop mode.</li> <li>1 Low-voltage detect enabled during stop mode.</li> </ul> |

| 2<br>LVDE   | <ul> <li>Low-Voltage Detect Enable — This write-once bit enables low-voltage detect logic and qualifies the operation of other bits in this register.</li> <li>0 LVD logic disabled.</li> <li>1 LVD logic enabled.</li> </ul>                                                                          |

| 0<br>BGBE   | <ul> <li>Bandgap Buffer Enable — This bit enables an internal buffer for the bandgap voltage reference for use by the ACMP module on one of its internal channels.</li> <li>0 Bandgap buffer disabled.</li> <li>1 Bandgap buffer enabled.</li> </ul>                                                   |

#### Table 5-8. SPMSC1 Register Field Descriptions

Chapter 5 Resets, Interrupts, and General System Control

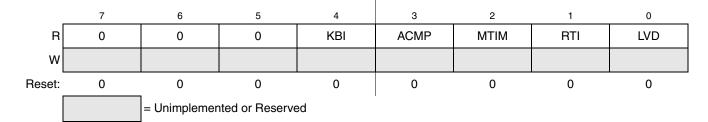

### 5.8.6 System Interrupt Pending Register (SIP1)

This high page register contains status of the pending interrupt from the modules.

#### Figure 5-7. System Interrupt Pending Register (SIP1)

| Field     | Description                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4<br>KBI  | <ul> <li>Keyboard Interrupt Pending — This read-only bit indicates there is a pending interrupt from the KBI module.</li> <li>Clearing the KBF flag of the KBISC register clears this bit. Reset also clears this bit.</li> <li>0 There is no pending KBI interrupt; i.e., KBF flag and/or KBIE bit is cleared.</li> <li>1 There is a pending KBI interrupt; i.e., KBF flag and KBIE bit are set.</li> </ul>                              |

| 3<br>ACMP | <ul> <li>Analog Comparator Interrupt Pending — This read-only bit indicates there is a pending interrupt from the ACMP module. Clearing the ACF flag of the ACMPSC register clears this bit. Reset also clears this bit.</li> <li>0 There is no pending ACMP interrupt; i.e., ACF flag and/or ACIE bit is cleared.</li> <li>1 There is a pending a ACMP interrupt; i.e., ACF flag and ACIE bit are set.</li> </ul>                        |

| 2<br>MTIM | <ul> <li>Modulo Timer Interrupt Pending — This read-only bit indicates there is a pending interrupt from the MTIM module. Clearing the TOF flag of the MTIMSC register clears this bit. Reset also clears this bit.</li> <li>0 There is no pending MTIM interrupt; i.e., TOF flag and/or TOIE bit is cleared.</li> <li>1 There is a pending MTIM interrupt; i.e., TOF flag and TOIE bit are set.</li> </ul>                               |

| 1<br>RTI  | <ul> <li>Real-Time Interrupt Pending — This read-only bit indicates there is a pending interrupt from the RTI. Clearing the RTIF flag of the SRTISC register clears this bit. Reset also clears this bit.</li> <li>0 There is no pending RTI interrupt; i.e., RTIF flag and/or RTIE bit is cleared.</li> <li>1 There is a pending RTI interrupt; i.e., RTIF flag and RTIE bit are set.</li> </ul>                                         |

| 0<br>LVD  | <ul> <li>Low-Voltage Detect Interrupt Pending — This read-only bit indicates there is a pending interrupt from the low voltage detect module. Clearing the LVDF flag of the SPMSC1 register clears this bit. Reset also clears this bit.</li> <li>0 There is no pending LVD interrupt; i.e., LVDF flag and/or LVDE bit is cleared.</li> <li>1 There is a pending LVD interrupt; i.e., LVDF flag, LVDIE, and LVDE bits are set.</li> </ul> |

#### Table 5-9. SIP1 Register Field Descriptions

#### **Chapter 6 Parallel Input/Output Control**

When a shared digital function is enabled for a pin, the output buffer is controlled by the shared function. However, the data direction register bit will continue to control the source for reads of the port data register.

When a shared analog function is enabled for a pin, both the input and output buffers are disabled. A value of 0 is read for any port data bit where the bit is an input (PTADDn = 0) and the input buffer is disabled. In general, whenever a pin is shared with both an alternative digital function and an analog function, the analog function has priority such that if both the digital and analog functions are enabled, the analog function controls the pin.

It is a good programming practice to write to the port data register before changing the direction of a port pin to become an output. This ensures that the pin will not be driven temporarily with an old data value that happened to be in the port data register.

Associated with the parallel I/O ports is a set of registers located in the high page register space that operate independently of the parallel I/O registers. These registers are used to control pullup/pulldown and slew rate for the pins. See Section 6.3, "Pin Control Registers" for more information.

### 6.1 Pin Behavior in Low-Power Modes

In wait and stop modes, all pin states are maintained because internal logic stays powered up. Upon recovery, all pin functions are the same as before entering stop.

### 6.2 Parallel I/O Registers

This section provides information about the registers associated with the parallel I/O ports. The parallel I/O registers are located within the \$001F memory boundary of the memory map, so that short and direct addressing mode instructions can be used.

Refer to tables in Chapter 4, "Memory," for the absolute address assignments for all parallel I/O. This section refers to registers and control bits only by their names. A Freescale Semiconductor-provided equate or header file normally is used to translate these names into the appropriate absolute addresses.

### 6.2.1 Port A Registers

Port A parallel I/O function is controlled by the data and data direction registers described in this section.

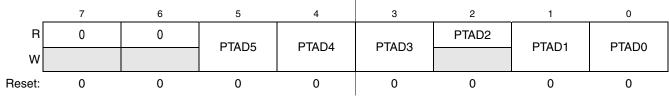

Figure 6-2. Port A Data Register (PTAD)

#### Chapter 8 Central Processor Unit (RS08CPUV1)

Other instructions may be executed between the test and the conditional branch as long as the only instructions used are those which do not disturb the CCR bits that affect the conditional branch. For instance, a test is performed in a subroutine or function and the conditional branch is not executed until the subroutine has returned to the main program. This is a form of parameter passing (that is, information is returned to the calling program in the condition code bits).

#### Z — Zero Flag

The Z bit is set to indicate the result of an operation was \$00.

Branch if equal (BEQ) and branch if not equal (BNE) are simple branches that branch based solely on the value in the Z bit. All load, store, move, arithmetic, logical, shift, and rotate instructions cause the Z bit to be updated.

#### C — Carry

After an addition operation, the C bit is set if the source operands were both greater than or equal to \$80 or if one of the operands was greater than or equal to \$80 and the result was less than \$80. This is equivalent to an unsigned overflow. A subtract or compare performs a subtraction of a memory operand from the contents of a CPU register so after a subtract operation, the C bit is set if the unsigned value of the memory operand was greater than the unsigned value of the CPU register. This is equivalent to an unsigned borrow or underflow.

Branch if carry clear (BCC) and branch if carry set (BCS) are branches that branch based solely on the value in the C bit. The C bit is also used by the unsigned branches BLO and BHS. Add, subtract, shift, and rotate instructions cause the C bit to be updated. The branch if bit set (BRSET) and branch if bit clear (BRCLR) instructions copy the tested bit into the C bit to facilitate efficient serial-to-parallel conversion algorithms. Set carry (SEC) and clear carry (CLC) allow the carry bit to be set or cleared directly. This is useful in combination with the shift and rotate instructions and for routines that pass status information back to a main program, from a subroutine, in the C bit.

The C bit is included in shift and rotate operations so those operations can easily be extended to multi-byte operands. The shift and rotate operations can be considered 9-bit shifts that include an 8-bit operand or CPU register and the carry bit of the CCR. After a logical shift, C holds the bit that was shifted out of the 8-bit operand. If a rotate instruction is used next, this C bit is shifted into the operand for the rotate, and the bit that gets shifted out the other end of the operand replaces the value in C so it can be used in subsequent rotate instructions.

### 8.2.5 Indexed Data Register (D[X])

This 8-bit indexed data register allows the user to access the data in the direct page address space indexed by X. This register resides at the memory mapped location \$000E. For details on the D[X] register, please refer to Section 8.3.8, "Indexed Addressing Mode (IX, Implemented by Pseudo Instructions)."

### 8.2.6 Index Register (X)

This 8-bit index register allows the user to index or address any location in the direct page address space. This register resides at the memory mapped location \$000F. For details on the X register, please refer to Section 8.3.8, "Indexed Addressing Mode (IX, Implemented by Pseudo Instructions)."

Internal Clock Source (RS08ICSV1)

### 9.1.1 Features

Key features of the ICS module are:

- Frequency-locked loop (FLL) is trimmable for accuracy

- 0.2% resolution using internal 32 kHz reference

- 2% deviation over voltage and temperature using internal 32 kHz reference

- DCO output is 512 times internal reference frequency

- Internal reference clock has 9 trim bits available

- Internal reference clock can be selected as the clock source for the MCU

- Whichever clock is selected as the source can be divided down

- 2 bit select for clock divider is provided (allowable dividers are: 1, 2, 4, and 8)

- FLL engaged internal mode is automatically selected out of reset

### 9.1.2 Modes of Operation

There are four modes of operation for the ICS: FEI, FBI, FBILP, and stop.

### 9.1.2.1 FLL Engaged Internal (FEI)

In FLL engaged internal mode, which is the default mode, the ICS supplies a clock derived from the FLL which is controlled by the internal reference clock.

### 9.1.2.2 FLL Bypassed Internal (FBI)

In FLL bypassed internal mode, the FLL is enabled and controlled by the internal reference clock, but is bypassed. The ICS supplies a clock derived from the internal reference clock.

### 9.1.2.3 FLL Bypassed Internal Low Power (FBILP)

In FLL bypassed internal low power mode, the FLL is disabled and bypassed, and the ICS supplies a clock derived from the internal reference clock.

### 9.1.2.4 Stop (STOP)

In stop mode, the FLL is disabled and the internal reference clocks can be selected to be enabled or disabled. The ICS does not provide an MCU clock source.

### 9.1.3 Block Diagram

Figure 9-2 shows the ICS block diagram.

Modulo Timer (RS08MTIMV1)

| Field        | Description                                                                                                                                                            |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7:0<br>COUNT | <b>MTIM Count</b> — These eight read-only bits contain the current value of the 8-bit counter. Writes have no effect to this register. Reset clears the count to \$00. |

#### Table 11-5. MTIMCNT Field Description

### 11.3.4 MTIM Modulo Register (MTIMMOD)

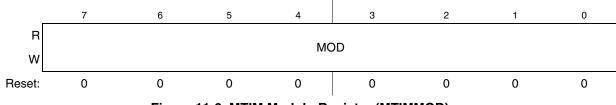

Figure 11-6. MTIM Modulo Register (MTIMMOD)

#### Table 11-6. MTIMMOD Descriptions

| Field | Description                                                                                                                                                                                                                                                   |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MOD   | <b>MTIM Modulo</b> — These eight read/write bits contain the modulo value used to reset the count and set TOF. A value of \$00 puts the MTIM in free-running mode. Writing to MTIMMOD resets the COUNT to \$00 and clears TOF. Reset sets the modulo to \$00. |

#### **Chapter 12 Development Support**

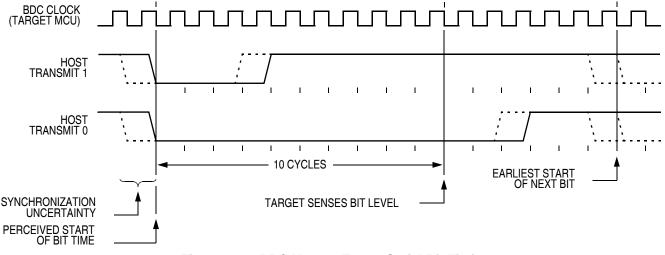

The BDC serial communication protocol requires the host to know the target BDC clock speed. Commands and data are sent most significant bit first (MSB-first) at 16 BDC clock cycles per bit. The interface times out if 512 BDC clock cycles occur between falling edges from the host. Any BDC command that was in progress when this timeout occurs is aborted without affecting the memory or operating mode of the target MCU system.

Figure 12-3 shows an external host transmitting a logic 1 or 0 to the BKGD pin of a target MCU. The host is asynchronous to the target so there is a 0-to-1 cycle delay from the host-generated falling edge to where the target perceives the beginning of the bit time. Ten target BDC clock cycles later, the target senses the bit level on the BKGD pin. Typically, the host actively drives the pseudo-open-drain BKGD pin during host-to-target transmissions to speed up rising edges. Because the target does not drive the BKGD pin during the host-to-target period, there is no need to treat the line as an open-drain signal during this period.

Figure 12-3. BDC Host-to-Target Serial Bit Timing

Figure 12-4 shows the host receiving a logic 1 from the target MCU. Because the host is asynchronous to the target, there is a 0-to-1 cycle delay from the host-generated falling edge on BKGD to the perceived start of the bit time in the target. The host holds the BKGD pin low long enough for the target to recognize it (at least two target BDC cycles). The host must release the low drive before the target drives a brief active-high speedup pulse seven cycles after the perceived start of the bit time. The host must sample the bit level approximately 10 cycles after it started the bit time.

Chapter 12 Development Support

# Appendix A Electrical Characteristics

### A.1 Introduction

This chapter contains electrical and timing specifications.

### A.2 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only, and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table A-1 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this chapter.

This device contains circuitry protecting against damage due to high static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit. Reliability of operation is enhanced if unused inputs are tied to an appropriate logic voltage level (for instance, either  $V_{SS}$  or  $V_{DD}$ ) or the programmable pull-up resistor associated with the pin is enabled.

| Rating                                                                                          | Symbol           | Value                         | Unit |

|-------------------------------------------------------------------------------------------------|------------------|-------------------------------|------|

| Supply voltage                                                                                  | V <sub>DD</sub>  | -0.3 to +5.8                  | V    |

| Maximum current into V <sub>DD</sub>                                                            | I <sub>DD</sub>  | 120                           | mA   |

| Digital input voltage                                                                           | V <sub>In</sub>  | –0.3 to V <sub>DD</sub> + 0.3 | V    |

| Instantaneous maximum current<br>Single pin limit (applies to all port pins) <sup>1, 2, 3</sup> | ۱ <sub>D</sub>   | ± 25                          | mA   |

| Storage temperature range                                                                       | T <sub>stg</sub> | –55 to 150                    | °C   |

#### Table A-1. Absolute Maximum Ratings

<sup>1</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive (V<sub>DD</sub>) and negative (V<sub>SS</sub>) clamp voltages, then use the larger of the two resistance values.

<sup>2</sup> All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> except the RESET/V<sub>PP</sub> pin which is internally clamped to V<sub>SS</sub> only.

<sup>3</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if the clock rate is very low which would reduce overall power consumption.

**Appendix A Electrical Characteristics**

Eqn. A-2

$$\mathbf{P}_{\mathbf{D}} = \mathbf{K} \div (\mathbf{T}_{\mathbf{J}} + \mathbf{273}^{\circ}\mathbf{C})$$

Solving Equation A-1 and Equation A-2 for K gives:

$$K = P_D \times (T_A + 273^{\circ}C) + \theta_{JA} \times (P_D)^2$$

Eqn. A-3

where K is a constant pertaining to the particular part. K can be determined from Equation A-3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  can be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

### A.4 Electrostatic Discharge (ESD) Protection Characteristics

Although damage from static discharge is much less common on these devices than on early CMOS circuits, normal handling precautions should be used to avoid exposure to static discharge. Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage. All ESD testing is in conformity with CDF-AEC-Q00 Stress Test Qualification for Automotive Grade Integrated Circuits. (http://www.aecouncil.com/) A device is considered to have failed if, after exposure to ESD pulses, the device no longer meets the device specification requirements. Complete dc parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

| Parameter                                                        | Symbol             | Value | Unit |

|------------------------------------------------------------------|--------------------|-------|------|

| ESD Target for Machine Model (MM)<br>MM circuit description      | V <sub>THMM</sub>  | 200   | V    |

| ESD Target for Human Body Model (HBM)<br>HBM circuit description | V <sub>THHBM</sub> | 2000  | V    |

#### **Table A-3. ESD Protection Characteristics**

### A.5 DC Characteristics

This section includes information about power supply requirements, I/O pin characteristics, and power supply current in various operating modes.

Table A-4. DC Characteristics (Temperature Range = -40 to 85°C Ambient)

| Parameter                                                                                | Symbol           | Min                  | Typical      | Max          | Unit |

|------------------------------------------------------------------------------------------|------------------|----------------------|--------------|--------------|------|

| Supply voltage (run, wait and stop modes.)<br>0 < f <sub>Bus</sub> <10MHz                | V <sub>DD</sub>  | 1.8                  | _            | 5.5          | V    |

| Minimum RAM retention supply voltage applied to $\mathrm{V}_{\mathrm{DD}}$               | V <sub>RAM</sub> | 0.8 <sup>1</sup>     | —            | —            | V    |

| Low-voltage Detection threshold<br>(V <sub>DD</sub> falling)<br>(V <sub>DD</sub> rising) | V <sub>LVD</sub> | 1.80<br>1.88         | 1.86<br>1.94 | 1.95<br>2.03 | v    |

| Power on RESET (POR) voltage                                                             | V <sub>POR</sub> | 0.9                  | 1.4          | 1.7          | V    |

| Input high voltage (V <sub>DD</sub> > 2.3V) (all digital inputs)                         | V <sub>IH</sub>  | $0.70 \times V_{DD}$ | _            | —            | V    |

| Input high voltage (1.8 V $\leq$ V_{DD} $\leq$ 2.3 V) (all digital inputs)               | V <sub>IH</sub>  | $0.85 \times V_{DD}$ | _            | —            | V    |

| Parameter                                                                                                                                                                                                                                                                   | Symbol              | Min                   | Typical | Мах                       | Unit     |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|-----------------------|---------|---------------------------|----------|

| Input low voltage ( $V_{DD}$ > 2.3 V) (all digital inputs)                                                                                                                                                                                                                  | V <sub>IL</sub>     | _                     | _       | $0.30 \times V_{DD}$      | V        |

| Input low voltage (1.8 V $\leq$ V <sub>DD</sub> $\leq$ 2.3 V) (all digital inputs)                                                                                                                                                                                          | V <sub>IL</sub>     | _                     | _       | 0.30 ×<br>V <sub>DD</sub> | V        |

| Input hysteresis (all digital inputs)                                                                                                                                                                                                                                       | V <sub>hys</sub>    | $0.06 \times V_{DD}$  | —       | —                         | V        |

| Input leakage current (per pin)<br>$V_{In} = V_{DD}$ or $V_{SS}$ , all input only pins                                                                                                                                                                                      | ll <sub>In</sub> l  | —                     | 0.025   | 1.0                       | μΑ       |

| High impedance (off-state) leakage current (per pin)<br>$V_{In} = V_{DD}$ or $V_{SS}$ , all input/output                                                                                                                                                                    | ll <sub>oz</sub> l  | _                     | 0.025   | 1.0                       | μA       |

| Internal pullup/pulldown resistors <sup>2</sup> (all port pins)                                                                                                                                                                                                             | R <sub>PU</sub>     | 20                    | 45      | 65                        | kΩ       |

|                                                                                                                                                                                                                                                                             | V <sub>OH</sub>     | V <sub>DD</sub> – 0.8 | _       |                           | v        |

| Maximum total I <sub>OH</sub> for all port pins                                                                                                                                                                                                                             | II <sub>OHT</sub> I |                       | —       | 40                        | mA       |

| $\begin{array}{l} \text{Output low voltage (port A)} \\ \text{I}_{OL} = 5 \text{ mA } (\text{V}_{DD} \geq 4.5 \text{ V}) \\ \text{I}_{OL} = 3 \text{ mA } (\text{V}_{DD} \geq 3 \text{ V}) \\ \text{I}_{OL} = 2 \text{ mA } (\text{V}_{DD} \geq 1.8 \text{ V}) \end{array}$ | V <sub>OL</sub>     | _                     | _       | 0.8<br>0.8<br>0.8         | v        |

| Maximum total I <sub>OL</sub> for all port pins                                                                                                                                                                                                                             | I <sub>OLT</sub>    | —                     | —       | 40                        | mA       |

| dc injection current <sup>3, 4, 5 6</sup><br>V <sub>In</sub> < V <sub>SS</sub> , V <sub>In</sub> > V <sub>DD</sub><br>Single pin limit<br>Total MCU limit, includes sum of all stressed pins                                                                                | lI <sub>IC</sub> I  | _                     | _       | 0.2<br>0.8                | mA<br>mA |

| Input capacitance (all non-supply pins)                                                                                                                                                                                                                                     | C <sub>In</sub>     | —                     | —       | 7                         | pF       |

#### Table A-4. DC Characteristics (continued) (Temperature Range = -40 to 85°C Ambient)

<sup>1</sup> This parameter is characterized and not tested on each device.

<sup>2</sup> Measurement condition for pull resistors:  $V_{In} = V_{SS}$  for pullup and  $V_{In} = V_{DD}$  for pulldown.

<sup>3</sup> All functional non-supply pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> except the  $\overline{\text{RESET}}/V_{PP}$  which is internally clamped to V<sub>SS</sub> only.

<sup>4</sup> Input must be current limited to the value specified. To determine the value of the required current-limiting resistor, calculate resistance values for positive and negative clamp voltages, then use the larger of the two values.

<sup>5</sup> Power supply must maintain regulation within operating  $V_{DD}$  range during instantaneous and operating maximum current conditions. If positive injection current ( $V_{In} > V_{DD}$ ) is greater than  $I_{DD}$ , the injection current may flow out of  $V_{DD}$  and could result in external power supply going out of regulation. Ensure external  $V_{DD}$  load will shunt current greater than maximum injection current. This will be the greatest risk when the MCU is not consuming power. Examples are: if no system clock is present, or if clock rate is very low which would reduce overall power consumption.

<sup>6</sup> This parameter is characterized and not tested on each device.

#### Appendix A Electrical Characteristics

$^1\,V_{\text{DD}}$  must be at a valid operating voltage before voltage is applied or removed from the  $V_{\text{PP}}$  pin.

Figure A-5. Flash Mass Erase Timing

## Appendix B Ordering Information and Mechanical Drawings

### B.1 Ordering Information

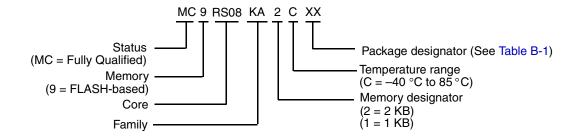

This section contains ordering numbers for MC9RS08KA2 Series devices. See below for an example of the device numbering system.

| Device Number            | Men          | nory     | Package   |            |              |

|--------------------------|--------------|----------|-----------|------------|--------------|

| Device Nulliber          | FLASH        | RAM      | Туре      | Designator | Document No. |

| MCODCOOKAO               | 2 KB<br>1 KB | 63 bytes | 6 DFN     | DB         | 98ARL10602D  |

| MC9RS08KA2<br>MC9RS08KA1 |              |          | 8 PDIP    | PC         | 98ASB42420B  |

|                          | T TE         |          | 8 NB-SOIC | SC         | 98ASB42564B  |

#### Table B-1. Device Numbering System

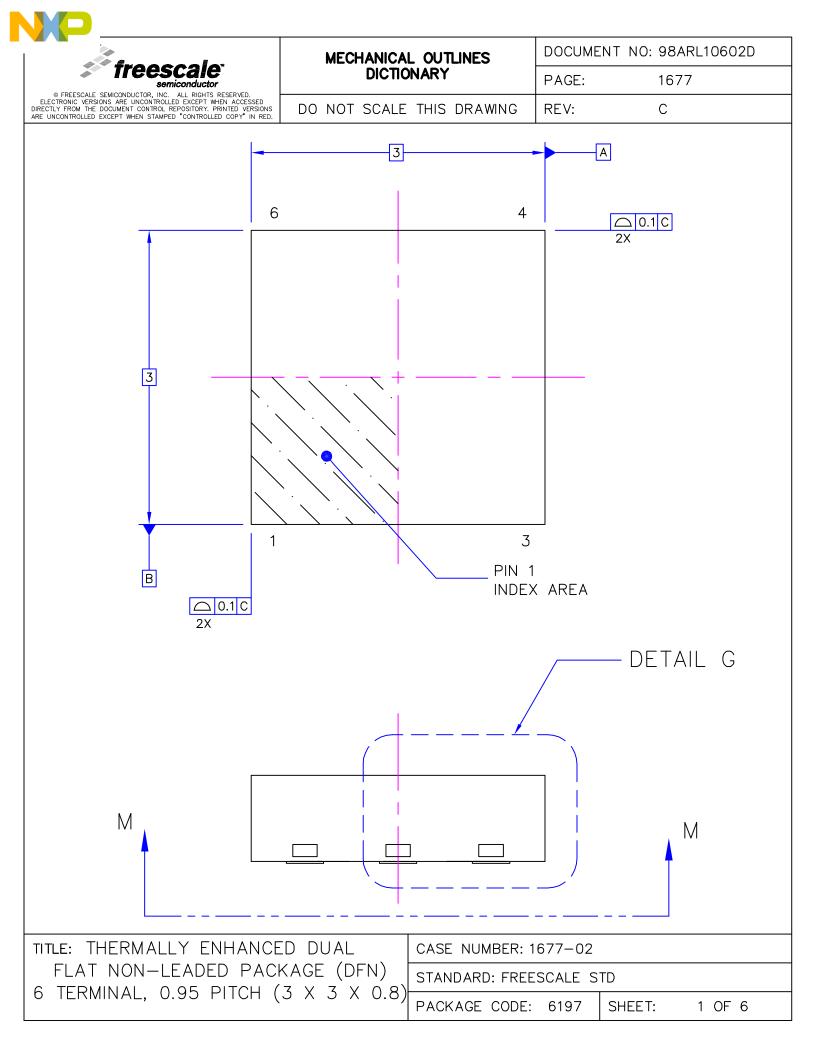

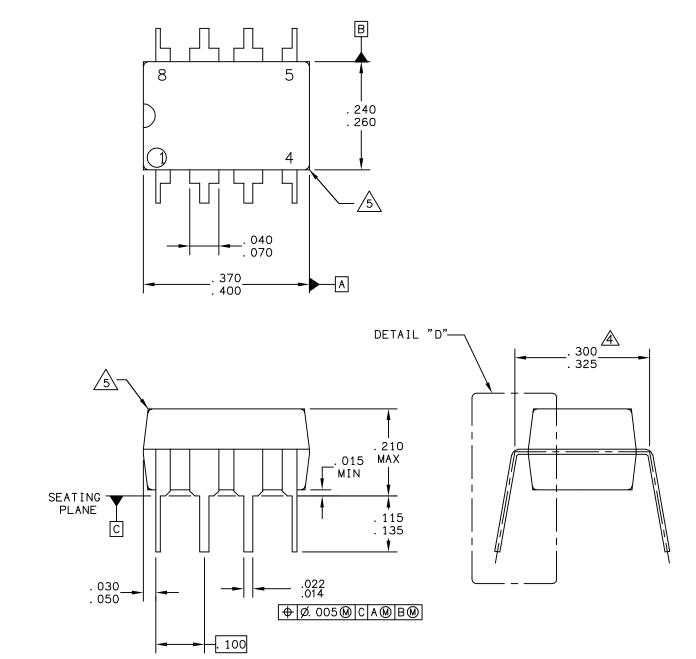

### **B.2** Mechanical Drawings

This following pages contain mechanical specifications for MC9RS08KA2 Series package options:

- 6-pin DFN (dual flat no-lead)

- 8-pin PDIP (plastic dual in-line pin)

- 8-pin NB-SOIC (narrow body small outline integrated circuit)

| © FREESCALE SEMICONDUCTOR, INC.<br>All RIGHTS RESERVED. | MECHANICAL OUTLINE | PRINT VERSION NO         | DT TO SCALE |  |

|---------------------------------------------------------|--------------------|--------------------------|-------------|--|

| TITLE:                                                  | DOCUMENT N         | DOCUMENT NO: 98ASB42420B |             |  |

| 8 LD PDIP                                               | CASE NUMBE         | CASE NUMBER: 626–06 19   |             |  |

|                                                         | STANDARD: N        | ON-JEDEC                 |             |  |

Appendix B Ordering Information and Mechanical Drawings