Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064ht-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             |     |                   | A3                        | 4                         |

|-------------------|-------------------------------------------------------|-----|-------------------|---------------------------|---------------------------|

|                   |                                                       | B13 | B29               |                           | Conductive<br>Thermal Pad |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1  | B56               | B41                       | A51                       |

|                   | A1                                                    |     |                   |                           |                           |

|                   | Polarity Indicator                                    |     | A68               |                           |                           |

| Package<br>Bump # | Full Pin Name                                         |     | Package<br>Bump # | F                         | ull Pin Name              |

| B8                | Vss                                                   |     | B33               | TDO/RA5                   |                           |

| B9                | TMS/RA0                                               |     | B34               | OSC1/CLKI/RC              | 212                       |

| B10               | AERXD1/INT2/RE9                                       |     | B35               | No Connect (N             | C)                        |

| B11               | AN4/C1IN-/CN6/RB4                                     |     | B36               | AETXCLK/SCL               | .1/INT3/RA14              |

| B12               | Vss                                                   |     | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |

| B13               | AN2/C2IN-/CN4/RB2                                     |     | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |

| B14               | PGED1/AN0/CN2/RB0                                     |     | B39               | SDO1/OC1/INT              | [0/RD0                    |

| B15               | No Connect (NC)                                       |     | B40               | SOSCO/T1CK/               | CN0/RC14                  |

| B16               | PGED2/AN7/RB7                                         |     | B41               | Vss                       |                           |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |     | B42               | OC3/RD2                   |                           |

| B18               | AVss                                                  |     | B43               | ETXD2/IC5/PN              | ID12/RD12                 |

| B19               | AN9/C2OUT/RB9                                         |     | B44               | OC5/PMWR/CI               | N13/RD4                   |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |     | B45               | ETXEN/PMD14               | 4/CN15/RD6                |

| B21               | Vdd                                                   |     | B46               | Vss                       |                           |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |     | B47               | No Connect (N             | C)                        |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |     | B48               | VCAP                      |                           |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |     | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |

| B25               | Vss                                                   |     | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |     | B51               | TRCLK/RA6                 |                           |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |     | B52               | PMD0/RE0                  |                           |

| B28               | No Connect (NC)                                       |     | B53               | Vdd                       |                           |

| B29               | SCL3/SDO3/U1TX/RF8                                    |     | B54               | TRD2/RG14                 |                           |

| B30               | VUSB3V3                                               |     | B55               | TRD0/RG13                 |                           |

| B31               | D+/RG2                                                |     | B56               | PMD3/RE3                  |                           |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

| TABLE 1-1 | : PINOU            | T I/O DES       |                     | NS (CONT        | )    |        |                                                                                                                |  |  |  |

|-----------|--------------------|-----------------|---------------------|-----------------|------|--------|----------------------------------------------------------------------------------------------------------------|--|--|--|

|           |                    | Pin Nun         | nber <sup>(1)</sup> |                 | Pin  | Buffer |                                                                                                                |  |  |  |

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре | Туре   | Description                                                                                                    |  |  |  |

| PMD0      | 60                 | 93              | A4                  | B52             | I/O  | TTL/ST | Parallel Master Port data                                                                                      |  |  |  |

| PMD1      | 61                 | 94              | B4                  | A64             | I/O  | TTL/ST | (Demultiplexed Master mode) or                                                                                 |  |  |  |

| PMD2      | 62                 | 98              | B3                  | A66             | I/O  | TTL/ST | address/data (Multiplexed Master modes)                                                                        |  |  |  |

| PMD3      | 63                 | 99              | A2                  | B56             | I/O  | TTL/ST | nodes)                                                                                                         |  |  |  |

| PMD4      | 64                 | 100             | A1                  | A67             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD5      | 1                  | 3               | D3                  | B2              | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD6      | 2                  | 4               | C1                  | A4              | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD7      | 3                  | 5               | D2                  | B3              | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD8      | —                  | 90              | A5                  | A61             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD9      | —                  | 89              | E6                  | B50             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD10     | —                  | 88              | A6                  | A60             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD11     | _                  | 87              | B6                  | B49             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD12     | _                  | 79              | A9                  | B43             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD13     | _                  | 80              | D8                  | A54             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD14     | _                  | 83              | D7                  | B45             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMD15     | _                  | 84              | C7                  | A56             | I/O  | TTL/ST |                                                                                                                |  |  |  |

| PMALL     | 30                 | 44              | L8                  | A29             | ο    | _      | Parallel Master Port address latch<br>enable low byte (Multiplexed Master<br>modes)                            |  |  |  |

| PMALH     | 29                 | 43              | К7                  | B24             | 0    | _      | Parallel Master Port address latch<br>enable high byte (Multiplexed Master<br>modes)                           |  |  |  |

| PMRD      | 53                 | 82              | B8                  | A55             | 0    | _      | Parallel Master Port read strobe                                                                               |  |  |  |

| PMWR      | 52                 | 81              | C8                  | B44             | 0    | _      | Parallel Master Port write strobe                                                                              |  |  |  |

| VBUS      | 34                 | 54              | H8                  | A37             | I    | Analog | USB bus power monitor                                                                                          |  |  |  |

| VUSB3V3   | 35                 | 55              | H9                  | B30             | Р    | _      | USB internal transceiver supply. If the<br>USB module is <i>not</i> used, this pin mus<br>be connected to VDD. |  |  |  |

| VBUSON    | 11                 | 20              | H1                  | A12             | 0    | _      | USB Host and OTG bus power contro<br>output                                                                    |  |  |  |

| D+        | 37                 | 57              | H10                 | B31             | I/O  | Analog | USB D+                                                                                                         |  |  |  |

| D-        | 36                 | 56              | J11                 | A38             | I/O  | Analog | USB D-                                                                                                         |  |  |  |

| USBID     | 33                 | 51              | K10                 | A35             | Ι    | ST     | USB OTG ID detect                                                                                              |  |  |  |

| C1RX      | 58                 | 87              | B6                  | B49             | I    | ST     | CAN1 bus receive pin                                                                                           |  |  |  |

| C1TX      | 59                 | 88              | A6                  | A60             | 0    |        | CAN1 bus transmit pin                                                                                          |  |  |  |

| AC1RX     | 32                 | 40              | K6                  | A27             | I    | ST     | Alternate CAN1 bus receive pin                                                                                 |  |  |  |

| AC1TX     | 31                 | 39              | L6                  | B22             | 0    | —      | Alternate CAN1 bus transmit pin                                                                                |  |  |  |

| C2RX      | 29                 | 90              | A5                  | A61             | I    | ST     | CAN2 bus receive pin                                                                                           |  |  |  |

|           | 21                 | 89              | E6                  | B50             | 0    | —      | CAN2 bus transmit pin                                                                                          |  |  |  |

| C2TX      |                    |                 | 1                   | 1               | 1    |        | Alternate CAN2 bus receive pin                                                                                 |  |  |  |

#### PINOLIT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 **SOSCEN:** Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

#### bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit Bit<br>28/20/12/4 27/19/11/3 |         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|----------------------------------|---------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                            | R/W-0   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                                  |         |                   |                  |                  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0                            | R/W-0   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23.10        | DCRCDATA<23:16>   |                   |                   |                                  |         |                   |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                            | R/W-0   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                                  |         |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                            | R/W-0   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCDA                           | ΓA<7:0> |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31.24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

#### 1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0 R/W-0 R     |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | CHCSIZ            | /<7:0>            |                   |                  |                  |  |  |  |  |

#### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

### REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0 R-0          | R-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-16 Unimplemented: Read as '0'

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

### TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                        |                                 |           |       |       |       |       |       |       |      |      | Bits |      |      |          |        |        |         |        |            |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 53A0                       | U1EP10                          | 31:16     | _     | _     | _     | _     | _     | —     | _    | _    |      | _    | —    | —        | -      |        | _       | _      | 0000       |

| 55A0                       | U1EP10                          | 15:0      | —     | —     | _     | _     | _     | —     | _    | _    | —    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                       | U1EP11                          | 31:16     | -     | _     | _     |       |       | _     |      |      |      | _    | _    | —        |        |        | _       |        | 0000       |

| 5560                       |                                 | 15:0      | -     | _     | _     |       |       | _     |      |      |      | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                       | U1EP12                          | 31:16     | Ι     | _     |       | -     |       | _     |      |      | _    | —    | —    | _        | -      | -      | _       | -      | 0000       |

| 5300                       | UTEPTZ                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | —    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5200                       |                                 | 31:16     |       | _     | _     | —     | _     | -     | —    | —    | _    | -    | —    | —        | —      | _      | _       | _      | 0000       |

| 53D0                       | U1EP13                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | —    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

|                            |                                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                       | U1EP14                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                       |                                 | 31:16     | _     | _     | _     |       | -     | _     | _    | _    | -    | _    | —    | _        |        |        | —       | -      | 0000       |

| 53F0                       | U1EP15                          | 15:0      | _     | —     | —     | -     |       | _     | -    | —    |      | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated SET and INV registers. 2:

3: This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined. 4:

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 |                   |                   | _                 |                   |                  | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | SIDL              | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 |                   |                   | _                 |                   | _                | _                |

### REGISTER 12-1: CNCON: CHANGE NOTICE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle mode does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

NOTES:

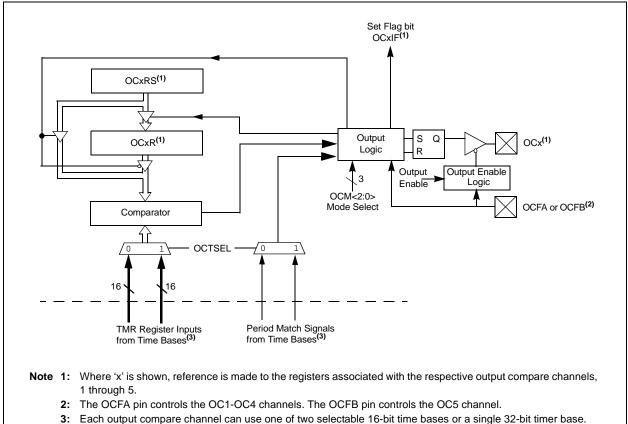

## 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16.** "Output Compare" (DS60001111) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Output Compare module is used to generate a single pulse or a series of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of the Output Compare module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Programmable selection of 16-bit or 32-bit time bases

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 |         |     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|---------|-----|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0     | R-0 | R-0              | R-0              |  |

| 31:24        | —                 | —                 | —                 | RXBUFELM<4:0>     |         |     |                  |                  |  |

| 00.40        | U-0               | U-0               | U-0               | R-0               | R-0     | R-0 | R-0              | R-0              |  |

| 23:16        | —                 | —                 | —                 | TXBUFELM<4:0>     |         |     |                  |                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R-0     | U-0 | U-0              | R-0              |  |

| 15:8         | —                 | —                 | —                 | _                 | SPIBUSY | _   | _                | SPITUR           |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1     | U-0 | R-0              | R-0              |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            |                   | SPITBE  |     | SPITBF           | SPIRBF           |  |

#### **REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER**

| Legend:           | C = Clearable bit | C = Clearable bit HS = Set in hardware              |                    |

|-------------------|-------------------|-----------------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | W = Writable bit U = Unimplemented bit, read as the |                    |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared                                | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (only valid when ENHBUF = 1)

- bit 15-12 Unimplemented: Read as '0'

- bit 11 SPIBUSY: SPI Activity Status bit 1 = SPI peripheral is currently busy with some transactions 0 = SPI peripheral is currently idle

- Unimplemented: Read as '0'

- bit 10-9

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling/re-enabling the module.

- bit 7 **SRMT:** Shift Register Empty bit (only valid when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

- This bit is set in hardware; can only be cleared (= 0) in software.

- bit 5 **SPIRBE:** RX FIFO Empty bit (only valid when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR) 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

- bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB is empty

- 0 = Transmit buffer, SPIxTXB is not empty

- Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR.

- Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

- bit 2 Unimplemented: Read as '0'

### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- $0 = \text{Read Strobe active-low } (\overline{\text{PMRD}})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|

| 04.04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 31:24            |                   | HR10-             | <3:0>             |                   |                                    | HR01              | <3:0>            |                  |

| 00.40            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 23:16            |                   | MIN10             | <3:0>             | MIN01<3:0>        |                                    |                   |                  |                  |

| 45-0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |

| 15:8             |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                         |                   |                  |                  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | U-0                                | U-0               | U-0              | U-0              |

| 7:0              | —                 | —                 | —                 | —                 | —                                  | —                 | —                | —                |

|                  |                   |                   |                   |                   |                                    |                   |                  |                  |

| Legend:          |                   |                   |                   |                   |                                    |                   |                  |                  |

| R = Readable bit |                   |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |

|                  |                   |                   |                   |                   |                                    |                   |                  |                  |

#### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

| IX – IXeauable bit            |                            |                                | it, read as 0      |

|-------------------------------|----------------------------|--------------------------------|--------------------|

| -n = Value at POR             | '1' = Bit is set           | '0' = Bit is cleared           | x = Bit is unknown |

|                               |                            |                                |                    |

| bit 31-28 HR10<3:0>: Binary-0 | Coded Decimal Value of Hou | rs bits, 10 digits; contains a | value from 0 to 2  |

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits, contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9

bit 17-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

### REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| r         |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 25-32: EMAC1MCMD: ETHERNET CONTROLLER MAC MII MANAGEMENT COMMAND REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 |                   | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   | _                 | _                 | SCAN             | READ             |

#### Legend:

| 5                 |                           |                      |                                    |  |  |  |

|-------------------|---------------------------|----------------------|------------------------------------|--|--|--|

| R = Readable bit  | able bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |

#### bit 31-2 Unimplemented: Read as '0'

- bit 1 SCAN: MII Management Scan Mode bit

- 1 = The MII Management module will perform read cycles continuously (for example, useful for monitoring the Link Fail)

- 0 = Normal Operation

#### bit 0 READ: MII Management Read Command bit

- 1 = The MII Management module will perform a single read cycle. The read data is returned in the EMAC1MRDD register

- 0 = The MII Management module will perform a write cycle. The write data is taken from the EMAC1MWTD register

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## REGISTER 25-36: EMAC1MIND: ETHERNET CONTROLLER MAC MII MANAGEMENT INDICATORS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   | —                 | _                 | —                 | —                 | -                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | —                 |                   | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY         |

### Legend:

| 5                 |                  |                          |                    |   |

|-------------------|------------------|--------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown | 1 |

#### bit 31-4 Unimplemented: Read as '0'

bit 3 LINKFAIL: Link Fail bit

When '1' is returned - indicates link fail has occurred. This bit reflects the value last read from the PHY status register.

bit 2 NOTVALID: MII Management Read Data Not Valid bit When '1' is returned - indicates an MII management read cycle has not completed and the Read Data is not yet valid.

## bit 1 SCAN: MII Management Scanning bit When '1' is returned - indicates a scan operation (continuous MII Management Read cycles) is in progress.

#### bit 0 MIIMBUSY: MII Management Busy bit

When '1' is returned - indicates MII Management module is currently performing an MII Management Read or Write cycle.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 31.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

| DC CHA                               | DC CHARACTERISTICS |                                       |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |            |                                               |  |  |

|--------------------------------------|--------------------|---------------------------------------|--------|------------------------------------------------------|------|------------|-----------------------------------------------|--|--|

| Param.<br>No. Symbol Characteristics |                    |                                       | Min.   | Typ. <sup>(1)</sup>                                  | Max. | Units      | Conditions                                    |  |  |

| D130                                 | Ер                 | Cell Endurance                        | 1000   | _                                                    | _    | E/W        | _                                             |  |  |

| D130a                                | Ер                 | Cell Endurance                        | 20,000 |                                                      |      | E/W        | See Note 5                                    |  |  |

| D131                                 | Vpr                | VDD for Read                          | 2.3    | —                                                    | 3.6  | V          | —                                             |  |  |

| D132                                 | Vpew               | VDD for Erase or Write                | 3.0    | —                                                    | 3.6  | V          | —                                             |  |  |

| D132a                                | Vpew               | VDD for Erase or Write                | 2.3    | _                                                    | 3.6  | V          | See Note 5                                    |  |  |

| D134                                 | Tretd              | Characteristic Retention              | 20     | _                                                    | —    | Year       | Provided no other specifications are violated |  |  |

| D135                                 | IDDP               | Supply Current during<br>Programming  | —      | 10                                                   | _    | mA         | _                                             |  |  |

| D138                                 | Tww                | Word Write Cycle Time <sup>(4)</sup>  | —      | 411                                                  | _    | FRC Cycles |                                               |  |  |

| D136                                 | Trw                | Row Write Cycle Time <sup>(2,4)</sup> | _      | 26067                                                | _    | FRC Cycles |                                               |  |  |

| D137                                 | TPE                | Page Erase Cycle Time <sup>(4)</sup>  | _      | 201060                                               |      | FRC Cycles |                                               |  |  |

| D139                                 | TCE                | Chip Erase Cycle Time <sup>(4)</sup>  | _      | 804652                                               |      | FRC Cycles | —                                             |  |  |

## TABLE 32-11: DC CHARACTERISTICS: PROGRAM MEMORY<sup>(3)</sup>

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 4 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

- **3:** Refer to *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

- 4: This parameter depends on the FRC accuracy (see Table 32-19) and the FRC tuning values (see Register 8-2).

- **5:** This parameter only applies to PIC32MX534/564/664/764 devices.

#### TABLE 32-12: PROGRAM FLASH MEMORY WAIT STATE CHARACTERISTICS

| DC CHARACTERISTICS         |          |       |          |  |

|----------------------------|----------|-------|----------|--|

| Required Flash Wait States | SYSCLK   | Units | Comments |  |

| 0 Wait State               | 0 to 30  | MHz   | —        |  |

| 1 Wait State               | 31 to 60 |       |          |  |

| 2 Wait States              | 61 to 80 |       |          |  |

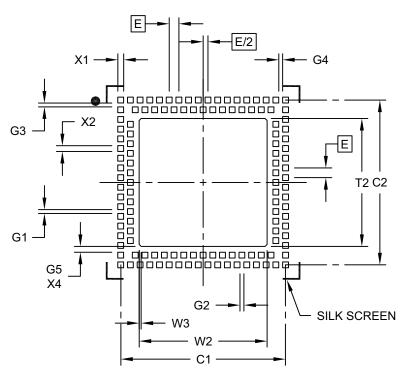

## 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

| Units                                |        | MILLIMETERS |      |      |

|--------------------------------------|--------|-------------|------|------|

| Dimensior                            | Limits | MIN         | NOM  | MAX  |

| Contact Pitch E                      |        | 0.50 BSC    |      |      |

| Pad Clearance                        | G1     | 0.20        |      |      |

| Pad Clearance                        | G2     | 0.20        |      |      |

| Pad Clearance                        | G3     | 0.20        |      |      |

| Pad Clearance                        | G4     | 0.20        |      |      |

| Contact to Center Pad Clearance (X4) | G5     | 0.30        |      |      |

| Optional Center Pad Width            | T2     |             |      | 6.60 |

| Optional Center Pad Length           | W2     |             |      | 6.60 |

| Optional Center Pad Chamfer (X4)     | W3     |             | 0.10 |      |

| Contact Pad Spacing                  | C1     |             | 8.50 |      |

| Contact Pad Spacing                  | C2     |             | 8.50 |      |

| Contact Pad Width (X124)             | X1     |             |      | 0.30 |

| Contact Pad Length (X124)            |        |             |      | 0.30 |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A

## APPENDIX B: REVISION HISTORY

## **Revision A (August 2009)**

This is the initial released version of this document.

## **Revision B (November 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits.

Other major changes are referenced by their respective chapter/section in Table B-1.

| Section Name                                                                  | Update Description                                                                                                                                                       |  |  |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| "High-Performance, USB, CAN and<br>Ethernet 32-bit Flash<br>Microcontrollers" | Added the following devices:<br>- PIC32MX575F256L<br>- PIC32MX695F512L                                                                                                   |  |  |

|                                                                               | <ul> <li>PIC32MX695F512H</li> <li>The 100-pin TQFP pin diagrams have been updated to reflect the current pin name locations (see the "Pin Diagrams" section).</li> </ul> |  |  |

|                                                                               | Added the 121-pin Ball Grid Array (XBGA) pin diagram.                                                                                                                    |  |  |

|                                                                               | Updated Table 1: "PIC32 USB and CAN – Features"                                                                                                                          |  |  |

|                                                                               | Added the following tables:                                                                                                                                              |  |  |

|                                                                               | <ul> <li>Table 4: "Pin Names: PIC32MX534F064L, PIC32MX564F064L,<br/>PIC32MX564F128L, PIC32MX575F256L and PIC32MX575F512L<br/>Devices"</li> </ul>                         |  |  |

|                                                                               | <ul> <li>Table 5: "Pin Names: PIC32MX664F064L, PIC32MX664F128L,<br/>PIC32MX675F256L, PIC32MX675F512L and PIC32MX695F512L<br/>Devices"</li> </ul>                         |  |  |

|                                                                               | <ul> <li>Table 6: "Pin Names: PIC32MX775F256L, PIC32MX775F512L and<br/>PIC32MX795F512L Devices"</li> </ul>                                                               |  |  |

|                                                                               | Updated the following pins as 5V tolerant:                                                                                                                               |  |  |

|                                                                               | - 64-pin QFN: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)                                                                                                                        |  |  |

|                                                                               | <ul> <li>64-pin TQFP: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)</li> <li>100-pin TQFP: Pin 56 (D-/RG3) and Pin 57 (D+/RG2)</li> </ul>                                          |  |  |

| 1.0 "Guidelines for Getting Started                                           | Removed the last sentence of 1.3.1 "Internal Regulator Mode".                                                                                                            |  |  |

| with 32-bit Microcontrollers"                                                 | Removed Section 2.3.2 "External Regulator Mode"                                                                                                                          |  |  |

### TABLE B-1: MAJOR SECTION UPDATES