Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

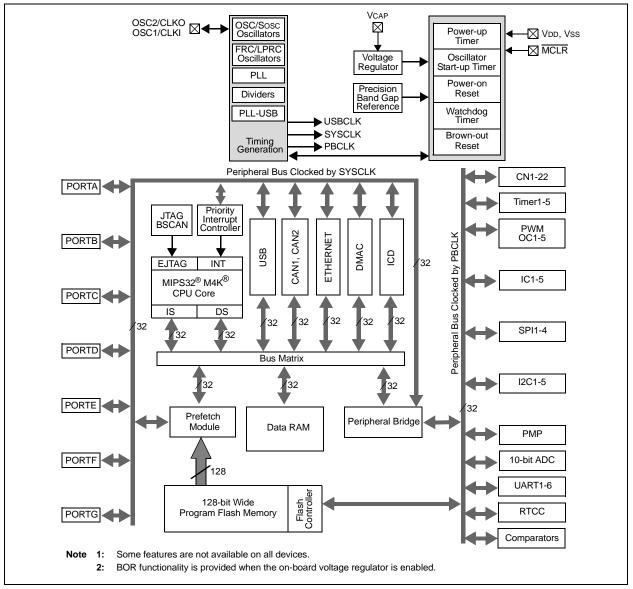

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

## 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Resets" (DS60001118) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

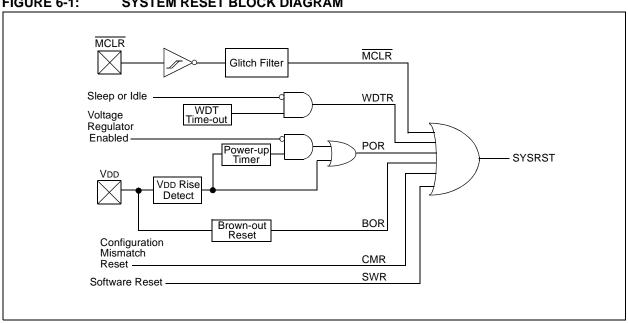

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- Power-on Reset (POR)

- Master Clear Reset pin (MCLR)

- Software Reset (SWR)

- Watchdog Timer Reset (WDTR)

- Brown-out Reset (BOR)

- Configuration Mismatch Reset (CMR)

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

## FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

## TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |             |       |                                | Bi                    | its         |            |             |             |             |             |             |                      |            |  |             |   |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|--------------------------------|-----------------------|-------------|------------|-------------|-------------|-------------|-------------|-------------|----------------------|------------|--|-------------|---|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9                           | 24/8                  | 23/7        | 22/6       | 21/5        | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                 | All Resets |  |             |   |        |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |       | INT4IP<2:0> |       | INT4IS                         | S<1:0>                | _           | —          | -           |             | OC4IP<2:0>  |             | OC4IS<1:0>  |                      | 0000       |  |             |   |        |        |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |       | IC4IP<2:0>  |       | IC4IS                          | <1:0>                 | _           | _          | _           |             | T4IP<2:0>   |             | T4IS-       | <1:0>                | 0000       |  |             |   |        |        |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |       | SPI1IP<2:0> |       | SPI1IS                         | 6<1:0>                | _           | _          | _           |             | OC5IP<2:0>  |             | OC5IS       | S<1:0>               | 0000       |  |             |   |        |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |       | IC5IP<2:0>  |       | IC5IS                          | <1:0>                 | -           |            | _           |             | T5IP<2:0>   |             | T5IS-       | <1:0>                | 0000       |  |             |   |        |        |      |

|                             |                                 | 31:16     | _     | _     | _     |       | AD1IP<2:0>  |       | AD1IS                          | S<1:0>                | _           | _          | _           |             | CNIP<2:0>   |             | CNIS        | <1:0>                | 0000       |  |             |   |        |        |      |

| 10F0                        | IPC6                            |           |       |       |       |       |             |       |                                |                       |             |            |             |             | U1IP<2:0>   |             | U1IS-       | <1:0>                |            |  |             |   |        |        |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0> |       | I2C1IS<1:0>                    |                       | I2C1IS<1:0> |            | I2C1IS<1:0> |             | I2C1IS<1    |             | —           | —                    | —          |  | SPI3IP<2:0> | • | SPI3IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |       |             |       |                                |                       |             |            |             | I2C3IP<2:0> |             | I2C3IS<1:0> |             |                      |            |  |             |   |        |        |      |

|                             |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS                           | U3IS<1:0>             |             |            |             |             |             |             |             |                      |            |  |             |   |        |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |       | SPI2IP<2:0> |       | SPI2IS                         | S<1:0>                | —           | —          | —           | CMP2IP<2:0> |             | CMP2IS<1:0> |             | 0000                 |            |  |             |   |        |        |      |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0> |       | 12C415                         | S<1:0>                |             |            |             |             |             |             |             |                      |            |  |             |   |        |        |      |

|                             |                                 | 15:0      | _     |       |       | (     | CMP1IP<2:0  | >     | CMP1I                          | S<1:0>                | _           | _          |             | PMPIP<2:0>  |             | PMPIS<1:0>  |             | 0000                 |            |  |             |   |        |        |      |

|                             |                                 | 31:16     | _     |       |       | F     | RTCCIP<2:0  | >     | RTCCIS<1:0>                    |                       | _           | _          |             | I           | FSCMIP<2:0  | >           | FSCMIS<1:0> |                      | 0000       |  |             |   |        |        |      |

| 1110                        | IPC8                            |           |       |       |       |       |             |       |                                |                       |             |            |             |             | U2IP<2:0>   |             | U2IS<1:0>   |                      |            |  |             |   |        |        |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |       | I2C2IP<2:0> |       | 12C215                         | 6<1:0>                | —           | —          | —           |             | SPI4IP<2:0> |             | SPI4IS      | S<1:0>               | 0000       |  |             |   |        |        |      |

|                             |                                 |           |       |       |       |       |             |       |                                |                       |             |            |             |             | I2C5IP<2:0> |             | 12C515      | S<1:0>               |            |  |             |   |        |        |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |       | DMA3IP<2:0  |       | DMA3I                          | S<1:0>                | _           |            |             |             | DMA2IP<2:0  |             | DMA2I       | S<1:0>               | 0000       |  |             |   |        |        |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |       | DMA1IP<2:0  |       | DMA1I                          |                       | _           |            |             |             | DMA0IP<2:0  |             | DMA0I       | S<1:0>               | 0000       |  |             |   |        |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI    | MA7IP<2:0>  | (2)   | DMA7IS                         | i<1:0> <sup>(2)</sup> | —           | _          | —           | D           | MA6IP<2:0>  | (2)         | DMA6IS      | <1:0> <sup>(2)</sup> | 0000       |  |             |   |        |        |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI    | MA5IP<2:0>  | (2)   | DMA5IS<1:0> <sup>(2)</sup>     |                       | _           | _          | —           | D           | MA4IP<2:0>  | (2)         | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |  |             |   |        |        |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _     | _           |       | _                              |                       |             |            | _           | _           | —           |             | —           |                      | 0000       |  |             |   |        |        |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |       | USBIP<2:0>  |       | USBIS                          | S<1:0>                | _           | _          | —           | FCEIP<2:0>  |             | FCEIS       | <1:0>       | 0000                 |            |  |             |   |        |        |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |       | U5IP<2:0>   |       | U5IS-                          | <1:0>                 | _           |            | -           | U6IP<2:0>   |             | U6IS<1:0>   |             | <1:0>                | 0000       |  |             |   |        |        |      |

| 1150                        | IFUIZ                           | 15:0      | _     | -     |       |       | U4IP<2:0>   |       | J4IP<2:0> U4IS<1:0> ETHIP<2:0> |                       |             | ETHIS<1:0> |             | 0000        |             |             |             |                      |            |  |             |   |        |        |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

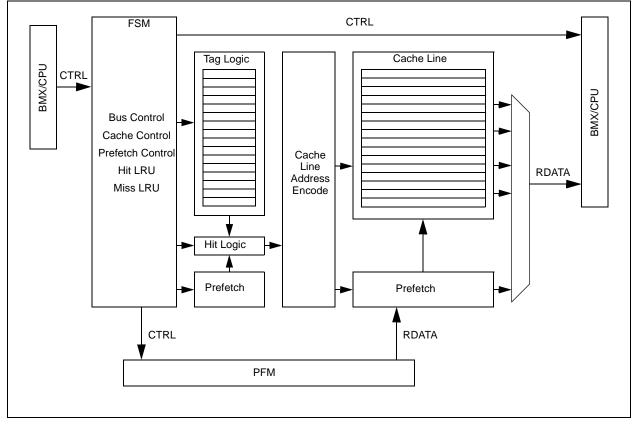

## 9.0 PREFETCH CACHE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS60001119) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

## 9.1 Features

- 16 fully-associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- Pseudo-LRU replacement policy

- All cache lines are software writable

- 16-byte parallel memory fetch

- Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

## FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

## 14.2 Control Registers

| TABLE 14-1: | TIMER2 THROUGH TIMER5 REGISTER MAP |

|-------------|------------------------------------|

|             |                                    |

|                             |                                 | ••            |                   |       |       |       |       |       |      |      |            |      |                |          |      |      |                         |      |            |

|-----------------------------|---------------------------------|---------------|-------------------|-------|-------|-------|-------|-------|------|------|------------|------|----------------|----------|------|------|-------------------------|------|------------|

| ess                         |                                 |               |                   |       |       |       |       |       |      | В    | ts         |      |                |          |      |      |                         |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15             | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7       | 22/6 | 21/5           | 20/4     | 19/3 | 18/2 | 17/1                    | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16         | —                 | _     | —     | —     |       | —     |      |      | —          | —    | —              |          | —    | -    | —                       |      | 0000       |

| 0800                        | 12001                           | 15:0          | ON                | _     | SIDL  | _     | -     | —     | 1    |      | TGATE      |      | TCKPS<2:0>     |          | T32  |      | TCS <sup>(2)</sup>      |      | 0000       |

| 0810                        | TMR2                            | 31:16         | _                 | —     | —     | —     | _     | —     | _    | —    | —          | _    | —              | _        | —    | _    | —                       | _    | 0000       |

| 0010                        | T IVIT VZ                       | 15:0          |                   |       | -     |       |       |       |      | TMR2 | <15:0>     |      |                |          | -    |      |                         |      | 0000       |

| 0820                        | PR2                             | 31:16         | —                 |       |       |       |       |       |      |      |            |      | 0000           |          |      |      |                         |      |            |

| 0020                        | 1112                            | 15:0          | PR2<15:0>         |       |       |       |       |       |      |      |            | FFFF |                |          |      |      |                         |      |            |

| 0A00                        | T3CON                           | 31:16         | —                 | —     | —     | —     | —     | —     | —    | _    | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

| 0,100                       | 100011                          | 15:0          | ON                | —     | SIDL  | _     | _     | —     | _    | _    | TGATE      |      | TCKPS<2:0>     | <b>`</b> | —    | —    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0A10                        | TMR3                            | 31:16         | —                 | —     | —     | _     | —     | —     | —    | —    | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             |                                 | 15:0          |                   |       | 1     |       |       |       |      | TMR3 | <15:0>     |      |                |          |      |      |                         |      | 0000       |

| 0A20                        | PR3                             | 31:16         | —                 | —     | —     | —     | —     | —     | —    | —    | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             | -                               | 15:0          |                   |       |       |       |       |       |      | PR3< | 15:0>      |      | -              |          |      |      |                         |      | FFFF       |

| 0C00                        | T4CON                           | 31:16         | _                 | —     | —     | —     | —     | —     | —    | —    | —          | —    | —              | —        |      | —    |                         | —    | 0000       |

|                             |                                 | 15:0          | ON                | _     | SIDL  | —     | _     | _     |      | _    | TGATE      |      | TCKPS<2:0>     | >        | T32  | _    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0C10                        | TMR4                            | 31:16         | —                 | —     |       | —     | —     | —     | _    |      |            | —    | —              | —        |      | _    | —                       | _    | 0000       |

|                             |                                 | 15:0          |                   |       |       |       |       |       |      | TMR4 |            |      |                |          |      |      |                         |      | 0000       |

| 0C20                        | PR4                             | 31:16         | -                 | —     | —     | —     | _     | _     | _    | -    | -          | _    | —              | _        | —    | _    | _                       | —    | 0000       |

|                             |                                 | 15:0          | _                 |       |       | _     |       |       |      | PR4< |            |      |                | _        |      | _    | _                       | _    | FFFF       |

| 0E00                        | T5CON                           | 31:16<br>15:0 | ON                |       |       |       |       |       |      |      | —<br>TGATE |      | <br>TCKPS<2:0> |          |      |      | —<br>TCS <sup>(2)</sup> |      | 0000       |

| <u> </u>                    |                                 | 31:16         | - UN              |       | SIDL  |       |       |       |      | _    | IGATE      | _    |                | ,<br>    | _    |      | -                       | _    | 0000       |

| 0E10                        | TMR5                            | 15:0          |                   |       |       |       |       |       |      |      |            | 0000 |                |          |      |      |                         |      |            |

|                             |                                 | 31:16         | _                 | _     |       | _     | _     | _     | _    | —    |            | _    | _              | _        | _    | _    | _                       | _    | 0000       |

| 0E20                        | PR5                             | 15:0          |                   |       |       |       |       |       |      |      |            |      | _              |          |      |      |                         |      |            |

|                             |                                 | 13.0          | :0 PR5<15:0> FFFF |       |       |       |       |       |      |      |            |      |                |          |      |      |                         |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|-------------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                     | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        |                      |                   |                         |                   | -                  |                   |                    | —                |

| 23:16        | U-0                  | U-0               | U-0                     | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23.10        | _                    | -                 | _                       | —                 | _                  | —                 | -                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0                   | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1,3)</sup>  |                   | SIDL <sup>(4)</sup>     | _                 | -                  | _                 | _                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0                   | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0> <sup>(:</sup> | 3)                | T32 <sup>(2)</sup> | _                 | TCS <sup>(3)</sup> | _                |

#### REGISTER 14-1: TXCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode0 = Continue operation when device is in Idle mode

- bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

When TCS = 1:

This bit is ignored and is read as '0'.

#### When TCS = 0:

1 =Gated time accumulation is enabled

0 = Gated time accumulation is disabled

#### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only available on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 31:24        | FRMEN             | FRMSYNC           | FRMPOL            | MSSEN             | FRMSYPW           | FRMCNT<2:0>       |                  |                       |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |  |  |

| 23:16        | _                 | —                 | _                 | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |  |  |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 7:0          | SSEN              | CKP               | MSTEN             | _                 | STXISEL<1:0>      |                   | SRXISEL<1:0>     |                       |  |  |

#### REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| F  | R = Readable bit | W = Writable bit | U = Unimplemented bit, re | oit, read as '0'   |  |  |  |

|----|------------------|------------------|---------------------------|--------------------|--|--|--|

| -1 | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

| bit 31 | FRMEN: Framed SPI Support | bit |

|--------|---------------------------|-----|

|        |                           | Dir |

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on SSx pin bit (only Framed SPI mode) 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (only Framed SPI mode)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed Sync mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23-18 Unimplemented: Read as '0'

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (only Framed SPI mode)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

## 20.1 Control Registers

### TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP

|                             |                       |           |        |        |        |       |        |       |       | Bi     | ts     |         |       |          |          |       |        |       |            |

|-----------------------------|-----------------------|-----------|--------|--------|--------|-------|--------|-------|-------|--------|--------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8   | 23/7   | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     |        |        | —      |       |        |       |       | _      |        | _       |       | _        |          |       |        |       | 0000       |

| 0000                        | UTWODE: /             | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN   | <1:0>  | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | _      |        |        |       | —      | _     |       | ADM_EN |        |         |       | ADDR     | <7:0>    |       |        | -     | 0000       |

| 0010                        | UIUIA                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISE | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 6020                        | U1TXREG               | 31:16     | —      | —      | —      | _     | —      | —     | —     | —      | —      | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0020                        | OTIMALEO              | 15:0      | —      | —      | —      | _     | —      | —     | —     | TX8    |        |         |       | Transmit | Register |       |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16     |        | —      | _      | _     | —      | _     | —     | _      |        | —       | —     | —        | —        | —     | —      | _     | 0000       |

| 0000                        | OHOULEO               | 15:0      |        | —      | _      | _     | —      | _     | —     | RX8    |        |         |       | Receive  | Register |       |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | —      | _      | —      | —     | —      | —     | _     | —      | -      | —       | —     | —        | _        | —     | _      | —     | 0000       |

|                             |                       | 15:0      |        |        |        |       |        |       |       | BRG<   | 15:0>  |         |       |          |          |       |        |       | 0000       |

| 6200                        | U4MODE <sup>(1)</sup> | 31:16     |        |        | _      | _     | _      | _     |       | —      |        |         | _     |          | _        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | ON     | _      | SIDL   | IREN  | _      | _     | _     | —      |        |         |       |          |          | STSEL | 0000   |       |            |

| 6210                        | U4STA <sup>(1)</sup>  | 31:16     |        | —      | _      | —     | —      | —     | —     | ADM_EN |        |         |       |          |          |       | r      | 0000  |            |

|                             |                       | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXIS  | L<1:0>  | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 6220                        | U4TXREG               | 31:16     | —      |        |        |       | _      | _     |       | —      |        |         | —     |          | —        | —     | —      | _     | 0000       |

|                             |                       | 15:0      | —      | —      | _      | —     | —      | —     | —     | TX8    |        |         |       | Transmit | Register |       |        |       | 0000       |

| 6230                        | U4RXREG               | 31:16     | —      |        |        |       | _      | _     |       | —      |        |         | —     |          | —        | —     | —      | _     | 0000       |

|                             |                       | 15:0      | —      |        |        |       | _      | _     |       | RX8    |        |         |       | Receive  | Register |       |        |       | 0000       |

| 6240                        | U4BRG <sup>(1)</sup>  | 31:16     |        | —      | —      | —     | —      | —     | —     | —      |        |         | —     |          | —        | —     | —      | _     | 0000       |

|                             |                       | 15:0      |        |        |        |       | 1      |       |       | BRG<   | 15:0>  | 1       |       | 1        |          |       |        | 1     | 0000       |

| 6400                        | U3MODE <sup>(1)</sup> | 31:16     | —      | _      | —      | —     | —      | —     | _     | —      | -      | —       | —     | _        | _        | -     | _      | —     | 0000       |

|                             |                       | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  |       | UEN   |        | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>  | 31:16     | —      | _      | -      | —     | —      | —     | _     | ADM_EN |        |         |       | ADDR     |          | 1     |        | I.    | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXIS  | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

| 6420                        | U3TXREG               | 31:16     | —      |        |        |       | _      | _     |       | —      |        |         | —     |          | —        | —     | —      | _     | 0000       |

|                             |                       | 15:0      | —      |        |        |       | _      | _     |       | TX8    |        |         |       | Transmit | Register |       |        |       | 0000       |

| 6430                        | <b>U3RXREG</b>        | 31:16     | —      | _      | -      | _     | —      | —     | _     | —      | -      | _       | —     | —        | _        | —     | _      | —     | 0000       |

|                             |                       | 15:0      | —      |        |        |       | _      | _     |       | RX8    |        |         |       | Receive  | Register |       |        |       | 0000       |

| 6440                        | U3BRG <sup>(1)</sup>  | 31:16     | —      | —      | -      | _     | —      | —     | —     | —      | —      | —       | _     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      |        |        |        |       |        |       |       |        |        |         | 0000  |          |          |       |        |       |            |

| 6600                        | U6MODE <sup>(1)</sup> | 31:16     | _      | _      | -      | —     | —      | _     | _     | —      | —      | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             | CONODE                | 15:0      | ON     | _      | SIDL   | IREN  | —      | _     | _     | —      | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE  | _<1:0> | STSEL | 0000       |

| 6610                        | U6STA <sup>(1)</sup>  | 31:16     | —      | —      | -      | —     | —      |       | —     | ADM_EN |        |         |       | ADDR     |          | 1     |        |       | 0000       |

| 0010                        | 2001/1                | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISE | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | 0110       |

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                 | —                 | -                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | IREN              | RTSMD             | -                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

#### **REGISTER 20-1: UXMODE: UARTX MODE REGISTER**

| Legend:           |                  | HC = Cleared by hard | ware               |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits.

- 0 = UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal.

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation when device enters Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

- bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range                                                 | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04                                                        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24                                                        |                   | YEAR1             | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |

| 00.40                                                        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16                                                        | 16 MONTH10<3:0>   |                   |                   |                   | MONTH01<3:0>      |                   |                  |                  |

| 45.0                                                         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8                                                         |                   | DAY10             | 0<3:0>            |                   | DAY01<3:0>        |                   |                  |                  |

| 7.0                                                          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0                                                          | —                 | —                 | _                 | _                 | WDAY01<3:0>       |                   |                  |                  |

|                                                              |                   |                   |                   |                   |                   |                   |                  |                  |

| Legend:                                                      |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Readable bit $W = Writable bit$ $U = Unimplemented bit,$ |                   |                   | emented bit, re   | ead as '0'        |                   |                   |                  |                  |

0' = Bit is cleared

### REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 04.04        | U-0                 | U-0                 |

| 31:24        | —                 | —                 | —                 |                   | _                 | —                 | —                   | _                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                 | —                 | FORM<2:0>         |                     |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           | —                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | R = Readable bit W = Writable bit |                      | ad as '0'          |

|-------------------|-----------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                  | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

#### bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing the SAMP bit ends sampling and starts conversion

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        | FLTEN27           | MSEL2             | 27<1:0>           |                   |                   | FSEL27<4:0>       |                  |                  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN26           | MSEL2             | 26<1:0>           | FSEL26<4:0>       |                   |                   |                  |                  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN25           | MSEL2             | 25<1:0>           | FSEL25<4:0>       |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN24           | MSEL2             | 24<1:0>           | FSEL24<4:0>       |                   |                   |                  |                  |  |

#### REGISTER 24-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | <b>FLTEN27:</b> Filter 27 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL27<1:0>: Filter 27 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | FSEL27<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN26: Filter 26 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                    |

| bit 22-21 | MSEL26<1:0>: Filter 26 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 20-16 | <pre>FSEL26&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>           |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 25-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   |                   |                   |                   |                   |                   | —                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   |                   |                   |                   |                   |                   | —                | _                |  |  |  |

| 15:8         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |  |  |

| 10.0         | —                 |                   | NB2BIPKTGP1<6:0>  |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |  |  |  |

| 7.0          |                   |                   |                   | NB2E              | BIPKTGP2<6:       | 0>                |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-15 Unimplemented: Read as '0'

#### bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If the carrier is detected during the timing of IPGR1, the MAC defers to the carrier. If, however, the carrier comes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to the medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

#### bit 7 Unimplemented: Read as '0'

## bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   | —                 |                   | —                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 15:8         |                   |                   |                   | STNADD            | R4<7:0>           |                   |                  |                  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 7:0          |                   |                   |                   | STNADD            | R3<7:0>           |                   |                  |                  |

#### REGISTER 25-38: EMAC1SA1: ETHERNET CONTROLLER MAC STATION ADDRESS 1 REGISTER

| Legend:           |                  | P = Programmable bit     |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR4<7:0>:** Station Address Octet 4 bits These bits hold the fourth transmitted octet of the station address.

- bit 7-0 **STNADDR3<7:0>:** Station Address Octet 3 bits These bits hold the third transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                    | —                 | _                 | -                 | _                 | _                 | _                | —                |

| 22.16        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                  | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-P              | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 15:8         | 15:8 STNADDR2<7:0> |                   |                   |                   |                   |                   |                  |                  |

| 7.0          | R/W-P              | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 7:0          |                    |                   |                   | STNADDR           | 1<7:0>            |                   |                  |                  |

#### REGISTER 25-39: EMAC1SA2: ETHERNET CONTROLLER MAC STATION ADDRESS 2 REGISTER

| Legend:           | P = Programmable bit |                        |                    |  |

|-------------------|----------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared   | x = Bit is unknown |  |

- bit 31-16 Reserved: Maintain as '0'; ignore read

- bit 15-8 **STNADDR2<7:0>:** Station Address Octet 2 bits These bits hold the second transmitted octet of the station address.

- bit 7-0 **STNADDR1<7:0>:** Station Address Octet 1 bits These bits hold the most significant (first transmitted) octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

| DC CHARACTERISTICS                                                            |                        |      | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |       |                                  |  |  |

|-------------------------------------------------------------------------------|------------------------|------|-------------------------------------------------------|---------------------|-------|----------------------------------|--|--|

| Parameter<br>No.                                                              | Typical <sup>(2)</sup> | Max. | Units                                                 | Conditions          |       |                                  |  |  |

| Idle Current (IIDLE) <sup>(1)</sup> for PIC32MX534/564/664/764 Family Devices |                        |      |                                                       |                     |       |                                  |  |  |

| DC30a                                                                         | 1.5                    | 5    |                                                       | -40°C, +25°C, +85°C |       | 4 MHz                            |  |  |

| DC30c                                                                         | 3.5                    | 6    | mA                                                    | +105⁰C              | —     | 4 M⊡Z                            |  |  |

| DC31a                                                                         | 7                      | 11   |                                                       | -40°C, +25°C, +85°C | —     | 25 MHz (Note 3)                  |  |  |

| DC32a                                                                         | 13                     | 20   | mA                                                    | -40°C, +25°C, +85°C | —     | 60 MHz (Note 3)                  |  |  |

| DC33a                                                                         | 17                     | 25   | - mA                                                  | -40°C, +25°C, +85°C |       | 80 MHz                           |  |  |

| DC33c                                                                         | 20                     | 27   | mA                                                    | +105°C              | —     |                                  |  |  |

| DC34c                                                                         |                        | 40   |                                                       | -40°C               |       | LPRC (31 kHz)<br><b>(Note 3)</b> |  |  |

| DC34d                                                                         |                        |      | μΑ                                                    | +25°C               | 2.3V  |                                  |  |  |

| DC34e                                                                         |                        |      |                                                       | +85°C               | 2.3V  |                                  |  |  |

| DC34f                                                                         |                        | 1000 |                                                       | +105°C              |       |                                  |  |  |

| DC35c                                                                         | 30                     |      | μA                                                    | -40°C               |       |                                  |  |  |

| DC35d                                                                         | 55                     |      |                                                       | +25°C               | 2.21/ |                                  |  |  |

| DC35e                                                                         | 230                    | _    |                                                       | +85°C               | 3.3V  |                                  |  |  |

| DC35f                                                                         | 800                    |      |                                                       | +105°C              |       |                                  |  |  |

| DC36c                                                                         |                        | 43   |                                                       | -40°C               |       |                                  |  |  |

| DC36d                                                                         | 1                      | 106  |                                                       | +25°C               | 2.01/ |                                  |  |  |

| DC36e                                                                         |                        | 800  | μA                                                    | +85°C               | 3.6V  |                                  |  |  |

| DC36f                                                                         | 1000                   |      | 1                                                     | +105ºC              |       |                                  |  |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

#### TABLE 32-36: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHARACTERISTICS |            |                                   | Standard Operating Conditions (see Note 5): 2.5V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |         |      |          |                                                         |  |

|--------------------|------------|-----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|----------|---------------------------------------------------------|--|

| Param.<br>No.      | Symbol     | Characteristics                   | Min.                                                                                                                                                                                                                   | Typical | Max. | Units    | Conditions                                              |  |

| ADC Ac             | curacy – N | leasurements with Inter           | nal VREF+/VR                                                                                                                                                                                                           | EF-     |      |          |                                                         |  |

| AD20d              | Nr         | Resolution                        | 10 data bits                                                                                                                                                                                                           |         | bits | (Note 3) |                                                         |  |

| AD21d              | INL        | Integral Nonlinearity             | > -1                                                                                                                                                                                                                   | —       | < 1  | LSb      | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD22d              | DNL        | Differential Nonlinearity         | > -1                                                                                                                                                                                                                   |         | < 1  | LSb      | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |

| AD23d              | Gerr       | Gain Error                        | > -4                                                                                                                                                                                                                   | -       | < 4  | LSb      | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD24d              | EOFF       | Offset Error                      | > -2                                                                                                                                                                                                                   | -       | < 2  | LSb      | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD25d              | —          | Monotonicity                      | —                                                                                                                                                                                                                      | —       | _    | —        | Guaranteed                                              |  |

| Dynami             | c Performa | ance                              |                                                                                                                                                                                                                        |         |      |          |                                                         |  |