Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064l-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         |                      | Pin Nur         | nber <sup>(1)</sup> |                 | Dim         | Duffer         |                                   |

|---------|----------------------|-----------------|---------------------|-----------------|-------------|----------------|-----------------------------------|

| Pin Nam | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                       |

| RA0     | _                    | 17              | G3                  | B9              | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1     | —                    | 38              | J6                  | A26             | I/O         | ST             |                                   |

| RA2     | —                    | 58              | H11                 | A39             | I/O         | ST             |                                   |

| RA3     | —                    | 59              | G10                 | B32             | I/O         | ST             |                                   |

| RA4     | —                    | 60              | G11                 | A40             | I/O         | ST             |                                   |

| RA5     | —                    | 61              | G9                  | B33             | I/O         | ST             |                                   |

| RA6     | —                    | 91              | C5                  | B51             | I/O         | ST             |                                   |

| RA7     | —                    | 92              | B5                  | A62             | I/O         | ST             |                                   |

| RA9     | —                    | 28              | L2                  | A21             | I/O         | ST             |                                   |

| RA10    |                      | 29              | K3                  | B17             | I/O         | ST             | ]                                 |

| RA14    |                      | 66              | E11                 | B36             | I/O         | ST             | ]                                 |

| RA15    | —                    | 67              | E8                  | A44             | I/O         | ST             |                                   |

| RB0     | 16                   | 25              | K2                  | B14             | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1     | 15                   | 24              | K1                  | A15             | I/O         | ST             |                                   |

| RB2     | 14                   | 23              | J2                  | B13             | I/O         | ST             |                                   |

| RB3     | 13                   | 22              | J1                  | A13             | I/O         | ST             |                                   |

| RB4     | 12                   | 21              | H2                  | B11             | I/O         | ST             |                                   |

| RB5     | 11                   | 20              | H1                  | A12             | I/O         | ST             |                                   |

| RB6     | 17                   | 26              | L1                  | A20             | I/O         | ST             |                                   |

| RB7     | 18                   | 27              | J3                  | B16             | I/O         | ST             |                                   |

| RB8     | 21                   | 32              | K4                  | A23             | I/O         | ST             |                                   |

| RB9     | 22                   | 33              | L4                  | B19             | I/O         | ST             |                                   |

| RB10    | 23                   | 34              | L5                  | A24             | I/O         | ST             | 1                                 |

| RB11    | 24                   | 35              | J5                  | B20             | I/O         | ST             | ]                                 |

| RB12    | 27                   | 41              | J7                  | B23             | I/O         | ST             | ]                                 |

| RB13    | 28                   | 42              | L7                  | A28             | I/O         | ST             | ]                                 |

| RB14    | 29                   | 43              | K7                  | B24             | I/O         | ST             |                                   |

| RB15    | 30                   | 44              | L8                  | A29             | I/O         | ST             |                                   |

| RC1     | —                    | 6               | D1                  | A5              | I/O         | ST             | PORTC is a bidirectional I/O port |

| RC2     | —                    | 7               | E4                  | B4              | I/O         | ST             |                                   |

| RC3     | —                    | 8               | E2                  | A6              | I/O         | ST             |                                   |

| RC4     |                      | 9               | E1                  | B5              | I/O         | ST             | ]                                 |

| RC12    | 39                   | 63              | F9                  | B34             | I/O         | ST             | ]                                 |

| RC13    | 47                   | 73              | C10                 | A47             | I/O         | ST             | ]                                 |

| RC14    | 48                   | 74              | B11                 | B40             | I/O         | ST             | ]                                 |

|         | -                    | 64              | F11                 | A42             | I/O         | ST             | 1                                 |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

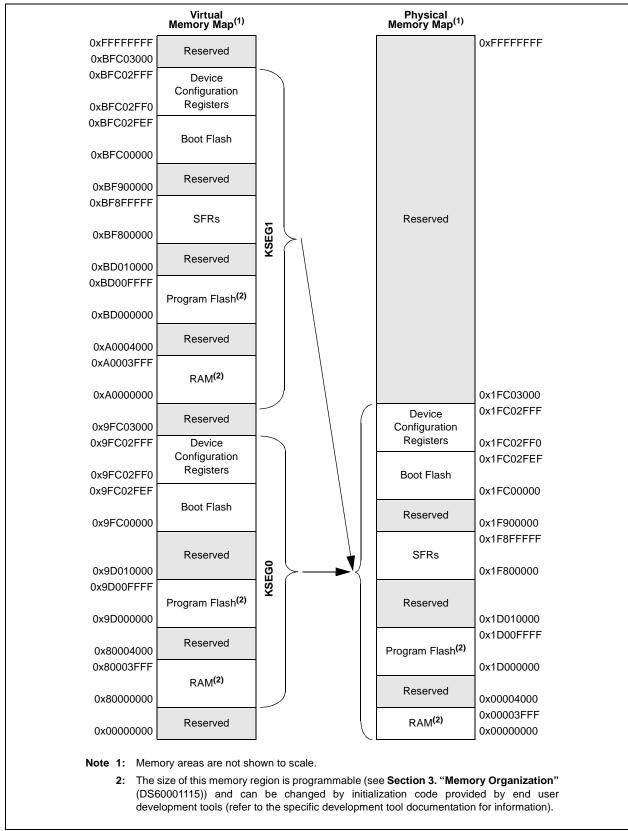

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        |                   | _                     | BYTO              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                     | _                 | —                 | —                  | _                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | —                  | (                 | CRCCH<2:0>       | ,                |

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

#### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-30 **Unimplemented:** Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (reverse source byte order)

- 00 = No swapping (source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (not reflected)

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

#### REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | —                 |                   |                   |                   |                   |                  | —                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           |                   |                   |                  | UASUSPND         |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

- bit 6 **UOEMON:** USB OE Monitor Enable bit

- $1 = \overline{OE}$  signal is active; it indicates intervals during which the D+/D- lines are driving

- $0 = \overline{OE}$  signal is inactive

- bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   | _                 |                   |                   |                  | _                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | -                 |                   | -                 |                   |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | —                 | —                 | —                 | -                 | -                | —                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

#### REGISTER 11-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

bit 1

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NACK'd transactions disabled

- 0 = Retry NACK'd transactions enabled; retry done in hardware

- bit 5 Unimplemented: Read as '0'

- bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

- If EPTXEN = 1 and EPRXEN = 1:

- 1 = Disable Endpoint 'n' from control transfers; only TX and RX transfers are allowed

- 0 = Enable Endpoint 'n' for control (SETUP) transfers; TX and RX transfers are also allowed Otherwise, this bit is ignored.

- bit 3 EPRXEN: Endpoint Receive Enable bit

- 1 = Endpoint 'n' receive is enabled

- 0 = Endpoint 'n' receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint 'n' transmit is enabled

- 0 = Endpoint 'n' transmit is disabled

- EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint 'n' was stalled

- 0 = Endpoint 'n' was not stalled

- bit 0 **EPHSHK:** Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

## TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |         |        |       |        | •      |              |               | Bi      | ts    |             |             |           |          |        |      |          |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|--------|--------------|---------------|---------|-------|-------------|-------------|-----------|----------|--------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11  | 26/10        | 25/9          | 24/8    | 23/7  | 22/6        | 21/5        | 20/4      | 19/3     | 18/2   | 17/1 | 16/0     | All Resets |

| 5230                        | I2C5MSK                         | 31:16         | -       | —      | —     | _      |        | _            | —             | -       | _     | _           |             | _         | —        | —      | _    |          | 0000       |

| 5230                        | IZCONISK                        | 15:0          | -       | —      | —     | -      |        | _            |               |         |       |             | MSK         | <9:0>     |          |        |      | -        | 0000       |

| 5240                        | I2C5BRG                         | 31:16         | _       | _      | _     | —      | _      | —            | —             | —       | _     | —           | _           | —         | —        |        | -    | _        | 0000       |

| 5240                        |                                 | 15:0          | —       | —      | —     | —      |        |              |               |         | Ba    | ud Rate Ger | erator Regi | ster      |          |        | •    |          | 0000       |

| 5250                        | I2C5TRN                         | 31:16         | —       | —      | —     | —      | _      | —            | _             | —       | _     | —           | —           | —         | —        |        | —    | —        | 0000       |

| 0200                        |                                 | 15:0          | —       | _      | _     | —      | _      | —            | _             | _       |       | -           |             | Transmit  | Register |        | •    |          | 0000       |

| 5260                        | I2C5RCV                         | 31:16         | -       |        |       | —      | _      | -            |               | _       | _     | —           | _           | —         |          | _      | —    | _        | 0000       |

|                             |                                 | 15:0          | -       |        | —     | —      |        | —            |               | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| 5300                        | I2C1CON                         | 31:16         | _       | —      | —     | —      | —      | —            | —             | —       | _     | —           | —           | —         | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | ON      | _      | SIDL  | SCLREL | STRICT | A10M         | DISSLW        | SMEN    | GCEN  | STREN       | ACKDT       | ACKEN     | RCEN     | PEN    | RSEN | SEN      | 1000       |

| 5310                        | I2C1STAT                        | 31:16         | —       | _      | _     | _      | _      | _            | —             | —       | _     | —           | —           | _         | _        |        | —    | _        | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT | —     | —      | —      | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5320                        | I2C1ADD                         | 31:16         | _       | _      | —     | —      | _      |              | —             |         | _     | —           |             | _         | —        |        | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _      | -            |               |         |       |             | ADD         | <9:0>     |          |        |      |          | 0000       |

| 5330                        | I2C1MSK                         | 31:16         | _       | _      | _     | _      | _      | -            | _             | -       | _     | _           | —           | -         | _        | -      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       |        | _     | _      |        | _            |               |         |       |             | MSK         | <9:0>     |          |        | 1    |          | 0000       |

| 5340                        | I2C1BRG                         | 31:16         | _       |        |       | _      | _      | —            |               | _       | -     | -           |             | _         | —        |        | -    | _        | 0000       |

| -                           |                                 | 15:0          | _       |        |       | _      |        |              |               |         | Ва    | ud Rate Ger | Ū.          | ster      |          |        | 1    |          | 0000       |

| 5350                        | I2C1TRN                         | 31:16         | _       | —      | —     | _      | _      | _            | _             | _       | _     | _           | —           |           | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _      | _            |               | _       |       |             |             | Transmit  | Register |        |      |          | 0000       |

| 5360                        | I2C1RCV                         | 31:16<br>15:0 | _       | _      |       |        |        | —            |               |         | —     | —           | —           | - Deseive |          | —      | —    | —        | 0000       |

|                             |                                 |               |         |        |       |        |        | _            |               |         |       |             |             | Receive   |          |        |      |          |            |

| 5400                        | 12C2CON(2)                      | 31:16<br>15:0 | ON      |        | -     | -      |        | -            | —<br>DI001144 | -       | -     | —<br>STREN  | —<br>ACKDT  |           |          | -      |      | -        | 0000       |

|                             |                                 |               |         | _      | SIDL  | SCLREL | STRICT | A10M         | DISSLW        | SMEN    | GCEN  |             |             |           |          | PEN    | RSEN | SEN      | 1000       |

| 5410                        | 12C2STAT <sup>(2)</sup>         | 31:16         |         |        | _     | _      | _      | —<br>DCI     | —<br>         | -       | -     | -           | —<br>D/A    | —<br>P    | -        | —<br>• | -    | —<br>TDF | 0000       |

|                             |                                 | 15:0<br>31:16 | ACKSTAT | TRSTAT |       | _      | _      | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5420                        | 12C2ADD(2)                      | 15:0          |         |        |       | _      | _      |              | _             | -       | —     | —           |             | <br><9:0> | —        |        | —    | —        | 0000       |

|                             |                                 | 31:16         | _       |        |       | _      |        | _            | _             |         | _     |             | ADD         | <9.0>     |          |        | _    | _        | 0000       |

| 5430                        | 12C2MSK <sup>(2)</sup>          | 15:0          |         |        |       |        |        |              |               | _       | _     | _           | <br>MSK     | <0.0>     | _        |        | _    | _        | 0000       |

|                             |                                 | 31:16         |         |        |       |        |        |              |               |         | _     |             |             | < 3.02    |          |        |      | _        | 0000       |

| 5440                        | I2C2BRG <sup>(2)</sup>          | 15:0          | _       |        |       | _      | _      | _            | _             |         | Ra    | ud Rate Ger | erator Regi | ster      |          |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _            | _             | _       | Da    |             |             |           | _        |        | _    | _        | 0000       |

| 5450                        | I2C2TRN <sup>(2)</sup>          | 15:0          | _       | _      | _     |        | _      |              | _             |         |       |             |             | Transmit  | Register |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      |        | _            | _             | _       | _     | _           | _           |           |          |        | _    | _        | 0000       |

| 5460                        | 12C2RCV <sup>(2)</sup>          | 15:0          | _       | _      | _     | _      | _      | _            | _             | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| Legen                       |                                 |               |         |        |       |        |        | Les are show | l<br>         | aire al |       |             |             | 110001100 |          |        |      |          | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

## REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 5 **ABAUD:** Auto-Baud Enable bit 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55);

- cleared by hardware upon completion 0 = Baud rate measurement disabled or completed

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

## 21.1 Control Registers

## TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

|                                         |                                 |           |                                                                                                                                                 |              |       |       |         |        |        | Bi     | ts      |        |      |      |      |      |      |      |            |

|-----------------------------------------|---------------------------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-------|-------|---------|--------|--------|--------|---------|--------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#)<br>Register | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                                                                                                                           | 30/14        | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000 PM0                                |                                 | 31:16     | _                                                                                                                                               | _            | _     | _     | _       | _      | _      | _      |         | _      | _    | _    | —    | _    | —    | _    | 0000       |

| 7000 1 100                              |                                 | 15:0      | ON                                                                                                                                              | —            | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P | CS1P | —    | WRSP | RDSP | 0000       |

| 7010 PMM                                | MODE                            | 31:16     | —                                                                                                                                               | —            | —     | —     | —       | —      | —      | —      | —       | —      | —    | —    | —    | —    | —    | —    | 0000       |

| 7010 Pivily                             | NODE                            | 15:0      | BUSY         IRQM<1:0>         INCM<1:0>         MODE16         MODE<1:0>         WAITE<1:0>         WAITM<3:0>         WAITE<1:0>         0000 |              |       |       |         |        |        |        |         |        |      |      |      |      |      |      |            |

| 7020 PMA                                |                                 | 31:16     |                                                                                                                                                 | _            | _     | _     | _       | _      | _      |        | _       | -      | -    | _    | _    | _    | _    | _    | 0000       |

| 7020 PINA                               | IADDR                           | 15:0      | CS2EN/A15                                                                                                                                       | CS1EN/A14    |       |       |         |        |        |        | ADDR    | <13:0> |      |      |      |      |      |      | 0000       |

| 7000 040                                |                                 | 31:16     |                                                                                                                                                 |              |       |       |         |        |        | DATAOU | T 04.0  |        |      |      |      |      |      |      | 0000       |

| 7030 PMD                                |                                 | 15:0      |                                                                                                                                                 |              |       |       |         |        |        | DATAOU | 1<31:0> |        |      |      |      |      |      |      | 0000       |

| 7040 DM                                 | MDIN                            | 31:16     |                                                                                                                                                 |              |       |       |         |        |        |        | .01.0   |        |      |      |      |      |      |      | 0000       |

| 7040 PM                                 |                                 | 15:0      |                                                                                                                                                 | DATAIN<31:0> |       |       |         |        |        |        |         |        |      |      |      |      |      |      |            |

| 7050 014                                | MAEN                            | 31:16     |                                                                                                                                                 | _            | _     | _     | _       | _      | _      |        | _       | -      | -    | _    | _    | _    | _    | _    | 0000       |

| 7050 PM/                                | VIAEN                           | 15:0      |                                                                                                                                                 |              |       |       |         |        |        | PTEN<  | :15:0>  |        |      |      |      |      |      |      | 0000       |

| 7000 0140                               | 10TAT                           | 31:16     | _                                                                                                                                               | _            | _     | _     | _       | _      | _      | _      | _       | _      | —    | _    | _    | _    | _    | _    | 0000       |

| 7060 PMS                                | ISTAL                           | 15:0      | IBF                                                                                                                                             | IBOV         | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —    | -    | OB3E | OB2E | OB1E | OB0E | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 |                   | —                 | —                 | —                | —                |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01             | <3:0>            |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   | _                 | _                 |                   |                   | WDAY0             | )1<3:0>          |                  |

## REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

## Legend:

| Logona.           |                  |                        |                    | 1 |

|-------------------|------------------|------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        | I |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |   |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23.10        | —                 | —                 | ТХВО              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.6         |                   |                   |                   | TERRCI            | NT<7:0>           |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | RERRC             | NT<7:0>           |                   |                  |                  |

#### REGISTER 24-5: CITREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT  $\geq$  128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

- bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

- bit 17 **RXWARN:** Receiver in Error State Warning  $(128 > \text{RERRCNT} \ge 96)$

- bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

#### REGISTER 24-6: CIFSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24        | FIFOIP31          | FIFOIP30          | FIFOIP29          | FIFOIP28          | FIFOIP27          | FIFOIP26          | FIFOIP25         | FIFOIP24         |

| 23:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23.10        | FIFOIP23          | FIFOIP22          | FIFOIP21          | FIFOIP20          | FIFOIP19          | FIFOIP18          | FIFOIP17         | FIFOIP16         |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | FIFOIP15          | FIFOIP14          | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | FIFOIP7           | FIFOIP6           | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-0 FIFOIP<31:0>: FIFOn Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | FLTEN19           | MSEL1             | 9<1:0>            |                   | F                 | SEL19<4:0>        | >                |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN18           | MSEL1             | 8<1:0>            |                   | F                 | SEL18<4:0>        | >                |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | FLTEN17           | MSEL1             | 7<1:0>            |                   | F                 | SEL17<4:0>        | >                |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | FLTEN16           | MSEL1             | 6<1:0>            |                   | F                 | SEL16<4:0>        | >                |                  |  |

### REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | <b>FLTEN19:</b> Filter 19 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                                                                                       |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                              |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                                                                             |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>      |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           |                                                                                                                                                                                     |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

|           |                                                                                                                                                                                     |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 24-20: CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

- bit 6 TXABAT: Message Aborted bit<sup>(2)</sup> 1 = Message was aborted 0 = Message completed successfully bit 5 TXLARB: Message Lost Arbitration bit<sup>(3)</sup> 1 = Message lost arbitration while being sent 0 = Message did not lose arbitration while being sent TXERR: Error Detected During Transmission bit<sup>(3)</sup> bit 4 1 = A bus error occured while the message was being sent 0 = A bus error did not occur while the message was being sent bit 3 **TXREQ:** Message Send Request TXEN = 1: (FIFO configured as a Transmit FIFO) Setting this bit to '1' requests sending a message. The bit will automatically clear when all the messages queued in the FIFO are successfully sent. Clearing the bit to '0' while set ('1') will request a message abort. TXEN = 0: (FIFO configured as a receive FIFO) This bit has no effect. bit 2 RTREN: Auto RTR Enable bit 1 = When a remote transmit is received, TXREQ will be set 0 = When a remote transmit is received, TXREQ will be unaffected bit 1-0 TXPR<1:0>: Message Transmit Priority bits 11 = Highest message priority 10 = High intermediate message priority 01 = Low intermediate message priority 00 = Lowest message priority Note 1: These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

#### REGISTER 25-17: ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | FRMTXOKCNT<15:8>  |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | FRMTXOKCNT<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## **30.0 INSTRUCTION SET**

The PIC32MX5XX/6XX/7XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core Extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

| DC CHARACTERISTICS |                        |                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                              |                           |      |               |  |

|--------------------|------------------------|-------------------------------------|------------------------------------------------------|------------------------------|---------------------------|------|---------------|--|

| Param.<br>No.      | Typical <sup>(3)</sup> | Max.                                | Units                                                |                              | Conditions                | i    |               |  |

| Operatir           | ng Current (I          | DD) <sup>(1,2,4)</sup> f <b>O</b> I | PIC32MX5                                             | 575/675/695/775/795 Family D | )evices                   |      |               |  |

| DC20               | 6                      | 9                                   | mA                                                   | Code executing from Flash    | 4 MHz                     |      |               |  |

| DC20b              | 7                      | 10                                  |                                                      |                              | +105⁰C                    |      |               |  |

| DC20a              | 4                      |                                     |                                                      | Code executing from SRAM     | _                         |      |               |  |

| DC21               | 37                     | 40                                  | mA                                                   | Code executing from Flash    |                           |      | 25 MHz        |  |

| DC21a              | 25                     |                                     | IIIA                                                 | Code executing from SRAM     | _                         | _    |               |  |

| DC22               | 64                     | 70                                  | mA                                                   | Code executing from Flash    |                           |      | 60 MHz        |  |

| DC22a              | 61                     | _                                   | IIIA                                                 | Code executing from SRAM     |                           |      |               |  |

| DC23               | 85                     | 98                                  | mA                                                   | Code executing from Flash    | -40ºC,<br>+25ºC,<br>+85ºC | _    | 80 MHz        |  |

| DC23b              | 90                     | 120                                 | ]                                                    | +105°C                       |                           |      |               |  |

| DC23a              | 85                     |                                     | ]                                                    | Code executing from SRAM —   |                           |      |               |  |

| DC25a              | 125                    | 150                                 | μA                                                   | —                            | +25°C                     | 3.3V | LPRC (31 kHz) |  |

#### TABLE 32-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

| DC CHA     | RACTER                                            | ISTICS                                                                                                                     | (unless            | otherwi  | se state | ed)                                          | $\frac{1}{2.3} \times \frac{1}{5} \times $ |

|------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------|----------|----------|----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            |                                                   |                                                                                                                            | Operatin           | ig tempe | erature  |                                              | $\leq$ TA $\leq$ +85°C for Industrial<br>$\leq$ TA $\leq$ +105°C for V-temp                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Param.     | Symbol                                            | Characteristic                                                                                                             | Min.               | Тур.     | Max.     | Units                                        | Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |