Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064l-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                |                                            | Pin Nun                    | nber <sup>(1)</sup> |                 |             | <b>D</b> "     |                                       |

|----------------|--------------------------------------------|----------------------------|---------------------|-----------------|-------------|----------------|---------------------------------------|

| Pin Name       | 64-Pin<br>QFN/TQFP                         | 100-Pin<br>TQFP            | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                           |

| CN0            | 48                                         | 74                         | B11                 | B40             | I           | ST             | Change notification inputs. Can be    |

| CN1            | 47                                         | 73                         | C10                 | A47             | I           | ST             | software programmed for internal weak |

| CN2            | 16                                         | 25                         | K2                  | B14             | I           | ST             | pull-ups on all inputs.               |

| CN3            | 15                                         | 24                         | K1                  | A15             | I           | ST             |                                       |

| CN4            | 14                                         | 23                         | J2                  | B13             | I           | ST             |                                       |

| CN5            | 13                                         | 22                         | J1                  | A13             | I           | ST             |                                       |

| CN6            | 12                                         | 21                         | H2                  | B11             | I           | ST             |                                       |

| CN7            | 11                                         | 20                         | H1                  | A12             | I           | ST             |                                       |

| CN8            | 4                                          | 10                         | E3                  | A7              | I           | ST             |                                       |

| CN9            | 5                                          | 11                         | F4                  | B6              | I           | ST             |                                       |

| CN10           | 6                                          | 12                         | F2                  | A8              | I           | ST             |                                       |

| CN11           | 8                                          | 14                         | F3                  | A9              | I           | ST             |                                       |

| CN12           | 30                                         | 44                         | L8                  | A29             | I           | ST             |                                       |

| CN13           | 52                                         | 81                         | C8                  | B44             | I           | ST             |                                       |

| CN14           | 53                                         | 82                         | B8                  | A55             | I           | ST             |                                       |

| CN15           | 54                                         | 83                         | D7                  | B45             | I           | ST             |                                       |

| CN16           | 55                                         | 84                         | C7                  | A56             | I           | ST             |                                       |

| CN17           | 31                                         | 49                         | L10                 | B27             | I           | ST             |                                       |

| CN18           | 32                                         | 50                         | L11                 | A32             | I           | ST             |                                       |

| CN19           | —                                          | 80                         | D8                  | A54             | I           | ST             |                                       |

| CN20           | —                                          | 47                         | L9                  | B26             | I           | ST             |                                       |

| CN21           | —                                          | 48                         | K9                  | A31             | I           | ST             |                                       |

| IC1            | 42                                         | 68                         | E9                  | B37             | I           | ST             | Capture Inputs 1-5                    |

| IC2            | 43                                         | 69                         | E10                 | A45             | I           | ST             |                                       |

| IC3            | 44                                         | 70                         | D11                 | B38             | I           | ST             | -                                     |

| IC4            | 45                                         | 71                         | C11                 | A46             | I           | ST             | -                                     |

| IC5            | 52                                         | 79                         | A9                  | A60             | I           | ST             | -                                     |

| OCFA           | 17                                         | 26                         | L1                  | A20             | I           | ST             | Output Compare Fault A Input          |

| OC1            | 46                                         | 72                         | D9                  | B39             | 0           | _              | Output Compare Output 1               |

| OC2            | 49                                         | 76                         | A11                 | A52             | 0           |                | Output Compare Output 2               |

| OC3            | 50                                         | 77                         | A10                 | B42             | 0           |                | Output Compare Output 3               |

| OC4            | 51                                         | 78                         | B9                  | A53             | 0           | _              | Output Compare Output 4               |

| OC5            | 52                                         | 81                         | C8                  | B44             | 0           |                | Output Compare Output 5               |

| OCFB           | 30                                         | 44                         | L8                  | A29             | I           | ST             | Output Compare Fault B Input          |

| INT0           | 46                                         | 72                         | D9                  | B39             | I           | ST             | External Interrupt 0                  |

| INT1           | 42                                         | 18                         | G1                  | A11             | I           | ST             | External Interrupt 1                  |

| INT2           | 43                                         | 19                         | G2                  | B10             | I           | ST             | External Interrupt 2                  |

| INT3           | 44                                         | 66                         | E11                 | B36             | 1           | ST             | External Interrupt 3                  |

| INT4           | 45                                         | 67                         | E8                  | A44             | 1           | ST             | External Interrupt 4                  |

| Legend: C<br>S | MOS = CMO<br>T = Schmitt T<br>TL = TTL inp | S compatib<br>rigger input | le input or c       | output          | A           |                | Analog input P = Power                |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# 6.1 Control Registers

## TABLE 6-1: RESETS REGISTER MAP

| ess                         |                                 | e         |       | Bits  |       |       |       |       |      |       |      |      |      | (2)  |       |      |      |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Resets |

| E000                        | DCON                            | 31:16     | _     | —     | —     | —     | _     | _     | _    | _     | _    | —    | —    | _    | _     | _    | —    | —     | 0000       |

| F600                        | RCON                            | 15:0      |       | _     | _     | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | _    | WDTO | SLEEP | IDLE | BOR  | POR   | 0000       |

| 5040                        | RSWRST                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _     | _    | _    | _    | _    | _     | _    | _    | _     | 0000       |

| F610                        | RSWRSI                          | 15:0      | —     |       |       | _     | _     | —     | _    | —     | —    | _    |      | _    | _     | _    | _    | SWRST | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

#### **TABLE 7-2:** INTERRUPT REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H AND PIC32MX575F512H DEVICES (CONTINUED)

| ess                         |                                 | 0         |                        |       |       |            |             |            |         | Bits                 |      |            |             |            |            |             |        |                       |               |

|-----------------------------|---------------------------------|-----------|------------------------|-------|-------|------------|-------------|------------|---------|----------------------|------|------------|-------------|------------|------------|-------------|--------|-----------------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                  | 30/14 | 29/13 | 28/12      | 27/11       | 26/10      | 25/9    | 24/8                 | 23/7 | 22/6       | 21/5        | 20/4       | 19/3       | 18/2        | 17/1   | 16/0                  | All<br>Resets |

| 10A0                        | IPC1                            | 31:16     | _                      | —     | —     |            | INT1IP<2:0> |            | INT1IS  | <1:0>                | -    | _          | _           | OC1IP<2:0> |            | OC1IS       | S<1:0> | 0000                  |               |

| TUAU                        | IFCI                            | 15:0      |                        | _     | _     |            | IC1IP<2:0>  |            | IC1IS<  | <1:0>                | _    | _          |             | -          | T1IP<2:0>  |             | T1IS   | <1:0>                 | 0000          |

| 10B0                        | IPC2                            | 31:16     |                        | —     | —     |            | INT2IP<2:0> |            | INT2IS  | <1:0>                | —    | _          | -           | C          | C2IP<2:0>  | >           | OC2IS  | S<1:0>                | 0000          |

| тово                        | IF 02                           | 15:0      |                        | _     | _     |            | IC2IP<2:0>  |            | IC2IS<  | <1:0>                | _    | -          |             | -          | T2IP<2:0>  |             | T2IS   | <1:0>                 | 0000          |

| 10C0                        | IPC3                            | 31:16     |                        | _     | _     |            | INT3IP<2:0> |            | INT3IS  | <1:0>                | —    | _          |             | C          | C3IP<2:0>  | >           | OC3IS  | S<1:0>                | 0000          |

| 1000                        | 11 00                           | 15:0      | —                      | —     | —     |            | IC3IP<2:0>  |            | IC3IS<  | <1:0>                | —    | —          | —           | -          | T3IP<2:0>  |             | T3IS   | <1:0>                 | 0000          |

| 10D0                        | IPC4                            | 31:16     | —                      | —     | —     |            | INT4IP<2:0> |            | INT4IS  | <1:0>                | —    | —          | —           | C          | C4IP<2:0>  | <b>&gt;</b> | OC4IS  | S<1:0>                | 0000          |

| TODO                        | 11 04                           | 15:0      | —                      | —     | —     |            | IC4IP<2:0>  |            | IC4IS<  | <1:0>                | —    | —          | —           | -          | T4IP<2:0>  |             | T4IS   | <1:0>                 | 0000          |

| 10E0                        | IPC5                            | 31:16     | —                      | —     | —     |            | —           | —          | —       | —                    | —    | —          | _           | -          | C5IP<2:0>  | >           | OC5IS  | S<1:0>                | 0000          |

| IOLO                        | 1 00                            | 15:0      | —                      | —     | —     |            | IC5IP<2:0>  |            | IC5IS<  | <1:0>                | —    | —          | —           |            | T5IP<2:0>  |             | T5IS   |                       | 0000          |

|                             |                                 | 31:16     | —                      | —     | —     | AD1IP<2:0> |             | AD1IP<2:0> |         | <1:0>                | —    | —          | —           | CNIP<2:0>  |            | CNIS        | -      | 0000                  |               |

| 10E0                        | 10F0 IPC6                       |           |                        |       |       |            |             |            |         |                      |      |            |             | l          | J1IP<2:0>  |             | U1IS   | <1:0>                 |               |

| 101.0                       | 1 00                            | 15:0      | 15:0 — — — I2C1IP<2:0> |       |       | I2C1IS     | <1:0>       | —          | —       | —                    | S    | PI3IP<2:0: | >           | SPI3IS     | S<1:0>     | 0000        |        |                       |               |

|                             |                                 |           |                        |       |       |            |             |            |         |                      |      |            |             | 12         | 2C3IP<2:0> | >           | 12C31  | S<1:0>                |               |

|                             |                                 |           |                        |       |       |            | U3IP<2:0>   |            | U3IS<   | :1:0>                |      |            |             |            |            |             |        |                       |               |

| 1100                        | IPC7                            | 31:16     | —                      | —     | —     |            | SPI2IP<2:0> |            | SPI2IS  | <1:0>                | —    | —          | —           | C          | MP2IP<2:0  | >           | CMP2I  | S<1:0>                | 0000          |

| 1100                        | 11 07                           |           |                        |       |       |            | I2C4IP<2:0> |            | I2C4IS  | -                    |      |            |             |            |            |             |        |                       |               |

|                             |                                 | 15:0      | —                      | —     | —     | (          | CMP1IP<2:0> | •          | CMP1IS  |                      | —    | —          | _           |            | MPIP<2:0   |             | PMPIS  | S<1:0>                | 0000          |

|                             |                                 | 31:16     | —                      | —     | —     | F          | RTCCIP<2:0> | •          | RTCCIS  | S<1:0>               | —    | —          | _           |            | SCMIP<2:0  | >           |        | S<1:0>                | 0000          |

| 1110                        | IPC8                            |           |                        |       |       |            |             |            |         |                      |      |            |             |            | J2IP<2:0>  |             | U2IS   |                       |               |

|                             | 11 00                           | 15:0      | —                      | —     | —     | —          | —           | —          | —       | —                    | —    | —          | —           | S          | PI4IP<2:0; | >           | SPI4IS | S<1:0>                | 0000          |

|                             |                                 |           |                        |       |       |            |             |            |         |                      |      |            |             |            | 2C5IP<2:0> |             | 12C518 |                       |               |

| 1120                        | IPC9                            | 31:16     | _                      | —     | —     |            | DMA3IP<2:0> |            | DMA3IS  |                      | _    | —          | _           |            | MA2IP<2:0  |             | DMA2I  |                       | 0000          |

| 1120                        | 11 00                           | 15:0      | _                      | —     | —     |            | DMA1IP<2:0> |            | DMA1IS  |                      | _    | —          | _           |            | MA0IP<2:0  |             | DMA0I  |                       | 0000          |

| 1130                        | IPC10                           | 31:16     | —                      | —     | —     |            | MA7IP<2:0>( |            | DMA7IS- | -                    | —    | —          | —           |            | A6IP<2:0>  |             |        | S<1:0> <sup>(2)</sup> | 0000          |

| 1100                        | 1 010                           | 15:0      | —                      | —     | —     | D          | MA5IP<2:0>( | 2)         | DMA5IS- | <1:0> <sup>(2)</sup> | —    | —          | —           | DM         | IA4IP<2:0> | (2)         | DMA4IS | S<1:0> <sup>(2)</sup> | 0000          |

| 1140                        | IPC11                           | 31:16     | _                      | _     | _     |            |             | _          | _       | —                    | _    | _          | CAN1IP<2:0> |            | CAN1I      | S<1:0>      | 0000   |                       |               |

| 1140                        |                                 | 15:0      | —                      | —     | —     |            | USBIP<2:0>  |            | USBIS   | <1:0>                | —    | —          | _           | FCEIP<2:0> |            | FCEIS       | 6<1:0> | 0000                  |               |

| 1150                        | IPC12                           | 31:16     | _                      | —     | —     |            | U5IP<2:0>   |            | U5IS<   | :1:0>                | —    | —          | —           | U6IP<2:0>  |            | U6IS        | <1:0>  | 0000                  |               |

| 1100                        | 1 012                           | 15:0      | —                      | —     | —     |            | U4IP<2:0>   |            | U4IS<   | :1:0>                | —    | —          | _           | —          | —          | -           | -      | —                     | 0000          |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET Note 1: and INV Registers" for more information.

These bits are not available on PIC32MX534/564/664/764 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

# TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |             |                         |             |                            | Bi          | its         |                   |             |             |             |             |             |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|-------------------------|-------------|----------------------------|-------------|-------------|-------------------|-------------|-------------|-------------|-------------|-------------|----------------------|-------------|-------------|-------------|-------|-------------|------|-------------|--|---|---|---|--|-------------|---|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11                   | 26/10       | 25/9                       | 24/8        | 23/7        | 22/6              | 21/5        | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                 | All Resets  |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |             | INT4IP<2:0>             |             | INT4IS                     | S<1:0>      | _           | —                 | -           |             | OC4IP<2:0>  |             | OC4IS       | 6<1:0>               | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |             | IC4IP<2:0>              |             | IC4IS                      | <1:0>       | _           | _                 | _           |             | T4IP<2:0>   |             | T4IS-       | <1:0>                | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |             | SPI1IP<2:0>             |             | SPI1IS                     | 6<1:0>      | _           | _                 | _           |             | OC5IP<2:0>  |             | OC5IS       | S<1:0>               | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |             | IC5IP<2:0>              |             | IC5IS                      | <1:0>       | -           |                   | _           |             | T5IP<2:0>   |             | T5IS-       | <1:0>                | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 | 31:16     | _     | _     | _     |             | AD1IP<2:0>              |             | AD1IS                      | S<1:0>      | _           | _                 | _           |             | CNIP<2:0>   |             | CNIS        | <1:0>                | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 10F0                        | IPC6                            |           |       |       |       |             |                         |             |                            |             |             |                   |             |             | U1IP<2:0>   |             | U1IS-       | <1:0>                |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |             | I2C1IP<2:0>             |             | I2C1IS<1:0> —              |             | I2C1IS<1:0> |                   | I2C1IS<1:0> |             | I2C1IS<1:0> |             | I2C1IS<1:0> |                      | I2C1IS<1:0> |             | I2C1IS<1:0> |       | I2C1IS<1:0> |      | I2C1IS<1:0> |  | — | — | — |  | SPI3IP<2:0> | • | SPI3IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |             |                         |             |                            |             |             | I2C3IP<2:0> I2C3I |             | S<1:0>      |             |             |             |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 |           | 6     |       |       |             | U3IP<2:0>               |             | U3IS                       | <1:0>       |             |                   |             |             |             |             |             |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |             | SPI2IP<2:0>             |             | SPI2IS<1:0>                |             | —           | —                 | —           | (           | CMP2IP<2:0  | >           | CMP2IS<1:0> |                      | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1100                        | 11 07                           |           |       |       |       |             | I2C4IP<2:0>             |             | I2C4IS<1:0>                |             |             |                   |             |             |             |             |             |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 | 15:0      | _     |       |       | (           | CMP1IP<2:0              | >           | CMP1I                      | S<1:0>      | _           | - <u> </u>        |             |             | PMPIS       | S<1:0>      | 0000        |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 | 31:16     | _     |       |       | RTCCIP<2:0> |                         | RTCCIP<2:0> |                            | RTCCIP<2:0> |             | RTCCIP<2:0>       |             | RTCCIP<2:0> |             | RTCCIS<1:0> |             | _                    |             | FSCMIP<2:0> |             | FSCMI | S<1:0>      | 0000 |             |  |   |   |   |  |             |   |        |        |      |

| 1110                        | IPC8                            |           |       |       |       |             |                         |             |                            |             |             |                   |             |             | U2IP<2:0>   |             | U2IS-       | <1:0>                |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |             | I2C2IP<2:0>             |             | 12C215                     | 6<1:0>      | —           | —                 | —           |             | SPI4IP<2:0> |             | SPI4IS      | S<1:0>               | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

|                             |                                 |           |       |       |       |             |                         |             |                            |             |             |                   |             |             | I2C5IP<2:0> |             | 12C515      | S<1:0>               |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |             | DMA3IP<2:0              |             | DMA3I                      | S<1:0>      | _           | — — DMA2IP<2:0>   |             | DMA2I       | S<1:0>      | 0000        |             |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |             | DMA1IP<2:0              |             | DMA1I                      |             | _           |                   |             |             | DMA0IP<2:0  |             | DMA0I       | S<1:0>               | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI          | MA7IP<2:0>              | (2)         | DMA7IS<1:0> <sup>(2)</sup> |             | —           | _                 | —           | D           | MA6IP<2:0>  | (2)         | DMA6IS      | <1:0> <sup>(2)</sup> | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI          | MA5IP<2:0>              | (2)         | DMA5IS<1:0> <sup>(2)</sup> |             | _           | _                 | —           | D           | MA4IP<2:0>  | (2)         | DMA4IS      | <1:0> <sup>(2)</sup> | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _           | _                       |             | _                          |             |             |                   | _           | _           | —           |             | —           |                      | 0000        |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |             | USBIP<2:0>              |             | USBIS                      | S<1:0>      | _           | _                 | —           | FCEIP<2:0>  |             | FCEIP<2:0>  |             | FCEIS                | <1:0>       | 0000        |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     | U5IP<2:0>   |                         | U5IP<2:0>   |                            | U5IP<2:0>   |             | <1:0>             | _           |             | -           | U6IP<2:0>   |             | U6IP<2:0>            |             | U6IP<2:0>   |             | U6IS- | <1:0>       | 0000 |             |  |   |   |   |  |             |   |        |        |      |

| 1150                        | IFUIZ                           | 15:0      | _     | -     |       |             | U4IP<2:0> U4IS<1:0> ETH |             | ETHIP<2:0>                 |             | ETHIS       | i<1:0>            | 0000        |             |             |             |             |                      |             |             |             |       |             |      |             |  |   |   |   |  |             |   |        |        |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|----------------------------|----------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                          |                            | _                 |                   | _                 | _                 | _                | —                |  |  |  |  |

| 22.16        | R/W-1                      | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        |                            | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-1                      | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup> |                            |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | S-0                        | S-0                        | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |  |

| 7.0          | CFORCE                     | CABORT                     | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | —                |  |  |  |  |

## REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

## bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   | _                 |                   |                   | _                | _                |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   | _                 |                   |                   | -                |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   |                   |                   | _                 |                   |                   | -                |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

### REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

### Legend:

bit 7

| •                 |                                                               |                      |                    |  |

|-------------------|---------------------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | e bit $W = Writable bit$ $U = Unimplemented bit, read as '0'$ |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                              | '0' = Bit is cleared | x = Bit is unknown |  |

### bit 31-8 Unimplemented: Read as '0'

**DPPULUP:** D+ Pull-Up Enable bit 1 = D+ data line pull-up resistor is enabled 0 = D+ data line pull-up resistor is disabled

### bit 6 **DMPULUP:** D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled0 = D- data line pull-up resistor is disabled

- bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

### bit 3 VBUSON: VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 **OTGEN:** OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

### bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 |                   | —                 | —                 |                   |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 | —                 | —                 | —                 | -                 | _                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 | _                 | —                 | —                 | —                 | -                 | _                | -                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7:0          |                   | ENDP              | Г<3:0>            |                   | DIR               | PPBI              | _                | _                |

## REGISTER 11-10: U1STAT: USB STATUS REGISTER

## Legend:

| 3                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 •

- 0001 = Endpoint 1

- 0000 = Endpoint 0

- bit 3 DIR: Last Buffer Descriptor Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 **PPBI:** Ping-Pong Buffer Descriptor Pointer Indicator bit

- 1 = The last transaction was to the Odd buffer descriptor bank

- 0 = The last transaction was to the Even buffer descriptor bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when U1IR<TRNIF> is active. Clearing the U1IR<TRNIF> bit advances the FIFO. Data in register is invalid when U1IR<TRNIF> = 0.

# 16.1 Control Registers

| ess                         |                                               |               |        |       |       |       |       |       |       | Bi      | ts      |      |      |      |        |      |            |      |              |

|-----------------------------|-----------------------------------------------|---------------|--------|-------|-------|-------|-------|-------|-------|---------|---------|------|------|------|--------|------|------------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name                              | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8    | 23/7    | 22/6 | 21/5 | 20/4 | 19/3   | 18/2 | 17/1       | 16/0 | All Resets   |

| 2000                        | IC1CON <sup>(1)</sup>                         | 31:16         |        | —     | —     | —     | _     | —     | _     | _       | _       | —    | —    | _    | —      | —    | _          | _    | 0000         |

| 2000                        |                                               | 15:0          | ON     | _     | SIDL  | _     | _     | _     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2010                        | IC1BUF                                        | 31:16         |        |       |       |       |       |       |       | IC1BUF  | ~31.0>  |      |      |      |        |      |            |      | xxxx         |

| 2010                        |                                               | 15:0          |        |       |       |       |       |       |       | 101201  |         |      |      | -    |        |      |            |      | xxxx         |

| 2200                        | IC2CON <sup>(1)</sup>                         | 31:16         |        | _     | —     | —     | _     | _     | —     | _       | _       | _    | _    | —    | —      |      | —          | —    | 0000         |

| 2200                        | .0200.1                                       | 15:0          | ON     | —     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2210                        | IC2BUF                                        | 31:16         |        |       |       |       |       |       |       | IC2BUF  | <31:0>  |      |      |      |        |      |            |      | xxxx         |

|                             |                                               | 15:0          |        |       | -     |       |       |       |       |         |         |      |      |      | -      |      |            |      | xxxx         |

| 2400                        | IC3CON <sup>(1)</sup>                         | 31:16         | -      | _     | —     | _     | _     | —     | _     | _       | -       | -    | —    | —    | —      |      | -          |      | 0000         |

|                             |                                               | 15:0          | ON     | —     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2410                        | IC3BUF                                        | 31:16         |        |       |       |       |       |       |       | IC3BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                                               | 15:0          | XX     |       |       |       |       |       |       |         |         | XXXX |      |      |        |      |            |      |              |

| 2600                        | IC4CON <sup>(1)</sup>                         | 31:16         | -      |       | -     | _     |       |       | -     | -       | -       | -    |      | -    |        | —    | -          | _    | 0000         |

|                             |                                               | 15:0          | ON     | _     | SIDL  | —     | —     | —     | FEDGE | C32     | ICTMR   | ICI< | 1:0> | ICOV | ICBNE  |      | ICM<2:0>   |      | 0000         |

| 2610                        | IC4BUF                                        | 31:16<br>15:0 |        |       |       |       |       |       |       | IC4BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             |                                               | 31:16         |        | _     | _     | _     | _     |       | _     | _       | _       | _    |      |      | _      |      | _          | _    | xxxx<br>0000 |

| 2800                        | IC5CON <sup>(1)</sup>                         | 15:0          | ON     | _     |       | _     |       |       | FEDGE | <br>C32 | ICTMR   | ICI< |      | ICOV | ICBNE  |      | ICM<2:0>   |      |              |

|                             |                                               | 31:16         | UN     |       | SIDL  | —     | _     |       | FEDGE | 632     | ICTIVIK |      | 1.0> | 1000 | ICDINE | l    | 10101<2.0> |      | 0000         |

| 2810                        | IC5BUF                                        |               |        |       |       |       |       |       |       | IC5BUF  | <31:0>  |      |      |      |        |      |            |      | XXXX         |

|                             | <b>ل</b> ــــــــــــــــــــــــــــــــــــ | 15.0          | 15:0 x |       |       |       |       |       |       |         |         |      | XXXX |      |        |      |            |      |              |

# TABLE 16-1: INPUT CAPTURE 1-INPUT CAPTURE 5 REGISTER MAP

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

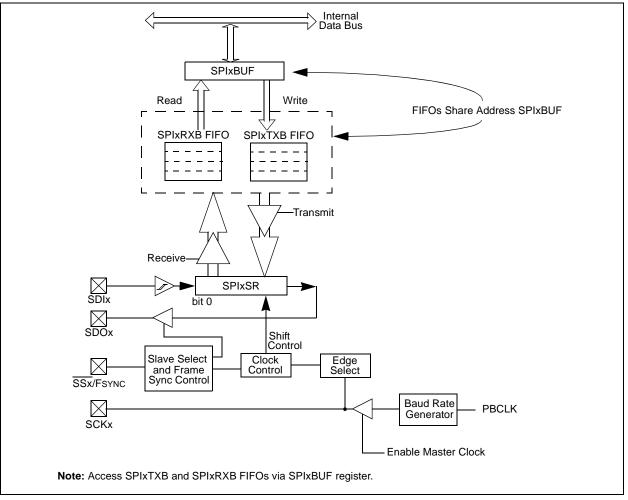

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

## REGISTER 20-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

- bit 5 **ABAUD:** Auto-Baud Enable bit 1 = Enable baud rate measurement on the next character – requires reception of Sync character (0x55);

- cleared by hardware upon completion 0 = Baud rate measurement disabled or completed

- bit 4 **RXINV:** Receive Polarity Inversion bit

- 1 = UxRX Idle state is '0'

- 0 = UxRX Idle state is '1'

- bit 3 BRGH: High Baud Rate Enable bit

- 1 = High-Speed mode 4x baud clock enabled

- 0 = Standard Speed mode 16x baud clock enabled

- bit 2-1 **PDSEL<1:0>:** Parity and Data Selection bits

- 11 = 9-bit data, no parity

- 10 = 8-bit data, odd parity

- 01 = 8-bit data, even parity

- 00 = 8-bit data, no parity

- bit 0 STSEL: Stop Selection bit

- 1 = 2 Stop bits

- 0 = 1 Stop bit

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | PTEN14            | _                 | —                 | _                 |                   | PTEN<10:8>       |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |

## REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

- bit 31-15 **Unimplemented:** Read as '0'

- bit 15-14 **PTEN14:** PMCS1 Strobe Enable bits

- 1 = PMA14 functions as either PMA14 or PMCS1<sup>(1)</sup>

- 0 = PMA14 functions as port I/O

- bit 13-11 Unimplemented: Read as '0'

- bit 10-2 PTEN<10:2>: PMP Address Port Enable bits

- 1 = PMA<10:2> function as PMP address lines

- 0 = PMA<10:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- **Note 1:** The use of this pin as PMA14 or CS1 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

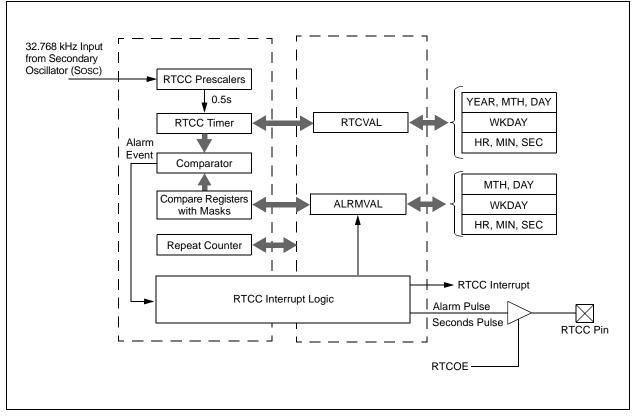

# 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. A simplified block diagram of the RTCC module is illustrated in Figure 22-1. Key features of the RTCC module include:

- Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- Alarm repeat with decrementing counter

- Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

## FIGURE 22-1: RTCC BLOCK DIAGRAM

## REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit<sup>(4)</sup>

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read. If the register is read twice and results in the same data, the data can be assumed to be valid.

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled (clock presented onto an I/O)

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- 4: The RTCWREN bit can only be set when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is only reset on a Power-on Reset (POR).

|              |                          | -                    | -                  |                         |                             |                   |                  |                  |  |  |

|--------------|--------------------------|----------------------|--------------------|-------------------------|-----------------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | U-0                      | U-0                  | U-0                | U-0                     | U-0                         | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                        | —                    | —                  | —                       | _                           | —                 | _                | —                |  |  |

| 00.40        | U-0                      | U-0                  | U-0                | U-0                     | U-0                         | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                        |                      | —                  | —                       | —                           | _                 | _                | —                |  |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0                       | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | ) AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0                       | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                         |                             |                   |                  |                  |  |  |

### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 **CHIME:** Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(3)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read.

The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

1111 = Reserved

- 1010 = Reserved

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half-second

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0 > = 0.0 and CHIME = 0.

- **2:** This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is only reset on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | —                 | _                 |                   | —                 | —                 | —                | —                |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH             | 01<3:0>          | R/W-x            |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   | DAY01<3:0>        |                   |                  |                  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   | _                 | WDAY01<3:0>       |                   |                   |                   |                  |                  |  |  |  |