Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 6:PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

# 64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

#### PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

|       | 64                                                        | 1                  |                                               |

|-------|-----------------------------------------------------------|--------------------|-----------------------------------------------|

|       |                                                           | QFN <sup>(3)</sup> | 64<br>TQFP                                    |

| Pin # | Full Pin Name                                             | Pin #              | Full Pin Name                                 |

| 1     | ETXEN/PMD5/RE5                                            | 33                 | USBID/RF3                                     |

| 2     | ETXD0/PMD6/RE6                                            | 34                 | VBUS                                          |

| 3     | ETXD1/PMD7/RE7                                            | 35                 | VUSB3V3                                       |

| 4     | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              | 36                 | D-/RG3                                        |

| 5     | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               | 37                 | D+/RG2                                        |

| 6     | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              | 38                 | Vdd                                           |

| 7     | MCLR                                                      | 39                 | OSC1/CLKI/RC12                                |

| 8     | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              | 40                 | OSC2/CLKO/RC15                                |

| 9     | Vss                                                       | 41                 | Vss                                           |

| 10    | Vdd                                                       | 42                 | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |

| 11    | AN5/C1IN+/VBUSON/CN7/RB5                                  | 43                 | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |

| 12    | AN4/C1IN-/CN6/RB4                                         | 44                 | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |

| 13    | AN3/C2IN+/CN5/RB3                                         | 45                 | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |

| 14    | AN2/C2IN-/CN4/RB2                                         | 46                 | OC1/INT0/RD0                                  |

| 15    | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            | 47                 | SOSCI/CN1/RC13                                |

| 16    | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       | 48                 | SOSCO/T1CK/CN0/RC14                           |

| 17    | PGEC2/AN6/OCFA/RB6                                        | 49                 | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |

| 18    | PGED2/AN7/RB7                                             | 50                 | SDA3/SDI3/U1RX/OC3/RD2                        |

| 19    | AVdd                                                      | 51                 | SCL3/SDO3/U1TX/OC4/RD3                        |

| 20    | AVss                                                      | 52                 | OC5/IC5/PMWR/CN13/RD4                         |

| 21    | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         | 53                 | PMRD/CN14/RD5                                 |

| 22    | AN9/C2OUT/PMA7/RB9                                        | 54                 | AETXEN/ETXERR/CN15/RD6                        |

| 23    | TMS/AN10/CVREFOUT/PMA13/RB10                              | 55                 | ETXCLK/AERXERR/CN16/RD7                       |

| 24    | TDO/AN11/PMA12/RB11                                       | 56                 | VCAP                                          |

| 25    | Vss                                                       | 57                 | VDD                                           |

| 26    | Vdd                                                       | 58                 | C1RX/AETXD1/ERXD3/RF0                         |

| 27    | TCK/AN12/PMA11/RB12                                       | 59                 | C1TX/AETXD0/ERXD2/RF1                         |

| 28    | TDI/AN13/PMA10/RB13                                       | 60                 | ERXD1/PMD0/RE0                                |

| 29    | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 | 61                 | ERXD0/PMD1/RE1                                |

| 30    | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 | 62                 | ERXDV/ECRSDV/PMD2/RE2                         |

| 31    | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        | 63                 | ERXCLK/EREFCLKPMD3/RE3                        |

| 32    | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        | 64                 | ERXERR/PMD4/RE4                               |

| Note  | 1: Shaded pins are 5V tolerant.                           |                    |                                               |

**Note 1:** Shaded pins are 5V tolerant.

2: This pin is not available on PIC32MX765F128H devices.

3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

| Pin Number <sup>(1)</sup> |                 |                                 |                                                                                                             |                                                                                              | Buffer                                                                                                 |                                                                                                                                                                                                                         |  |  |

|---------------------------|-----------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 64-Pin<br>N/TQFP          | 100-Pin<br>TQFP | 121-Pin<br>TFBGA                | 124-pin<br>VTLA                                                                                             | Pin<br>Type                                                                                  | Винег<br>Туре                                                                                          | Description                                                                                                                                                                                                             |  |  |

| 46                        | 72              | D9                              | B39                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTD is a bidirectional I/O port                                                                                                                                                                                       |  |  |

| 49                        | 76              | A11                             | A52                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 50                        | 77              | A10                             | B42                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 51                        | 78              | B9                              | A53                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 52                        | 81              | C8                              | B44                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 53                        | 82              | B8                              | A55                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 54                        | 83              | D7                              | B45                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 55                        | 84              | C7                              | A56                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 42                        | 68              | E9                              | B37                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 43                        | 69              | E10                             | A45                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 44                        | 70              | D11                             | B38                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 45                        | 71              | C11                             | A46                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 79              | A9                              | B43                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 80              | D8                              | A54                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 47              | L9                              | B26                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 48              | K9                              | A31                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 60                        | 93              | A4                              | B52                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTE is a bidirectional I/O port                                                                                                                                                                                       |  |  |

| 61                        | 94              | B4                              | A64                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 62                        | 98              | B3                              | A66                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 63                        | 99              | A2                              | B56                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 64                        | 100             | A1                              | A67                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 1                         | 3               | D3                              | B2                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 2                         | 4               | C1                              | A4                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 3                         | 5               | D2                              | B3                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 18              | G1                              | A11                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 19              | G2                              | B10                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 58                        | 87              | B6                              | B49                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTF is a bidirectional I/O port                                                                                                                                                                                       |  |  |

| 59                        | 88              | A6                              | A60                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 52              | K11                             | A36                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 33                        | 51              | K10                             | A35                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 31                        | 49              | L10                             | B27                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| 32                        | 50              | L11                             | A32                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 53              | J10                             | B29                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 40              | K6                              | A27                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| _                         | 39              | L6                              | B22                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |  |

| <br><br>S = C<br>Schn     | nitt 1          | 53<br>40<br>39<br>CMOS compatib | 53     J10       40     K6       39     L6       CMOS compatible input or contribut Trigger input with CMOS | 53J10B2940K6A2739L6B22CMOS compatible input or output<br>nitt Trigger input with CMOS levels | 53J10B29I/O40K6A27I/O39L6B22I/OCMOS compatible input or output<br>nitt Trigger input with CMOS levelsA | 53     J10     B29     I/O     ST       40     K6     A27     I/O     ST       39     L6     B22     I/O     ST       CMOS compatible input or output nitt Trigger input with CMOS levels     Analog = A     O = Output |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

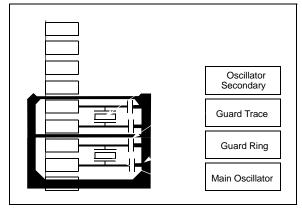

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# TABLE 7-5: INTERRUPT REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L PIC32MX575F512L AND PIC32MX575F256L DEVICES (CONTINUED)

| ess                         |                                 | â         |       | Bits  |       |       |                            |             |                                                                   |                      |                            |        |        |                       |             |             |             |                       |            |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------------------|-------------|-------------------------------------------------------------------|----------------------|----------------------------|--------|--------|-----------------------|-------------|-------------|-------------|-----------------------|------------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                      | 26/10       | 25/9                                                              | 24/8                 | 23/7                       | 22/6   | 21/5   | 20/4                  | 19/3        | 18/2        | 17/1        | 16/0                  | All Resets |        |      |

| 10D0                        | IPC4                            | 31:16     | —     | _     | —     |       | INT4IP<2:0>                | <b>`</b>    | INT4IS                                                            | S<1:0>               |                            | —      | —      |                       | OC4IP<2:0>  |             | OC4I        | S<1:0>                | 0000       |        |      |

| 1000                        | IFC4                            | 15:0      | -     |       | _     |       | IC4IP<2:0>                 |             | IC4IS                                                             | <1:0>                |                            | _      | _      |                       | T4IP<2:0>   |             | T4IS        | <1:0>                 | 0000       |        |      |

| 4050                        | IDOF                            | 31:16     | Ι     | _     | -     |       | SPI1IP<2:0>                | <b>&gt;</b> | SPI1IS                                                            | S<1:0>               | _                          | _      | -      |                       | OC5IP<2:0>  |             | OC5I        | S<1:0>                | 0000       |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |       | IC5IP<2:0>                 |             | IC5IS                                                             | <1:0>                |                            | _      | _      |                       | T5IP<2:0>   |             | T5IS        | <1:0>                 | 0000       |        |      |

|                             |                                 | 31:16     | _     | _     | _     |       | AD1IP<2:0>                 |             | AD1IS                                                             | <1:0>                |                            | _      | _      |                       | CNIP<2:0>   |             | CNIS        | <1:0>                 | 0000       |        |      |

| 10F0                        | IPC6                            |           |       |       |       |       |                            |             |                                                                   |                      |                            |        |        |                       | U1IP<2:0>   |             | U1IS        | <1:0>                 |            |        |      |

| 10F0                        | IPC6                            | 15:0      | _     |       | _     |       | I2C1IP<2:0>                | •           | 12C115                                                            | S<1:0>               | _                          | _      | _      | SPI3IP<2:0>           |             | SPI3I       | S<1:0>      | 0000                  |            |        |      |

|                             |                                 |           |       |       |       |       |                            |             |                                                                   |                      |                            |        |        | I2C3IP<2:0>           |             | I2C3IS<1:0> |             |                       |            |        |      |

|                             |                                 |           |       |       |       |       | U3IP<2:0>                  |             | U3IS-                                                             | <1:0>                |                            |        |        |                       |             |             |             |                       |            |        |      |

| 1100                        | IPC7                            | 31:16     | _     | —     | —     |       | SPI2IP<2:0>                | <b>`</b>    | SPI2IS                                                            | S<1:0>               | —                          | _      | —      |                       | CMP2IP<2:0  | >           | CMP2IS<1:0> | 0000                  |            |        |      |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0>                | •           | 12C415                                                            | S<1:0>               |                            |        |        |                       |             |             |             |                       |            |        |      |

|                             |                                 | 15:0      | —     | —     | —     | (     | CMP1IP<2:0                 | >           | CMP1                                                              | S<1:0>               | _                          | _      | —      | PMPIP<2:0>            |             | PMPI        | S<1:0>      | 0000                  |            |        |      |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0>                |             | RTCCIP<2:0>                                                       |                      | RTCCI                      | S<1:0> | _      | _                     | —           |             | FSCMIP<2:0  | >                     | FSCM       | S<1:0> | 0000 |

| 1110                        | IPC8                            |           |       |       |       |       |                            |             |                                                                   |                      |                            |        |        |                       |             |             | U2IP<2:0>   |                       | U2IS       | <1:0>  |      |

| 1110                        | 11 00                           | 15:0      | -     | —     | -     |       | I2C2IP<2:0>                |             | 12C215                                                            | S<1:0>               | —                          | —      | —      |                       | SPI4IP<2:0> |             | SPI4I       | S<1:0>                | 0000       |        |      |

|                             |                                 |           |       |       |       |       |                            |             |                                                                   |                      |                            |        |        |                       | I2C5IP<2:0> |             | 12C51       | S<1:0>                |            |        |      |

| 1120                        | IPC9                            | 31:16     | -     |       | —     | [     | DMA3IP<2:0                 | >           | DMA3I                                                             | S<1:0>               |                            | —      | —      |                       | DMA2IP<2:0  | >           | DMA2        | S<1:0>                | 0000       |        |      |

| 1120                        | 11 00                           | 15:0      | —     | _     | —     |       | DMA1IP<2:0                 |             | DMA1                                                              |                      |                            |        | —      |                       | DMA0IP<2:0  |             |             | S<1:0>                | 0000       |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |       | DMA7IP<2:0> <sup>(2)</sup> |             | DMA7IP<2:0> <sup>(2)</sup> DMA7IS<1:0> <sup>(2)</sup> DMA6IP<2:0: |                      | DMA6IP<2:0> <sup>(2)</sup> |        | DMA6IS | 6<1:0> <sup>(2)</sup> | 0000        |             |             |                       |            |        |      |

| 1130                        | 1 010                           | 15:0      | _     | —     | —     | D     | DMA5IP<2:0> <sup>(2)</sup> |             | DMA5IS                                                            | <1:0> <sup>(2)</sup> | _                          | —      | —      | D                     | MA4IP<2:0>  | (2)         | DMA4IS      | S<1:0> <sup>(2)</sup> | 0000       |        |      |

| 1140                        | IPC11                           | 31:16     | Ι     |       | _     | _     |                            |             |                                                                   |                      | _                          | _      | —      | —                     | _           | CAN1IP<2:0> |             | CAN1                  | S<1:0>     | 0000   |      |

| 1140                        | 1011                            | 15:0      | _     | _     | —     |       | USBIP<2:0>                 |             | USBIS                                                             | 5<1:0>               | —                          | —      | —      | FCEIP<2:0>            |             | FCEIS       | S<1:0>      | 0000                  |            |        |      |

| 1150                        | IPC12                           | 31:16     | -     |       | _     |       | U5IP<2:0>                  |             | U5IS-                                                             | <1:0>                | —                          | —      | _      |                       | U6IP<2:0>   |             | U6IS        | <1:0>                 | 0000       |        |      |

| 1150                        | 11 012                          | 15:0      | -     |       | _     |       | U4IP<2:0>                  |             | U4IS-                                                             | <1:0>                | _                          | _      | _      | _                     | —           |             | —           | _                     | 0000       |        |      |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX534/564 devices.

3: This register does not have associated CLR, SET, and INV registers.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2   | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | _                   | _                | —                |

| 22:46        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | _                   | —                | —                |

| 45.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0                 | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | _                 | _                   | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0            | R/W-0            |

| 7:0          | —                 | —                 |                   |                   | TUN<              | 5:0> <sup>(1)</sup> |                  |                  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| J. J.             |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

| bit 5-0 | <b>TUN&lt;5:0&gt;:</b> FRC Oscillator Tuning bits <sup>(1)</sup><br>100000 = Center frequency -12.5% for PIC32MX575/595/675/695/775/795 devices<br>100000 = Center frequency -1.5% for PIC32MX534/564/664/764 devices<br>100001 = |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 111111 =<br>000000 = Center frequency; Oscillator runs at nominal frequency (8 MHz)<br>000001 =                                                                                                                                   |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 011110 =<br>011111 = Center frequency +12.5% for PIC32MX575/595/675/695/775/795 devices<br>011111 = Center frequency +1.5% for PIC32MX534/564/664/764 devices                                                                     |

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the |

|-------|----------------------------------------------------------------------------------------------------------|

|       | "PIC32 Family Reference Manual" for details.                                                             |

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|--|

| 04.04        | U-0                   | U-0              |  |

| 31:24        |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |  |

| 22.10        | U-0                   | U-0              |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                     | —                |  |

| 15:8         | U-0                   | U-0              |  |

| 10.0         |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |  |

|              | R/W-0                 | R/W-0            |  |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup> |                  |  |

|              | DISEE             | DIVIXEE           | DIVIAEE           | DIVEE             | DENGEE            | URUIDEE           | EOFEE <sup>(2)</sup>  | PIDEE            |  |

#### REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                               |

|----------|------------------------------------------------------------------------------------------|

| bit 7    | BTSEE: Bit Stuff Error Interrupt Enable bit                                              |

|          | <ul><li>1 = BTSEF interrupt is enabled</li><li>0 = BTSEF interrupt is disabled</li></ul> |

| bit 6    | BMXEE: Bus Matrix Error Interrupt Enable bit                                             |

|          | 1 = BMXEF interrupt is enabled                                                           |

|          | 0 = BMXEF interrupt is disabled                                                          |

| bit 5    | DMAEE: DMA Error Interrupt Enable bit                                                    |

|          | <ul><li>1 = DMAEF interrupt is enabled</li><li>0 = DMAEF interrupt is disabled</li></ul> |

| bit 4    | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                                |

|          | 1 = BTOEF interrupt is enabled                                                           |

- 0 = BTOEF interrupt is disabled

- bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup> bit 1

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

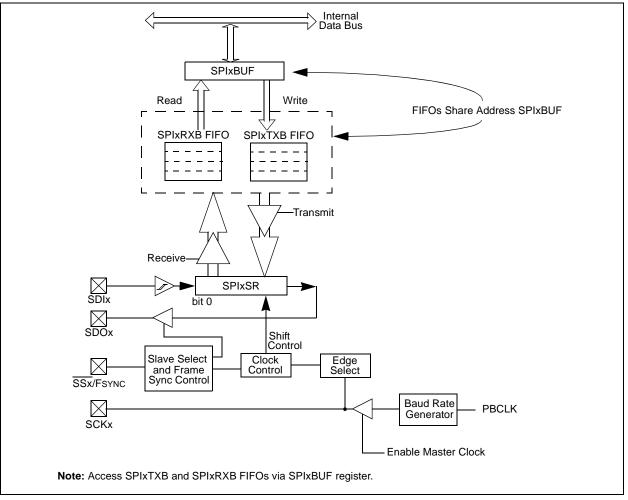

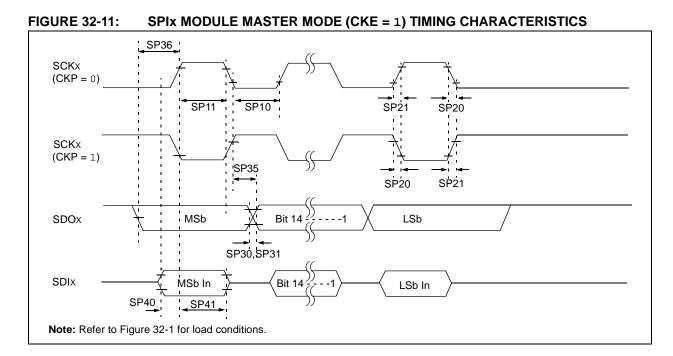

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN             | FRMSYNC           | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | >                     |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | _                 | —                 | _                 | —                 | —                 |                   | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN              | CKP               | MSTEN             | _                 | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

#### REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| F  | R = Readable bit | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|----|------------------|------------------|---------------------------|--------------------|

| -1 | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31 | FRMEN: Framed SPI Support | bit |

|--------|---------------------------|-----|

|        |                           | Dir |

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on SSx pin bit (only Framed SPI mode) 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (only Framed SPI mode)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed Sync mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23-18 Unimplemented: Read as '0'

- bit 17 SPIFE: Frame Sync Pulse Edge Select bit (only Framed SPI mode)

- 1 = Frame synchronization pulse coincides with the first bit clock

- 0 = Frame synchronization pulse precedes the first bit clock

- bit 16 ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup>

- 1 = Enhanced Buffer mode is enabled

- 0 = Enhanced Buffer mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

# PIC32MX5XX/6XX/7XX

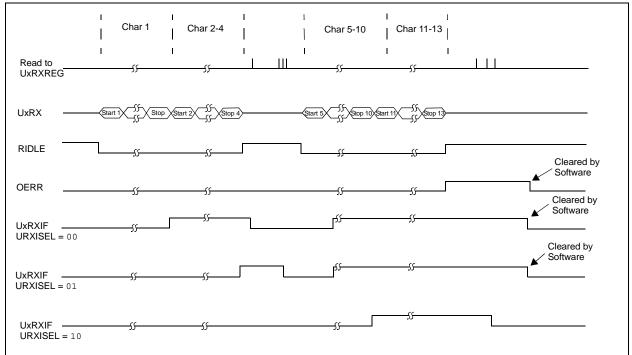

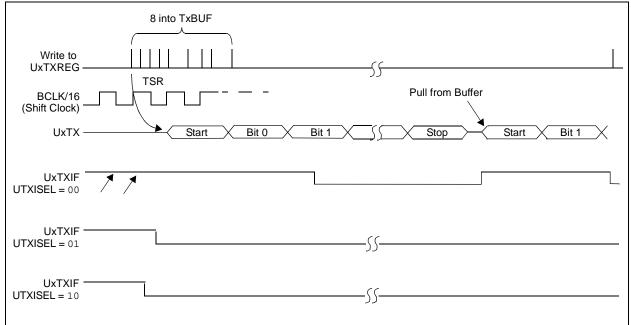

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

### FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        |                   | _                   | _                  |                   | _                   |                   |                  | —                |

| 00.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | -                   | _                  | -                 |                     | _                 | —                | —                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                   | SIDL               | ADRML             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

#### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS2 and PMCS1 function as Chip Select

- 01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

- 00 = PMCS2 and PMCS1 function as address bits 15 and  $14^{(2)}$

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 Unimplemented: Read as '0'