Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              |                                                                                 |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

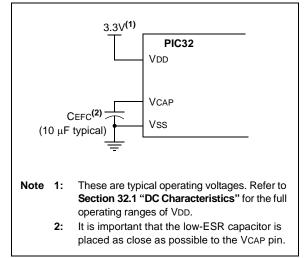

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

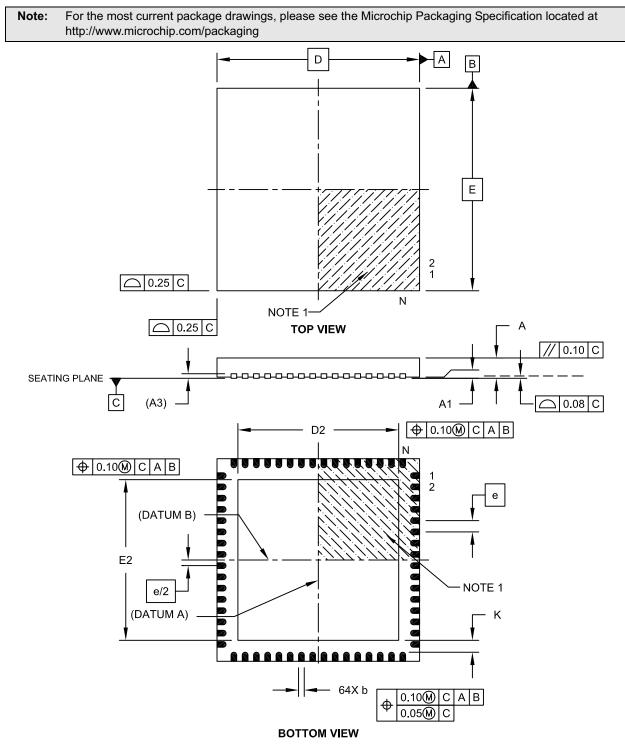

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064lt-i-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 5: PIN NAMES FOR 64-PIN USB AND ETHERNET DEVICES

| IABL  | E 5: PIN NAMES FOR 64-PIN USB AND E                                                            | INCKN                   |                                               |  |  |  |  |  |

|-------|------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------|--|--|--|--|--|

| 64    | 64-PIN QFN <sup>(2)</sup> AND TQFP (TOP VIEW)                                                  |                         |                                               |  |  |  |  |  |

|       | PIC32MX664F064H<br>PIC32MX664F128H<br>PIC32MX675F256H<br>PIC32MX675F512H<br>PIC32MX695F512H 64 | 1                       |                                               |  |  |  |  |  |

|       | 04                                                                                             | 1                       |                                               |  |  |  |  |  |

|       | QFN                                                                                            | <b>1</b> <sup>(2)</sup> | <sup>64</sup> <b>TQFP</b>                     |  |  |  |  |  |

| Pin # | Full Pin Name                                                                                  | Pin #                   | Full Pin Name                                 |  |  |  |  |  |

| 1     | ETXEN/PMD5/RE5                                                                                 | 33                      | USBID/RF3                                     |  |  |  |  |  |

| 2     | ETXD0/PMD6/RE6                                                                                 | 34                      | VBUS                                          |  |  |  |  |  |

| 3     | ETXD1/PMD7/RE7                                                                                 | 35                      | VUSB3V3                                       |  |  |  |  |  |

| 4     | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                                                                   | 36                      | D-/RG3                                        |  |  |  |  |  |

| 5     | SDA4/SDI2/U3RX/PMA4/CN9/RG7                                                                    | 37                      | D+/RG2                                        |  |  |  |  |  |

| 6     | SCL4/SDO2/U3TX/PMA3/CN10/RG8                                                                   | 38                      | Vdd                                           |  |  |  |  |  |

| 7     | MCLR                                                                                           | 39                      | OSC1/CLKI/RC12                                |  |  |  |  |  |

| 8     | SS2/U6RX/U3CTS/PMA2/CN11/RG9                                                                   | 40                      | OSC2/CLKO/RC15                                |  |  |  |  |  |

| 9     | Vss                                                                                            | 41                      | Vss                                           |  |  |  |  |  |

| 10    | Vdd                                                                                            | 42                      | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |  |  |  |  |  |

| 11    | AN5/C1IN+/Vbuson/CN7/RB5                                                                       | 43                      | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |  |  |  |  |  |

| 12    | AN4/C1IN-/CN6/RB4                                                                              | 44                      | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |  |  |  |  |  |

| 13    | AN3/C2IN+/CN5/RB3                                                                              | 45                      | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |  |  |  |  |  |

| 14    | AN2/C2IN-/CN4/RB2                                                                              | 46                      | OC1/INT0/RD0                                  |  |  |  |  |  |

| 15    | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                                                                 | 47                      | SOSCI/CN1/RC13                                |  |  |  |  |  |

| 16    | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                                                            | 48                      | SOSCO/T1CK/CN0/RC14                           |  |  |  |  |  |

| 17    | PGEC2/AN6/OCFA/RB6                                                                             | 49                      | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |  |  |  |  |  |

| 18    | PGED2/AN7/RB7                                                                                  | 50                      | SDA3/SDI3/U1RX/OC3/RD2                        |  |  |  |  |  |

| 19    | AVdd                                                                                           | 51                      | SCL3/SDO3/U1TX/OC4/RD3                        |  |  |  |  |  |

| 20    | AVss                                                                                           | 52                      | OC5/IC5/PMWR/CN13/RD4                         |  |  |  |  |  |

| 21    | AN8/SS4/U5RX/U2CTS/C1OUT/RB8                                                                   | 53                      | PMRD/CN14/RD5                                 |  |  |  |  |  |

| 22    | AN9/C2OUT/PMA7/RB9                                                                             | 54                      | AETXEN/ETXERR/CN15/RD6                        |  |  |  |  |  |

| 23    | TMS/AN10/CVREFOUT/PMA13/RB10                                                                   | 55                      | ETXCLK/AERXERR/CN16/RD7                       |  |  |  |  |  |

| 24    | TDO/AN11/PMA12/RB11                                                                            | 56                      | VCAP                                          |  |  |  |  |  |

| 25    | Vss                                                                                            | 57                      | VDD                                           |  |  |  |  |  |

| 26    | Vdd                                                                                            | 58                      | AETXD1/ERXD3/RF0                              |  |  |  |  |  |

| 27    | TCK/AN12/PMA11/RB12                                                                            | 59                      | AETXD0/ERXD2/RF1                              |  |  |  |  |  |

| 28    | TDI/AN13/PMA10/RB13                                                                            | 60                      | ERXD1/PMD0/RE0                                |  |  |  |  |  |

| 29    | AN14/SCK4/U5TX/U2RTSU2RTS/PMALH/PMA1/RB14                                                      | 61                      | ERXD0/PMD1/RE1                                |  |  |  |  |  |

| 30    | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                                                      | 62                      | ERXDV/ECRSDV/PMD2/RE2                         |  |  |  |  |  |

| 31    | SDA5/SDI4/U2RX/PMA9/CN17/RF4                                                                   | 63                      | ERXCLK/EREFCLK/PMD3/RE3                       |  |  |  |  |  |

| 32    | SCL5/SDO4/U2TX/PMA8/CN18/RF5                                                                   | 64                      | ERXERR/PMD4/RE4                               |  |  |  |  |  |

|       |                                                                                                |                         |                                               |  |  |  |  |  |

Note 1: Shaded pins are 5V tolerant.

2: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

PIC32MX795F512L

#### **TABLE 12:** PIN NAMES FOR USB, ETHERNET, AND CAN DEVICES

| 121-PIN TFBGA (BOTTOM VIEW)                           |    | L11 |

|-------------------------------------------------------|----|-----|

| PIC32MX764F128L<br>PIC32MX775F256L<br>PIC32MX775F512L | L1 | A11 |

A1

Note: The TFBGA package skips from row "H" to row "J" and has no "I" row.

| Pin #      | Full Pin Name                                | Pin # | Full Pin Name                                                |

|------------|----------------------------------------------|-------|--------------------------------------------------------------|

| A1         | PMD4/RE4                                     | E2    | T4CK/AC2RX <sup>(1)</sup> /RC3                               |

| A2         | PMD3/RE3                                     | E3    | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                    | E4    | T3CK/AC2TX <sup>(1)</sup> /RC2                               |

| A4         | PMD0/RE0                                     | E5    | Vdd                                                          |

| A5         | C2RX <sup>(1)</sup> /PMD8/RG0                | E6    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1                         |

| A6         | C1TX/ETXD0/PMD10/RF1                         | E7    | Vss                                                          |

| A7         | VDD                                          | E8    | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                          | E9    | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                         | E10   | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                      | E11   | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                      | F1    | MCLR                                                         |

| B1         | No Connect (NC)                              | F2    | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8     |

| B2         | AERXERR/RG15                                 | F3    | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                     | F4    | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                     | F5    | Vss                                                          |

| B5         | TRD3/RA7                                     | F6    | No Connect (NC)                                              |

| B6         | C1RX/ETXD1/PMD11/RF0                         | F7    | No Connect (NC)                                              |

| B7         | VCAP                                         | F8    | Vdd                                                          |

| B8         | PMRD/CN14/RD5                                | F9    | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                      | F10   | Vss                                                          |

| B10        | Vss                                          | F11   | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                          | G1    | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                     | G2    | AERXD1/INT2/RE9                                              |

| C2         | VDD                                          | G3    | TMS/RA0                                                      |

| C3         | TRD1/RG12                                    | G4    | No Connect (NC)                                              |

| C4         | TRD2/RG14                                    | G5    | Vdd                                                          |

| C5         | TRCLK/RA6                                    | G6    | Vss                                                          |

| C6         | No Connect (NC)                              | G7    | Vss                                                          |

| C7         | ETXCLK/PMD15/CN16/RD7                        | G8    | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                            | G9    | TDO/RA5                                                      |

| C9         | VDD                                          | G10   | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                               | G11   | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11              | H1    | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                     | H2    | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                     | H3    | Vss                                                          |

| D3         | PMD5/RE5                                     | H4    | VDD                                                          |

| D4         | Vss                                          | H5    | No Connect (NC)                                              |

| D5         | Vss                                          | H6    | VDD                                                          |

| D6         |                                              | H7    | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                         | H8    | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                        | H9    | VUSB3V3                                                      |

| D9         | SD01/0C1/INT0/RD0                            | H10   | D+/RG2                                                       |

| D10        | No Connect (NC)<br>SCK1/IC3/PMCS2/PMA15/RD10 | H11   | SCL2/RA2<br>AN3/C2IN+/CN5/RB3                                |

| D11        |                                              | J1    |                                                              |

| E1<br>Note | 1: This pin is not available on PIC32MX764   | J2    | AN2/C2IN-/CN4/RB2                                            |

2: Shaded pins are 5V tolerant.

## **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | —                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | —                 | —                 | _                 | E                 | 3MXARB<2:0       | >                |

# REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

# bit 31-21 **Unimplemented:** Read as '0'

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          |                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                     |

|          | 011 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | 010 = Arbitration Mode 2<br>001 = Arbitration Mode 1 (default)                                                                                                                                                                        |

|          | 000 = Arbitration Mode 0                                                                                                                                                                                                              |

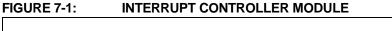

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHCSIZ            | /<7:0>            |                   |                  |                  |  |

#### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | lemented bit, read as '0' |  |  |

|-------------------|------------------|--------------------------|---------------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown        |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

## REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |  |

| Legend:           |                  |                                            |                    |

|-------------------|------------------|--------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | ble bit U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                       | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

## REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | —                 | —                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   | —                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | —                 | _                 | —                 | —                 | -                | —                |

| 7:0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7.0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |        |  |

|-------------------|-------------------------|------------------------------------|--------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |        |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared x = Bit is un | nknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

#### bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

- bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

#### bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

## REGISTER 11-12: U1ADDR: USB ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        | _                 | _                 | -                 |                   | _                 | -                 |                  | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | -                 |                   |                   |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 |                   |                   | _                 |                   |                  | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **LSPDEN:** Low-Speed Enable Indicator bit

- 1 = Next token command to be executed at low-speed

- 0 = Next token command to be executed at full-speed

- bit 6-0 DEVADDR<6:0>: 7-bit USB Device Address bits

#### REGISTER 11-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | -                 |                   | —                 |                   |                   |                  | -                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | -                 |                   | —                 |                   |                   |                  | -                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | -                 | _                 |                  | _                |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | .<7:0>            |                   |                  |                  |

| Legend:           |                  |                                                   |                    |  |

|-------------------|------------------|---------------------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | = Writable bit U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                              | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** 11-bit Frame Number Lower bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

NOTES:

## REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC S&H circuit is sampling

- 0 = The ADC S&H circuit is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC < 2:0 > = 000, writing '0' to this bit will end sampling and start conversion.

#### bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- Clearing this bit will not affect any operation in progress.

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | _                 | -                 | ABAT              | F                 | REQOP<2:0>       | >                |

| 22:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | OPMOD<2:0>        |                   |                   | CANCAP            | —                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | -                 | CANBUSY           | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 |                   |                   | DNCNT<4:0>        |                  |                  |

#### REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER

| Legend:           | HC = Hardware Clear | S = Settable bit                   |                    |  |

|-------------------|---------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0 |  |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------|--|

| 24.24        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0               | U-0                          | U-0              |  |

| 31:24        | _                       |                    | _                 | _                 | _                 | —                 | _                            | —                |  |

| 22:16        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0                        | R/W-0            |  |

| 23:16        | —                       | WAKFIL             | _                 | —                 | _                 | SEG               | SEG2PH<2:0> <sup>(1,4)</sup> |                  |  |

| 15.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            |  |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | 5                 | SEG1PH<2:0:       | >                 | Р                 | RSEG<2:0>                    |                  |  |

| 7:0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            |  |

|              | SJW<1:                  | 0> <sup>(3)</sup>  |                   | BRP<5:0>          |                   |                   |                              |                  |  |

## REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER

| Legend:           | HC = Hardware Clear | S = Settable bit         |                     |  |  |

|-------------------|---------------------|--------------------------|---------------------|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, I | ed bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared     | x = Bit is unknown  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

- bit 22 **WAKFIL:** CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

|           | Chimplemented. Read as 0                                                      |

|-----------|-------------------------------------------------------------------------------|

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | <b>SAM:</b> Sample of the CAN Bus Line bit <sup>(2)</sup>                     |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x Tq                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | $SJW \leq SEG2PH.$                                                            |

| 4:        | The Time Quanta per bit must be greater than 7 (that is, $TQBIT > 7$ ).       |

|           |                                                                               |

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN11           | MSEL11<1:0>       |                   | FSEL11<4:0>       |                   |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | FLTEN10           | MSEL10<1:0>       |                   | FSEL10<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN9            | MSEL              | 9<1:0>            |                   | F                 | SEL9<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN8            | MSEL              | 8<1:0>            | FSEL8<4:0>        |                   |                   |                  |                  |

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31    | FLTEN11: Filter 11 Enable bit                                                                                                                                                  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                |

| bit 30-29 | MSEL11<1:0>: Filter 11 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL11<4:0>: FIFO Selection bits                                                                                                                                               |

|           | <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                             |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                  |

| bit 23    | FLTEN10: Filter 10 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL10<1:0>: Filter 10 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 20-16 | FSEL10<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | ·<br>·                                                                                                                                                                         |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

|           | — · · · · · · · · · · · · · · · · · · ·                                                                                                                                        |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     |                   |                   |                   | PMM<              | 31:24>            |                   |                  |                  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10     | PMM<23:16>        |                   |                   |                   |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0      | PMM<15:8>         |                   |                   |                   |                   |                   |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           |                   |                   |                   | PMM               | <7:0>             |                   |                  |                  |

#### REGISTER 25-7: ETHPMM0: ETHERNET CONTROLLER PATTERN MATCH MASK 0 REGISTER

# Legend:

| 9                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-24 | PMM<31:24>: Pattern Match Mask 3 bits |

|-----------|---------------------------------------|

| hit 23-16 | PMM-23-16- Pattern Match Mask 2 hits  |

- bit 23-16 PMM<23:16>: Pattern Match Mask 2 bits

- bit 15-8 **PMM<15:8>:** Pattern Match Mask 1 bits

- bit 7-0 PMM<7:0>: Pattern Match Mask 0 bits

- Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

## REGISTER 25-8: ETHPMM1: ETHERNET CONTROLLER PATTERN MATCH MASK 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24     | PMM<63:56>        |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10     | PMM<55:48>        |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.6      | PMM<47:40>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0       |                   |                   |                   | PMM<              | 39:32>            |                   |                  |                  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | vit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

|                   |                  |                      |                    |

| bit 31-24 | PMM<63:56>: Pattern Match Mask 7 bits |

|-----------|---------------------------------------|

| bit 23-16 | PMM<55:48>: Pattern Match Mask 6 bits |

| bit 15-8  | PMM<47:40>: Pattern Match Mask 5 bits |

| bit 7-0   | PMM<39:32>: Pattern Match Mask 4 bits |

# Note 1: This register is only used for RX operations. 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 | _                 | _                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   |                   |                   | —                |                  |

| 15:8         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | HTEN              | MPEN              | _                 | NOTPM             | PMMODE<3:0>       |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **HTEN:** Enable Hash Table Filtering bit

- 1 = Enable Hash Table Filtering

- 0 = Disable Hash Table Filtering

- bit 14 **MPEN:** Magic Packet<sup>™</sup> Enable bit 1 = Enable Magic Packet Filtering 0 = Disable Magic Packet Filtering

- bit 13 Unimplemented: Read as '0'

- bit 12 **NOTPM:** Pattern Match Inversion bit

- 1 = The Pattern Match Checksum must not match for a successful Pattern Match to occur

- 0 = The Pattern Match Checksum must match for a successful Pattern Match to occur

This bit determines whether Pattern Match Checksum must match in order for a successful Pattern Match to occur.

- bit 11-8 PMMODE<3:0>: Pattern Match Mode bits

- 1001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Packet = Magic Packet)<sup>(1,3)</sup>