Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | ·                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064lt-v-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22:46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        |                   | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          | BMXPFMSZ<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

# Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = device has 64 KB Flash 0x00020000 = device has 128 KB Flash 0x00040000 = device has 256 KB Flash 0x00080000 = device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 31:24        |                   |                   |                   | BMXBOO            | TSZ<31:24>        |                   |                  |                  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |

| 7:0          | BMXBOOTSZ<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = device has 12 KB boot Flash

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                       | _                 | _                 | _                | —                |  |  |

| 22:46        | U-0               | R-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                       | _                 | _                 | —                | —                |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | —                 | —                 | _                       | _                 | _                 | _                | —                |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | —                 | —                 |                   | TUN<5:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

# Legend:

| J. J.             |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

| bit 5-0 | <b>TUN&lt;5:0&gt;:</b> FRC Oscillator Tuning bits <sup>(1)</sup><br>100000 = Center frequency -12.5% for PIC32MX575/595/675/695/775/795 devices<br>100000 = Center frequency -1.5% for PIC32MX534/564/664/764 devices<br>100001 = |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 111111 =<br>000000 = Center frequency; Oscillator runs at nominal frequency (8 MHz)<br>000001 =                                                                                                                                   |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 011110 =<br>011111 = Center frequency +12.5% for PIC32MX575/595/675/695/775/795 devices<br>011111 = Center frequency +1.5% for PIC32MX534/564/664/764 devices                                                                     |

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the |

|-------|----------------------------------------------------------------------------------------------------------|

|       | "PIC32 Family Reference Manual" for details.                                                             |

x = Bit is unknown

|              |                   |                   | •••••••           |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   |                   |                   | CHEHIT<           | :31:24>           |                   |                  |                  |  |  |

| 00:40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEHIT<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEHIT<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | CHEHIT<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 1            |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Rea      | dable bit         |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ad as '0'        |                  |  |  |

#### **REGISTER 9-10: CHEHIT: CACHE HIT STATISTICS REGISTER**

#### bit 31-0 CHEHIT<31:0>: Cache Hit Count bits

- - - - -

-n = Value at POR

Incremented each time the processor issues an instruction fetch or load that hits the prefetch cache from a cacheable region. Non-cacheable accesses do not modify this value.

-----

'0' = Bit is cleared

| REGIST | ER 9-11: 0 | CHEMIS: CA | CHE MISS | STATISTICS | 6 REGISTEI | ĸ |

|--------|------------|------------|----------|------------|------------|---|

|        |            |            |          |            |            |   |

'1' = Bit is set

| Bit<br>Range         | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|----------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|

| 24.24                | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24                |                   |                   |                   | CHEMIS<           | <31:24>                            |                   |                  |                  |  |  |

| 00.40                | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16                | CHEMIS<23:16>     |                   |                   |                   |                                    |                   |                  |                  |  |  |

| 45.0                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8                 | CHEMIS<15:8>      |                   |                   |                   |                                    |                   |                  |                  |  |  |

| 7.0                  | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0                  | CHEMIS<7:0>       |                   |                   |                   |                                    |                   |                  |                  |  |  |

|                      |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |

| Legend:              |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |

| R = Readable bit W = |                   |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |

| -n = Value at POR    |                   |                   |                   |                   | '0' = Bit is cl                    | eared             | x = Bit is unl   | known            |  |  |

#### bit 31-0 CHEMIS<31:0>: Cache Miss Count bits

Incremented each time the processor issues an instruction fetch from a cacheable region that misses the prefetch cache. Non-cacheable accesses do not modify this value.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit Bit<br>28/20/12/4 27/19/11/3 |                    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|----------------------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0                            | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        |                   | _                     | BYTO              | <1:0>                            | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0                              | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                     | _                 | —                                | —                  | _                 | _                | _                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0                            | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                     | _                 | _                                |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0                              | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                                | —                  | — CRCCH<2:0>      |                  | ,                |

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

#### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-30 **Unimplemented:** Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (reverse source byte order)

- 00 = No swapping (source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (not reflected)

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | —                 | —                 | _                 | _                 | —                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | —                 | —                 | _                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | —                 | _                 | —                 | _                 | —                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

## REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **CHBUSY:** Channel Busy bit 1 = Channel is active or has been enabled 0 = Channel is inactive or has been disabled

- bit 14-9 **Unimplemented:** Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 Chain to channel lower in patteral priority (CH1 will be enabled by C

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 =Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

#### bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

- 0 = Channel is disabled on block transfer complete

- bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

#### bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- **Note 1:** The chain selection bit takes effect when chaining is enabled (CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHCSIZ            | /<7:0>            |                   |                  |                  |

#### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

## REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHCPTR            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHCPTF            | R<7:0>            |                   |                  |                  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

## REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | -                 |                   | —                 | —                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

# Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

## TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       | · · · |       |       |       |      |      | Bits  |          |       |          |        |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|-------|----------|-------|----------|--------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6     | 21/5  | 20/4     | 19/3   | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     |       | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5200                        | OTTRIME                         | 15:0      | —     | _     | —     | —     | —     | —     | —    | —    |       |          |       | FRML<    | 7:0>   |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 0200                        | 01110                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | -        | —      |        | FRMH<2:0> | •        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —     | —        | —     | —        | —      | —      | —         | —        | 0000       |

| 02/10                       | orron                           | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       | PID      | <3:0> |          |        | EP     | <3:0>     |          | 0000       |

| 52B0                        | U1SOF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | _     | —        | _     | —        | —      | —      | _         | —        | 0000       |

| 5260                        | 0130F                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      |       |          |       | CNT<7    | 7:0>   |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | -     | _     | —     | _     | _     | -    |      | —     | —        |       | —        | —      | _      |           | _        | 0000       |

| 5200                        | OIBDIF2                         | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    |       |          |       | BDTPTRH  | H<7:0> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5200                        | UIBDIF3                         | 15:0      | —     | _     | _     | _     | _     | _     | -    |      |       |          |       | BDTPTRU  | J<7:0> |        |           |          | 0000       |

| 52E0                        | U1CNFG1                         | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 52E0                        | UTCINFGT                        | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | UTEYE | UOEMON   |       | USBSIDL  | —      | _      |           | UASUSPND | 0001       |

| 5300                        | U1EP0                           | 31:16     | —     | _     | _     | _     | _     | _     | -    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5300                        | UIEPU                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | LSPD  | RETRYDIS |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5310                        | UIEPI                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | —        | _      | _      |           | _        | 0000       |

| 5520                        | UIEFZ                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | —        | _      | -      |           | _        | 0000       |

| 5330                        | UIEP3                           | 15:0      | —     | _     | _     | —     | _     | _     | _    |      | —     | _        |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5540                        | UTEP4                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    | —     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | —        | -      | _      | _         | _        | 0000       |

| 5350                        | UIEP5                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5260                        | U1EP6                           | 31:16     |       |       | _     | —     | _     |       | _    | _    | —     |          |       | —        | _      | —      |           |          | 0000       |

| 5360                        | UIEP6                           | 15:0      | _     | _     | -     | -     | -     | -     | -    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5270                        | U1EP7                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _     | —        | _     | —        | _      | _      | -         | _        | 0000       |

| 5370                        | UTEP7                           | 15:0      |       |       | _     | _     | _     |       | _    | _    | —     |          |       | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5200                        |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | —    | -     | —        | _     | —        | _      | —      | _         | _        | 0000       |

| 5380                        | U1EP8                           | 15:0      | —     | _     | —     | —     | _     | _     | —    | _    | _     | _        | -     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5000                        |                                 | 31:16     | _     | —     | _     | —     | _     | —     | _    | —    | _     | —        | _     | —        | —      | —      | —         | —        | 0000       |

| 5390                        | U1EP9                           | 15:0      | _     | —     | _     | _     | _     | _     | _    | _    | _     | _        | _     | EPCONDIS | EPRXEN | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

5390

U1EP9

Legend:

x =

Note

1:

All n

end: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

1: All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit Bit Bit 31/23/15/7 30/22/14/6 29/21/13/5 |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------------------------|-----|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                                          | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                                            | _   |                   | _                 |                   |                   | —                | —                |

| 23:16        | U-0                                          | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                                            | -   | _                 | _                 |                   | _                 | —                | _                |

| 15:8         | U-0                                          | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                                            | -   | _                 | _                 |                   | _                 | —                | _                |

| 7:0          | R-0                                          | U-0 | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND                                      | _   |                   | USLPGRD           | USBBUSY           |                   | USUSPEND         | USBPWR           |

#### REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

# Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

- 0 = An interrupt is not pending

#### bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

#### bit 3 USBBUSY: USB Module Busy bit

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

#### bit 2 Unimplemented: Read as '0'

#### bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

## REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0                   | U-0                     |

| 31.24        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 23:16        | U-0                   | U-0                     |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

| 15:8         | U-0                   | U-0                     |

| 15.6         | —                 | —                 | —                 | —                 | _                 | —                 | _                     |                         |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | IKINE             | SUFIE             | UEKRIE                | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | •·····                                                          |

|-------|-----------------------------------------------------------------|

| bit 7 | STALLIE: STALL Handshake Interrupt Enable bit                   |

|       | 1 = STALL interrupt is enabled                                  |

|       | 0 = STALL interrupt is disabled                                 |

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit                           |

|       | 1 = ATTACH interrupt is enabled                                 |

|       | 0 = ATTACH interrupt is disabled                                |

| bit 5 | RESUMEIE: RESUME Interrupt Enable bit                           |

|       | 1 = RESUME interrupt is enabled                                 |

|       | 0 = RESUME interrupt is disabled                                |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit                        |

|       | 1 = Idle interrupt is enabled                                   |

|       | 0 = Idle interrupt is disabled                                  |

| bit 3 | TRNIE: Token Processing Complete Interrupt Enable bit           |

|       | 1 = TRNIF interrupt is enabled                                  |

|       | 0 = TRNIF interrupt is disabled                                 |

| bit 2 | SOFIE: SOF Token Interrupt Enable bit                           |

|       | 1 = SOFIF interrupt is enabled                                  |

|       | 0 = SOFIF interrupt is disabled                                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup>           |

|       | 1 = USB Error interrupt is enabled                              |

|       | 0 = USB Error interrupt is disabled                             |

| bit 0 | URSTIE: USB Reset Interrupt Enable bit <sup>(2)</sup>           |

|       | 1 = URSTIF interrupt is enabled                                 |

|       | 0 = URSTIF interrupt is disabled                                |

|       | <b>DETACHIE:</b> USB Detach Interrupt Enable bit <sup>(3)</sup> |

|       | 1 = DATTCHIF interrupt is enabled                               |

|       | 0 = DATTCHIF interrupt is disabled                              |

|       |                                                                 |

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

NOTES:

# 18.1 Control Registers

# TABLE 18-1: SPI1 THROUGH SPI4 REGISTER MAP

| SS                          |                                 |               |            |         |        |        |                     |          |           | Bi     | ts     |               |        |          |        |          |        |         |            |

|-----------------------------|---------------------------------|---------------|------------|---------|--------|--------|---------------------|----------|-----------|--------|--------|---------------|--------|----------|--------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14   | 29/13  | 28/12  | 27/11               | 26/10    | 25/9      | 24/8   | 23/7   | 22/6          | 21/5   | 20/4     | 19/3   | 18/2     | 17/1   | 16/0    | All Resets |

|                             | 0011001(2)                      | 31:16         | FRMEN      | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW             | F        | RMCNT<2:0 | >      | _      | _             | _      | _        | _      | _        | SPIFE  | ENHBUF  | 0000       |

| 5E00                        | SPI1CON <sup>(2)</sup>          | 15:0          | ON         | -       | SIDL   | DISSDO | MODE32              | MODE16   | SMP       | CKE    | SSEN   | CKP           | MSTEN  | —        | STXISE | L<1:0>   | SRXISE | L<1:0>  | 0000       |

| 5510                        | SPI1STAT <sup>(2)</sup>         | 31:16         | —          | _       | _      |        | RX                  | BUFELM<4 | :0>       |        | —      | —             | _      |          | TX     | BUFELM<4 | :0>    |         | 0000       |

| 5E IU                       | SPIISIAL                        | 15:0          | —          | _       | _      | _      | SPIBUSY             | _        | -         | SPITUR | SRMT   | SPIROV        | SPIRBE | —        | SPITBE | —        | SPITBF | SPIRBF  | 0008       |

| 5E20                        | SPI1BUF <sup>(2)</sup>          | 31:16<br>15:0 |            |         |        |        |                     |          |           | DATA<  | :31:0> |               |        |          |        |          |        |         | 0000       |

| 5520                        | SPI1BRG <sup>(2)</sup>          | 31:16         | —          | _       | _      | _      | _                   | _        | -         | _      | —      | —             | _      | —        | _      | —        | —      | _       | 0000       |

| 3E30                        | SFIIDKG                         | 15:0          | —          | —       | _      | _      | _                   | -        |           |        |        |               |        | BRG<8:0> |        |          |        |         | 0000       |

| 5800                        | SPI3CON                         | 31:16         | FRMEN      | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW             | F        | RMCNT<2:0 | >      | _      | - 1           | _      | -        | _      | _        | SPIFE  | ENHBUF  | 0000       |

| 5800                        | SPI3CON                         | 15:0          | ON         | _       | SIDL   | DISSDO | MODE32              | MODE16   | SMP       | CKE    | SSEN   | CKP           | MSTEN  | —        | STXISE | L<1:0>   | SRXISE | L<1:0>  | 0000       |

| 5040                        | SPI3STAT                        | 31:16         | —          | _       | _      |        | RXBUFELM<4:0> — — — |          |           | _      |        | TXBUFELM<4:0> |        |          | 0000   |          |        |         |            |

| 5810                        | SFISSIAI                        | 15:0          |            | _       | -      | _      | SPIBUSY             | -        |           | SPITUR | SRMT   | SPIROV        | SPIRBE | _        | SPITBE | —        | SPITBF | SPIRBF  | 0008       |

| 5820                        | SPI3BUF                         | 31:16<br>15:0 | DATA<31:0> |         |        |        |                     |          |           |        |        | 0000          |        |          |        |          |        |         |            |

|                             | 0010000                         | 31:16         |            | _       | _      | —      | —                   | _        | _         |        | _      | _             | _      | _        | _      | —        | _      | _       | 0000       |

| 5830                        | SPI3BRG                         | 15:0          | _          | —       | _      | —      | _                   | _        |           |        |        | •             |        | BRG<8:0> |        |          | •      |         | 0000       |

| 5400                        | SPI2CON                         | 31:16         | FRMEN      | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW             | F        | RMCNT<2:0 | <<br>< | _      | —             | _      | -        | _      | _        | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | 3F12001N                        | 15:0          | ON         | _       | SIDL   | DISSDO | MODE32              | MODE16   | SMP       | CKE    | SSEN   | CKP           | MSTEN  | _        | STXISE | L<1:0>   | SRXISE | EL<1:0> | 0000       |

| 5A10                        | SPI2STAT                        | 31:16         | _          |         |        |        | RX                  | BUFELM<4 | :0>       |        | _      |               |        |          | TX     | BUFELM<4 | :0>    | -       | 0000       |

| 5A 10                       | 51 125 TAT                      | 15:0          | —          | —       | —      | —      | SPIBUSY             | —        | —         | SPITUR | SRMT   | SPIROV        | SPIRBE | —        | SPITBE | —        | SPITBF | SPIRBF  | 0008       |

| 5A20                        | SPI2BUF                         | 31:16<br>15:0 |            |         |        |        |                     |          |           | DATA<  | :31:0> |               |        |          |        |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16         | _          | —       | —      | —      | —                   | —        | _         | —      | _      | —             | —      | —        | —      | —        | —      | —       | 0000       |

| 5A30                        |                                 | 15:0          | _          | —       | —      | —      | —                   | —        | _         |        |        |               |        | BRG<8:0> |        |          |        |         | 0000       |

| 5C00                        | SPI4CON                         | 31:16         | FRMEN      | FRMSYNC | FRMPOL | MSSEN  | FRMSYPW             | F        | RMCNT<2:0 | >      | —      | —             | —      | _        | —      | —        | SPIFE  | ENHBUF  | 0000       |

| 5000                        | 01140011                        | 15:0          | ON         | —       | SIDL   | DISSDO | MODE32              | MODE16   | SMP       | CKE    | SSEN   | CKP           | MSTEN  | —        | STXISE |          | SRXISE | EL<1:0> | 0000       |

| 5C10                        | SPI4STAT                        | 31:16         | —          | —       |        |        |                     | BUFELM<4 | :0>       |        | —      | —             | —      |          | TX     | BUFELM<4 |        |         | 0000       |

| 3010                        | 0                               | 15:0          | -          | -       | _      | —      | SPIBUSY             | —        | —         | SPITUR | SRMT   | SPIROV        | SPIRBE | —        | SPITBE | —        | SPITBF | SPIRBF  | 0008       |

| 5C20                        | SPI4BUF                         | 31:16<br>15:0 |            |         |        |        |                     |          |           | DATA<  | :31:0> |               |        |          |        |          |        |         | 0000       |

| 5C30                        | SPI4BRG                         | 31:16         | _          | -       | -      | —      | —                   | —        | —         | -      | _      | -             | —      | —        | -      | —        | -      | _       | 0000       |

| 5030                        |                                 | 15:0          | -          | -       | _      | _      | _                   | _        | —         |        |        |               |        | BRG<8:0> |        |          |        |         | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

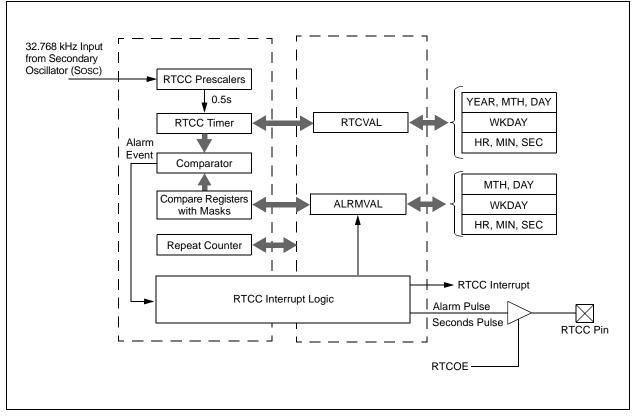

# 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. A simplified block diagram of the RTCC module is illustrated in Figure 22-1. Key features of the RTCC module include:

- Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- Alarm repeat with decrementing counter

- Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

## FIGURE 22-1: RTCC BLOCK DIAGRAM

#### REGISTER 25-3: ETHTXST: ETHERNET CONTROLLER TX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | TXSTADDR<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | TXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.0         | TXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |  |

| 7.0          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# Legend:

| Legenu.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-2 **TXSTADDR<31:2>:** Starting Address of First Transmit Descriptor bits This register should not be written while any transmit, receive or DMA operations are in progress. This address must be 4-byte aligned (bits 1-0 must be '00').

#### bit 1-0 Unimplemented: Read as '0'

Note 1: This register is only used for TX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

## REGISTER 25-4: ETHRXST: ETHERNET CONTROLLER RX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        |                   |                   |                   | RXSTADE           | )R<31:24>         |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | RXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 0.61         | RXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |

| 7:0          |                   |                   | _                 |                   |                   |                   |                  |                  |  |  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-2 **RXSTADDR<31:2>:** Starting Address of First Receive Descriptor bits

This register should not be written while any transmit, receive or DMA operations are in progress. This address must be 4-byte aligned (bits 1-0 must be '00').

#### bit 1-0 Unimplemented: Read as '0'

Note 1: This register is only used for RX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

#### REGISTER 25-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | _                 | —                 | —                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | _                 |                   |                   | B2                | BIPKTGP<6:(       | )>                |                  |                  |

#### Legend:

| Logona.           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet, to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

#### REGISTER 25-28: EMAC1MAXF: ETHERNET CONTROLLER MAC MAXIMUM FRAME LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|------------------------------|-----------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                          | U-0                         | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                              | —                           | _                 | _                 | —                 | —                 | _                | _                |  |  |  |

| 22:16        | U-0                          | U-0                         | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                            | —                           | —                 | —                 | —                 | —                 | _                | —                |  |  |  |

| 15.0         | R/W-0                        | R/W-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-0            | R/W-1            |  |  |  |

| 15:8         | MACMAXF<15:8> <sup>(1)</sup> |                             |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-1                        | R/W-1                       | R/W-1             | R/W-0             | R/W-1             | R/W-1             | R/W-1            | R/W-0            |  |  |  |

| 7:0          |                              | MACMAXF<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MACMAXF<15:0>: Maximum Frame Length bits<sup>(1)</sup>

These bits reset to 0x05EE, which represents a maximum receive frame of 1518 octets. An untagged maximum size Ethernet frame is 1518 octets. A tagged frame adds four octets for a total of 1522 octets. If a shorter/longer maximum length restriction is desired, program this 16-bit field.

**Note 1:** If a proprietary header is allowed, this bit should be adjusted accordingly. For example, if 4-byte headers are prepended to frames, MACMAXF could be set to 1527 octets. This would allow the maximum VLAN tagged frame plus the 4-byte header.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

NOTES:

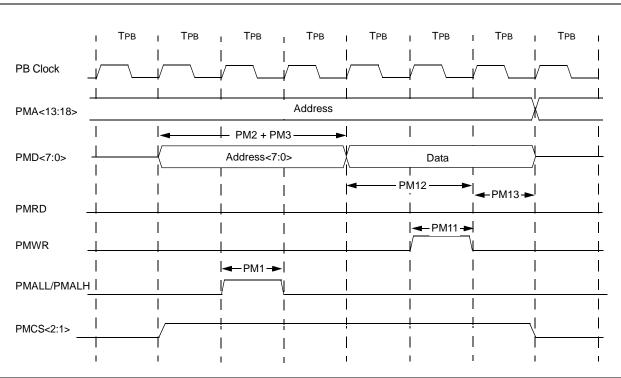

## FIGURE 32-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

# TABLE 32-41: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS