Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

|                           |                                                                                 |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| Speed                     | 80MHz                                                                           |

| Connectivity              | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| lumber of I/O             | 85                                                                              |

| Program Memory Size       | 64KB (64K x 8)                                                                  |

| Program Memory Type       | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| RAM Size                  | 16K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters           | A/D 16x10b                                                                      |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Nounting Type             | Surface Mount                                                                   |

| ackage / Case             | 100-TQFP                                                                        |

| upplier Device Package    | 100-TQFP (12x12)                                                                |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx534f064lt-v-pt |

TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES

|                 |      |                         |                  |     | USE      | and E                  | therne                                | t                     |                    |                                 |                              |             |         |      |       |                         |

|-----------------|------|-------------------------|------------------|-----|----------|------------------------|---------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device          | Pins | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels (Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | PMP/PSP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H | 64   | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                   | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                   | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                   | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                   | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H | 64   | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                   | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L | 100  | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                   | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                   | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                   | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L | 100  | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                   | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L | 100  | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                   | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

**Legend:** PF, PT = TQFP

MR = QFN

BG = TFBGA

TL = VTLA<sup>(5)</sup>

Note 1: This device features 12 KB boot Flash memory.

- 2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information

- 3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "**Device Pin Tables**" section for more information.

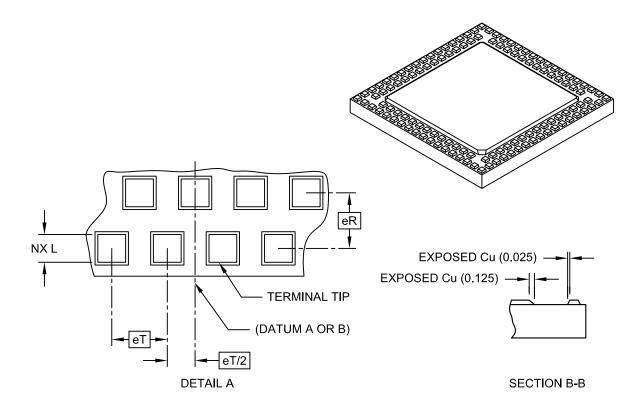

- 4: Refer to 34.0 "Packaging Information" for more information.

- 5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

### TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES (CONTINUED)

100-PIN TQFP (TOP VIEW)

PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L

100

1

| Pin# | Full Pin Name        |

|------|----------------------|

| 71   | IC4/PMCS1/PMA14/RD11 |

| 72   | SDO1/OC1/INT0/RD0    |

| 73   | SOSCI/CN1/RC13       |

| 74   | SOSCO/T1CK/CN0/RC14  |

| 75   | Vss                  |

| 76   | OC2/RD1              |

| 77   | OC3/RD2              |

| 78   | OC4/RD3              |

| 79   | IC5/PMD12/RD12       |

| 80   | PMD13/CN19/RD13      |

| 81   | OC5/PMWR/CN13/RD4    |

| 82   | PMRD/CN14/RD5        |

| 83   | PMD14/CN15/RD6       |

| 84   | PMD15/CN16/RD7       |

| 85   | VCAP                 |

| Pin # | Full Pin Name  |

|-------|----------------|

| 86    | VDD            |

| 87    | C1RX/PMD11/RF0 |

| 88    | C1TX/PMD10/RF1 |

| 89    | PMD9/RG1       |

| 90    | PMD8/RG0       |

| 91    | TRCLK/RA6      |

| 92    | TRD3/RA7       |

| 93    | PMD0/RE0       |

| 94    | PMD1/RE1       |

| 95    | TRD2/RG14      |

| 96    | TRD1/RG12      |

| 97    | TRD0/RG13      |

| 98    | PMD2/RE2       |

| 99    | PMD3/RE3       |

| 100   | PMD4/RE4       |

Note 1: Shaded pins are 5V tolerant.

### TABLE 9: PIN NAMES FOR 100-PIN USB, ETHERNET, AND CAN DEVICES

### 100-PIN TQFP (TOP VIEW)

PIC32MX764F128L PIC32MX775F256L PIC32MX775F512L PIC32MX795F512L

100

1

| Pin# | Full Pin Name                                                |

|------|--------------------------------------------------------------|

| 1    | AERXERR/RG15                                                 |

| 2    | VDD                                                          |

| 3    | PMD5/RE5                                                     |

| 4    | PMD6/RE6                                                     |

| 5    | PMD7/RE7                                                     |

| 6    | T2CK/RC1                                                     |

| 7    | T3CK/AC2TX <sup>(1)</sup> /RC2                               |

| 8    | T4CK/AC2RX <sup>(1)</sup> /RC3                               |

| 9    | T5CK/SDI1/RC4                                                |

| 10   | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| 11   | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| 12   | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8     |

| 13   | MCLR                                                         |

| 14   | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| 15   | Vss                                                          |

| 16   | VDD                                                          |

| 17   | TMS/RA0                                                      |

| 18   | AERXD0/INT1/RE8                                              |

| 19   | AERXD1/INT2/RE9                                              |

| 20   | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| 21   | AN4/C1IN-/CN6/RB4                                            |

| 22   | AN3/C2IN+/CN5/RB3                                            |

| 23   | AN2/C2IN-/CN4/RB2                                            |

| 24   | PGEC1/AN1/CN3/RB1                                            |

| 25   | PGED1/AN0/CN2/RB0                                            |

| 26   | PGEC2/AN6/OCFA/RB6                                           |

| 27   | PGED2/AN7/RB7                                                |

| 28   | VREF-/CVREF-/AERXD2/PMA7/RA9                                 |

| 29   | VREF+/CVREF+/AERXD3/PMA6/RA10                                |

| 30   | AVDD                                                         |

| 31   | AVss                                                         |

| 32   | AN8/C1OUT/RB8                                                |

| 33   | AN9/C2OUT/RB9                                                |

| 34   | AN10/CVREFOUT/PMA13/RB10                                     |

| 35   | AN11/ERXERR/AETXERR/PMA12/RB11                               |

| Pin # | Full Pin Name                               |

|-------|---------------------------------------------|

| 36    | Vss                                         |

| 37    | VDD                                         |

| 38    | TCK/RA1                                     |

| 39    | AC1TX/SCK4/U5TX/U2RTS/RF13                  |

| 40    | AC1RX/SS4/U5RX/U2CTS/RF12                   |

| 41    | AN12/ERXD0/AECRS/PMA11/RB12                 |

| 42    | AN13/ERXD1/AECOL/PMA10/RB13                 |

| 43    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14           |

| 44    | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |

| 45    | Vss                                         |

| 46    | VDD                                         |

| 47    | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |

| 48    | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |

| 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |

| 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |

| 51    | USBID/RF3                                   |

| 52    | SDA3/SDI3/U1RX/RF2                          |

| 53    | SCL3/SDO3/U1TX/RF8                          |

| 54    | VBUS                                        |

| 55    | VUSB3V3                                     |

| 56    | D-/RG3                                      |

| 57    | D+/RG2                                      |

| 58    | SCL2/RA2                                    |

| 59    | SDA2/RA3                                    |

| 60    | TDI/RA4                                     |

| 61    | TDO/RA5                                     |

| 62    | VDD                                         |

| 63    | OSC1/CLKI/RC12                              |

| 64    | OSC2/CLKO/RC15                              |

| 65    | Vss                                         |

| 66    | AETXCLK/SCL1/INT3/RA14                      |

| 67    | AETXEN/SDA1/INT4/RA15                       |

| 68    | RTCC/EMDIO/AEMDIO/IC1/RD8                   |

| 69    | SS1/IC2/RD9                                 |

| 70    | SCK1/IC3/PMCS2/PMA15/RD10                   |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

| In ( (1)                          | IRQ    | Vector        |                               | Interru  | ot Bit Location |              |  |  |  |  |  |  |  |  |

|-----------------------------------|--------|---------------|-------------------------------|----------|-----------------|--------------|--|--|--|--|--|--|--|--|

| Interrupt Source <sup>(1)</sup>   | Number | Number        | Flag                          | Enable   | Priority        | Sub-Priority |  |  |  |  |  |  |  |  |

| IC3E – Input Capture 3 Error      | 63     | 13            | IFS1<31>                      | IEC1<31> | IPC3<12:10>     | IPC3<9:8>    |  |  |  |  |  |  |  |  |

| IC4E – Input Capture 4 Error      | 64     | 17            | IFS2<0>                       | IEC2<0>  | IPC4<12:10>     | IPC4<9:8>    |  |  |  |  |  |  |  |  |

| IC5E – Input Capture 5 Error      | 65     | 21            | IFS2<1>                       | IEC2<1>  | IPC5<12:10>     | IPC5<9:8>    |  |  |  |  |  |  |  |  |

| PMPE – Parallel Master Port Error | 66     | 28            | IFS2<2>                       | IEC2<2>  | IPC7<4:2>       | IPC7<1:0>    |  |  |  |  |  |  |  |  |

| U4E – UART4 Error                 | 67     | 49            | IFS2<3>                       | IEC2<3>  | IPC12<12:10>    | IPC12<9:8>   |  |  |  |  |  |  |  |  |

| U4RX – UART4 Receiver             | 68     | 49            | IFS2<4>                       | IEC2<4>  | IPC12<12:10>    | IPC12<9:8>   |  |  |  |  |  |  |  |  |

| U4TX – UART4 Transmitter          | 69     | 49            | IFS2<5>                       | IEC2<5>  | IPC12<12:10>    | IPC12<9:8>   |  |  |  |  |  |  |  |  |

| U6E – UART6 Error                 | 70     | 50            | IFS2<6>                       | IEC2<6>  | IPC12<20:18>    | IPC12<17:16> |  |  |  |  |  |  |  |  |

| U6RX – UART6 Receiver             | 71     | 50            | IFS2<7>                       | IEC2<7>  | IPC12<20:18>    | IPC12<17:16> |  |  |  |  |  |  |  |  |

| U6TX – UART6 Transmitter          | 72     | 50            | IFS2<8>                       | IEC2<8>  | IPC12<20:18>    | IPC12<17:16> |  |  |  |  |  |  |  |  |

| U5E – UART5 Error                 | 73     | 51            | IFS2<9>                       | IEC2<9>  | IPC12<28:26>    | IPC12<25:24> |  |  |  |  |  |  |  |  |

| U5RX – UART5 Receiver             | 74     | 51            | IFS2<10>                      | IEC2<10> | IPC12<28:26>    | IPC12<25:24> |  |  |  |  |  |  |  |  |

| U5TX – UART5 Transmitter          | 75     | 51            | IFS2<11>                      | IEC2<11> | IPC12<28:26>    | IPC12<25:24> |  |  |  |  |  |  |  |  |

| (Reserved) — — — — — — —          |        |               |                               |          |                 |              |  |  |  |  |  |  |  |  |

|                                   | Lowe   | est Natural ( | Lowest Natural Order Priority |          |                 |              |  |  |  |  |  |  |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

### 10.1 Control Registers

#### TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                       | Bits      |       |       |       |         |         |       |      |          |          |      |      |      |      | s    |           |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|----------|------|------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2000                        | DMACON <sup>(1)</sup> | 31:16     | _     | _     | _     | _       | _       | _     | _    | _        | _        | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 3000                        | DIVIACON              | 15:0      | ON    | _     | _     | SUSPEND | DMABUSY | _     | _    | _        | _        | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 2010                        | DMASTAT               | 31:16     |       | _     | _     | _       | _       | _     | _    | _        | _        | _    | _    | _    | _    | _    | _         |      | 0000       |

| 3010                        | DIVIASTAT             | 15:0      |       | _     | _     | _       | _       |       | _    | _        | _        | _    | _    | _    | RDWR | D    | MACH<2:0> | (2)  | 0000       |

| 2020                        | DMAADDR               | 31:16     |       | •     | •     |         |         | •     | •    | DMAADE   | DR<31:0> |      | •    | •    |      |      |           |      | 0000       |

| 3020                        | DIVIAADDK             | 15:0      |       |       |       |         |         |       |      | DIVIAADL | /N<31.0> |      |      |      |      |      |           |      | 0000       |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: DMACH<3> bit is not available on PIC32MX534/564/664/764 devices.

## TABLE 10-2: DMA CRC REGISTER MAP<sup>(1)</sup>

| ess                         |                                 |           |       |               |       |        |       |           |      | В      | its       |        |        |      |      |      |            |      | ·s         |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|--------|-------|-----------|------|--------|-----------|--------|--------|------|------|------|------------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12  | 27/11 | 26/10     | 25/9 | 24/8   | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1       | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _             | BYTO  | )<1:0> | WBO   | _         | _    | BITO   | _         | _      | _      | _    | _    | _    | _          | _    | 0000       |

| 3030                        | DCKCCON                         | 15:0      | _     | _             | _     |        |       | PLEN<4:0> |      |        | CRCEN     | CRCAPP | CRCTYP | _    | _    | (    | CRCCH<2:0: | >    | 0000       |

| 2040                        | DCRCDATA                        | 31:16     |       |               |       |        |       |           |      | DCRCDA | TA -21:05 |        |        |      |      |      |            |      | 0000       |

| 3040                        | DCKCDAIA                        | 15:0      |       |               |       |        |       |           |      | DCKCDA | 11AC31.U2 |        |        |      |      |      |            |      | 0000       |

| 2050                        | DCRCXOR                         | 31:16     |       |               |       |        |       |           |      | DCBCVC | ND -21:05 |        |        |      |      |      |            |      | 0000       |

| 3050                        | DONOXOR                         | 15:0      |       | DCRCXOR<31:0> |       |        |       |           |      |        |           |        |        |      |      |      |            |      |            |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | _                 |                   | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 |                   | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CHPDAT<7:0>: Channel Data Register bits

Pattern Terminate mode:

Data to be matched must be stored in this register to allow terminate on match.

All other modes:

Unused.

REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

bit 3 Unimplemented: Read as '0'

bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

When TCS = 1:

1 = External clock input is synchronized 0 = External clock input is not synchronized

When TCS = 0: This bit is ignored.

bit 1 TCS: Timer Clock Source Select bit

1 = External clock from TxCKI pin0 = Internal peripheral clock

bit 0 Unimplemented: Read as '0'

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### 17.0 OUTPUT COMPARE

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

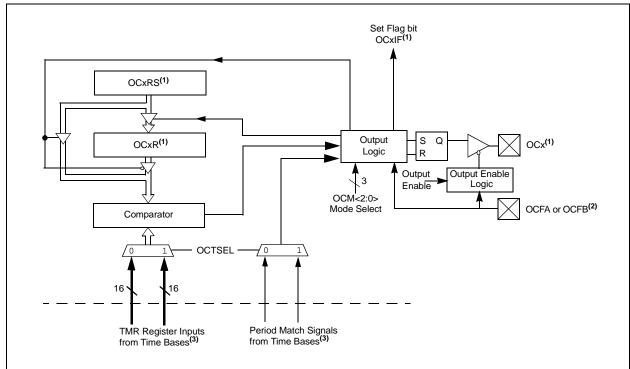

The Output Compare module is used to generate a single pulse or a series of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of the Output Compare module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- · Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Programmable selection of 16-bit or 32-bit time bases

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

- **Note 1:** Where 'x' is shown, reference is made to the registers associated with the respective output compare channels, 1 through 5.

- **2:** The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

- 3: Each output compare channel can use one of two selectable 16-bit time bases or a single 32-bit timer base.

### REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | _                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7.0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

Legend:HS = Set by hardwareHSC = Hardware set/clearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedC = Clearable bit

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

This bit is set or cleared by hardware at the end of a slave Acknowledge.

- 1 = NACK received from slave

- 0 = ACK received from slave

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

This bit is set by hardware at the beginning of a master transmission, and is cleared by hardware at the end of a slave Acknowledge.

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

This bit is set by hardware at the detection of a bus collision.

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

- bit 9 GCSTAT: General Call Status bit

This bit is set by hardware when the address matches the general call address, and is cleared by hardware clear at a Stop detection.

- 1 = General call address was received

- 0 = General call address was not received

- bit 8 ADD10: 10-bit Address Status bit

This bit is set by hardware upon a match of the 2nd byte of the matched 10-bit address, and is cleared by hardware at a Stop detection.

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

- bit 7 IWCOL: Write Collision Detect bit

This bit is set by hardware at the occurrence of a write to I2CxTRN while busy (cleared by software).

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2$ C module is busy

- 0 = No collision

- bit 6 I2COV: Receive Overflow Flag bit

This bit is set by hardware at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

#### REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 |                   | _                 | -                 | _                | _                |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | DAY′              | 10<1:0>           |                   |                   | DAY01             | l<3:0>           |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | _                 | _                 | _                 | _                 |                   | WDAYO             | )1<3:0>          | ·                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

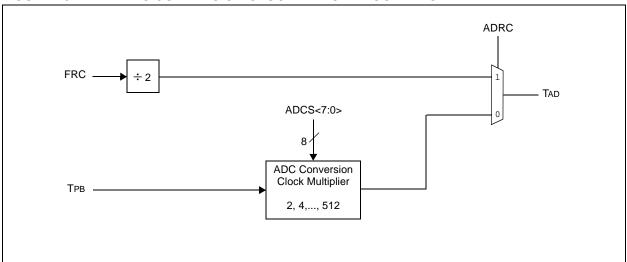

### FIGURE 23-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

### 25.1 Control Registers

TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512L, PIC32MX764F128H, PIC32MX764F128H, PIC32MX775F256L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ss                          |                                 |               |       |              | · · ·        |       |       |       |              | В            | its          |               |               |        |              |               |               |               |            |

|-----------------------------|---------------------------------|---------------|-------|--------------|--------------|-------|-------|-------|--------------|--------------|--------------|---------------|---------------|--------|--------------|---------------|---------------|---------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14        | 29/13        | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6          | 21/5          | 20/4   | 19/3         | 18/2          | 17/1          | 16/0          | All Resets |

| 9000                        | ETHCON1                         | 31:16         |       |              |              |       |       |       |              |              |              |               |               |        |              |               |               |               |            |

| 9000                        | LITICONT                        | 15:0          | ON    | _            | SIDL         | _     |       | _     | TXRTS        | RXEN         | AUTOFC       | _             | _             | MANFC  | _            | _             | _             | BUFCDEC       | 0000       |

| 9010                        | ETHCON2                         | 31:16         |       |              | _            | _     |       | _     | _            | _            | _            | _             | _             | _      | _            | _             |               |               | 0000       |

|                             |                                 | 15:0          | _     | _            | _            | _     | _     |       |              |              | XBUFSZ<6:0   | )>            |               |        | _            | _             | _             | _             | 0000       |

| 9020                        | ETHTXST                         | 31:16         |       |              |              |       |       |       | T)/OT4 D     | TXSTADE      | R<31:16>     |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 15:0          |       |              |              |       |       |       | TXSTADE      |              | D 04:40      |               |               |        |              |               | _             | _             | 0000       |

| 9030                        | ETHRXST                         | 31:16<br>15:0 |       |              |              |       |       |       | RXSTADI      | RXSTADE      | JR<31:16>    |               |               |        |              |               | _             | _             | 0000       |

|                             |                                 | 31:16         |       |              |              |       |       |       | KASTADI      | JK<13.2>     |              |               |               |        |              |               | _             | _             | 0000       |

| 9040                        | ETHHT0                          | 15:0          |       |              |              |       |       |       |              | HT<          | 31:0>        |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         |       |              |              |       |       |       |              |              |              |               |               |        |              |               |               |               | 0000       |

| 9050                        | ETHHT1                          | 15:0          |       |              |              |       |       |       |              | HT<6         | 3:32>        |               |               |        |              |               |               |               | 0000       |

| 0000                        | ETHPMM0                         | 31:16         |       |              |              |       |       |       |              | DMM          | :31:0>       |               |               |        |              |               |               |               | 0000       |

| 9060                        | ETHPIMIMU                       | 15:0          |       |              |              |       |       |       |              | PIVIIVI      | 31:0>        |               |               |        |              |               |               |               | 0000       |

| 9070                        | ETHPMM1                         | 31:16<br>15:0 |       |              |              |       |       |       |              | PMM<         | 63:32>       |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         | _     | _            | _            | _     | _     | _     | _            | _            | _            | _             | _             | _      | _            | _             | _             | _             | 0000       |

| 9080                        | ETHPMCS                         | 15:0          |       |              |              |       |       |       |              | PMCS         | <15:0>       |               |               |        |              |               |               |               | 0000       |

|                             |                                 | 31:16         | _     | _            | _            | _     | _     | _     | _            | _            | _            | _             | _             | _      | _            | _             | _             | _             | 0000       |

| 9090                        | ETHPMO                          | 15:0          |       |              | •            |       |       |       | •            | PMO-         | :15:0>       | •             |               | •      |              | •             |               | •             | 0000       |

|                             |                                 | 31:16         | _     | _            | _            | _     | _     | _     | _            | _            | _            | _             | _             | _      | _            | _             | _             | _             | 0000       |

| 90A0                        | ETHRXFC                         | 15:0          | HTEN  | MPEN         | _            | NOTPM |       | PMMOI | DE<3:0>      |              | CRC<br>ERREN | CRC<br>OKEN   | RUNT<br>ERREN | RUNTEN | UCEN         | NOT<br>MEEN   | MCEN          | BCEN          | 0000       |

| 90B0                        | ETHRXWM                         | 31:16         | =     | _            | _            | _     | _     | _     | _            | _            |              |               |               | RXFW   | M<7:0>       |               |               |               | 0000       |

| 9000                        | LIUKAVVIVI                      | 15:0          | _     | _            | _            | _     | _     | _     | _            | _            |              |               |               | RXEW   | M<7:0>       |               |               |               | 0000       |

|                             |                                 | 31:16         | _     | _            | _            | _     | -     | _     | _            | _            | _            | _             |               | _      | _            | _             | _             | _             | 0000       |

| 90C0                        | ETHIEN                          | 15:0          | _     | TX<br>BUSEIE | RX<br>BUSEIE | _     | _     | _     | EW<br>MARKIE | FW<br>MARKIE | RX<br>DONEIE | PK<br>TPENDIE | RX<br>ACTIE   | _      | TX<br>DONEIE | TX<br>ABORTIE | RX<br>BUFNAIE | RX<br>OVFLWIE | 0000       |

| 90D0                        | ETHIRQ                          | 31:16         |       |              | _            | _     |       | -     | _            | _            | _            | _             |               | _      | _            | _             |               | _             | 0000       |

| 9000                        |                                 | 15:0          | _     | TXBUSE       | RXBUSE       | _     | _     | _     | EWMARK       | FWMARK       | RXDONE       | PKTPEND       | RXACT         | _      | TXDONE       | TXABORT       | RXBUFNA       | RXOVFLW       | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

PIC32MX5XX/6XX/7XX

Note 1: All registers in this table (with the exception of ETHSTAT) have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> Reset values default to the factory programmed value.

# REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER (CONTINUED)

- bit 7 CRCERREN: CRC Error Collection Enable bit

- 1 = The received packet CRC must be invalid for the packet to be accepted

- 0 = Disable CRC Error Collection filtering

This bit allows the user to collect all packets that have an invalid CRC.

- bit 6 CRCOKEN: CRC OK Enable bit

- 1 = The received packet CRC must be valid for the packet to be accepted

- 0 = Disable CRC filtering

This bit allows the user to reject all packets that have an invalid CRC.

- bit 5 RUNTERREN: Runt Error Collection Enable bit

- 1 = The received packet must be a runt packet for the packet to be accepted

- 0 = Disable Runt Error Collection filtering

This bit allows the user to collect all packets that are runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes (when CRCOKEN = 0) or any packet with a size of less than 64 bytes that has a valid CRC (when CRCOKEN = 1).

- bit 4 RUNTEN: Runt Enable bit

- 1 = The received packet must not be a runt packet for the packet to be accepted

- 0 = Disable Runt filtering

This bit allows the user to reject all runt packets. For this filter, a runt packet is defined as any packet with a size of less than 64 bytes.

- bit 3 UCEN: Unicast Enable bit

- 1 = Enable Unicast Filtering

- 0 = Disable Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address matches the Station Address.

- bit 2 NOTMEEN: Not Me Unicast Enable bit

- 1 = Enable Not Me Unicast Filtering

- 0 = Disable Not Me Unicast Filtering

This bit allows the user to accept all unicast packets whose Destination Address does not match the Station Address.

- bit 1 MCEN: Multicast Enable bit

- 1 = Enable Multicast Filtering

- 0 = Disable Multicast Filtering

This bit allows the user to accept all Multicast Address packets.

- bit 0 BCEN: Broadcast Enable bit

- 1 = Enable Broadcast Filtering

- 0 = Disable Broadcast Filtering

This bit allows the user to accept all Broadcast Address packets.

- **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

- Note 1: This register is only used for RX operations.

- 2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

### REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER

bit 6 **PKTPEND:** Packet Pending Interrupt bit

1 = RX packet pending in memory

0 = RX packet is not pending in memory

This bit is set when the BUFCNT counter has a value other than '0'. It is cleared by either a Reset or by writing the BUFCDEC bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.

bit 5 RXACT: Receive Activity Interrupt bit

1 = RX packet data was successfully received

0 = No interrupt pending

This bit is set whenever RX packet data is stored in the RXBM FIFO. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 4 **Unimplemented:** Read as '0'

bit 3 **TXDONE:** Transmit Done Interrupt bit

1 = TX packet was successfully sent

0 = No interrupt pending

This bit is set when the currently transmitted TX packet completes transmission, and the Transmit Status Vector is loaded into the first descriptor used for the packet. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 2 TXABORT: Transmit Abort Condition Interrupt bit

1 = TX abort condition occurred on the last TX packet

0 = No interrupt pending

This bit is set when the MAC aborts the transmission of a TX packet for one of the following reasons:

- · Jumbo TX packet abort

- · Underrun abort

- Excessive defer abort

- · Late collision abort

- · Excessive collisions abort

This bit is cleared by either a Reset or CPU write of a '1' to the CLR register.

bit 1 RXBUFNA: Receive Buffer Not Available Interrupt bit

1 = RX Buffer Descriptor Not Available condition has occurred

0 = No interrupt pending

This bit is set by a RX Buffer Descriptor Overrun condition. It is cleared by either a Reset or a CPU write of a '1' to the CLR register.

bit 0 RXOVFLW: Receive FIFO Over Flow Error bit

1 = RX FIFO Overflow Error condition has occurred

0 = No interrupt pending

RXOVFLW is set by the RXBM Logic for an RX FIFO Overflow condition. It is cleared by either a Reset or CPU write of a '1' to the CLR register.

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

# REGISTER 25-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7  | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                    | _                 | -                 | _                 | -                 |                   | _                | _                |  |

| 23:16        | U-0                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                    | _                 | -                 | _                 | -                 |                   | _                | _                |  |

| 15:8         | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |

| 15.6         | _                  |                   |                   | NB2E              | BIPKTGP1<6:       | 0>                |                  |                  |  |

| 7:0          | U-0                | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |  |

| 7.0          | - NB2BIPKTGP2<6:0> |                   |                   |                   |                   |                   |                  |                  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-15 Unimplemented: Read as '0'

bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If the carrier is detected during the timing of IPGR1, the MAC defers to the carrier. If, however, the carrier comes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to the medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

bit 7 Unimplemented: Read as '0'

bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of  $0.96 \mu s$  (in 100 Mbps) or  $9.6 \mu s$  (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# REGISTER 25-31: EMAC1MCFG: ETHERNET CONTROLLER MAC MII MANAGEMENT CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 |                   |                   | _                 | _                 | -                |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                 |                   |                   | _                 | _                 | -                | _                |

| 15:8         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | RESETMGMT         | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | R/W-1             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 |                   | CLKSEI            | NOPRE             | SCANINC           |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 RESETMGMT: Test Reset MII Management bit

1 = Reset the MII Management module

0 = Normal Operation

bit 14-6 Unimplemented: Read as '0'

bit 5-2 CLKSEL<3:0>: MII Management Clock Select 1 bits<sup>(1)</sup>

These bits are used by the clock divide logic in creating the MII Management Clock (MDC), which the IEEE 802.3 Specification defines to be no faster than 2.5 MHz. Some PHYs support clock rates up to 12.5 MHz.

bit 1 NOPRE: Suppress Preamble bit

- 1 = The MII Management will perform read/write cycles without the 32-bit preamble field. Some PHYs support suppressed preamble

- 0 = Normal read/write cycles are performed

- bit 0 **SCANINC:** Scan Increment bit

- 1 = The MII Management module will perform read cycles across a range of PHYs. The read cycles will start from address 1 through the value set in EMAC1MADR<PHYADDR>

- 0 = Continuous reads of the same PHY

**Note 1:** Table 25-7 provides a description of the clock divider encoding.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

#### TABLE 25-7: MIIM CLOCK SELECTION

| MIIM Clock Select    | EMAC1MCFG<5:2>        |

|----------------------|-----------------------|

| SYSCLK divided by 4  | 000x                  |

| SYSCLK divided by 6  | 0010                  |

| SYSCLK divided by 8  | 0011                  |

| SYSCLK divided by 10 | 0100                  |

| SYSCLK divided by 14 | 0101                  |

| SYSCLK divided by 20 | 0110                  |

| SYSCLK divided by 28 | 0111                  |

| SYSCLK divided by 40 | 1000                  |

| Undefined            | Any other combination |

TABLE 32-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

| DC CHA                                                                            | RACTERIS               | TICS               | (unless  | d Operatin<br>otherwise<br>ng temperat | stated)<br>ure -4                                                                                         | itions: 2.3V to 3.6V $0^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $0^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |  |  |  |  |

|-----------------------------------------------------------------------------------|------------------------|--------------------|----------|----------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Param.<br>No.                                                                     | Typical <sup>(2)</sup> | Max.               | Units    | Conditions                             |                                                                                                           |                                                                                                                           |  |  |  |  |

| Power-Down Current (IPD) <sup>(1)</sup> for PIC32MX534/564/664/764 Family Devices |                        |                    |          |                                        |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC40g                                                                             | 12                     | 40                 |          | -40°C                                  |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC40h                                                                             | 20                     | 120                |          | +25°C                                  | 2.3V                                                                                                      | Base Power-Down Current (Note 6)                                                                                          |  |  |  |  |

| DC40i                                                                             | 210                    | 600                |          | +85°C                                  | 2.3 V                                                                                                     | Base Fower-Down Current (Note o)                                                                                          |  |  |  |  |

| DC40o                                                                             | 400                    | 1000               |          | +105°C                                 |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC40j                                                                             | 20                     | 120                | μА       | +25°C                                  | 3.3V Base Power-Down Current                                                                              |                                                                                                                           |  |  |  |  |

| DC40k                                                                             | 15                     | 80                 | μΑ       | -40°C                                  |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC40I                                                                             | 20                     | 120                |          | +25°C                                  |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC40m                                                                             | 113                    | 350 <sup>(5)</sup> |          | +70°C                                  | 3.6V Base Power-Down Current                                                                              |                                                                                                                           |  |  |  |  |

| DC40n                                                                             | 220                    | 650                |          | +85°C                                  |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC40p                                                                             | 500                    | 1000               |          | +105°C                                 |                                                                                                           |                                                                                                                           |  |  |  |  |

| Module                                                                            | Differential           | Current fo         | r PIC32N | IX534/564/                             | 664/764                                                                                                   | Family Devices                                                                                                            |  |  |  |  |

| DC41c                                                                             | _                      | 10                 |          |                                        | 2.5V                                                                                                      | Watchdog Timer Current: ∆IWDT (Notes 3,6)                                                                                 |  |  |  |  |

| DC41d                                                                             | 5                      | _                  | μΑ       | _                                      | 3.3V                                                                                                      | Watchdog Timer Current: ∆IWDT (Note 3)                                                                                    |  |  |  |  |

| DC41e                                                                             | _                      | 20                 |          |                                        | 3.6V                                                                                                      | Watchdog Timer Current: ΔIWDT (Note 3)                                                                                    |  |  |  |  |

| DC42c                                                                             | _                      | 40                 |          |                                        | 2.5V                                                                                                      | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Notes 3,6)                                                                        |  |  |  |  |

| DC42d                                                                             | 23                     | _                  | μΑ       | _                                      | 3.3V RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) 3.6V RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3) |                                                                                                                           |  |  |  |  |

| DC42e                                                                             | _                      | 50                 |          |                                        |                                                                                                           |                                                                                                                           |  |  |  |  |

| DC43c                                                                             | _                      | 1300               |          |                                        | 2.5V                                                                                                      | ADC: ΔIADC (Notes 3,4,6)                                                                                                  |  |  |  |  |

| DC43d                                                                             | 1100                   | _                  | μΑ       | _                                      | 3.3V                                                                                                      | ADC: ΔIADC (Notes 3,4)                                                                                                    |  |  |  |  |

| DC43e                                                                             | _                      | 1300               |          |                                        | 3.6V ADC: ΔΙΑDC (Notes 3,4)                                                                               |                                                                                                                           |  |  |  |  |

**Note 1:** The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- **2:** Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- **4:** Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: Data is characterized at +70°C and not tested. Parameter is for design guidance only.

- **6:** This parameter is characterized, but not tested in manufacturing.

TABLE 32-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

|         |        |                                                                                                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                |     |                                                                     |                                                     |  |  |  |

|---------|--------|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------|-----|---------------------------------------------------------------------|-----------------------------------------------------|--|--|--|

| DC CHA  | RACTER | ISTICS                                                                                                         | Operatin                                                              |                |     | -40°C ≤ TA ≤ +85°C for Industrial<br>-40°C ≤ TA ≤ +105°C for V-temp |                                                     |  |  |  |

| Param.  | Symbol | Characteristic                                                                                                 | Min.                                                                  | Min. Typ. Max. |     |                                                                     | Conditions                                          |  |  |  |

| DO10    | Vol    | Output Low Voltage I/O Pins: 4x Sink Driver Pins - All I/O output pins not defined as 8x Sink Driver pins      | _                                                                     | _              | 0.4 | >                                                                   | IOL ≤ 10 mA, VDD = 3.3V                             |  |  |  |

|         |        | Output Low Voltage I/O Pins: 8x Sink Driver Pins - RC15                                                        | _                                                                     | _              | 0.4 | V                                                                   | $IOL \leq 15 \text{ mA}, \text{VDD} = 3.3 \text{V}$ |  |  |  |

| DO20    | Vон    | Output High Voltage I/O Pins: 4x Source Driver Pins - All I/O output pins not defined as 8x Source Driver pins | 2.4                                                                   | _              | _   | V                                                                   | IOH ≥ -10 mA, VDD = 3.3V                            |  |  |  |

|         |        | Output High Voltage I/O Pins: 8x Source Driver Pins - RC15                                                     | 2.4                                                                   | _              | _   | V                                                                   | IOH ≥ -15 mA, VDD = 3.3V                            |  |  |  |

|         |        | Output High Voltage                                                                                            | 1.5 <sup>(1)</sup>                                                    | _              | _   |                                                                     | IOH ≥ -14 mA, VDD = 3.3V                            |  |  |  |

|         |        | 4x Source Driver Pins - All I/O                                                                                | 2.0 <sup>(1)</sup>                                                    | _              | _   | V                                                                   | IOH ≥ -12 mA, VDD = 3.3V                            |  |  |  |

| DO20A   | \/OU1  | output pins not defined as 8x Sink Driver pins                                                                 | 3.0 <sup>(1)</sup>                                                    | _              | _   |                                                                     | IOH ≥ -7 mA, VDD = 3.3V                             |  |  |  |

| DOZUA   | VOITI  | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>                                                    | _              | _   | V                                                                   | IOH ≥ -22 mA, VDD = 3.3V                            |  |  |  |

|         |        | 8x Source Driver Pins - RC15                                                                                   | 2.0 <sup>(1)</sup>                                                    | _              | _   |                                                                     | IOH ≥ -18 mA, VDD = 3.3V                            |  |  |  |

| Note 1: |        | tors are characterized, but not too                                                                            | 3.0 <sup>(1)</sup>                                                    | _              |     |                                                                     | IOH ≥ -10 mA, VDD = 3.3V                            |  |  |  |

**Note 1:** Parameters are characterized, but not tested.

### TABLE 32-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHAR       | ACTERIS | псѕ                                                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |   |     |   |            |  |  |

|---------------|---------|-----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----|---|------------|--|--|

| Param.<br>No. | Symbol  | Characteristics                                           | Min. <sup>(1)</sup> Typical Max. L                                                                                                                                                                                                                |   |     |   | Conditions |  |  |

| BO10          | VBOR    | BOR Event on VDD transition high-to-low ( <b>Note 2</b> ) | 2.0                                                                                                                                                                                                                                               | _ | 2.3 | V | _          |  |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

<sup>2:</sup> This driver pin only applies to devices with less than 64 pins.

<sup>3:</sup> This driver pin only applies to devices with 64 pins.

TABLE 32-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        | RACTERIS | STICS             |                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-Temp |      |       |                         |  |  |  |

|---------------|----------|-------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------|--|--|--|

| Param.<br>No. | Symbol   | Charact           | eristics                  | Min. <sup>(1)</sup>                                                                                                                                                                                                                                 | Max. | Units | Conditions              |  |  |  |

| IM10          | TLO:SCL  | Clock Low Time    | 100 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                     | _    | μS    | _                       |  |  |  |

|               |          |                   | 400 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                     | _    | μS    | _                       |  |  |  |

|               |          |                   | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                                                                                                                                                                                                                     | _    | μS    |                         |  |  |  |

| IM11          | THI:SCL  | Clock High Time   | 100 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                     | _    | μS    |                         |  |  |  |

|               |          |                   | 400 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                     | _    | μS    | _                       |  |  |  |