Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f064ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|         |                      | Pin Nur         | nber <sup>(1)</sup> |                 | Din         | Buffer         |                                   |  |  |

|---------|----------------------|-----------------|---------------------|-----------------|-------------|----------------|-----------------------------------|--|--|

| Pin Nam | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                       |  |  |

| RA0     | _                    | 17              | G3                  | B9              | I/O         | ST             | PORTA is a bidirectional I/O port |  |  |

| RA1     | —                    | 38              | J6                  | A26             | I/O         | ST             |                                   |  |  |

| RA2     | —                    | 58              | H11                 | A39             | I/O         | ST             |                                   |  |  |

| RA3     | —                    | 59              | G10                 | B32             | I/O         | ST             |                                   |  |  |

| RA4     | —                    | 60              | G11                 | A40             | I/O         | ST             |                                   |  |  |

| RA5     | —                    | 61              | G9                  | B33             | I/O         | ST             |                                   |  |  |

| RA6     | —                    | 91              | C5                  | B51             | I/O         | ST             |                                   |  |  |

| RA7     | —                    | 92              | B5                  | A62             | I/O         | ST             |                                   |  |  |

| RA9     | —                    | 28              | L2                  | A21             | I/O         | ST             |                                   |  |  |

| RA10    |                      | 29              | K3                  | B17             | I/O         | ST             | ]                                 |  |  |

| RA14    |                      | 66              | E11                 | B36             | I/O         | ST             | ]                                 |  |  |

| RA15    | —                    | 67              | E8                  | A44             | I/O         | ST             |                                   |  |  |

| RB0     | 16                   | 25              | K2                  | B14             | I/O         | ST             | PORTB is a bidirectional I/O port |  |  |

| RB1     | 15                   | 24              | K1                  | A15             | I/O         | ST             |                                   |  |  |

| RB2     | 14                   | 23              | J2                  | B13             | I/O         | ST             |                                   |  |  |

| RB3     | 13                   | 22              | J1                  | A13             | I/O         | ST             |                                   |  |  |

| RB4     | 12                   | 21              | H2                  | B11             | I/O         | ST             |                                   |  |  |

| RB5     | 11                   | 20              | H1                  | A12             | I/O         | ST             |                                   |  |  |

| RB6     | 17                   | 26              | L1                  | A20             | I/O         | ST             |                                   |  |  |

| RB7     | 18                   | 27              | J3                  | B16             | I/O         | ST             |                                   |  |  |

| RB8     | 21                   | 32              | K4                  | A23             | I/O         | ST             |                                   |  |  |

| RB9     | 22                   | 33              | L4                  | B19             | I/O         | ST             |                                   |  |  |

| RB10    | 23                   | 34              | L5                  | A24             | I/O         | ST             | 1                                 |  |  |

| RB11    | 24                   | 35              | J5                  | B20             | I/O         | ST             | ]                                 |  |  |

| RB12    | 27                   | 41              | J7                  | B23             | I/O         | ST             | ]                                 |  |  |

| RB13    | 28                   | 42              | L7                  | A28             | I/O         | ST             | ]                                 |  |  |

| RB14    | 29                   | 43              | K7                  | B24             | I/O         | ST             |                                   |  |  |

| RB15    | 30                   | 44              | L8                  | A29             | I/O         | ST             |                                   |  |  |

| RC1     | —                    | 6               | D1                  | A5              | I/O         | ST             | PORTC is a bidirectional I/O port |  |  |

| RC2     | —                    | 7               | E4                  | B4              | I/O         | ST             |                                   |  |  |

| RC3     | —                    | 8               | E2                  | A6              | I/O         | ST             |                                   |  |  |

| RC4     |                      | 9               | E1                  | B5              | I/O         | ST             | ]                                 |  |  |

| RC12    | 39                   | 63              | F9                  | B34             | I/O         | ST             | ]                                 |  |  |

| RC13    | 47                   | 73              | C10                 | A47             | I/O         | ST             | ]                                 |  |  |

| RC14    | 48                   | 74              | B11                 | B40             | I/O         | ST             | ]                                 |  |  |

|         | -                    | 64              | F11                 | A42             | I/O         | ST             | 1                                 |  |  |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:46        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |

### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

### Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = device has 64 KB Flash 0x00020000 = device has 128 KB Flash 0x00040000 = device has 256 KB Flash 0x00080000 = device has 512 KB Flash

### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = device has 12 KB boot Flash

#### **Control Registers** 9.2

#### **TABLE 9-1:** PREFETCH REGISTER MAP

| ess                         |                         |               |                          |       |       |       |       |       |        | Bi      | ts                  |      |       |            |        |       |           |      |              |

|-----------------------------|-------------------------|---------------|--------------------------|-------|-------|-------|-------|-------|--------|---------|---------------------|------|-------|------------|--------|-------|-----------|------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range     | 31/15                    | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8    | 23/7                | 22/6 | 21/5  | 20/4       | 19/3   | 18/2  | 17/1      | 16/0 | All Resets   |

| 4000                        | CHECON <sup>(1,2)</sup> | 31:16         | :16 <u> C</u> H          |       |       |       |       |       |        | CHECOH  | 0000                |      |       |            |        |       |           |      |              |

| 4000                        | CHECON                  | 15:0          |                          | _     | —     | _     | _     | _     | DCSZ   | <1:0>   | _                   | —    | PREFE | N<1:0>     | _      | F     | PFMWS<2:0 | >    | 0007         |

| 4010                        | CHEACC <sup>(1)</sup>   | 31:16 CHEWEN  |                          |       |       |       |       |       |        | 0000    |                     |      |       |            |        |       |           |      |              |

| 4010                        |                         | 15:0          | —                        | —     | —     | —     | —     | —     | —      | —       | -                   | —    | —     | —          |        | CHEID | X<3:0>    |      | 0000         |

| 4020                        | CHETAG <sup>(1)</sup>   |               | LTAGBOOT                 | —     | —     | —     | —     | —     | —      | —       |                     |      |       | LTAG<      |        |       | -         |      | 00xx         |

| .020                        | 01121710                | 15:0          |                          |       |       |       |       | LTAG< | <15:4> |         |                     |      |       |            | LVALID | LLOCK | LTYPE     | —    | xxx2         |

| 4030                        | CHEMSK <sup>(1)</sup>   | 31:16         | —                        | _     | —     | —     | _     | —     |        | —       | —                   | —    | —     | _          | _      | _     |           | —    | 0000         |

|                             |                         | 15:0          | LMASK<15:5> — — — — 0000 |       |       |       |       |       |        |         | 0000                |      |       |            |        |       |           |      |              |

| 4040                        | CHEW0                   | 31:16         |                          |       |       |       |       |       |        | CHEWO   | )<31:0>             |      |       |            |        |       |           |      | XXXX         |

|                             |                         | 15:0          |                          |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |      | XXXX         |

| 4050                        | CHEW1                   | 31:16         |                          |       |       |       |       |       |        | CHEW1   | <31:0>              |      |       |            |        |       |           |      | XXXX         |

|                             |                         | 15:0          |                          |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |      | XXXX         |

| 4060                        | CHEW2                   | 31:16<br>15:0 |                          |       |       |       |       |       |        | CHEW2   | 2<31:0>             |      |       |            |        |       |           |      | XXXX         |

|                             |                         | 31:16         |                          |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |      | xxxx<br>xxxx |

| 4070                        | CHEW3                   | 15:0          |                          |       |       |       |       |       |        | CHEWS   | 8<31:0>             |      |       |            |        |       |           |      | XXXX         |

|                             |                         | 31:16         | _                        | _     | _     | _     | _     | _     | _      |         |                     |      | CI    | HELRU<24:1 | 6>     |       |           |      | 0000         |

| 4080                        | CHELRU                  | 15:0          |                          |       |       |       |       |       |        | CHELR   | J<15:0>             |      | 0.    |            |        |       |           |      | 0000         |

|                             |                         | 31:16         |                          |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |      | xxxx         |

| 4090                        | CHEHIT                  | 15:0          |                          |       |       |       |       |       |        | CHEHI   | <sup>-</sup> <31:0> |      |       |            |        |       |           |      | xxxx         |

|                             |                         | 31:16         |                          |       |       |       |       |       |        |         |                     |      |       |            |        |       |           |      | xxxx         |

| 40A0                        | CHEMIS                  | 15:0          |                          |       |       |       |       |       |        | CHEMIS  | 5<31:0>             |      |       |            |        |       |           |      | xxxx         |

| 4000                        | CHEPFABT                | 31:16         |                          |       |       |       |       |       |        | CHEPFAI | OT -21-0-           |      |       |            |        |       |           |      | xxxx         |

| 4000                        | CHEFFABI                | 15:0          |                          |       |       |       |       |       |        | UNEPFAI | 51<31.0>            |      |       |            |        |       |           |      | xxxx         |

Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Reset value is dependent on DEVCFGx configuration. 1:

2:

Note

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

### REGISTER 11-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | -                 | —                        | —                 | _                     | -                     | —                | —                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         |                   |                   | —                        | —                 |                       |                       | —                | —                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | TATE SE0          | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              |                   |                   | TOKBUSY <sup>(1,5)</sup> |                   |                       |                       |                  | SOFEN <sup>(5)</sup> |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = JSTATE was not detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-ended zero was detected on the USB

0 = Single-ended zero was not detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

- bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- **2:** All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit(5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

### REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | —                 |                   |                   |                   |                   |                  | —                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           |                   |                   |                  | UASUSPND         |

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | read as '0'        |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

- bit 6 **UOEMON:** USB OE Monitor Enable bit

- $1 = \overline{OE}$  signal is active; it indicates intervals during which the D+/D- lines are driving

- $0 = \overline{OE}$  signal is inactive

- bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 3-1 Unimplemented: Read as '0'

### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| Т | ABLE 12 | PORTG REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H | Н. |

|---|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |         | PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES                                                                                                                   | ,  |

|   | ŝ       | Bits                                                                                                                                                                                            |    |

| ö                          |                                 | Φ         |       | 9 No. 10 |       |       |       |       |        |        |        | <i>(</i> 0 |      |      |        |        |      |      |           |

|----------------------------|---------------------------------|-----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|-------|-------|--------|--------|--------|------------|------|------|--------|--------|------|------|-----------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29/13 | 28/12 | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6       | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Reset |

| 6180                       | TRISG                           | 31:16     | —     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —     | _     | —     | —     | _      | —      | —      | —          | _    | _    | -      | _      | _    | _    | 0000      |

| 6160                       | TRIBU                           | 15:0      | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | _     |       | TRISG9 | TRISG8 | TRISG7 | TRISG6     | _    |      | TRISG3 | TRISG2 | -    |      | 03CC      |

| 6100                       | PORTG                           | 31:16     | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | _     |       | _      | _      | _      | _          | _    |      |        |        | -    |      | 0000      |

| 6190                       | PURIG                           | 15:0      | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | _     |       | RG9    | RG8    | RG7    | RG6        | _    |      | RG3    | RG2    | -    |      | xxxx      |

| 61A0                       | LATG                            | 31:16     | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | _     |       | _      | _      | _      | _          | _    |      |        |        | -    |      | 0000      |

| OTAU                       | LAIG                            | 15:0      | _     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | _     |       | LATG9  | LATG8  | LATG7  | LATG6      | _    |      | LATG3  | LATG2  | -    |      | xxxx      |

| 61B0                       | ODCG                            | 31:16     | -     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | -     | _     | _      | _      | _      | -          | _    |      |        | -      | _    |      | 0000      |

| 0180                       | ODCG                            | 15:0      | -     | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _     | _     | -     | _     | ODCG9  | ODCG8  | ODCG7  | ODCG6      | _    |      | ODCG3  | ODCG2  | _    |      | 0000      |

| Laware                     |                                 |           |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |       |       |       |        |        |        |            |      |      |        |        |      |      |           |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

### TABLE 12-12: PORTG REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 |           |         |         |         |         |       |       |        | Bi     | ts     |        |      |      |        |        |        |        | <i>(</i> 0 |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG                           | 31:16     | _       | —       | _       | -       | _     | —     | -      | —      | —      | -      | —    | -    | -      | -      | -      | -      | 0000       |

| 0100                        | TRISG                           | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _     | _     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF       |

| 6100                        | PORTG                           | 31:16     |         | _       |         | _       |       | -     | -      | -      | -      | —      | -    | —    | —      | —      | _      | —      | 0000       |

| 6190                        | PURIG                           | 15:0      | RG15    | RG14    | RG13    | RG12    |       |       | RG9    | RG8    | RG7    | RG6    |      | -    | RG3    | RG2    | RG1    | RG0    | xxxx       |

| 61A0                        | LATG                            | 31:16     | -       | _       |         | _       | -     | -     | -      | -      | -      | —      | -    | —    | —      | —      | —      | —      | 0000       |

| 61A0                        | LAIG                            | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | _    | -    | LATG3  | LATG2  | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG                            | 31:16     |         | —       | _       | _       |       | _     |        | _      | _      | —      | _    | —    | —      | —      | —      | —      | 0000       |

| 0160                        | ODCG                            | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | -    | _    | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

### TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |         |        |       |        | •      |              |               | Bi      | ts    |             |             |           |          |        |      |          |            |

|-----------------------------|---------------------------------|---------------|---------|--------|-------|--------|--------|--------------|---------------|---------|-------|-------------|-------------|-----------|----------|--------|------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13 | 28/12  | 27/11  | 26/10        | 25/9          | 24/8    | 23/7  | 22/6        | 21/5        | 20/4      | 19/3     | 18/2   | 17/1 | 16/0     | All Resets |

| 5230                        | I2C5MSK                         | 31:16         | -       | —      | —     | _      |        | _            | —             | -       | _     | _           |             | _         | —        | —      | _    |          | 0000       |

| 5230                        | IZCONISK                        | 15:0          | -       | —      | —     | -      |        | _            |               |         |       |             | MSK         | <9:0>     |          |        |      | -        | 0000       |

| 5240                        | I2C5BRG                         | 31:16         | _       | _      | _     | —      | _      | —            | —             | —       | _     | —           | _           | —         | _        |        | -    | _        | 0000       |

| 5240                        |                                 | 15:0          | —       | —      | —     | —      |        |              |               |         | Ba    | ud Rate Ger | erator Regi | ster      |          |        | •    |          | 0000       |

| 5250                        | I2C5TRN                         | 31:16         | —       | —      | —     | —      | _      | —            | _             | —       | _     | —           | —           | —         | —        |        | —    | —        | 0000       |

| 0200                        |                                 | 15:0          | —       | _      | _     | —      | _      | —            | _             | _       |       | -           |             | Transmit  | Register |        | •    |          | 0000       |

| 5260                        | I2C5RCV                         | 31:16         | -       |        |       | —      | _      | —            |               | _       | _     | —           | —           | —         |          | _      | —    | _        | 0000       |

|                             |                                 | 15:0          | -       |        | —     | —      |        | —            |               | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| 5300                        | I2C1CON                         | 31:16         | _       | —      | —     | —      | —      | —            | —             | —       | _     | —           | —           | —         | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | ON      | _      | SIDL  | SCLREL | STRICT | A10M         | DISSLW        | SMEN    | GCEN  | STREN       | ACKDT       | ACKEN     | RCEN     | PEN    | RSEN | SEN      | 1000       |

| 5310                        | I2C1STAT                        | 31:16         | —       | _      | _     | _      | _      | _            | —             | —       | _     | —           | —           | _         | _        |        | —    | _        | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT | —     | —      | —      | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5320                        | I2C1ADD                         | 31:16         | _       | _      | —     | —      | _      |              | —             |         | _     | _           |             | _         | —        |        | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _      | -            |               |         |       |             | ADD         | <9:0>     |          |        |      |          | 0000       |

| 5330                        | I2C1MSK                         | 31:16         | _       | _      | _     | _      | _      | -            | _             | -       | _     | _           | —           | -         | _        | -      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       |        | _     | _      |        | _            |               |         |       |             | MSK         | <9:0>     |          |        |      |          | 0000       |

| 5340                        | I2C1BRG                         | 31:16         | _       |        |       | —      | _      | —            |               | _       | -     | -           |             | _         | —        |        | -    | _        | 0000       |

| -                           |                                 | 15:0          | _       |        |       | —      |        |              |               |         | Ва    | ud Rate Ger | Ū.          | ster      |          |        | 1    |          | 0000       |

| 5350                        | I2C1TRN                         | 31:16         | _       | —      | —     | _      | _      | _            | _             | _       | _     | _           | —           |           | —        | —      | —    | —        | 0000       |

|                             |                                 | 15:0          | _       | _      | _     | _      | _      | _            |               | _       |       |             |             | Transmit  | Register |        |      |          | 0000       |

| 5360                        | I2C1RCV                         | 31:16<br>15:0 | _       | _      |       |        |        | —            |               |         | —     | —           | —           | - Deseive |          | —      | —    | —        | 0000       |

|                             |                                 |               |         |        |       |        |        | _            |               |         |       |             |             | Receive   |          |        |      |          |            |

| 5400                        | 12C2CON(2)                      | 31:16<br>15:0 | ON      |        | -     | -      |        | -            | —<br>DI001144 | -       | -     | —<br>STREN  | —<br>ACKDT  |           |          | -      |      | -        | 0000       |

|                             |                                 |               |         | _      | SIDL  | SCLREL | STRICT | A10M         | DISSLW        | SMEN    | GCEN  |             |             |           |          | PEN    | RSEN | SEN      | 1000       |

| 5410                        | 12C2STAT <sup>(2)</sup>         | 31:16         |         |        | _     | _      | _      | —<br>DCI     | —<br>         | -       | -     | -           | —<br>D/A    | —<br>P    | -        | —<br>• | -    | —<br>TDF | 0000       |

|                             |                                 | 15:0<br>31:16 | ACKSTAT | TRSTAT |       | _      | _      | BCL          | GCSTAT        | ADD10   | IWCOL | I2COV       | D/A         | Р         | S        | R/W    | RBF  | TBF      | 0000       |

| 5420                        | 12C2ADD(2)                      | 15:0          |         |        |       | _      | _      |              | _             | -       | —     | —           |             | <br><9:0> | —        |        | _    | —        | 0000       |

|                             |                                 | 31:16         | _       |        |       | _      |        | _            | _             |         | _     |             | ADD         | <9.0>     |          |        | _    | _        | 0000       |

| 5430                        | 12C2MSK <sup>(2)</sup>          | 15:0          |         |        |       |        |        |              | _             | _       | _     | _           | <br>MSK     | <0.0>     | _        |        | _    | _        | 0000       |

|                             |                                 | 31:16         |         |        |       |        |        |              |               |         | _     |             |             | < 3.02    |          |        |      | _        | 0000       |

| 5440                        | I2C2BRG <sup>(2)</sup>          | 15:0          | _       |        |       | _      | _      | _            | _             |         | Ra    | ud Rate Ger | erator Regi | ster      |          |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      | _      | _            | _             | _       | Da    |             |             |           | _        |        | _    | _        | 0000       |

| 5450                        | I2C2TRN <sup>(2)</sup>          | 15:0          | _       | _      | _     | _      | _      |              | _             |         |       |             |             | Transmit  | Register |        |      |          | 0000       |

|                             |                                 | 31:16         | _       | _      | _     | _      |        | _            | _             | _       |       | _           | _           |           |          |        | _    | _        | 0000       |

| 5460                        | 12C2RCV <sup>(2)</sup>          | 15:0          | _       | _      | _     | _      | _      | _            | _             | _       |       |             |             | Receive   | Register |        |      |          | 0000       |

| Legen                       |                                 |               |         |        |       |        |        | Les are show | l<br>         | aire al |       |             |             | 110001100 |          |        |      |          | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   |                   |                   |                  | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

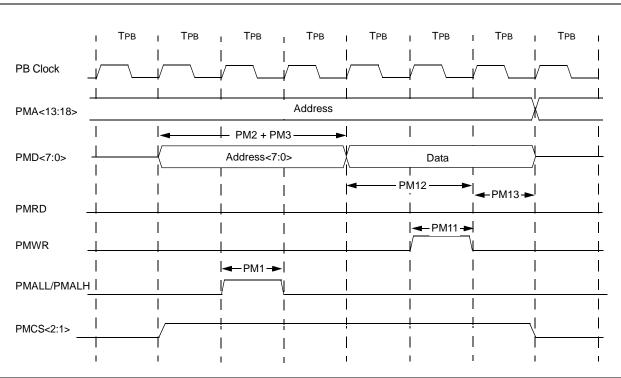

### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (ONLY SLAVE MODES)

| Legend:           | HS = Set by Hardware | SC = Cleared by software  |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **IBF:** Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

- 0 = An overflow has not occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = An underflow has not occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

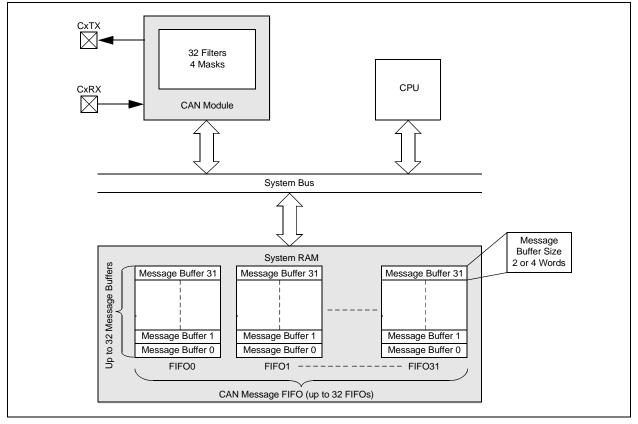

### 24.0 CONTROLLER AREA NETWORK (CAN)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 34. "Controller Area Network (CAN)" (DS60001154) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Controller Area Network (CAN) module supports the following key features:

- Standards Compliance:

- Full CAN 2.0B compliance

- Programmable bit rate up to 1 Mbps

- Message Reception and Transmission:

- 32 message FIFOs

- Each FIFO can have up to 32 messages for a total of 1024 messages

- FIFO can be a transmit message FIFO or a receive message FIFO

- User-defined priority levels for message FIFOs used for transmission

- 32 acceptance filters for message filtering

- Four acceptance filter mask registers for message filtering

- Automatic response to remote transmit request

- DeviceNet<sup>™</sup> addressing support

- Additional Features:

- Loopback, Listen All Messages, and Listen Only modes for self-test, system diagnostics and bus monitoring

- Low-power operating modes

- CAN module is a bus master on the PIC32 system bus

- Use of DMA is not required

- Dedicated time-stamp timer

- Dedicated DMA channels

- Data-only Message Reception mode

Figure 24-1 illustrates the general structure of the CAN module.

### FIGURE 24-1: PIC32 CAN MODULE BLOCK DIAGRAM