Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f064l-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

1

#### TABLE 9: PIN NAMES FOR 100-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

#### **100-PIN TQFP (TOP VIEW)**

PIC32MX764F128L PIC32MX775F256L PIC32MX775F512L PIC32MX795F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name                        |

|-------|---------------------------------|-------|--------------------------------------|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD                                  |

| 72    | SDO1/OC1/INT0/RD0               | 87    | C1RX/ETXD1/PMD11/RF0                 |

| 73    | SOSCI/CN1/RC13                  | 88    | C1TX/ETXD0/PMD10/RF1                 |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1 |

| 75    | Vss                             | 90    | C2RX <sup>(1)</sup> /PMD8/RG0        |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6                            |

| 77    | OC3/RD2                         | 92    | TRD3/RA7                             |

| 78    | OC4/RD3                         | 93    | PMD0/RE0                             |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1                             |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14                            |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12                            |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13                            |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2                             |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3                             |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4                             |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                              | Pin Nun         | nber <sup>(1)</sup> |                 | Pin         | Buffer               |                                                                                                |  |  |  |

|----------|----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|------------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                           | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Ріп<br>Туре | Type                 | Description                                                                                    |  |  |  |

| TMS      | 23                                           | 17              | G3                  | B9              | I           | ST                   | JTAG Test mode select pin                                                                      |  |  |  |

| ТСК      | 27                                           | 38              | J6                  | A26             | I           | ST                   | JTAG test clock input pin                                                                      |  |  |  |

| TDI      | 28                                           | 60              | G11                 | A40             | I           | ST                   | JTAG test data input pin                                                                       |  |  |  |

| TDO      | 24                                           | 61              | G9                  | B33             | 0           |                      | JTAG test data output pin                                                                      |  |  |  |

| RTCC     | 42                                           | 68              | E9                  | B37             | 0           |                      | Real-Time Clock alarm output                                                                   |  |  |  |

| CVREF-   | 15                                           | 28              | L2                  | A21             | I           | Analog               | Comparator Voltage Reference (low)                                                             |  |  |  |

| CVREF+   | 16                                           | 29              | K3                  | B17             | I           | Analog               | Comparator Voltage Reference (high)                                                            |  |  |  |

| CVREFOUT | 23                                           | 34              | L5                  | A24             | 0           | Analog               | Comparator Voltage Reference output                                                            |  |  |  |

| C1IN-    | 12                                           | 21              | H2                  | B11             | I           | Analog               | Comparator 1 negative input                                                                    |  |  |  |

| C1IN+    | 11                                           | 20              | H1                  | A12             | I           | Analog               | Comparator 1 positive input                                                                    |  |  |  |

| C1OUT    | 21                                           | 32              | K4                  | A23             | 0           |                      | Comparator 1 output                                                                            |  |  |  |

| C2IN-    | 14                                           | 23              | J2                  | B13             | I           | Analog               | Comparator 2 negative input                                                                    |  |  |  |

| C2IN+    | 13                                           | 22              | J1                  | A13             | I           | Analog               | Comparator 2 positive input                                                                    |  |  |  |

| C2OUT    | 22                                           | 33              | L4                  | B19             | 0           |                      | Comparator 2 output                                                                            |  |  |  |

| PMA0     | 30                                           | 44              | L8                  | A29             | I/O         | TTL/ST               | Parallel Master Port Address bit 0 inpu<br>(Buffered Slave modes) and output<br>(Master modes) |  |  |  |

| PMA1     | 29                                           | 43              | K7                  | B24             | I/O         | TTL/ST               | Parallel Master Port Address bit 1 inpu<br>(Buffered Slave modes) and output<br>(Master modes) |  |  |  |

| PMA2     | 8                                            | 14              | F3                  | A9              | 0           | _                    | Parallel Master Port address                                                                   |  |  |  |

| PMA3     | 6                                            | 12              | F2                  | A8              | 0           |                      | (Demultiplexed Master modes)                                                                   |  |  |  |

| PMA4     | 5                                            | 11              | F4                  | B6              | 0           | _                    |                                                                                                |  |  |  |

| PMA5     | 4                                            | 10              | E3                  | A7              | 0           | _                    |                                                                                                |  |  |  |

| PMA6     | 16                                           | 29              | K3                  | B17             | 0           | —                    |                                                                                                |  |  |  |

| PMA7     | 22                                           | 28              | L2                  | A21             | 0           | —                    |                                                                                                |  |  |  |

| PMA8     | 32                                           | 50              | L11                 | A32             | 0           | _                    |                                                                                                |  |  |  |

| PMA9     | 31                                           | 49              | L10                 | B27             | 0           | _                    |                                                                                                |  |  |  |

| PMA10    | 28                                           | 42              | L7                  | A28             | 0           | _                    |                                                                                                |  |  |  |

| PMA11    | 27                                           | 41              | J7                  | B23             | 0           |                      |                                                                                                |  |  |  |

| PMA12    | 24                                           | 35              | J5                  | B20             | 0           |                      |                                                                                                |  |  |  |

| PMA13    | 23                                           | 34              | L5                  | A24             | 0           | _                    | 1                                                                                              |  |  |  |

| PMA14    | 45                                           | 71              | C11                 | A46             | 0           | _                    | 1                                                                                              |  |  |  |

| PMA15    | 44                                           | 70              | D11                 | B38             | 0           | _                    | 1                                                                                              |  |  |  |

| PMCS1    | 45                                           | 71              | C11                 | A46             | 0           |                      | Parallel Master Port Chip Select 1<br>strobe                                                   |  |  |  |

| PMCS2    | 44                                           | 70              | D11                 | B38             | 0           | _                    | Parallel Master Port Chip Select 2 strobe                                                      |  |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt 1<br>TL = TTL inp | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input                                                          |  |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

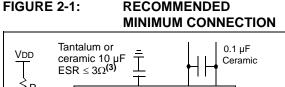

### **Note 1:** If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $3\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f = \frac{F_{CNV}}{2}$$

(i.e., ADC conversion rate/2)

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

3: Aluminum or electrolytic capacitors should not be used. ESR  $\leq 3\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

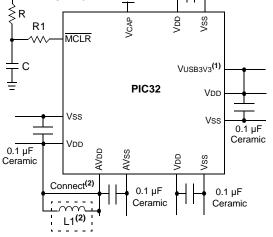

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 32.0 "Electrical Characteristics"** for additional information on CEFC specifications.

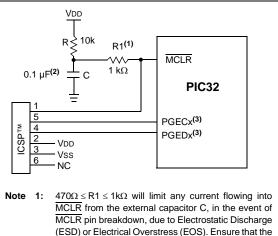

### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- **3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

NOTES:

## TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |            |             |              |             | Bi                    | its       |            |       |            |             |          |        |                      |            |              |  |           |       |       |       |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|------------|-------------|--------------|-------------|-----------------------|-----------|------------|-------|------------|-------------|----------|--------|----------------------|------------|--------------|--|-----------|-------|-------|-------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12      | 27/11       | 26/10        | 25/9        | 24/8                  | 23/7      | 22/6       | 21/5  | 20/4       | 19/3        | 18/2     | 17/1   | 16/0                 | All Resets |              |  |           |       |       |       |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |            | INT4IP<2:0> |              | INT4IS      | S<1:0>                | _         | —          | -     |            | OC4IP<2:0>  |          | OC4IS  | 6<1:0>               | 0000       |              |  |           |       |       |       |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |            | IC4IP<2:0>  |              | IC4IS       | <1:0>                 | _         | _          | _     |            | T4IP<2:0>   |          | T4IS-  | <1:0>                | 0000       |              |  |           |       |       |       |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |            | SPI1IP<2:0> |              | SPI1IS      | 6<1:0>                | _         | _          | _     |            | OC5IP<2:0>  |          | OC5IS  | S<1:0>               | 0000       |              |  |           |       |       |       |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |            | IC5IP<2:0>  |              | IC5IS       | <1:0>                 | -         |            | _     |            | T5IP<2:0>   |          | T5IS-  | <1:0>                | 0000       |              |  |           |       |       |       |      |

|                             |                                 | 31:16     | _     | _     | _     |            | AD1IP<2:0>  |              | AD1IS       | S<1:0>                | _         | _          | _     |            | CNIP<2:0>   |          | CNIS   | <1:0>                | 0000       |              |  |           |       |       |       |      |

| 10F0                        | IPC6                            |           |       |       |       |            |             |              |             |                       |           |            |       |            | U1IP<2:0>   |          | U1IS-  | <1:0>                |            |              |  |           |       |       |       |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |            | I2C1IP<2:0> |              | 12C115      | S<1:0>                | —         | —          | —     |            | SPI3IP<2:0> | •        | SPI3IS | S<1:0>               | 0000       |              |  |           |       |       |       |      |

|                             |                                 |           |       |       |       |            |             |              |             |                       |           |            |       |            | I2C3IP<2:0> |          | 12C315 | S<1:0>               |            |              |  |           |       |       |       |      |

|                             |                                 |           |       |       |       |            | U3IP<2:0>   |              | U3IS        | <1:0>                 |           |            |       |            |             |          |        |                      |            |              |  |           |       |       |       |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |            | SPI2IP<2:0> |              | SPI2IS      | S<1:0>                | —         | —          | —     | (          | CMP2IP<2:0  | >        | CMP2I  | S<1:0>               | 0000       |              |  |           |       |       |       |      |

| 1100                        | 11 07                           |           |       |       |       |            | I2C4IP<2:0> |              | I2C4IS<1:0: |                       |           |            |       | L          |             | <u> </u> |        |                      |            |              |  |           |       |       |       |      |

|                             |                                 | 15:0      | _     |       |       | (          | CMP1IP<2:0  | >            | CMP1I       | S<1:0>                | _         | _          |       | PMPIP<2:0> |             | PMPIS    | S<1:0> | 0000                 |            |              |  |           |       |       |       |      |

|                             |                                 | 31:16     | _     |       |       | F          | RTCCIP<2:0  | >            | RTCCIS<1:0> |                       | _         | _          |       | I          | FSCMIP<2:0  | >        | FSCMI  | S<1:0>               | 0000       |              |  |           |       |       |       |      |

| 1110                        | IPC8                            |           |       |       |       |            |             |              |             |                       |           |            |       |            | U2IP<2:0>   |          | U2IS-  | <1:0>                |            |              |  |           |       |       |       |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |            | I2C2IP<2:0> |              | 12C215      | 6<1:0>                | —         | —          | —     |            | SPI4IP<2:0> |          | SPI4IS | S<1:0>               | 0000       |              |  |           |       |       |       |      |

|                             |                                 |           |       |       |       |            |             |              |             |                       |           |            |       |            | I2C5IP<2:0> |          | 12C515 | S<1:0>               |            |              |  |           |       |       |       |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |            | DMA3IP<2:0  |              | DMA3I       | S<1:0>                | _         |            |       |            | DMA2IP<2:0  |          | DMA2I  | S<1:0>               | 0000       |              |  |           |       |       |       |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |            | DMA1IP<2:0  |              | DMA1I       |                       | _         |            |       |            | DMA0IP<2:0  |          | DMA0I  | S<1:0>               | 0000       |              |  |           |       |       |       |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI         | MA7IP<2:0>  | (2)          | DMA7IS      | i<1:0> <sup>(2)</sup> | —         | _          | —     | D          | MA6IP<2:0>  | (2)      | DMA6IS | <1:0> <sup>(2)</sup> | 0000       |              |  |           |       |       |       |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI         | MA5IP<2:0>  | (2)          | DMA5IS      | i<1:0> <sup>(2)</sup> | _         | _          | —     | D          | MA4IP<2:0>  | (2)      | DMA4IS | <1:0> <sup>(2)</sup> | 0000       |              |  |           |       |       |       |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _          | _           |              | _           |                       |           |            | _     | _          | —           |          | —      |                      | 0000       |              |  |           |       |       |       |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     | USBIP<2:0> |             | - USBIP<2:0> |             | USBIP<2:0>            |           | USBIP<2:0> |       | S<1:0>     | _           | _        | —      | - FCEIP<2:0>         |            | — FCEIP<2:0> |  | FCEIS     | <1:0> | 0000  |       |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |            | U5IP<2:0>   |              | U5IP<2:0>   |                       | U5IP<2:0> |            | U5IS- | <1:0>      | _           |          | -      | U6IP<2:0>            |            | U6IP<2:0>    |  | U6IP<2:0> |       | U6IS- | <1:0> | 0000 |

| 1150                        | IFUIZ                           | 15:0      | _     | -     |       |            | U4IP<2:0>   |              | U4IS-       | <1:0>                 |           |            |       |            | ETHIP<2:0>  |          | ETHIS  | i<1:0>               | 0000       |              |  |           |       |       |       |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 **SOSCEN:** Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

#### bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | —                 |                   |                   |                   |                   |                  | —                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           |                   |                   |                  | UASUSPND         |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

- bit 6 **UOEMON:** USB OE Monitor Enable bit

- $1 = \overline{OE}$  signal is active; it indicates intervals during which the D+/D- lines are driving

- $0 = \overline{OE}$  signal is inactive

- bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | —                 | _                 |                   | —                 | —                 | —                | —                |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   |                   | DAY01             | <3:0>            |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   | _                 | _                 |                   |                   | WDAY0             | )1<3:0>          |                  |  |  |

#### REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

### Legend:

| Logona.           |                  |                        |                    | 1 |

|-------------------|------------------|------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        | I |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |   |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1 digit; contains a value from 0 to 6

#### **Control Registers** 24.1

#### TABLE 24-1: CAN1 REGISTER SUMMARY FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

PIC32MX5XX/6XX/7XX

| ess                         |                                 |           |          |          |         |           |         |             |           | Bit       | 5        |          |          |          |           |            |           |          |            |

|-----------------------------|---------------------------------|-----------|----------|----------|---------|-----------|---------|-------------|-----------|-----------|----------|----------|----------|----------|-----------|------------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14    | 29/13   | 28/12     | 27/11   | 26/10       | 25/9      | 24/8      | 23/7     | 22/6     | 21/5     | 20/4     | 19/3      | 18/2       | 17/1      | 16/0     | All Resets |

| B000                        | C1CON                           | 31:16     | —        | —        | —       | —         | ABAT    |             | REQOP<2:0 | >         | C        | PMOD<2:0 | >        | CANCAP   |           | _          | —         | —        | 0480       |

| DUUU                        | CICON                           | 15:0      | ON       | _        | SIDLE   | _         | CANBUSY | _           | —         | _         | _        | _        | _        |          | D         | NCNT<4:0>  |           |          | 0000       |

| B010                        | C1CFG                           | 31:16     | —        | _        | _       | —         | _       | _           | —         | _         | _        | WAKFIL   | _        | —        | _         |            | EG2PH<2:0 | >        | 0000       |

| DUIU                        | CICIO                           | 15:0      | SEG2PHTS | SAM      | -       | EG1PH<2:0 |         | I           | PRSEG<2:0 | >         | SJW      | <1:0>    |          |          | BRP<      |            |           |          | 0000       |

| B020                        | C1INT                           | 31:16     | IVRIE    | WAKIE    | CERRIE  | SERRIE    | RBOVIE  | _           | —         | _         | _        | _        | _        | _        | MODIE     | CTMRIE     | RBIE      | TBIE     | 0000       |

| D020                        | Onivi                           | 15:0      | IVRIF    | WAKIF    | CERRIF  | SERRIF    | RBOVIF  | _           | —         | _         | _        | _        | _        | _        | MODIF     | CTMRIF     | RBIF      | TBIF     | 0000       |

| B030                        | C1VEC                           | 31:16     | —        | _        | —       | _         | _       | _           | —         | _         | _        | _        | —        | —        | _         | _          | -         | -        | 0000       |

| D030                        | CIVEC                           | 15:0      | —        | _        | —       |           | -       | FILHIT<4:0: | >         |           |          |          |          | 10       | CODE<6:0> |            | -         |          | 0040       |

| B040                        | C1TREC                          | 31:16     | —        | _        | —       | —         | _       | _           | —         | _         | _        | —        | TXBO     | TXBP     | RXBP      | TXWARN     | RXWARN    | EWARN    | 0000       |

| D040                        | OTINEO                          | 15:0      |          |          | -       | TERRC     | NT<7:0> |             |           |           |          |          |          | RERRCN   | IT<7:0>   |            | -         |          | 0000       |

| B050                        | C1FSTAT                         | 31:16     | FIFOIP31 | FIFOIP30 |         | FIFOIP28  | -       | FIFOIP26    | FIFOIP25  | FIFOIP24  | FIFOIP23 | FIFOIP22 | FIFOIP21 | FIFOIP20 | FIFOIP19  | FIFOIP18   | FIFOIP17  | FIFOIP16 | 0000       |

| D030                        | CHISTAI                         |           |          | FIFOIP14 |         | FIFOIP12  |         | FIFOIP10    | FIFOIP9   | FIFOIP8   | FIFOIP7  | FIFOIP6  | FIFOIP5  | FIFOIP4  | FIFOIP3   | FIFOIP2    | FIFOIP1   | FIFOIP0  | 0000       |

| B060                        | C1RXOVF                         |           |          |          | RXOVF29 |           |         |             |           | RXOVF24   | RXOVF23  | RXOVF22  | RXOVF21  | RXOVF20  | RXOVF19   | RXOVF18    | RXOVF17   | RXOVF16  | 0000       |

| D000                        | CIRAOVI                         | 15:0      | RXOVF15  | RXOVF14  | RXOVF13 | RXOVF12   | RXOVF11 | RXOVF10     | RXOVF9    | RXOVF8    | RXOVF7   | RXOVF6   | RXOVF5   | RXOVF4   | RXOVF3    | RXOVF2     | RXOVF1    | RXOVF0   | 0000       |

| B070                        | C1TMR                           | 31:16     |          |          |         |           |         |             |           | CANTS<    |          |          |          |          |           |            |           |          | 0000       |

| DOIO                        | OTTWIC                          | 15:0      |          |          |         |           |         |             | CA        | NTSPRE<15 | :0>      |          |          |          |           |            |           |          | 0000       |

| B080                        | C1RXM0                          | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          |          | MIDE      | -          | EID<1     | 7:16>    | xxxx       |

| DUUU                        | OTIVINO                         | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

| B090                        | C1RXM1                          | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          |          | MIDE      | —          | EID<1     | 7:16>    | xxxx       |

| D030                        | CIICAI                          | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

| BOVO                        | C1RXM2                          | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          | -        | MIDE      | -          | EID<1     | 7:16>    | xxxx       |

| B0A0                        | CIRAMZ                          | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

|                             | 0402440                         | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          |          | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

| B0B0                        | C1RXM3                          | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

|                             |                                 | 31:16     | FLTEN3   | MSEL:    | 3<1:0>  |           |         |             |           |           |          |          |          | 0000     |           |            |           |          |            |

| R0C0                        | C1FLTCON0                       | 15:0      | FLTEN1   | MSEL     | 1<1:0>  |           |         |             |           |           |          |          | 0000     |          |           |            |           |          |            |

|                             |                                 | 31:16     | FLTEN7   | MSEL     | 7<1:0>  |           |         | FSEL7<4:0:  | >         |           | FLTEN6   | MSEL     | 6<1:0>   |          | F         | SEL6<4:0>  |           |          | 0000       |

| R0D0                        | C1FLTCON1                       | 15:0      | FLTEN5   |          |         |           |         |             |           |           |          | 0000     |          |          |           |            |           |          |            |

| DOFC                        |                                 | 31:16     | FLTEN11  | MSEL1    | 1<1:0>  |           |         | FSEL11<4:0  | >         |           | FLTEN10  | MSEL1    | 0<1:0>   |          | F         | SEL10<4:0> | <b>,</b>  |          | 0000       |

| R0F0                        | C1FLTCON2                       | 15:0      | FLTEN9   | MSEL     | 9<1:0>  |           |         |             |           |           |          |          |          |          |           | 0000       |           |          |            |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is 1 x Tq}

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

#### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 7     | FLTEN28: Filter 28 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 6-5   | MSEL28<1:0>: Filter 28 Mask Select bits                                                                                                                                        |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                             |

| bit 4-0   | FSEL28<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                     |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                         |

|              |                   |                       |                       |                      |                   | •                         |                  | ,                |

|--------------|-------------------|-----------------------|-----------------------|----------------------|-------------------|---------------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0                   | U-0                   | U-0                  | U-0               | U-0                       | U-0              | U-0              |

| 31.24        | —                 | —                     | —                     | _                    | —                 | —                         | _                | —                |

| 00.40        | U-0               | U-0                   | U-0                   | R/W-0                | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 23:16        | —                 | —                     | —                     |                      |                   | FSIZE<4:0> <sup>(1)</sup> | )                |                  |

| 15.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                | U-0               | U-0                       | U-0              | U-0              |

| 15:8         | —                 | FRESET                | UINC                  | DONLY <sup>(1)</sup> | —                 | —                         | _                | —                |

| 7.0          | R/W-0             | R-0                   | R-0                   | R-0                  | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup> | TXREQ             | RTREN                     | TXPR             | <1:0>            |

#### **REGISTER 24-20:** CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-21 Unimplemented: Read as '0'

| bit 20-16 FSIZE<4:0>: FIFO Size bits' | bit 20-16 | E<4:0>: FIFO Size bits <sup>(1)</sup> |

|---------------------------------------|-----------|---------------------------------------|

|---------------------------------------|-----------|---------------------------------------|

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep 00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

#### bit 15 Unimplemented: Read as '0'

#### bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

#### 0 = No effect

#### bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{When this bit is set the FIFO head will increment by a single message$  $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message$ When this bit is set the FIFO tail will increment by a single message $<math display="block">\frac{TXEN = 0}{When this bit is set the FIFO tail will increment by a single message }$

### bit 12 DONLY: Store Message Data Only bit<sup>(1)</sup>

$\frac{\text{TXEN} = 1:}{\text{This bit is not used and has no effect.}}$   $\frac{\text{TXEN} = 0:}{\text{TXEN} = 0:}$ (FIFO configured as a Receive FIFO)

- 1 =Only data bytes will be stored in the FIFO

- 0 = Full message is stored, including identifier

#### bit 11-8 Unimplemented: Read as '0'

- bit 7 **TXEN:** TX/RX Buffer Selection bit

- 1 = FIFO is a Transmit FIFO

- 0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

#### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |               |               |         |               |               |               | В             | its       |         |               |               |            |         |          |          | ŝ          |

|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|---------------|---------------|---------|---------------|---------------|---------------|---------------|-----------|---------|---------------|---------------|------------|---------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 31/15         | 30/14         | 29/13         | 28/12   | 27/11         | 26/10         | 25/9          | 24/8          | 23/7      | 22/6    | 21/5          | 20/4          | 19/3       | 18/2    | 17/1     | 16/0     | All Resets |

| 90E0                        | ETHSTAT                         | THSTAT         31:16         -         -         -         -         -         BUFCNT<7:0>           THSTAT         15:0         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - |               |               |               |         |               |               | _             | 0000          |           |         |               |               |            |         |          |          |            |

|                             | ETH                             | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _             |               | _             | _       |               |               | _             |               | _         |         | _             |               | _          | _       | _        |          | 0000       |

| 9100                        | RXOVFLOW                        | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |               |               |         |               |               |               | RXOVFLW       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

|                             | ETH                             | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _             | _             | _             | _       |               | _             | _             |               | _         | _       |               | _             |            |         |          | _        | 0000       |

| 9110                        | FRMTXOK                         | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |               |               |         |               |               |               | FRMTXOK       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9120                        | ETH                             | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | _             | -             |               | _       | _             | -             | —             | -             | _         | -       | _             | -             |            | _       | _        | —        | 0000       |

| 9120                        | SCOLFRM                         | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |               |               |         |               |               |               | SCOLFRM       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9130                        | ETH                             | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —             | _             | _             | —       | _             | _             | —             | —             | —         | —       | _             | _             | —          | —       | —        | —        | 0000       |

|                             | MCOLFRM                         | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |               |               |         |               |               |               | MCOLFRM       | CNT<15:0> |         |               |               |            |         |          |          | 0000       |

| 9140                        | ETH<br>FRMRXOK                  | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | —             | _             | —             | —       | _             | _             | —             | -             | -         | —       | _             | —             | —          | _       | —        | —        | 0000       |

|                             |                                 | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |               |               |         |               |               |               | FRMRXOK       |           |         |               |               |            |         |          |          | 0000       |

| 9150                        |                                 | 31:16<br>15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _             | —             |               | —       | _             | —             | _             | FCSERRO       |           | _       |               | —             | —          | _       | —        | —        | 0000       |

|                             | ETH                             | 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |               |               |               |         |               |               |               |               | _         | 0000    |               |               |            |         |          |          |            |

| 9160                        | ALGNERR                         | 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |               |               |         |               |               |               |               |           |         | 0000          |               |            |         |          |          |            |