Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f064lt-v-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX5XX/6XX/7XX

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                              | Pin Nun         | nber <sup>(1)</sup> |                 | Pin         | Buffer               |                                                                                                                                           |  |  |

|----------|----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                           | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Ріп<br>Туре | Type                 | Description                                                                                                                               |  |  |

| TMS      | 23                                           | 17              | G3                  | B9              | I           | ST                   | JTAG Test mode select pin                                                                                                                 |  |  |

| ТСК      | 27                                           | 38              | J6                  | A26             | I           | ST                   | JTAG test clock input pin                                                                                                                 |  |  |

| TDI      | 28                                           | 60              | G11                 | A40             | I           | ST                   | JTAG test data input pin                                                                                                                  |  |  |

| TDO      | 24                                           | 61              | G9                  | B33             | 0           |                      | JTAG test data output pin                                                                                                                 |  |  |

| RTCC     | 42                                           | 68              | E9                  | B37             | 0           |                      | Real-Time Clock alarm output                                                                                                              |  |  |

| CVREF-   | 15                                           | 28              | L2                  | A21             | I           | Analog               | Comparator Voltage Reference (low)                                                                                                        |  |  |

| CVREF+   | 16                                           | 29              | K3                  | B17             | I           | Analog               | Comparator Voltage Reference (high)                                                                                                       |  |  |

| CVREFOUT | 23                                           | 34              | L5                  | A24             | 0           | Analog               | Comparator Voltage Reference output                                                                                                       |  |  |

| C1IN-    | 12                                           | 21              | H2                  | B11             | I           | Analog               | Comparator 1 negative input                                                                                                               |  |  |

| C1IN+    | 11                                           | 20              | H1                  | A12             | I           | Analog               | Comparator 1 positive input                                                                                                               |  |  |

| C1OUT    | 21                                           | 32              | K4                  | A23             | 0           |                      | Comparator 1 output                                                                                                                       |  |  |

| C2IN-    | 14                                           | 23              | J2                  | B13             | I           | Analog               | Comparator 2 negative input                                                                                                               |  |  |

| C2IN+    | 13                                           | 22              | J1                  | A13             | I           | Analog               | Comparator 2 positive input                                                                                                               |  |  |

| C2OUT    | 22                                           | 33              | L4                  | B19             | 0           |                      | Comparator 2 output                                                                                                                       |  |  |

| PMA0     | 30                                           | 44              | L8                  | A29             | I/O         | TTL/ST               | Parallel Master Port Address bit 0 inpu<br>(Buffered Slave modes) and output<br>(Master modes)<br>Parallel Master Port Address bit 1 inpu |  |  |

| PMA1     | 29                                           | 43              | K7                  | B24             | I/O         | TTL/ST               |                                                                                                                                           |  |  |

| PMA2     | 8                                            | 14              | F3                  | A9              | 0           | _                    | Parallel Master Port address                                                                                                              |  |  |

| PMA3     | 6                                            | 12              | F2                  | A8              | 0           |                      | (Demultiplexed Master modes)                                                                                                              |  |  |

| PMA4     | 5                                            | 11              | F4                  | B6              | 0           | _                    |                                                                                                                                           |  |  |

| PMA5     | 4                                            | 10              | E3                  | A7              | 0           | _                    |                                                                                                                                           |  |  |

| PMA6     | 16                                           | 29              | K3                  | B17             | 0           | —                    |                                                                                                                                           |  |  |

| PMA7     | 22                                           | 28              | L2                  | A21             | 0           | —                    |                                                                                                                                           |  |  |

| PMA8     | 32                                           | 50              | L11                 | A32             | 0           | _                    |                                                                                                                                           |  |  |

| PMA9     | 31                                           | 49              | L10                 | B27             | 0           | _                    |                                                                                                                                           |  |  |

| PMA10    | 28                                           | 42              | L7                  | A28             | 0           | _                    |                                                                                                                                           |  |  |

| PMA11    | 27                                           | 41              | J7                  | B23             | 0           |                      |                                                                                                                                           |  |  |

| PMA12    | 24                                           | 35              | J5                  | B20             | 0           |                      |                                                                                                                                           |  |  |

| PMA13    | 23                                           | 34              | L5                  | A24             | 0           | _                    | 1                                                                                                                                         |  |  |

| PMA14    | 45                                           | 71              | C11                 | A46             | 0           | _                    | 1                                                                                                                                         |  |  |

| PMA15    | 44                                           | 70              | D11                 | B38             | 0           | _                    | 1                                                                                                                                         |  |  |

| PMCS1    | 45                                           | 71              | C11                 | A46             | 0           |                      | Parallel Master Port Chip Select 1<br>strobe                                                                                              |  |  |

| PMCS2    | 44                                           | 70              | D11                 | B38             | 0           | _                    | Parallel Master Port Chip Select 2 strobe                                                                                                 |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt 1<br>TL = TTL inp | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input                                                                                                     |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

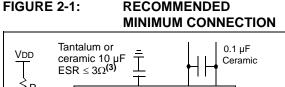

# **Note 1:** If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $3\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f = \frac{F_{CNV}}{2}$$

(i.e., ADC conversion rate/2)

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

3: Aluminum or electrolytic capacitors should not be used. ESR  $\leq 3\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

# 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

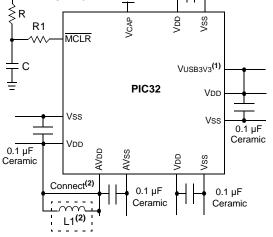

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

## 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 32.0 "Electrical Characteristics"** for additional information on CEFC specifications.

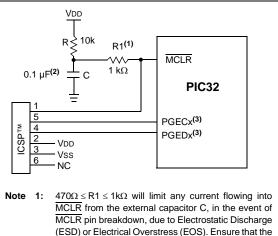

# 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

## FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- **3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

# 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

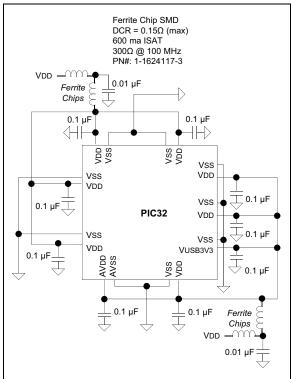

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

### FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

#### **TABLE 7-4:** INTERRUPT REGISTER MAP FOR PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |             |       |             | B                     | ts     |        |      |             |             |      |             |                       |            |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|-------------|-----------------------|--------|--------|------|-------------|-------------|------|-------------|-----------------------|------------|--------|------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|-----------|--|------|-------|--|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9        | 24/8                  | 23/7   | 22/6   | 21/5 | 20/4        | 19/3        | 18/2 | 17/1        | 16/0                  | All Resets |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 10D0                        | IPC4                            | 31:16     | _     | -     | —     |       | INT4IP<2:0> |       | INT4IS      | S<1:0>                | _      | —      | —    |             | OC4IP<2:0>  |      | OC4IS       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1000                        | IFC4                            | 15:0      | _     | _     | _     |       | IC4IP<2:0>  |       | IC4IS       | <1:0>                 |        | _      | _    |             | T4IP<2:0>   |      | T4IS        | <1:0>                 | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 10E0                        | IPC5                            | 31:16     | _     |       |       |       | -           |       | -           | _                     | _      |        | —    |             | OC5IP<2:0>  |      | OC5IS       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| IUEU                        | IFC5                            | 15:0      | _     | _     |       |       | IC5IP<2:0>  |       | IC5IS       | <1:0>                 | -      |        | _    |             | T5IP<2:0>   |      | T5IS        | <1:0>                 | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|                             |                                 | 31:16     | _     | _     | _     |       | AD1IP<2:0>  |       | AD1IS       | 6<1:0>                |        | _      | _    |             | CNIP<2:0>   |      | CNIS        | <1:0>                 | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 10F0                        | IPC6                            |           |       |       |       |       |             |       |             |                       |        |        |      |             | U1IP<2:0>   |      | U1IS        | <1:0>                 |            |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| TUFU                        | IPC6                            | 15:0      | —     | _     | _     |       | I2C1IP<2:0> |       | I2C1IS<1:0> |                       | _      | _      | _    |             | SPI3IP<2:0> |      | SPI3IS      | 6<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|                             |                                 |           |       |       |       |       |             |       |             |                       |        |        |      | 12C3IP<2:0> |             |      | 12C31       | 6<1:0>                | 1          |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|                             |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS<1:0>   |                       |        |        |      |             |             |      |             |                       |            |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1100                        | IPC7                            | 31:16     | —     | —     | _     |       | SPI2IP<2:0> |       | SPI2IP<2:0> |                       | SPI2IS | S<1:0> | —    | _           | —           | (    | CMP2IP<2:0: | >                     | CMP2I      | S<1:0> | 0000 |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1100                        | IFC7                            |           |       |       |       |       | I2C4IP<2:0> |       | 12C418      | S<1:0>                |        |        |      |             |             |      |             |                       |            |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|                             |                                 | 15:0      | _     |       |       | (     | CMP1IP<2:0> |       | CMP1I       | S<1:0>                | _      |        | —    |             | PMPIP<2:0>  | •    | PMPIS       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|                             |                                 | 31:16     | _     | _     |       | F     | RTCCIP<2:0  | >     | RTCCI       | RTCCIS<1:0>           |        |        | _    | F           | SCMIP<2:0   | >    | FSCMI       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1110                        | IPC8                            |           |       |       |       |       |             |       |             |                       |        |        |      |             |             |      |             |                       |            |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  | U2IP<2:0> |  | U2IS | <1:0> |  |

| 1110                        | IFCo                            | 15:0      | —     | —     | _     | _     | _           | —     | —           | —                     | _      | _      | —    |             | SPI4IP<2:0> |      | SPI4IS      | 6<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

|                             |                                 |           |       |       |       |       |             |       |             |                       |        |        |      |             | I2C5IP<2:0> |      | 12C518      | 6<1:0>                | 1          |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1120                        | IPC9                            | 31:16     |       | —     | -     | [     | DMA3IP<2:0  | >     | DMA3I       | S<1:0>                |        | -      | _    | [           | DMA2IP<2:0  | >    | DMA2I       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1120                        | IPC9                            | 15:0      | _     |       |       |       | DMA1IP<2:0  |       | DMA1I       | S<1:0>                | _      |        | —    | [           | DMA0IP<2:0  | >    | DMA0I       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1130                        | IPC10                           | 31:16     | _     | _     | _     | DI    | MA7IP<2:0>  | (2)   | DMA7IS      | S<1:0> <sup>(2)</sup> |        | _      | _    | D           | MA6IP<2:0>  | (2)  | DMA6IS      | i<1:0> <sup>(2)</sup> | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1130                        | IFC10                           | 15:0      | _     | _     | _     | DI    | MA5IP<2:0>  | (2)   | DMA5IS      | S<1:0> <sup>(2)</sup> | _      | _      | —    | D           | MA4IP<2:0>  | (2)  | DMA4IS      | i<1:0> <sup>(2)</sup> | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 11.10                       | IPC11                           | 31:16     | _     | _     |       | C     | AN2IP<2:0>  | (2)   | CAN2IS      | 5<1:0> <b>(2)</b>     | _      |        | —    | (           | CAN1IP<2:0: | >    | CAN1I       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1140                        | IPUTI                           | 15:0      | _     | _     | _     |       | USBIP<2:0>  |       | USBIS       | S<1:0>                | _      | _      | —    |             | FCEIP<2:0>  |      | FCEIS       | S<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1150                        | IPC12                           | 31:16     | _     | _     | _     |       | U5IP<2:0>   |       | U5IS        | <1:0>                 | _      | _      | _    |             | U6IP<2:0>   |      | U6IS        | <1:0>                 | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

| 1150                        | IPU12                           | 15:0      | _     | _     |       |       | U4IP<2:0>   |       | U4IS        | <1:0>                 | _      |        | —    |             | ETHIP<2:0>  |      | ETHIS       | 6<1:0>                | 0000       |        |      |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |           |  |      |       |  |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. This bit is unimplemented on PIC32MX764F128H device. This register does not have associated CLR, SET, and INV registers.

2:

3:

# TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |             |                               |                    |                            | Bi                    | its  |             |             |             |             |             |             |                      |            |             |  |   |   |  |             |  |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|-------------------------------|--------------------|----------------------------|-----------------------|------|-------------|-------------|-------------|-------------|-------------|-------------|----------------------|------------|-------------|--|---|---|--|-------------|--|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11                         | 26/10              | 25/9                       | 24/8                  | 23/7 | 22/6        | 21/5        | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                 | All Resets |             |  |   |   |  |             |  |        |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |             | INT4IP<2:0>                   | P<2:0> INT4IS<1:0> |                            | S<1:0>                | _    | —           | -           |             | OC4IP<2:0>  |             | OC4IS       | 6<1:0>               | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |             | IC4IP<2:0>                    |                    | IC4IS                      | <1:0>                 | _    | _           | _           |             | T4IP<2:0>   |             | T4IS-       | <1:0>                | 0000       |             |  |   |   |  |             |  |        |        |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |             | SPI1IP<2:0>                   |                    | SPI1IS                     | 6<1:0>                | _    | _           | _           |             | OC5IP<2:0>  |             | OC5IS       | S<1:0>               | 0000       |             |  |   |   |  |             |  |        |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |             | IC5IP<2:0>                    |                    | IC5IS                      | <1:0>                 | -    |             | _           |             | T5IP<2:0>   |             | T5IS-       | <1:0>                | 0000       |             |  |   |   |  |             |  |        |        |      |

|                             |                                 | 31:16     | _     | _     | _     |             | AD1IP<2:0>                    |                    | AD1IS                      | S<1:0>                | _    | _           | _           |             | CNIP<2:0>   |             | CNIS        | <1:0>                | 0000       |             |  |   |   |  |             |  |        |        |      |

| 10F0                        | IPC6                            |           |       |       |       |             |                               |                    |                            |                       |      |             |             |             | U1IP<2:0>   |             | U1IS-       | <1:0>                |            |             |  |   |   |  |             |  |        |        |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |             | I2C1IP<2:0>                   |                    | I2C1IS<1:0>                |                       | —    | —           | —           |             | SPI3IP<2:0> | •           | SPI3IS      | S<1:0>               | 0000       |             |  |   |   |  |             |  |        |        |      |

|                             |                                 |           |       |       |       |             | 1131P~2.0>                    |                    |                            | I2C3IP<2:0>           |      | I2C3IS<1:0> |             |             |             |             |             |                      |            |             |  |   |   |  |             |  |        |        |      |

|                             |                                 |           |       |       |       |             | U3IP<2:0>                     |                    | U3IS<1:0>                  |                       |      |             |             |             |             |             |             |                      |            |             |  |   |   |  |             |  |        |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |             | SPI2IP<2:0>                   |                    | SPI2IS<1:0>                |                       | —    | —           | —           | (           | CMP2IP<2:0  | >           | CMP2IS<1:0> |                      | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1100                        | 11 07                           |           |       |       |       | I2C4IP<2:0> |                               | 12C415             | S<1:0>                     |                       |      |             |             |             |             |             |             |                      |            |             |  |   |   |  |             |  |        |        |      |

|                             |                                 | 15:0      | _     |       |       | CMP1IP<2:0> |                               |                    |                            | CMP1IS<1:0>           |      | _           |             | PMPIP<2:0>  |             |             | PMPIS<1:0>  |                      | 0000       |             |  |   |   |  |             |  |        |        |      |

|                             |                                 | 31:16     | _     |       |       | F           | RTCCIP<2:0> RTCCIS<1:0> — — — |                    |                            | FSCMIP<2:0>           |      |             | FSCMIS<1:0> |             | 0000        |             |             |                      |            |             |  |   |   |  |             |  |        |        |      |

| 1110                        | IPC8                            |           |       |       |       |             |                               |                    |                            |                       |      |             |             |             |             |             | U2IP<2:0>   |                      | U2IS-      | <1:0>       |  |   |   |  |             |  |        |        |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |             | I2C2IP<2:0>                   |                    | 12C215                     | I2C2IS<1:0>           |      | I2C2IS<1:0> |             | I2C2IS<1:0> |             | I2C2IS<1:0> |             | I2C2IS<1:0>          |            | I2C2IS<1:0> |  | — | — |  | SPI4IP<2:0> |  | SPI4IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |             |                               |                    |                            |                       |      |             |             |             | I2C5IP<2:0> |             | 12C515      | S<1:0>               |            |             |  |   |   |  |             |  |        |        |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |             | DMA3IP<2:0                    |                    | DMA3I                      | S<1:0>                | _    |             |             |             | DMA2IP<2:0  |             | DMA2I       | S<1:0>               | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |             | DMA1IP<2:0                    |                    | DMA1I                      |                       | _    |             |             |             | DMA0IP<2:0  |             | DMA0I       | S<1:0>               | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI          | MA7IP<2:0>                    | (2)                | DMA7IS<1:0> <sup>(2)</sup> |                       | —    | _           | —           | D           | MA6IP<2:0>  | (2)         | DMA6IS      | <1:0> <sup>(2)</sup> | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI          | MA5IP<2:0>                    | (2)                | DMA5IS                     | i<1:0> <sup>(2)</sup> | _    | _           | —           | D           | MA4IP<2:0>  | (2)         | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _           | _                             |                    | _                          |                       |      |             | _           | _           | —           |             | —           |                      | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |             | USBIP<2:0>                    |                    | USBIS                      | S<1:0>                | _    | _           | —           |             | FCEIP<2:0>  |             | FCEIS       | <1:0>                | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |             | U5IP<2:0>                     |                    | U5IS-                      | <1:0>                 | _    |             | -           |             | U6IP<2:0>   |             | U6IS-       | <1:0>                | 0000       |             |  |   |   |  |             |  |        |        |      |

| 1150                        | IFUIZ                           | 15:0      | _     | -     |       |             | U4IP<2:0>                     |                    | U4IS-                      | <1:0>                 |      |             |             |             | ETHIP<2:0>  |             | ETHIS       | i<1:0>               | 0000       |             |  |   |   |  |             |  |        |        |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

# REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)

| REGIST    |                                                                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------------------|

| bit 12-10 | IP01<2:0>: Interrupt Priority bits                                                                                    |

|           | 111 = Interrupt priority is 7                                                                                         |

|           | •                                                                                                                     |

|           |                                                                                                                       |

|           | 010 = Interrupt priority is 2                                                                                         |

|           | 001 = Interrupt priority is 1                                                                                         |

|           | 000 = Interrupt is disabled                                                                                           |

| bit 9-8   | IS01<1:0>: Interrupt Sub-priority bits                                                                                |

|           | 11 = Interrupt sub-priority is 3                                                                                      |

|           | 10 = Interrupt sub-priority is 2                                                                                      |

|           | 01 = Interrupt sub-priority is 1                                                                                      |

|           | 00 = Interrupt sub-priority is 0                                                                                      |

| bit 7-5   | Unimplemented: Read as '0'                                                                                            |

| bit 4-2   | IP00<2:0>: Interrupt Priority bits                                                                                    |

|           | 111 = Interrupt priority is 7                                                                                         |

|           | •                                                                                                                     |

|           |                                                                                                                       |

|           | 010 = Interrupt priority is 2                                                                                         |

|           | 001 = Interrupt priority is 1                                                                                         |

|           | 000 = Interrupt is disabled                                                                                           |

| bit 1-0   | IS00<1:0>: Interrupt Sub-priority bits                                                                                |

|           | 11 = Interrupt sub-priority is 3                                                                                      |

|           | 10 = Interrupt sub-priority is 2                                                                                      |

|           | 01 = Interrupt sub-priority is 1                                                                                      |

|           | 00 = Interrupt sub-priority is 0                                                                                      |

| Nete      | This projection proposed to a proposite definition of the IDOs projection Defaulty T-11 T-1 ( ) ( )                   |

| Note:     | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions. |

|           |                                                                                                                       |

# 8.1 Control Registers

### TABLE 8-1: OSCILLATOR REGISTER MAP

| ess                         |                                 | Ð         |       |       |           |            |       | Bits            |           |   |         |         |                            |       |            |           | (2)    |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-----------|------------|-------|-----------------|-----------|---|---------|---------|----------------------------|-------|------------|-----------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13     | 28/12      | 27/11 | 26/10 25/9 24/8 |           |   | 23/7    | 22/6    | 21/5                       | 20/4  | 19/3       | 18/2      | 17/1   | 16/0  | All Resets |

| E000                        | OSCCON                          | 31:16     | —     | _     | P         | LLODIV<2:0 | >     | FRCDIV<2:0>     |           |   | —       | SOSCRDY | SOSCRDY — PBDIV<1:0> PLLMU |       | LLMULT<2:0 | MULT<2:0> |        |       |            |

| FUUU                        | USCCON                          | 15:0      | _     |       | COSC<2:0> | C<2:0> —   |       |                 | NOSC<2:0> |   | CLKLOCK | ULOCK   | SLOCK                      | SLPEN | CF         | UFRCEN    | SOSCEN | OSWEN | 0000       |

| E010                        | OSCTUN                          | 31:16     | —     | _     | _         |            |       | _               |           | - | —       | —       | _                          | —     | —          | _         | _      | —     | 0000       |

| FUIU                        | USCIUN                          | 15:0      | _     |       | _         |            |       |                 |           |   | _       | —       |                            |       | TUN        | <5:0>     |        |       | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

### TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |             |                                                                                        |       |       |            |       |      | В      | its     |        |        |        |                  |         |        |         |              |

|-----------------------------|---------------------------------|---------------|-------------|----------------------------------------------------------------------------------------|-------|-------|------------|-------|------|--------|---------|--------|--------|--------|------------------|---------|--------|---------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14                                                                                  | 29/13 | 28/12 | 27/11      | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3             | 18/2    | 17/1   | 16/0    | All Resets   |

|                             |                                 | 31:16         | _           |                                                                                        | _     | _     | _          | _     | _    | _      | —       | _      | _      | _      | _                | _       | _      | _       | 0000         |

| 3290                        | DCH2DAT                         | 15:0          | _           |                                                                                        | _     | _     | _          | _     | _    | _      |         |        |        | CHPDA  | AT<7:0>          |         |        |         | 0000         |

| 32A0                        | DCH3CON                         | 31:16         | _           |                                                                                        | _     | _     | _          | _     |      | _      | _       |        | _      | _      | —                | —       | _      | _       | 0000         |

| 32A0                        | Denseon                         | 15:0          | CHBUSY      | -                                                                                      | —     | —     | —          | —     | —    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | —                | CHEDET  | CHPR   | l<1:0>  | 0000         |

| 32B0                        | DCH3ECON                        | 31:16         |             | _                                                                                      | —     | —     | —          | —     |      | —      |         | 1      | 1      |        | Q<7:0>           |         |        |         | 00FF         |

|                             |                                 | 15:0          |             |                                                                                        |       |       | Q<7:0>     |       |      | -      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN           | _       | —      | —       | FF00         |

| 32C0                        | <b>DCH3INT</b>                  | 31:16         | —           | _                                                                                      | —     | —     | _          | _     | _    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE           | CHCCIE  | CHTAIE | CHERIE  | 0000         |

|                             |                                 | 15:0          |             | —                                                                                      | —     | —     | —          | —     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF           | CHCCIF  | CHTAIF | CHERIF  | 0000         |

| 32D0                        | DCH3SSA                         | 31:16         |             |                                                                                        |       |       |            |       |      | CHSSA  | A<31:0> |        |        |        |                  |         |        |         | 0000         |

|                             |                                 | 15:0<br>31:16 |             |                                                                                        |       |       |            |       |      |        |         |        |        |        |                  |         |        |         | 0000         |

| 32E0                        | DCH3DSA                         | 15:0          |             |                                                                                        |       |       |            |       |      | CHDSA  | A<31:0> |        |        |        |                  |         |        |         | 0000         |

|                             |                                 | 31:16         | _           | _                                                                                      | _     | _     | _          | _     | _    | _      | _       | _      | _      | _      | _                | _       | _      | _       | 0000         |

| 32F0                        | DCH3SSIZ                        | 15:0          |             |                                                                                        |       |       |            |       |      | CHSSIZ | Z<15:0> |        |        |        |                  |         |        |         | 0000         |

|                             |                                 | 31:16         | _           |                                                                                        |       |       |            |       |      |        |         | 0000   |        |        |                  |         |        |         |              |

| 3300                        | DCH3DSIZ                        | 15:0          |             |                                                                                        |       |       |            |       |      | CHDSI  | Z<15:0> |        |        |        |                  |         |        |         | 0000         |

|                             | DOLIGODTO                       | 31:16         | _           | _                                                                                      | _     | _     | _          | —     | _    | _      | _       | _      | _      | _      | _                | _       | _      | _       | 0000         |

| 3310                        | DCH3SPTR                        | 15:0          |             |                                                                                        |       | •     | •          |       |      | CHSPT  | R<15:0> |        | •      |        | •                |         |        |         | 0000         |

| 2220                        | DCH3DPTR                        | 31:16         | _           |                                                                                        | _     | —     | _          | _     | _    | —      | _       | _      | _      | _      | —                | —       | _      | _       | 0000         |

| 3320                        | DCH3DFTK                        | 15:0          |             |                                                                                        |       |       |            |       |      | CHDPT  | R<15:0> |        |        |        |                  |         |        |         | 0000         |

| 3330                        | DCH3CSIZ                        | 31:16         | —           | —                                                                                      | —     | —     | —          | —     | —    | —      | —       | —      | —      | —      | —                | —       | —      | —       | 0000         |

| 0000                        | DOI 130012                      | 15:0          |             |                                                                                        |       |       |            |       |      | CHCSI  | Z<15:0> |        | -      |        | -                |         |        |         | 0000         |

| 3340                        | DCH3CPTR                        | 31:16         | —           | —                                                                                      | —     | —     | —          | —     | —    | —      | —       | —      | -      | —      | —                | —       | —      | —       | 0000         |

|                             |                                 | 15:0          |             |                                                                                        |       | -     | -          |       |      | CHCPT  | R<15:0> |        | -      |        | -                |         |        |         | 0000         |

| 3350                        | DCH3DAT                         | 31:16         | _           | _                                                                                      | —     | _     |            | _     | _    |        | _       |        | _      | —      | —                | _       | _      |         | 0000         |

|                             |                                 | 15:0          | _           |                                                                                        | _     |       |            | _     | -    |        |         |        |        |        | AT<7:0>          | 1       |        |         | 0000         |

| 3360                        | DCH4CON                         | 31:16         | -           |                                                                                        | _     | _     | _          | _     | _    | -      | -       | -      | -      | -      | -                |         | -      | —       | 0000         |

|                             |                                 | 15:0          | CHBUSY      |                                                                                        | -     |       | _          |       | _    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | -                | CHEDET  | CHPR   | (1<1:0> | 0000         |

| 3370                        | DCH4ECON                        | 31:16<br>15:0 | _           |                                                                                        |       |       | <br>Q<7:0> |       |      | —      | CFORCE  | CABORT | PATEN  | SIRQEN | Q<7:0><br>AIRQEN |         | _      | _       | 00FF<br>FF00 |

|                             |                                 | 31:16         | _           | _                                                                                      |       |       |            |       |      | _      | CHSDIE  | CABORT | CHDDIE | CHDHIE | CHBCIE           | CHCCIE  | CHTAIE | CHERIE  | 0000         |

| 3380                        | DCH4INT                         | 15:0          |             | _                                                                                      | _     | _     | _          | _     |      | _      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE           | CHCCIE  | CHTAIE | CHERIE  | 0000         |

|                             |                                 | 31:16         |             |                                                                                        |       |       |            | 1     |      |        |         | Shorm  | 51000  |        | 0110011          | 0110011 | JIIAI  | SHER    | 0000         |

| 3390                        | DCH4SSA                         | 15:0          |             |                                                                                        |       |       |            |       |      | CHSSA  | A<31:0> |        |        |        |                  |         |        |         | 0000         |

|                             |                                 | 31:16         |             |                                                                                        |       |       |            |       |      |        |         |        |        |        |                  |         |        |         | 0000         |

| 33A0                        | DCH4DSA                         | 15:0          |             |                                                                                        |       |       |            |       |      | CHDSA  | \<31:0> |        |        |        |                  |         |        |         | 0000         |

| Legen                       | <b>d:</b> x = u                 | nknown        | value on Re | value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |       |       |            |       |      |        |         |        |        |        |                  |         |        |         |              |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

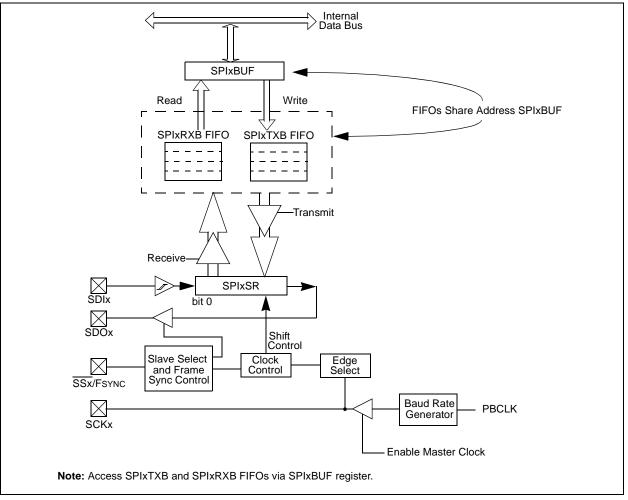

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

| Bit   | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |

|-------|------------|------------|------------|------------|------------|------------|-----------|-----------|

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |

| 24.24 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 31:24 | —          | _          | -          | —          | —          | —          | _         | _         |

| 00.40 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 23:16 | —          | _          | _          | _          | _          | —          | _         | _         |

| 45.0  | R-0, HSC   | R-0, HSC   | U-0        | U-0        | U-0        | R/C-0, HS  | R-0, HSC  | R-0, HSC  |

| 15:8  | ACKSTAT    | TRSTAT     | _          | —          | —          | BCL        | GCSTAT    | ADD10     |

| 7.0   | R/C-0, HS  | R/C-0, HS  | R-0, HSC   | R/C-0, HSC | R/C-0, HSC | R-0, HSC   | R-0, HSC  | R-0, HSC  |

| 7:0   | IWCOL      | I2COV      | D_A        | Р          | S          | R_W        | RBF       | TBF       |

# REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Set by hardware | HSC = Hardware set/cleared |                   |  |  |  |

|-------------------|----------------------|----------------------------|-------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r   | ead as '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | C = Clearable bit |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set or cleared by hardware at the end of a slave Acknowledge.

- 1 = NACK received from slave

- 0 = ACK received from slave

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set by hardware at the beginning of a master transmission, and is cleared by hardware at the end of a slave Acknowledge.

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

This bit is set by hardware at the detection of a bus collision.

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

- bit 9 GCSTAT: General Call Status bit

This bit is set by hardware when the address matches the general call address, and is cleared by hardware clear at a Stop detection.

- 1 = General call address was received

- 0 = General call address was not received

#### bit 8 ADD10: 10-bit Address Status bit

This bit is set by hardware upon a match of the 2nd byte of the matched 10-bit address, and is cleared by hardware at a Stop detection.

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

#### bit 7 IWCOL: Write Collision Detect bit

- This bit is set by hardware at the occurrence of a write to I2CxTRN while busy (cleared by software).

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2C$  module is busy

- 0 = No collision

# bit 6 I2COV: Receive Overflow Flag bit

- This bit is set by hardware at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

## REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

- bit 4 CLRASAM: Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set

- 0 = Sampling begins when SAMP bit is set

- bit 1 SAMP: ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC S&H circuit is sampling

- 0 = The ADC S&H circuit is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC < 2:0 > = 000, writing '0' to this bit will end sampling and start conversion.

## bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- Clearing this bit will not affect any operation in progress.

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

## REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER (CONTINUED)

- bit 14 WAKIF: CAN Bus Activity Wake-up Interrupt Flag bit 1 = A bus wake-up activity interrupt has occurred 0 = A bus wake-up activity interrupt has not occurred CERRIF: CAN Bus Error Interrupt Flag bit bit 13 1 = A CAN bus error has occurred 0 = A CAN bus error has not occurred bit 12 SERRIF: System Error Interrupt Flag bit 1 = A system error occurred (typically an illegal address was presented to the system bus) 0 = A system error has not occurred bit 11 **RBOVIF:** Receive Buffer Overflow Interrupt Flag bit 1 = A receive buffer overflow has occurred 0 = A receive buffer overflow has not occurred bit 10-4 Unimplemented: Read as '0' MODIF: CAN Mode Change Interrupt Flag bit bit 3 1 = A CAN module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP) 0 = A CAN module mode change has not occurred bit 2 CTMRIF: CAN Timer Overflow Interrupt Flag bit 1 = A CAN timer (CANTMR) overflow has occurred 0 = A CAN timer (CANTMR) overflow has not occurred bit 1 **RBIF:** Receive Buffer Interrupt Flag bit 1 = A receive buffer interrupt is pending 0 = A receive buffer interrupt is not pending bit 0 TBIF: Transmit Buffer Interrupt Flag bit 1 = A transmit buffer interrupt is pending

- 1 = A transmit buffer interrupt is pending

0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN31           | MSEL3             | 51<1:0>           |                   |                   | FSEL31<4:0>       |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN30           | MSEL3             | 0<1:0>            |                   |                   | FSEL30<4:0>       |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN29           | MSEL2             | 9<1:0>            |                   |                   | FSEL29<4:0>       |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN28           | MSEL2             | 8<1:0>            |                   |                   | FSEL28<4:0>       |                  |                  |

# REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN31: Filter 31 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL31<1:0>: Filter 31 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL31<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           |                                                                                                                                                                                |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 23    | FLTEN30: Filter 30Enable bit                                                                                                                                                   |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL30<1:0>: Filter 30Mask Select bits                                                                                                                                         |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                                                                             |

|           | 00 = Acceptance Mask 0 selected                                                                                                                                                |

| bit 20-16 | FSEL30<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           |                                                                                                                                                                                |