Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

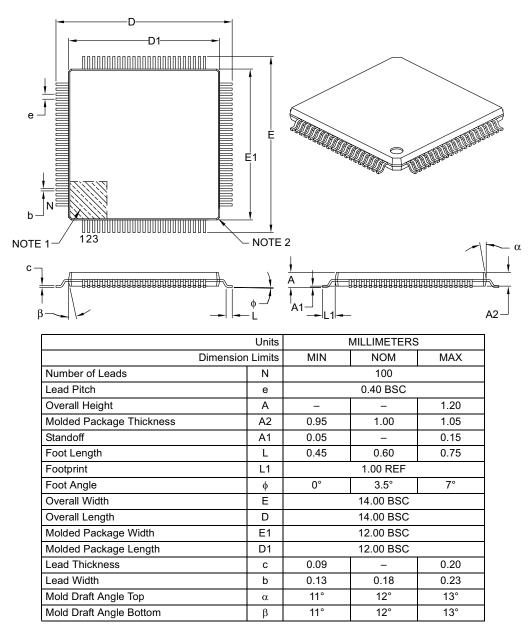

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f064lt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES (CONTINUED)

**100-PIN TQFP (TOP VIEW)** PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L 100 1 Pin # **Full Pin Name** Pin # Full Pin Name 71 IC4/PMCS1/PMA14/RD11 86 Vdd 72 SDO1/OC1/INT0/RD0 87 C1RX/PMD11/RF0 SOSCI/CN1/RC13 C1TX/PMD10/RF1 88 73 SOSCO/T1CK/CN0/RC14 74 89 PMD9/RG1 Vss PMD8/RG0 75 90 TRCLK/RA6 76 OC2/RD1 91 77 OC3/RD2 92 TRD3/RA7 78 OC4/RD3 93 PMD0/RE0 PMD1/RE1 79 IC5/PMD12/RD12 94 80 PMD13/CN19/RD13 95 TRD2/RG14 OC5/PMWR/CN13/RD4 96 TRD1/RG12 81 PMRD/CN14/RD5 TRD0/RG13 82 97 PMD14/CN15/RD6 98 PMD2/RE2 83 PMD15/CN16/RD7 PMD3/RE3 84 99 85 VCAP 100 PMD4/RE4

Note 1: Shaded pins are 5V tolerant.

# 1.0 DEVICE OVERVIEW

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

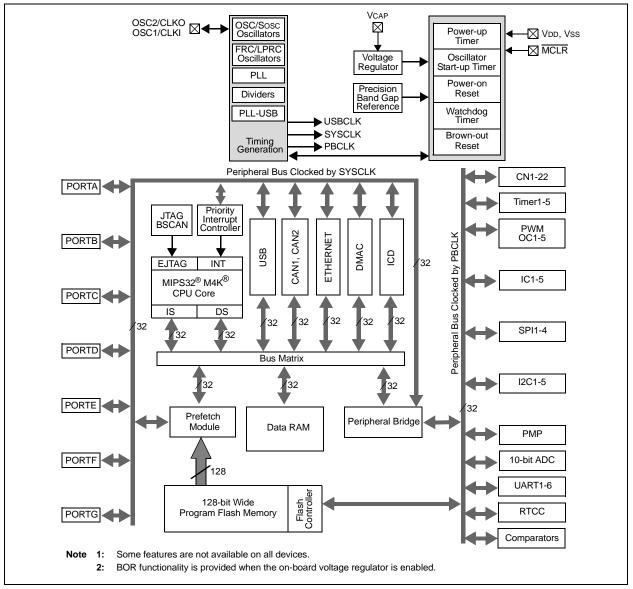

FIGURE 1-1: BLOCK DIAGRAM<sup>(1,2)</sup>

This document contains device-specific information for PIC32MX5XX/6XX/7XX devices.

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX5XX/6XX/7XX family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

|                             |                                 | P             | IC32M>  | (795F51      | 2H DE       | /ICES                         |                               |                               |                               |                             |                               |                               |                             |                       |                         |          |        |                 |            |

|-----------------------------|---------------------------------|---------------|---------|--------------|-------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|----------|--------|-----------------|------------|

| sse                         |                                 |               |         |              |             |                               |                               |                               |                               | В                           | lits                          |                               |                             |                       |                         |          |        |                 |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14        | 29/13       | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2     | 17/1   | 16/0            | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _            | _           | —                             | —                             | —                             | _                             | _                           | —                             | —                             |                             | _                     |                         | _        | _      | SS0             | 0000       |

| 1000                        | INTCOM                          | 15:0          | —       | _            | —           | MVEC                          | —                             |                               | TPC<2:0>                      |                             | -                             | -                             | -                           | INT4EP                | INT3EP                  | INT2EP   | INT1EP | INT0EP          | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | _       | —            | —           | _                             | _                             | —                             | —                             |                             | -                             | _                             | —                           | —                     | —                       | —        | —      | —               | 0000       |

| 1010                        |                                 | 15:0          | —       | —            | —           | _                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC                     | <5:0>    |        |                 | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |              | IPTMR<31:0> |                               |                               |                               |                               |                             |                               |                               |                             |                       |                         | 0000     |        |                 |            |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF      | I2C1BIF     | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | _                             | _                           | _                             | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF    | IC4IF  | T4IF            | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF        | IC3IF       | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF    | CS0IF  | CTIF            | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF       | IC1EIF      | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF   | DMA1IF | DMA0IF          | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF       | _           | _                             | _                             | U2TXIF<br>SPI4TXIF            | U2RXIF<br>SPI4RXIF            | U2EIF<br>SPI4EIF            | U3TXIF<br>SPI2TXIF            | U3RXIF<br>SPI2RXIF            | U3EIF<br>SPI2EIF            | CMP2IF                | CMP1IF                  | PMPIF    | AD1IF  | CNIF            | 0000       |

|                             |                                 | 31:16         | _       |              |             | _                             |                               | I2C5MIF                       | I2C5SIF                       | I2C5BIF                     | I2C4MIF                       | I2C4SIF                       | I2C4BIF                     | _                     |                         | _        | _      | _               | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _            |             |                               | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF   | IC5EIF | IC4EIF          | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE      | I2C1BIE     | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | _                             | -                           | -                             | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE    | IC4IE  | T4IE            | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE        | IC3IE       | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE    | CS0IE  | CTIE            | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE       | IC1EIE      | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE   | DMA1IE | DMA0IE          | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE       | _           | -                             | _                             | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE    | AD1IE  | CNIE            | 0000       |

| 1080                        | IEC2                            | 31:16         | _       | _            | _           | -                             | _                             | _                             | _                             | _                           | _                             | -                             | -                           | _                     | _                       | -        | _      | _               | 0000       |

| 1060                        | IEC2                            | 15:0          | —       | _            | _           | —                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE   | IC5EIE | IC4EIE          | 0000       |

| 1090                        | IPC0                            | 31:16         | —       | —            | —           |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | —                             | —                             | —                           |                       | CS1IP<2:0>              | ,        |        | S<1:0>          | 0000       |

| 1000                        |                                 | 15:0          | _       | _            | _           |                               | CS0IP<2:0>                    |                               |                               | S<1:0>                      | _                             | -                             | _                           |                       | CTIP<2:0>               |          |        | <1:0>           | 0000       |

| 10A0                        | IPC1                            | 31:16         | _       | -            | —           | ļ                             | INT1IP<2:0>                   | •                             |                               | S<1:0>                      | -                             | -                             | _                           |                       | OC1IP<2:0:              | >        |        | S<1:0>          | 0000       |

|                             |                                 | 15:0          | _       | _            | _           |                               | IC1IP<2:0>                    |                               |                               | <1:0>                       | _                             | _                             | _                           | T1IP<2:0>             |                         |          | _      | <1:0>           | 0000       |

| 10B0                        | IPC2                            | 31:16         | _       | _            | _           |                               | INT2IP<2:0>                   | •                             |                               | S<1:0>                      | _                             |                               |                             |                       | OC2IP<2:0:              | <b>`</b> |        | S<1:0>          | 0000       |

|                             |                                 | 15:0          | _       | _            | _           | <u> </u>                      | IC2IP<2:0>                    |                               | IC2IS                         |                             | —                             |                               |                             |                       | T2IP<2:0>               |          | -      | <1:0>           | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 | _       | _            |             |                               | INT3IP<2:0><br>IC3IP<2:0>     | •                             |                               | S<1:0><br><1:0>             |                               |                               |                             |                       | OC3IP<2:0:<br>T3IP<2:0> | >        |        | S<1:0><br><1:0> | 0000       |

| Legend                      | 1: x=1                          |               |         | Reset: — = u | nimplement  | ed, read as '                 |                               | ues are sho                   | wn in hexade                  |                             |                               |                               |                             |                       | 1011 \2.02              |          | 1010   | <1.0Z           | 0000       |

# TABLE 7-4: INTERRUPT REGISTER MAP FOR PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. This bit is unimplemented on PIC32MX764F128H device. This register does not have associated CLR, SET, and INV registers.

PIC32MX5XX/6XX/7XX

2:

3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW1<            | :31:24>           |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          | CHEW1<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

# REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14/6 |       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------------|-------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-x                         | R/W-x | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        | CHEW2<31:24>                  |       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x                         | R/W-x | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW2<23:16>                  |       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x                         | R/W-x | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         |                               |       |                   | CHEW2             | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x                         | R/W-x | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          | CHEW2<7:0>                    |       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

# TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 | 0             |             |       |       |               |        |       |      | В      | its         |        |        |        |         |        |        |        | ú          |

|-----------------------------|---------------------------------|---------------|-------------|-------|-------|---------------|--------|-------|------|--------|-------------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14 | 29/13 | 28/12         | 27/11  | 26/10 | 25/9 | 24/8   | 23/7        | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

| 34D0                        | DCH5DAT                         | 31:16         | —           | _     | —     | —             | _      | —     | _    | _      | _           | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 5400                        | DOI IODAI                       | 15:0          | _           | _     | —     | —             | _      | —     | _    | —      |             |        |        | CHPDA  | T<7:0>  |        |        |        | 0000       |

| 34E0                        | DCH6CON                         | 31:16         | —           | —     | _     | —             | _      | _     | _    | —      | —           | —      | —      | —      | _       | —      | —      | —      | 0000       |

|                             |                                 | 15:0          | CHBUSY      |       |       |               |        |       |      |        |             |        |        |        | 0000    |        |        |        |            |

| 34F0                        | DCH6ECON                        | 31:16         |             |       |       |               |        |       |      |        |             |        |        |        | 00FF    |        |        |        |            |

|                             |                                 | 15:0          |             |       |       | CHSIR         |        |       |      |        | CFORCE      | CABORT | PATEN  | SIRQEN | AIRQEN  | -      | -      | -      | FF00       |

| 3500                        | DCH6INT                         | 31:16         | _           | _     | _     | _             |        |       |      | _      | CHSDIE      | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0          | —           | _     | —     | —             | —      | —     | _    | —      | CHSDIF      | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3510                        | DCH6SSA                         | 31:16         |             |       |       |               |        |       |      | CHSSA  | <31:0>      |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0          |             |       |       |               |        |       |      |        |             |        |        |        |         |        |        |        | 0000       |

| 3520                        | DCH6DSA                         | 31:16<br>15:0 |             |       |       |               |        |       |      | CHDSA  | <31:0>      |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         |             | _     |       |               | _      |       | _    |        | _           | _      |        | _      | _       |        | _      | _      | 0000       |

| 3530                        | DCH6SSIZ                        | 15:0          |             |       |       |               |        |       |      | CHSSIZ | <br>Z<15:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _           | _     | _     | _             | _      | _     | _    | _      |             | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 3540                        | DCH6DSIZ                        | 15:0          |             |       |       |               |        |       |      |        |             |        |        |        | 0000    |        |        |        |            |

|                             |                                 | 31:16         |             | _     | _     | _             | _      | _     | _    | _      | _           | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 3550                        | DCH6SPTR                        | 15:0          |             |       |       |               |        |       |      | CHSPT  | R<15:0>     |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _           | _     | —     | _             | _      | _     | _    | _      | _           | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 3560                        | DCH6DPTR                        | 15:0          |             |       |       |               |        |       |      | CHDPT  | R<15:0>     |        |        |        |         |        |        |        | 0000       |

| 0570                        | 00100017                        | 31:16         | —           | _     | —     | —             | _      | —     | —    | —      | _           | —      | —      | —      | —       | _      | —      | —      | 0000       |

| 3570                        | DCH6CSIZ                        | 15:0          |             |       |       |               |        |       |      | CHCSI  | Z<15:0>     |        |        |        |         |        |        |        | 0000       |

| 3580                        | DCH6CPTR                        | 31:16         | _           | —     | —     | _             |        | _     |      | _      | -           | _      | _      | _      |         | —      | -      | —      | 0000       |

| 3360                        | DCHOCFTK                        | 15:0          |             |       |       |               |        |       |      | CHCPT  | R<15:0>     |        |        |        |         |        |        |        | 0000       |

| 3590                        | DCH6DAT                         | 31:16         | _           | _     |       | —             |        | _     |      | —      |             | —      |        | _      |         | —      | _      | -      | 0000       |

| 0000                        | DOI IODAI                       | 15:0          | —           | _     | _     | —             | _      | _     | _    | —      |             |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 35A0                        | DCH7CON                         | 31:16         | _           | _     | —     | —             | _      | —     | _    | —      | _           | —      | —      | —      | _       | _      | —      | —      | 0000       |

| 00/10                       | Donnoon                         | 15:0          | CHBUSY      | _     | —     | —             | _      | —     | _    | CHCHNS | CHEN        | CHAED  | CHCHN  | CHAEN  | —       | CHEDET | CHPR   | l<1:0> | 0000       |

| 35B0                        | DCH7ECON                        | 31:16         | —           | —     | —     | —             | —      | —     | _    | —      |             | r      | r      | CHAIR  | r       |        |        |        | 00FF       |

|                             |                                 | 15:0          |             |       |       | CHSIR         | Q<7:0> |       |      |        | CFORCE      | CABORT | PATEN  | SIRQEN | AIRQEN  | —      |        | —      | FF00       |

| 35C0                        | DCH7INT                         | 31:16         | _           |       | —     | —             | —      | —     | —    | —      | CHSDIE      | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0          | -           | _     | —     | —             | _      | -     | —    | —      | CHSDIF      | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 35D0                        | DCH7SSA                         | 31:16         | CHSSA<31:0> |       |       |               |        |       |      |        |             |        | 0000   |        |         |        |        |        |            |

|                             |                                 | 15:0          |             |       |       |               |        |       |      |        |             |        |        |        |         |        |        |        | 0000       |

| 35E0                        | DCH7DSA                         | 31:16         | CHDSA<31:05 |       |       |               |        |       |      |        |             |        | 0000   |        |         |        |        |        |            |

| Legen                       |                                 | 15:0          |             |       |       | d, read as '0 |        |       |      |        |             |        |        |        |         |        |        |        | 0000       |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices. 2:

DS60001156J-page 117

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 24.24        | U-0                   | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |

| 22.10        | U-0                   | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                     | —                |

| 15:8         | U-0                   | U-0              |

| 10.0         |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |

|              | R/W-0                 | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup> |                  |

|              | DISEE             | DIVIXEE           | DIVIAEE           | DIVEE             | DENGEE            | URUIDEE           | EOFEE <sup>(2)</sup>  | PIDEE            |

# REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

### Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                               |

|----------|------------------------------------------------------------------------------------------|

| bit 7    | BTSEE: Bit Stuff Error Interrupt Enable bit                                              |

|          | <ul><li>1 = BTSEF interrupt is enabled</li><li>0 = BTSEF interrupt is disabled</li></ul> |

| bit 6    | BMXEE: Bus Matrix Error Interrupt Enable bit                                             |

|          | 1 = BMXEF interrupt is enabled                                                           |

|          | 0 = BMXEF interrupt is disabled                                                          |

| bit 5    | DMAEE: DMA Error Interrupt Enable bit                                                    |

|          | <ul><li>1 = DMAEF interrupt is enabled</li><li>0 = DMAEF interrupt is disabled</li></ul> |

| bit 4    | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                                |

|          | 1 = BTOEF interrupt is enabled                                                           |

- 0 = BTOEF interrupt is disabled

- bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup> bit 1

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

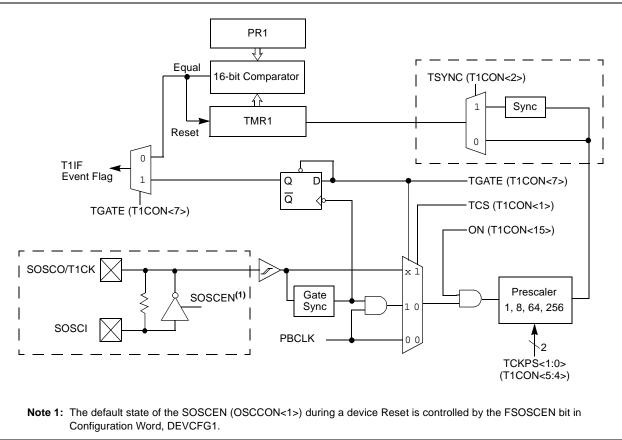

# 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

# FIGURE 13-1: TIMER1 BLOCK DIAGRAM

# 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

# **19.1 Control Registers**

# TABLE 19-1: I2C1THROUGH I2C5 REGISTER MAP

| ss                          |                                 |               |              |             |       |        |        |              |             | Bi         | ts    |             |              |              |               |          |          |          |            |

|-----------------------------|---------------------------------|---------------|--------------|-------------|-------|--------|--------|--------------|-------------|------------|-------|-------------|--------------|--------------|---------------|----------|----------|----------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14       | 29/13 | 28/12  | 27/11  | 26/10        | 25/9        | 24/8       | 23/7  | 22/6        | 21/5         | 20/4         | 19/3          | 18/2     | 17/1     | 16/0     | All Resets |

| 5000                        | I2C3CON                         | 31:16         | _            | _           | —     | _      |        |              | _           | _          |       |             | —            | _            | —             |          |          |          | 0000       |

|                             |                                 | 15:0          | ON           | —           | SIDL  | SCLREL | STRICT | A10M         | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5010                        | I2C3STAT                        | 31:16<br>15:0 | —<br>ACKSTAT | —<br>TRSTAT |       |        | _      | BCL          | —<br>GCSTAT | —<br>ADD10 |       | –<br>I2COV  | —<br>D/A     | —<br>P       |               | —<br>R/W | —<br>RBF | —<br>TBF | 0000       |

|                             | 1000100                         | 31:16         | —            | -           | _     | _      | _      | -            |             | -          | —     | -           |              | -            | _             | -        | —        | —        | 0000       |

| 5020                        | I2C3ADD                         | 15:0          | _            | _           | _     | _      | _      | — — ADD<9:0> |             |            |       |             |              |              |               |          |          | 0000     |            |

| 5000                        | IOCOMOK                         | 31:16         | _            | _           | —     | —      | —      | _            | —           | _          | —     | _           | —            | —            | —             | _        | —        | _        | 0000       |

| 5030                        | I2C3MSK                         | 15:0          | _            | _           | —     | _      | _      |              |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5040                        | I2C3BRG                         | 31:16         | _            | _           | —     | _      | _      | -            | _           | _          | -     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5040                        | IZCODKG                         | 15:0          | _            | _           | —     | —      |        |              |             |            | Ba    | ud Rate Ger | nerator Regi | ster         |               |          |          |          | 0000       |

| 5050                        | I2C3TRN                         | 31:16         | —            | —           |       |        | —      |              |             | _          |       | —           | -            | _            | -             | —        | —        | —        | 0000       |

| 5050                        | 120311(1)                       | 15:0          | —            | —           |       |        | —      |              |             | _          |       |             | -            | Transmit     | Register      |          |          |          | 0000       |

| 5060                        | I2C3RCV                         | 31:16         | —            | —           | —     | —      | —      | _            | —           | —          | _     | —           | —            | —            | —             | —        | —        | —        | 0000       |

| 0000                        | 12001101                        | 15:0          | _            | _           | —     | _      | —      | _            | _           | —          |       |             |              | Receive      | Register      | -        | -        |          | 0000       |

| 5100                        | I2C4CON                         | 31:16         | _            | _           | —     | _      | _      | _            | _           | —          | _     | —           | _            | _            | _             | —        | —        | —        | 0000       |

|                             |                                 | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M         | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5110                        | I2C4STAT                        | 31:16         | —            | —           | —     |        | _      | —            | —           | _          | —     | —           |              | —            |               | —        | —        | —        | 0000       |

| L                           |                                 | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL          | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5120                        | I2C4ADD                         | 31:16         | _            | _           | —     | _      | _      | _            | —           |            | —     | —           | —            | —            | —             | _        | _        | —        | 0000       |

| <b></b>                     |                                 | 15:0          | _            | _           | _     | _      | _      |              |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

| 5130                        | I2C4MSK                         | 31:16         | _            | _           |       |        |        |              |             | _          | _     | _           |              |              |               |          | _        | _        | 0000       |

| ┢────┼                      |                                 | 15:0          |              | _           |       |        | _      |              |             |            |       |             | MSK          | <9:0>        |               |          |          |          | 0000       |

| 5140                        | I2C4BRG                         | 31:16         |              | _           | _     |        |        | —            | —           |            | -     | —           | —            | —            | —             | _        | _        | —        | 0000       |

|                             |                                 | 15:0<br>31:16 | _            | _           | _     |        |        |              |             |            |       | ud Rate Ger | erator Regi  | ster         |               |          |          |          | 0000       |

| 5150                        | I2C4TRN                         | 15:0          |              |             |       |        |        |              |             |            | _     | _           | _            | <br>Transmit | —<br>Register | —        | —        | —        | 0000       |

| ł                           |                                 | 31:16         |              |             |       |        |        |              |             |            |       |             |              |              |               | _        | _        | _        | 0000       |

| 5160                        | I2C4RCV                         | 15:0          | _            | _           |       |        |        |              |             | _          | _     |             |              | Receive      | Register      |          |          |          | 0000       |

|                             |                                 | 31:16         | _            | _           | _     | _      | _      | _            | _           | _          | _     | _           | _            | _            | _             | _        | _        | _        | 0000       |

| 5200                        | I2C5CON                         | 15:0          | ON           | _           | SIDL  | SCLREL | STRICT | A10M         | DISSLW      | SMEN       | GCEN  | STREN       | ACKDT        | ACKEN        | RCEN          | PEN      | RSEN     | SEN      | 1000       |

| 5040                        | 10050747                        | 31:16         | _            | _           | —     | —      | _      | _            | —           |            | _     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5210                        | I2C5STAT                        | 15:0          | ACKSTAT      | TRSTAT      | —     | —      | —      | BCL          | GCSTAT      | ADD10      | IWCOL | I2COV       | D/A          | Р            | S             | R/W      | RBF      | TBF      | 0000       |

| 5000                        | 1005405                         | 31:16         | _            | _           | —     | —      | _      | —            | —           | _          | —     | _           | —            | —            | —             | _        | _        | _        | 0000       |

| 5220                        | I2C5ADD                         | 15:0          | _            | _           | _     | _      | _      | _            |             |            |       |             | ADD          | <9:0>        |               |          |          |          | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This register is not available on 64-pin devices.

# PIC32MX5XX/6XX/7XX

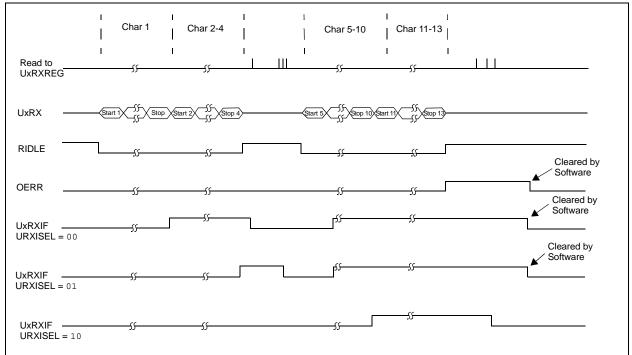

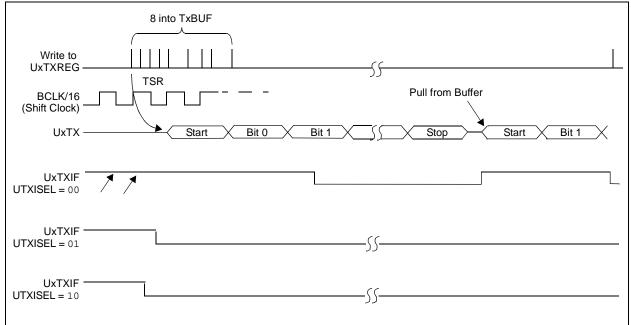

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

# FIGURE 20-2: UART RECEPTION

### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | HR10-             | <3:0>             |                   |                                    | HR01              | <3:0>            |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MIN10             | <3:0>             |                   | MIN01<3:0>                         |                   |                  |                  |  |  |

| 45.0         | R/W-x R/W-x       |                   | R/W-x R/W-x       |                   | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | SEC10             | <3:0>             |                   | SEC01<3:0>                         |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0 U-0           |                   | U-0 U-0                            |                   | U-0              | U-0              |  |  |

| 7:0          | —                 | —                 | —                 | —                 | —                                  | —                 | —                | —                |  |  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |

|              |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |

### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

| IX – IXeauable bit            |                            |                                | it, read as 0      |

|-------------------------------|----------------------------|--------------------------------|--------------------|

| -n = Value at POR             | '1' = Bit is set           | '0' = Bit is cleared           | x = Bit is unknown |

|                               |                            |                                |                    |

| bit 31-28 HR10<3:0>: Binary-0 | Coded Decimal Value of Hou | rs bits, 10 digits; contains a | value from 0 to 2  |

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10 digits, contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1 digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10 digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1 digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10 digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1 digit; contains a value from 0 to 9

bit 17-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

# REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)

| bit 15    | FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 12-8  | FSEL29<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 7     | FLTEN28: Filter 28 Enable bit                                                                                                                                                  |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 6-5   | MSEL28<1:0>: Filter 28 Mask Select bits                                                                                                                                        |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected                                                                                                                                                |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                             |

| bit 4-0   | FSEL28<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           | •                                                                                                                                                                              |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                                                                                                     |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                         |

# PIC32MX5XX/6XX/7XX

|              |                   |                       |                       |                           |                   | •                 |                  | ,                |

|--------------|-------------------|-----------------------|-----------------------|---------------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0                   | U-0                   | U-0                       | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                     | —                     | _                         | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0                   | U-0                   | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 | —                     | —                     | FSIZE<4:0> <sup>(1)</sup> |                   |                   |                  |                  |

| 15.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                     | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | FRESET                | UINC                  | DONLY <sup>(1)</sup>      | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R-0                   | R-0                   | R-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup>      | TXREQ             | RTREN             | TXPR             | <1:0>            |

# **REGISTER 24-20:** CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-21 Unimplemented: Read as '0'

| bit 20-16 FSIZE<4:0>: FIFO Size bits' | bit 20-16 | E<4:0>: FIFO Size bits <sup>(1)</sup> |

|---------------------------------------|-----------|---------------------------------------|

|---------------------------------------|-----------|---------------------------------------|

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep 00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

### bit 15 Unimplemented: Read as '0'

### bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

# 0 = No effect

### bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{When this bit is set the FIFO head will increment by a single message$  $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message$ When this bit is set the FIFO tail will increment by a single message $<math display="block">\frac{TXEN = 0}{When this bit is set the FIFO tail will increment by a single message }$

# bit 12 DONLY: Store Message Data Only bit<sup>(1)</sup>

$\frac{\text{TXEN} = 1:}{\text{TXEN} = 1:}$  (FIFO configured as a Transmit FIFO) This bit is not used and has no effect.  $\frac{\text{TXEN} = 0:}{\text{TXEN} = 0:}$  (FIFO configured as a Receive FIFO)

- 1 =Only data bytes will be stored in the FIFO

- 0 = Full message is stored, including identifier

# bit 11-8 Unimplemented: Read as '0'

- bit 7 **TXEN:** TX/RX Buffer Selection bit

- 1 = FIFO is a Transmit FIFO

- 0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

# PIC32MX5XX/6XX/7XX

# **REGISTER 25-13: ETHIEN: ETHERNET CONTROLLER INTERRUPT ENABLE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6        | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2        | Bit<br>25/17/9/1         | Bit<br>24/16/8/0         |

|--------------|-------------------------|--------------------------|-------------------------|-------------------|-------------------------|--------------------------|--------------------------|--------------------------|

| 31:24        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 31.24        |                         | —                        | _                       |                   | —                       | —                        |                          | —                        |

| 23:16        | U-0                     | U-0                      | U-0                     | U-0               | U-0                     | U-0                      | U-0                      | U-0                      |

| 23.10        | —                       | —                        | _                       | _                 | —                       | —                        | —                        | —                        |

| 15:8         | U-0                     | R/W-0                    | R/W-0                   | U-0               | U-0                     | U-0                      | R/W-0                    | R/W-0                    |

| 10.0         | —                       | TXBUSEIE <sup>(1)</sup>  | RXBUSEIE <sup>(2)</sup> | _                 | —                       | —                        | EWMARKIE <sup>(2)</sup>  | FWMARKIE <sup>(2)</sup>  |

| 7:0          | R/W-0                   | R/W-0                    | R/W-0                   | U-0               | R/W-0                   | R/W-0                    | R/W-0                    | R/W-0                    |

| 7.0          | RXDONEIE <sup>(2)</sup> | PKTPENDIE <sup>(2)</sup> | RXACTIE <sup>(2)</sup>  |                   | TXDONEIE <sup>(1)</sup> | TXABORTIE <sup>(1)</sup> | RXBUFNAIE <sup>(2)</sup> | RXOVFLWIE <sup>(2)</sup> |

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

- bit 14 **TXBUSEIE:** Transmit BVCI Bus Error Interrupt Enable bit<sup>(1)</sup>

- 1 = Enable TXBUS Error Interrupt

- 0 = Disable TXBUS Error Interrupt

- bit 13 **RXBUSEIE:** Receive BVCI Bus Error Interrupt Enable bit<sup>(2)</sup>

- 1 = Enable RXBUS Error Interrupt 0 = Disable RXBUS Error Interrupt

- bit 12-10 Unimplemented: Read as '0'

| bit 9 | <b>EWMARKIE:</b> Empty Watermark Interrupt Enable bit <sup>(2)</sup><br>1 = Enable EWMARK Interrupt |

|-------|-----------------------------------------------------------------------------------------------------|

|       | 0 = Disable EWMARK Interrupt                                                                        |

| bit 8 | FWMARKIE: Full Watermark Interrupt Enable bit <sup>(2)</sup>                                        |

|       | 1 = Enable FWMARK Interrupt                                                                         |

|       | 0 = Disable FWMARK Interrupt                                                                        |

| bit 7 | RXDONEIE: Receiver Done Interrupt Enable bit <sup>(2)</sup>                                         |

|       | 1 = Enable RXDONE Interrupt                                                                         |

|       | 0 = Disable RXDONE Interrupt                                                                        |

| bit 6 | <b>PKTPENDIE:</b> Packet Pending Interrupt Enable bit <sup>(2)</sup>                                |

|       | 1 = Enable PKTPEND Interrupt                                                                        |

|       | 0 = Disable PKTPEND Interrupt                                                                       |

| bit 5 | RXACTIE: RX Activity Interrupt Enable bit                                                           |

|       | 1 = Enable RXACT Interrupt<br>0 = Disable RXACT Interrupt                                           |

| bit 4 | Unimplemented: Read as '0'                                                                          |

| bit 3 | <b>TXDONEIE:</b> Transmitter Done Interrupt Enable bit <sup>(1)</sup>                               |

| DIL 3 | 1 = Enable TXDONE Interrupt                                                                         |

|       | 0 = Disable TXDONE Interrupt                                                                        |

| bit 2 | <b>TXABORTIE:</b> Transmitter Abort Interrupt Enable bit <sup>(1)</sup>                             |

| on L  | 1 = Enable TXABORT Interrupt                                                                        |

|       | 0 = Disable TXABORT Interrupt                                                                       |

| bit 1 | <b>RXBUFNAIE:</b> Receive Buffer Not Available Interrupt Enable bit <sup>(2)</sup>                  |

|       | 1 = Enable RXBUFNA Interrupt                                                                        |

|       | 0 = Disable RXBUFNA Interrupt                                                                       |

| bit 0 | RXOVFLWIE: Receive FIFO Overflow Interrupt Enable bit <sup>(2)</sup>                                |

|       | 1 = Enable RXOVFLW Interrupt                                                                        |

- 0 = Disable RXOVFLW Interrupt

- **Note 1:** This bit is only used for TX operations.

- **2:** This bit is only used for RX operations.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|------------------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |

| 23:16        | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | BUFCNT<7:0>            |                       |                       |                   |                   |                   |                  |                  |

| 15:8         | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0                  | R/W-0                 | R/W-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | ETHBUSY <sup>(1)</sup> | TXBUSY <sup>(2)</sup> | RXBUSY <sup>(2)</sup> | —                 |                   | _                 |                  | _                |

# REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

# Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-16 **BUFCNT<7:0>:** Packet Buffer Count bits

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x000. When software attempts to decrement the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

- **Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

- bit 15-8 **Unimplemented:** Read as '0'

- bit 7 ETHBUSY: Ethernet Module busy bit<sup>(1)</sup>

1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2)</sup>

- 1 = TX logic is receiving data

- 0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

# 28.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MX5XX/6XX/7XX family of devices. These devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 28.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the Peripheral Bus Clock (PBCLK) and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

# 28.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- **Posc Idle mode:** the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- **Sosc Idle mode:** the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 28.3 Power-Saving Operation

Peripherals and the CPU can be halted or disabled to further reduce power consumption.

# 28.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 28.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit, if enabled, remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).