Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  |      |                         |                  |     | USE      | B and E                | therne                                   | t                     |                    |                                 |                              |             |         |      |       |                         |

|------------------|------|-------------------------|------------------|-----|----------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSP/PMP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H  | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H  | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H  | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H  | 64   | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L  | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L  | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L  | 100  | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L  | 100  | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFP | MR = QF                 | N                |     | BG =     | TFBGA                  | 4                                        | TL =                  | VTL/               | ų( <del>5</del> )               |                              |             |         |      |       |                         |

| TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES |

|-----------------------------------------------|

|-----------------------------------------------|

Legend: PF, PT = TQFP MR = QFN BG = Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                              | Pin Nun         | nber <sup>(1)</sup> |                 | Pin         | Buffer               |                                                                                              |  |  |  |

|----------|----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|----------------------------------------------------------------------------------------------|--|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                           | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Ріп<br>Туре | Витег<br>Туре        | Description                                                                                  |  |  |  |

| TMS      | 23                                           | 17              | G3                  | B9              | I           | ST                   | JTAG Test mode select pin                                                                    |  |  |  |

| ТСК      | 27                                           | 38              | J6                  | A26             | I           | ST                   | JTAG test clock input pin                                                                    |  |  |  |

| TDI      | 28                                           | 60              | G11                 | A40             | I           | ST                   | JTAG test data input pin                                                                     |  |  |  |

| TDO      | 24                                           | 61              | G9                  | B33             | 0           |                      | JTAG test data output pin                                                                    |  |  |  |

| RTCC     | 42                                           | 68              | E9                  | B37             | 0           |                      | Real-Time Clock alarm output                                                                 |  |  |  |

| CVREF-   | 15                                           | 28              | L2                  | A21             | I           | Analog               | Comparator Voltage Reference (low)                                                           |  |  |  |

| CVREF+   | 16                                           | 29              | K3                  | B17             | I           | Analog               | Comparator Voltage Reference (high)                                                          |  |  |  |

| CVREFOUT | 23                                           | 34              | L5                  | A24             | 0           | Analog               | Comparator Voltage Reference output                                                          |  |  |  |

| C1IN-    | 12                                           | 21              | H2                  | B11             | I           | Analog               | Comparator 1 negative input                                                                  |  |  |  |

| C1IN+    | 11                                           | 20              | H1                  | A12             | I           | Analog               | Comparator 1 positive input                                                                  |  |  |  |

| C1OUT    | 21                                           | 32              | K4                  | A23             | 0           |                      | Comparator 1 output                                                                          |  |  |  |

| C2IN-    | 14                                           | 23              | J2                  | B13             | I           | Analog               | Comparator 2 negative input                                                                  |  |  |  |

| C2IN+    | 13                                           | 22              | J1                  | A13             | I           | Analog               | Comparator 2 positive input                                                                  |  |  |  |

| C2OUT    | 22                                           | 33              | L4                  | B19             | 0           |                      | Comparator 2 output                                                                          |  |  |  |

| PMA0     | 30                                           | 44              | L8                  | A29             | I/O         | TTL/ST               | Parallel Master Port Address bit 0                                                           |  |  |  |

| PMA1     | 29                                           | 43              | K7                  | B24             | I/O         | TTL/ST               | Parallel Master Port Address bit 1 in<br>(Buffered Slave modes) and output<br>(Master modes) |  |  |  |

| PMA2     | 8                                            | 14              | F3                  | A9              | 0           | _                    | Parallel Master Port address                                                                 |  |  |  |

| PMA3     | 6                                            | 12              | F2                  | A8              | 0           |                      | (Demultiplexed Master modes)                                                                 |  |  |  |

| PMA4     | 5                                            | 11              | F4                  | B6              | 0           | _                    |                                                                                              |  |  |  |

| PMA5     | 4                                            | 10              | E3                  | A7              | 0           | _                    |                                                                                              |  |  |  |

| PMA6     | 16                                           | 29              | K3                  | B17             | 0           | —                    |                                                                                              |  |  |  |

| PMA7     | 22                                           | 28              | L2                  | A21             | 0           | —                    |                                                                                              |  |  |  |

| PMA8     | 32                                           | 50              | L11                 | A32             | 0           | _                    |                                                                                              |  |  |  |

| PMA9     | 31                                           | 49              | L10                 | B27             | 0           | _                    |                                                                                              |  |  |  |

| PMA10    | 28                                           | 42              | L7                  | A28             | 0           | _                    |                                                                                              |  |  |  |

| PMA11    | 27                                           | 41              | J7                  | B23             | 0           |                      |                                                                                              |  |  |  |

| PMA12    | 24                                           | 35              | J5                  | B20             | 0           |                      |                                                                                              |  |  |  |

| PMA13    | 23                                           | 34              | L5                  | A24             | 0           | _                    | 1                                                                                            |  |  |  |

| PMA14    | 45                                           | 71              | C11                 | A46             | 0           | _                    | 1                                                                                            |  |  |  |

| PMA15    | 44                                           | 70              | D11                 | B38             | 0           | _                    | 1                                                                                            |  |  |  |

| PMCS1    | 45                                           | 71              | C11                 | A46             | 0           |                      | Parallel Master Port Chip Select 1<br>strobe                                                 |  |  |  |

| PMCS2    | 44                                           | 70              | D11                 | B38             | 0           | _                    | Parallel Master Port Chip Select 2 strobe                                                    |  |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt 1<br>TL = TTL inp | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input                                                        |  |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

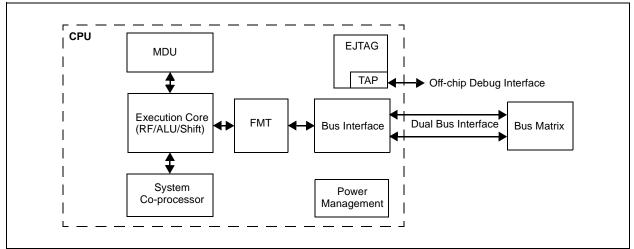

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 2. "CPU" (DS60001113) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The MIPS32<sup>®</sup> M4K<sup>®</sup> Processor core is the heart of the PIC32MX5XX/6XX/7XX family processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 2)

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> code compression

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8-bit and 16-bit data types

- Simple Fixed Mapping Translation (FMT) mechanism

- Simple dual bus interface

- Independent 32-bit address and data busses

- Transactions can be aborted to improve interrupt latency

- · Autonomous multiply/divide unit

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- Power control

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG debug and instruction trace

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

- PC tracing with trace compression

# FIGURE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE BLOCK DIAGRAM

NOTES:

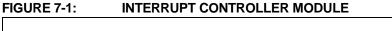

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                          |                   | _                 |                   | _                 | _                 | _                | —                |  |  |  |

| 22.46        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN            | _                 | _                | —                |  |  |  |

# REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit                                    |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

## bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

# 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# 15.1 Control Registers

# TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess                      |                                 | Bits      |       |       |       |       |       |       |      |      |      | (2)  |      |           |      |      |      |        |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|------|--------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0000                     | WDTOON                          | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | —    | —         | _    | —    | _    | _      | 0000       |

| 0000                     | WDTCON                          | 15:0      | ON    | _     |       | _     | _     | _     | _    | _    | _    |      | S    | WDTPS<4:0 | )>   |      | _    | WDTCLR | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

| Bit   | Bit        | Bit        | Bit        | Bit        | Bit        | Bit        | Bit       | Bit       |

|-------|------------|------------|------------|------------|------------|------------|-----------|-----------|

| Range | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2 | 25/17/9/1 | 24/16/8/0 |

| 24.24 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 31:24 | —          | _          |            | —          | —          | —          | _         | _         |

| 00.40 | U-0        | U-0        | U-0        | U-0        | U-0        | U-0        | U-0       | U-0       |

| 23:16 | —          | _          | _          | _          | _          | —          | _         | _         |

| 45.0  | R-0, HSC   | R-0, HSC   | U-0        | U-0        | U-0        | R/C-0, HS  | R-0, HSC  | R-0, HSC  |

| 15:8  | ACKSTAT    | TRSTAT     | _          | —          | —          | BCL        | GCSTAT    | ADD10     |

| 7.0   | R/C-0, HS  | R/C-0, HS  | R-0, HSC   | R/C-0, HSC | R/C-0, HSC | R-0, HSC   | R-0, HSC  | R-0, HSC  |

| 7:0   | IWCOL      | I2COV      | D_A        | Р          | S          | R_W        | RBF       | TBF       |

# REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Legend:           | HS = Set by hardware | HSC = Hardware set/cleared |                   |  |  |  |

|-------------------|----------------------|----------------------------|-------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r   | ead as '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | C = Clearable bit |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ACKSTAT:** Acknowledge Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set or cleared by hardware at the end of a slave Acknowledge.

- 1 = NACK received from slave

- 0 = ACK received from slave

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation) This bit is set by hardware at the beginning of a master transmission, and is cleared by hardware at the end of a slave Acknowledge.

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

This bit is set by hardware at the detection of a bus collision.

- 1 = A bus collision has been detected during a master operation

- 0 = No collision

- bit 9 GCSTAT: General Call Status bit

This bit is set by hardware when the address matches the general call address, and is cleared by hardware clear at a Stop detection.

- 1 = General call address was received

- 0 = General call address was not received

### bit 8 ADD10: 10-bit Address Status bit

This bit is set by hardware upon a match of the 2nd byte of the matched 10-bit address, and is cleared by hardware at a Stop detection.

- 1 = 10-bit address was matched

- 0 = 10-bit address was not matched

### bit 7 IWCOL: Write Collision Detect bit

- This bit is set by hardware at the occurrence of a write to I2CxTRN while busy (cleared by software).

- 1 = An attempt to write the I2CxTRN register failed because the  $I^2C$  module is busy

- 0 = No collision

# bit 6 I2COV: Receive Overflow Flag bit

- This bit is set by hardware at an attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- 1 = A byte was received while the I2CxRCV register is still holding the previous byte

- 0 = No overflow

# REGISTER 24-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6 (CONTINUED)

| bit 15    | FLTEN25: Filter 25 Enable bit                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL25<1:0>: Filter 25 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected                                                                        |

|           | 00 = Acceptance Mask 0 selected                                                                        |

| bit 12-8  | FSEL25<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN24: Filter 24 Enable bit                                                                          |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 6-5   | MSEL24<1:0>: Filter 24 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected                                                                        |

|           | 00 = Acceptance Mask 0 selected                                                                        |

| bit 4-0   | FSEL24<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           |                                                                                                        |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

|              |                   |                   |                   |                   |                   | •                 |                    | ,                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |  |

| 24.24        | R-x                | R-x                |  |  |  |  |

| 31:24        |                   |                   |                   | CiFIFOUA          | n<31:24>          |                   |                    | •                  |  |  |  |  |

| 00.40        | R-x                | R-x                |  |  |  |  |

| 23:16        | CiFIFOUAn<23:16>  |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |

| 45.0         | R-x                | R-x                |  |  |  |  |

| 15:8         | CiFIFOUAn<15:8>   |                   |                   |                   |                   |                   |                    |                    |  |  |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |  |

| 7:0          |                   |                   |                   | CiFIFOU           | IAn<7:0>          |                   |                    |                    |  |  |  |  |

## REGISTER 24-22: CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' (n = 0 THROUGH 31)

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | _                 | _                 | _                 | _                 |                  | _                |

| 7:0          | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | —                 | —                 | -                 |                   | (                 | CiFIFOCI<4:0      | >                |                  |

### **REGISTER 24-23:** CiFIFOCIN: CAN MODULE MESSAGE INDEX REGISTER 'n' (n = 0 THROUGH 31)

### Legend:

| J                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

# TABLE 25-5:ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L,<br/>PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H,<br/>PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX764F128H, PIC32MX764F128H,<br/>PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| sseptimize         and the sector         and the sector <th< th=""><th>:16        5:0        :16        :16    </th><th>30/14<br/>—<br/>—<br/>—<br/>—</th><th>29/13<br/>—<br/>—<br/>—</th><th>28/12<br/></th><th><b>27/11</b><br/>—<br/>RESET</th><th>26/10</th><th>25/9</th><th>24/8</th><th>its<br/>23/7</th><th>22/6</th><th>21/5</th><th>20/4</th><th>19/3</th><th>18/2</th><th>17/1</th><th>16/0</th><th>All Resets</th></th<> | :16        5:0        :16        :16 | 30/14<br>—<br>—<br>—<br>— | 29/13<br>—<br>—<br>— | 28/12<br> | <b>27/11</b><br>—<br>RESET | 26/10      | 25/9 | 24/8          | its<br>23/7 | 22/6 | 21/5 | 20/4   | 19/3          | 18/2      | 17/1      | 16/0     | All Resets |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|---------------------------|----------------------|-----------|----------------------------|------------|------|---------------|-------------|------|------|--------|---------------|-----------|-----------|----------|------------|

| 9260         EMAC1<br>SUPP         31:10<br>15:0           9270         EMAC1<br>TEST         31:10<br>15:0           9280         EMAC1<br>31:10         31:10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | :16        5:0        :16        :16 |                           |                      | _         | —<br>RESET                 |            |      |               | 23/7        | 22/6 | 21/5 | 20/4   | 19/3          | 18/2      | 17/1      | 16/0     | All Resets |

| 9260         EMAC1<br>SUPP         15:0           9270         EMAC1<br>TEST         31:16<br>15:0           9280         EMAC1<br>31:16         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5:0 —<br>:16 —<br>5:0 —<br>:16 —     | -                         | _                    |           |                            | —          | _    |               |             |      |      |        |               |           |           |          |            |

| 9260         SUPP         15:0           9270         EMAC1<br>TEST         31:16<br>15:0           9280         EMAC1         31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | :16 —<br>5:0 —<br>:16 —              | _                         |                      | -         |                            |            |      |               | _           | _    | —    |        | _             | _         | —         | _        | 0000       |

| 9270 TEST 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5:0 <u>—</u><br>:16 —                |                           | —                    |           | RMII                       | —          | —    | SPEED<br>RMII | -           | -    | —    | -      | —             | -         | -         | _        | 1000       |

| EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | :16 —                                | -                         |                      | _         | —                          | _          | _    | _             | _           | _    | _    | -      | —             | _         | _         |          | 0000       |

| end EMAC1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      |                           | _                    | _         | _                          | _          | —    | _             | _           | _    | _    | -      | _             | TESTBP    | TESTPAUSE | SHRTQNTA | 0000       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                      | -                         | _                    | _         | _                          | _          | _    | _             | _           | _    | —    | _      | _             | —         | _         | _        | 0000       |

| 9280 MCFG 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5:0 RESET<br>MGMT                    | -                         | _                    | _         | —                          | —          | —    | —             | -           | _    |      | CLKSE  | L<3:0>        |           | NOPRE     | SCANINC  | 0020       |

| 9290 EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | :16 —                                | _                         | _                    | _         | —                          | _          | _    | _             | _           | _    | _    | _      | _             | _         | _         | _        | 0000       |

| 9290 MCMD 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5:0 —                                | —                         | —                    | —         | _                          | —          | _    | —             | —           | _    | _    | _      | _             | —         | SCAN      | READ     | 0000       |

| 92A0 EMAC1 31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                      | -                         | —                    | —         | —                          | —          | —    | _             | _           | —    | —    | —      | —             | —         | —         | —        | 0000       |

| MADR 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                      | -                         | —                    |           | P                          | HYADDR<4:0 | )>   |               | _           | _    | _    |        | R             | EGADDR<4: | 0>        |          | 0100       |

| 92B0 EMAC1 31:16<br>MWTD 15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                      | —                         | —                    | _         | —                          | —          | —    | —             | _           | _    | —    | —      | —             | —         | _         | —        | 0000       |