Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

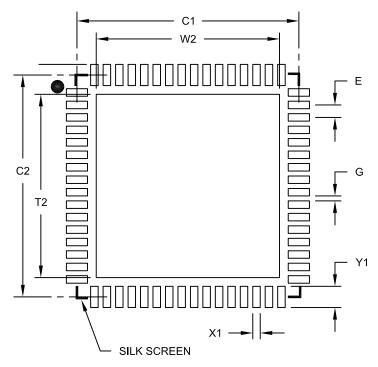

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128h-v-mr |

### TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES (CONTINUED)

100-PIN TQFP (TOP VIEW)

PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L

100

1

| Pin# | Full Pin Name        |

|------|----------------------|

| 71   | IC4/PMCS1/PMA14/RD11 |

| 72   | SDO1/OC1/INT0/RD0    |

| 73   | SOSCI/CN1/RC13       |

| 74   | SOSCO/T1CK/CN0/RC14  |

| 75   | Vss                  |

| 76   | OC2/RD1              |

| 77   | OC3/RD2              |

| 78   | OC4/RD3              |

| 79   | IC5/PMD12/RD12       |

| 80   | PMD13/CN19/RD13      |

| 81   | OC5/PMWR/CN13/RD4    |

| 82   | PMRD/CN14/RD5        |

| 83   | PMD14/CN15/RD6       |

| 84   | PMD15/CN16/RD7       |

| 85   | VCAP                 |

| Pin # | Full Pin Name  |

|-------|----------------|

| 86    | VDD            |

| 87    | C1RX/PMD11/RF0 |

| 88    | C1TX/PMD10/RF1 |

| 89    | PMD9/RG1       |

| 90    | PMD8/RG0       |

| 91    | TRCLK/RA6      |

| 92    | TRD3/RA7       |

| 93    | PMD0/RE0       |

| 94    | PMD1/RE1       |

| 95    | TRD2/RG14      |

| 96    | TRD1/RG12      |

| 97    | TRD0/RG13      |

| 98    | PMD2/RE2       |

| 99    | PMD3/RE3       |

| 100   | PMD4/RE4       |

Note 1: Shaded pins are 5V tolerant.

#### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com** or fax the **Reader Response Form** in the back of this data sheet to (480) 792-4150. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

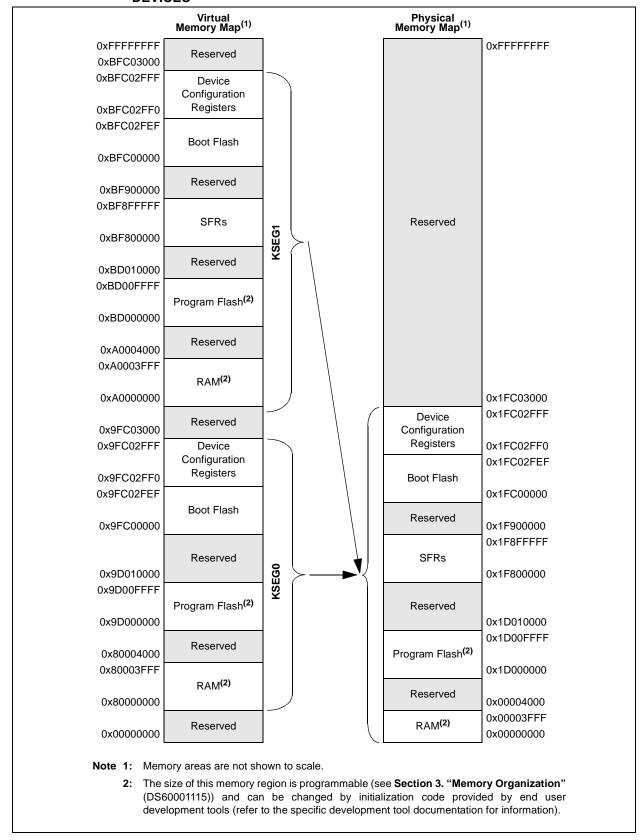

FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

**NOTES:**

| 0          |  |

|------------|--|

| 2009-2016  |  |

| Microchip  |  |

| Technology |  |

| y Inc.     |  |

| ess                         |                                 |                   |        |       |       |       |       | -     | 1025) | Ві     | its     |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-------------------|--------|-------|-------|-------|-------|-------|-------|--------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15  | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9  | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 3180                        | DCH1DSIZ                        | 31:16             | _      | _     | _     | _     |       | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3100                        | DOITIDGIZ                       | 15:0              |        |       |       |       |       |       |       | CHDSIZ | Z<15:0> |        |        |        |        |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 0100                        | DOITION III                     | 15:0              |        | ı     | ı     |       |       | ı     | ı     | CHSPTI | R<15:0> |        | ı      | ı      | I      | I      | ı      | ı      | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 0 17 10                     | 5011151 111                     | 15:0              |        | 1     | 1     |       |       | 1     | ı     | CHDPT  | R<15:0> |        | 1      | 1      | 1      | 1      | 1      | ı      | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16             |        | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0              |        | 1     | 1     |       |       | 1     | 1     | CHCSIZ | Z<15:0> |        | 1      | 1      | 1      | 1      | 1      | 1      | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0              |        |       |       |       |       |       |       | CHCPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16             |        | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      |        |        | _      | _      | _      | 0000       |

| -                           |                                 | 15:0              | _      | _     | _     | _     |       | _     | _     | _      |         | 1      |        | CHPDA  |        |        |        |        | 0000       |

| 31E0                        | DCH2CON                         | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0              | CHBUSY | _     | _     | _     | _     | _     | _     | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | I<1:0> | 0000       |

| 31F0                        | DCH2ECON                        | 31:16             | _      | _     | _     |       |       | _     | _     | _      |         | T      |        | CHAIR  |        |        | ı      | I      | 00FF       |

|                             |                                 | 15:0              |        |       |       | CHSIR |       |       |       | 1      | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      |        |        | FF00       |

| 3200                        | DCH2INT                         | 31:16             |        | _     | _     | _     |       | _     | _     | _      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

|                             |                                 | 15:0              | _      | _     | _     | _     | _     | _     | _     | _      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 31:16<br>15:0     |        |       |       |       |       |       |       | CHSSA  | N<31:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16             |        |       |       |       |       |       |       |        |         |        |        |        |        |        |        |        | 0000       |

| 3220                        | DCH2DSA                         | 15:0              |        |       |       |       |       |       |       | CHDSA  | N<31:0> |        |        |        |        |        |        |        | 0000       |

| 0000                        | DOL100017                       | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0              |        |       | •     |       |       |       | •     | CHSSIZ | Z<15:0> | •      | •      |        | •      | •      |        | •      | 0000       |

| 2040                        | DOLLODOLZ                       | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0              |        |       |       |       |       |       |       | CHDSIZ | Z<15:0> |        |        |        |        |        |        |        | 0000       |

| 0050                        | DOLLOODED                       | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3250                        | DCH2SPTR                        | 15:0              |        |       |       |       |       |       |       | CHSPTI | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 0000                        | DOLIODDED                       | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3260                        | DCH2DPTR 15:0 CHDPTR<15:0>      |                   |        |       |       |       |       |       |       |        | 0000    |        |        |        |        |        |        |        |            |

| 2270                        | DCHOCOLZ                        | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0              |        |       |       |       |       |       |       | CHCSIZ | Z<15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16             | _      | _     | _     | _     | _     | _     | _     | _      | _       | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3280                        | DCH2CPTR                        | 15:0              |        |       |       |       |       |       |       | CHCPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| Ь                           | i                               | 15:0 CHCPTR<15:0> |        |       |       |       |       |       |       |        | 3000    |        |        |        |        |        |        |        |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1:

<sup>2:</sup> DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

#### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 | _                 | -                 | _                 |                   | _                |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | -                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 CHSDIE: Channel Source Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 22 CHSHIE: Channel Source Half Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 21 CHDDIE: Channel Destination Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 20 CHDHIE: Channel Destination Half Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 19 CHBCIE: Channel Block Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 18 CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 17 CHTAIE: Channel Transfer Abort Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 16 CHERIE: Channel Address Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 15-8 **Unimplemented:** Read as '0'

bit 7 CHSDIF: Channel Source Done Interrupt Flag bit

1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)

0 = No interrupt is pending

bit 6 CHSHIF: Channel Source Half Empty Interrupt Flag bit

1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)

0 = No interrupt is pending

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | -                | _                |  |  |  |  |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   | _                 |                   | CHSPTF            | R<7:0>            | _                 |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

•

0000000000000000 = Points to byte 1 of the source 000000000000000 = Points to byte 0 of the source

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 10-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |  |  |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        |                   | _                 | _                 | _                 | _                 |                   | _                | _                |  |  |  |  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15.6         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

•

#### **Control Registers** 11.1

TABLE 11-1: USB REGISTER MAP

| sse                         |                                 |           |       |       |       |       |       |       |      |      | Bits                   |                    |                      |             |           |          |          |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------------------------|--------------------|----------------------|-------------|-----------|----------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                   | 22/6               | 21/5                 | 20/4        | 19/3      | 18/2     | 17/1     | 16/0     | All Resets |

| 5040                        | U1OTGIR <sup>(2)</sup>          | 31:16     | -     | ı     | _     | _     | ı     | _     | _    | _    | _                      | _                  | _                    | -           | _         | _        | -        | _        | 0000       |

| 3040                        | 0101GIK.7                       | 15:0      |       | _     | _     | _     | _     |       | _    | _    | IDIF                   | T1MSECIF           | LSTATEIF             | ACTVIF      | SESVDIF   | SESENDIF | _        | VBUSVDIF | 0000       |

| 5050                        | U1OTGIE                         | 31:16     |       | _     | _     | _     | _     |       | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 3030                        | OTOTOLE                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE             | ACTVIE      | SESVDIE   | SESENDIE | _        | VBUSVDIE | 0000       |

| 5060                        | U1OTGSTAT <sup>(3)</sup>        | 31:16     |       | _     | _     | _     | _     |       | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 3000                        | 010100171                       | 15:0      |       | _     | _     | _     | _     |       | _    | _    | ID                     | _                  | LSTATE               | _           | SESVD     | SESEND   | _        | VBUSVD   | 0000       |

| 5070                        | U1OTGCON                        | 31:16     |       | _     | _     | _     | _     |       | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 3070                        | 01010001                        | 15:0      |       | _     | _     | _     | _     |       | _    | _    | DPPULUP                | DMPULUP            | DPPULDWN             | DMPULDWN    | VBUSON    | OTGEN    | VBUSCHG  | VBUSDIS  | 0000       |

| 5080                        | U1PWRC                          | 31:16     |       | _     | _     | _     | _     |       | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 3000                        | OH WICE                         | 15:0      | _     | -     | _     | _     | -     | _     | _    | _    | UACTPND <sup>(4)</sup> | _                  | _                    | USLPGRD     | USBBUSY   | _        | USUSPEND | USBPWR   | 0000       |

|                             |                                 | 31:16     | _     | -     | _     | _     | -     | _     | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIF                | ATTACHIF           | RESUMEIF             | IDLEIF      | TRNIF     | SOFIF    | UERRIF   | URSTIF   | 0000       |

|                             |                                 | 10.0      |       |       |       |       |       |       |      |      | OTALLI                 | 711 17101111       | RECOME               | IDEEII      | 11(1411   | 00111    | OLITA    | DETACHIF | 0000       |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 5210                        | U1IE                            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE             | IDLEIE      | TRNIE     | SOFIE    | UERRIE   | URSTIE   | 0000       |

|                             |                                 | 10.0      |       |       |       |       |       |       |      |      | OTALLIL                | 7 (1 17 (OT III    | RECOME               | IDEEIE      | TI CI CI  | 00112    | OLIVIL   | DETACHIE | 0000       |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                  | BMXEF              | DMAEF                | BTOEF       | DFN8EF    | CRC16EF  | CRC5EF   | PIDEF    | 0000       |

|                             |                                 | 10.0      |       |       |       |       |       |       |      |      | 3.02.                  | 5.00%              | 2                    | 2.02.       | 51.102.   | 0.10.02. | EOFEF    | 52.      | 0000       |

|                             |                                 | 31:16     |       |       | _     | _     |       |       | _    |      | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 5230                        | U1EIE                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | BTSEE                  | BMXEE              | DMAEE                | BTOEE       | DFN8EE    | CRC16EE  | CRC5EE   | PIDEE    | 0000       |

|                             |                                 | .0.0      |       |       |       |       |       |       |      |      |                        | D.W.               | J                    |             | 2022      | 0.10.022 | EOFEE    | 522      | 0000       |

| 5240                        | U1STAT <sup>(3)</sup>           | 31:16     |       |       | _     | _     |       |       | _    |      | _                      | _                  |                      | _           | _         | _        |          | _        | 0000       |

| 02.0                        | 0.0                             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |                        | ENDPT              | <3:0> <sup>(4)</sup> |             | DIR       | PPBI     | _        | _        | 0000       |

|                             |                                 | 31:16     |       |       | _     | _     |       |       | _    |      | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 5250                        | U1CON                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | PKTDIS               | USBRST      | HOSTEN    | RESUME   | PPBRST   | USBEN    | 0000       |

|                             |                                 |           |       |       |       |       |       |       |      |      |                        | 020                | TOKBUSY              | 30501       |           |          |          | SOFEN    | 0000       |

| 5260                        | U1ADDR                          | 31:16     | _     | _     | _     | _     |       |       | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 3200                        | 317.0010                        | 15:0      | _     | _     | _     | _     |       | _     | _    | _    | LSPDEN                 |                    |                      | DE          | VADDR<6:0 | )>       |          |          | 0000       |

| 5270                        | U1BDTP1                         | 31:16     | _     | -     | _     | _     | -     | _     | _    | _    | _                      | _                  | _                    | _           | _         | _        | _        | _        | 0000       |

| 32.70                       | 3100111                         | 15:0      | _     | -     |       | _     |       |       | _    | _    |                        |                    | BI                   | OTPTRL<7:1> |           |          |          | _        | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

PIC32MX5XX/6XX/7XX

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for Note 1: more information.

This register does not have associated SET and INV registers. This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined.

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 PPBRST: Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit(4)

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit (5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

### 15.1 Control Registers

### TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess.                      |                                 | ø         |       | Bits  |       |       |       |       |      |      |      |      |      |           |      |      | (2)  |        |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|------|--------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0000                      | WDTCON                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _         | _    | _    | _    | _      | 0000       |

| 0000                      | 0000 WDTCON                     | 15:0      | ON    | ı     | _     | _     | _     | _     | _    | _    | _    |      | S    | WDTPS<4:0 | )>   |      | _    | WDTCLR | 0000       |

PIC32MX5XX/6XX/7XX

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                     | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                     | _                 | _                 | _                 | _                 |                   | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                     |                   | S                 | SWDTPS<4:0        | >                 |                   | WDTWINEN         | WDTCLR           |

**Legend:** y = Values set from Configuration bits on POR

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

1 = Enables the WDT if it is not enabled by the device configuration

0 = Disable the WDT if it was enabled in software

bit 14-7 Unimplemented: Read as '0'

bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits

On reset, these bits are set to the values of the WDTPS <4:0> Configuration bits.

bit 1 WDTWINEN: Watchdog Timer Window Enable bit

1 = Enable windowed Watchdog Timer

0 = Disable windowed Watchdog Timer

bit 0 WDTCLR: Watchdog Timer Reset bit

1 = Writing a '1' will clear the WDT

0 = Software cannot force this bit to a '0'

Note 1: A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

2: When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                       | 4                                 |        |         |        |       |        |       |       | Bi     | ts     |         |       |          |          |      |        |       |            |

|-----------------------------|-----------------------|-----------------------------------|--------|---------|--------|-------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range                         | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8   | 23/7   | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6620                        | U6TXREG               | 31:16                             | _      | _       | _      | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0020                        | UUIAREG               | 15:0                              |        | _       | _      |       | _      | _     |       | TX8    |        |         |       | Transmit | Register |      |        |       | 0000       |

| 6630                        | U6RXREG               | 31:16                             | _      | _       | _      | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0030                        | UUNANEG               | 15:0                              | _      | _       | _      | _     | _      | _     | _     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U6BRG <sup>(1)</sup>  | 31:16                             |        | _       | _      | _     | _      | _     |       | _      |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0040                        | OODING                | 15:0                              |        |         |        |       |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

| 6800                        | U2MODE <sup>(1)</sup> | 31:16                             |        | _       | _      | _     | _      | _     |       | _      |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0000                        | UZIVIODE              | 15:0                              | ON     | _       | SIDL   | IREN  | RTSMD  | _     | UEN-  |        | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U2STA <sup>(1)</sup>  | 31:16                             |        | _       | _      | _     | _      | _     |       | ADM_EN |        |         |       | ADDR     | R<7:0>   |      |        |       | 0000       |

| 0010                        | U2S1A\''              | 15:0                              | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISE | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6820                        | U2TXREG               | 31:16                             |        | _       | _      |       | _      | _     |       | _      |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0020                        | UZTANLO               | 15:0                              |        | _       | _      | _     | _      | _     |       | TX8    |        |         |       | Transmit | Register |      |        |       | 0000       |

| 6830                        | U2RXREG               | 31:16                             |        | _       | _      | _     | _      | _     |       | _      |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0000                        | OZIVANLO              | 15:0                              |        | _       | _      | _     | _      | _     |       | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6840                        | U2BRG <sup>(1)</sup>  | 31:16                             | _      | _       | _      | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 0040                        | OZBIKO                | 15:0                              |        |         |        |       |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

| 6A00                        | U5MODE <sup>(1)</sup> | 31:16                             |        | _       | _      | _     | _      | _     |       | _      |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| UNOU                        | OSINIODE              | 15:0                              | ON     | _       | SIDL   | IREN  | _      | _     | _     | _      | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6A10                        | U5STA <sup>(1)</sup>  | 31:16                             | _      | _       | _      | _     | _      | _     | _     | ADM_EN |        |         |       | ADDR     |          |      |        |       | 0000       |

| 0/110                       |                       | 15:0                              | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISE | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6A20                        | U5TXREG               | 31:16                             | _      | _       | _      | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 07120                       |                       | 15:0                              | _      | _       | _      | _     | _      | _     | _     | TX8    |        |         |       | Transmit | Register |      |        |       | 0000       |

| 6A30                        | U5RXREG               | 31:16                             | _      | _       | _      |       | _      | _     |       | _      | _      | _       | _     | _        | _        | _    | _      | _     | 0000       |

| J. 100                      |                       | 15:0 — — — — RX8 Receive Register |        |         |        |       |        |       | 1     | 0000   |        |         |       |          |          |      |        |       |            |

| 6A40                        | U5BRG <sup>(1)</sup>  | 31:16                             | _      | _       | _      | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | 0000       |

| 5, 110                      | 555.10                | 15:0                              |        |         |        |       |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

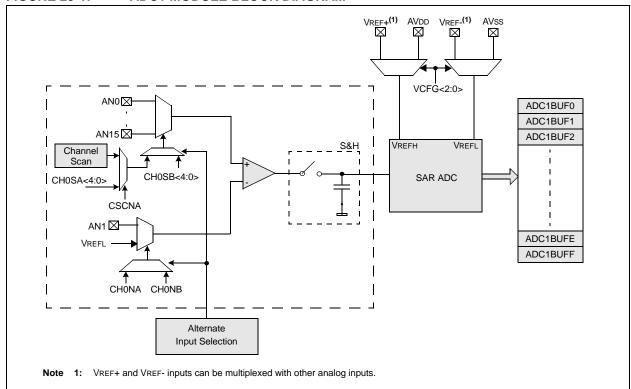

# 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold (S&H) circuit

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers to one S&H. The analog input multiplexers can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 23-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight 32-bit output formats when it is read from the result buffer.

#### FIGURE 23-1: ADC1 MODULE BLOCK DIAGRAM

#### **REGISTER 24-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN23           | MSEL2             | 23<1:0>           | FSEL23<4:0>       |                   |                   |                  |                  |  |  |

| 22,46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         | FLTEN21           | MSEL2             | MSEL21<1:0>       |                   | FSEL21<4:0>       |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN20           | 20 MSEL20<1:0>    |                   | FSEL20<4:0>       |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN23: Filter 23 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 30-29 MSEL23<1:0>: Filter 23 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL23<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN22: Filter 22 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 22-21 MSEL22<1:0>: Filter 22 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 20-16 FSEL22<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 24-21: CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)

bit 9 **TXHALFIF:** FIFO Transmit FIFO Half Empty Interrupt Flag bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a transmit buffer)

1 = FIFO is ≤ half full

0 = FIFO is > half full

$\overline{\text{TXEN}} = 0$ : (FIFO configured as a receive buffer)

Unused, reads '0'

bit 8 **TXEMPTYIF:** Transmit FIFO Empty Interrupt Flag bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a transmit buffer)

1 = FIFO is empty

0 = FIFO is not empty, at least 1 message queued to be transmitted

TXEN = 0: (FIFO configured as a receive buffer)

Unused, reads '0'

bit 7-4 **Unimplemented:** Read as '0'

bit 3 RXOVFLIF: Receive FIFO Overflow Interrupt Flag bit

TXEN = 1: (FIFO configured as a transmit buffer)

Unused, reads '0'

TXEN = 0: (FIFO configured as a receive buffer)

1 = Overflow event has occurred

0 = No overflow event occured

bit 2 **RXFULLIF:** Receive FIFO Full Interrupt Flag bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a transmit buffer)

Unused, reads '0'

TXEN = 0: (FIFO configured as a receive buffer)

1 = FIFO is full

0 = FIFO is not full

bit 1 RXHALFIF: Receive FIFO Half Full Interrupt Flag bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a transmit buffer)

Unused, reads '0'

TXEN = 0: (FIFO configured as a receive buffer)

1 = FIFO is  $\ge half full$

0 = FIFO is < half full

bit 0 **RXNEMPTYIF:** Receive Buffer Not Empty Interrupt Flag bit<sup>(1)</sup>

TXEN = 1: (FIFO configured as a transmit buffer)

Unused, reads '0'

TXEN = 0: (FIFO configured as a receive buffer)

1 = FIFO is not empty, has at least 1 message

0 = FIFO is empty

Note 1: This bit is read-only and reflects the status of the FIFO.

REGISTER 27-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2      | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------|------------------|----------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0                  |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                      | _                | _                    |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0                  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                      | _                | _                    |

| 15:8         | R/W-0             | U-0               | U-0               | U-0               | U-0               | R/W-0                  | R/W-0            | R/W-1                |

| 15.6         | ON <sup>(1)</sup> | _                 | _                 | _                 | _                 | VREFSEL <sup>(2)</sup> | BGSEL            | <1:0> <sup>(2)</sup> |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0            | R/W-0                |

| 7:0          | _                 | — CVROE CVRR      |                   | CVRSS             |                   |                        |                  |                      |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

Setting or clearing this bit does not affect the other bits in this register.

1 = Module is enabled

0 = Module is disabled and does not consume current

bit 14-11 Unimplemented: Read as '0'

bit 10 **VREFSEL:** Voltage Reference Select bit<sup>(2)</sup>

1 = CVREF = VREF+

0 = CVREF is generated by the resistor network

bit 9-8 **BGSEL<1:0>:** Band Gap Reference Source bits<sup>(2)</sup>

11 = IVREF = VREF+

10 = Reserved

01 = IVREF = 0.6V (nominal, default)

00 = IVREF = 1.2V (nominal)

bit 7 Unimplemented: Read as '0'

bit 6 CVROE: CVREFOUT Enable bit

1 = Voltage level is output on CVREFOUT pin

0 = Voltage level is disconnected from CVREFOUT pin

bit 5 CVRR: CVREF Range Selection bit

1 = 0 to 0.625 CVRSRC, with CVRSRC/24 step size

0 = 0.25 CVRSRC to 0.719 CVRSRC, with CVRSRC/32 step size

bit 4 CVRSS: CVREF Source Selection bit

1 = Comparator voltage reference source, CVRSRC = (VREF+) - (VREF-)

0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR < 3:0 > \le 15$  bits

When CVRR = 1:

When CVRR = 0:

$\overline{\text{CVREF}} = \frac{1}{4} \bullet (\overline{\text{CVRSRC}}) + (\overline{\text{CVR}} < 3:0 > /32) \bullet (\overline{\text{CVRSRC}})$

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: These bits are not available on PIC32MX575/675/775/795 devices. On these devices, the reset value for CVRON is '0000'.

**TABLE 32-13: COMPARATOR SPECIFICATIONS**

| DC CHA        | RACTERI                | STICS                                 | (unless | ard Operating Conditions (see Note 3): 2.3V to so therwise stated) ing temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Ten |      |       |                                                                               |

|---------------|------------------------|---------------------------------------|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------------------------------------------------------------------------------|

| Param.<br>No. | Symbol Characteristics |                                       | Min.    | Typical                                                                                                                                                                                                                              | Max. | Units | Comments                                                                      |

| D300          | VIOFF                  | Input Offset Voltage                  | _       | ±7.5                                                                                                                                                                                                                                 | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                     |

| D301          | VICM                   | Input Common Mode Voltage             | 0       | _                                                                                                                                                                                                                                    | VDD  | V     | AVDD = VDD,<br>AVSS = VSS<br>(Note 2)                                         |

| D302          | CMRR                   | Common Mode Rejection Ratio           | 55      | _                                                                                                                                                                                                                                    | _    | dB    | Max VICM = (VDD - 1)V (Note 2)                                                |

| D303          | TRESP                  | Response Time                         | _       | 150                                                                                                                                                                                                                                  | 400  | ns    | AVDD = VDD,<br>AVSS = VSS<br>(Notes 1, 2)                                     |

| D304          | ON2ov                  | Comparator Enabled to Output<br>Valid | _       | _                                                                                                                                                                                                                                    | 10   | μS    | Comparator module is configured before setting the comparator ON bit (Note 2) |

| D305          | IVREF                  | Internal Voltage Reference            | 0.57    | 0.6                                                                                                                                                                                                                                  | 0.63 | V     | For devices without BGSEL<1:0>                                                |

|               |                        |                                       | 1.14    | 1.2                                                                                                                                                                                                                                  | 1.26 | V     | BGSEL<1:0> = 00                                                               |

|               |                        |                                       | 0.57    | 0.6                                                                                                                                                                                                                                  | 0.63 | V     | BGSEL<1:0> = 01                                                               |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**<sup>2:</sup>** These parameters are characterized but not tested.

**<sup>3:</sup>** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

TABLE 32-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

| AC CHA        | RACTERIS | STICS                  |                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |          |       |                         |  |  |

|---------------|----------|------------------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-------|-------------------------|--|--|

| Param.<br>No. | Symbol   | Charact                | eristics                  | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Max.     | Units | Conditions              |  |  |

| IM10          | TLO:SCL  | Clock Low Time         | 100 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                | _        | μS    | _                       |  |  |

|               |          |                        | 400 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                | _        | μS    | _                       |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | Трв * (BRG + 2)                                                                                                                                                                                                                                | _        | μS    | _                       |  |  |

| IM11          | THI:SCL  | Clock High Time        | 100 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                | _        | μS    |                         |  |  |

|               |          |                        | 400 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                | _        | μS    | _                       |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | μS    | _                       |  |  |

| IM20          | TF:SCL   | SDAx and SCLx          | 100 kHz mode              | _                                                                                                                                                                                                                                              | 300      | ns    | CB is specified to be   |  |  |

|               |          | Fall Time              | 400 kHz mode              | 20 + 0.1 CB                                                                                                                                                                                                                                    | 300      | ns    | from 10 to 400 pF       |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                              | 100      | ns    |                         |  |  |

| IM21          | TR:SCL   | SDAx and SCLx          | 100 kHz mode              | _                                                                                                                                                                                                                                              | 1000     | ns    | CB is specified to be   |  |  |

|               |          | Rise Time              | 400 kHz mode              | 20 + 0.1 CB                                                                                                                                                                                                                                    | 300      | ns    | from 10 to 400 pF       |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                              | 300      | ns    |                         |  |  |

| IM25          | TSU:DAT  | Data Input             | 100 kHz mode              | 250                                                                                                                                                                                                                                            | _        | ns    | _                       |  |  |

|               |          | Setup Time             | 400 kHz mode              | 100                                                                                                                                                                                                                                            | _        | ns    |                         |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | 100                                                                                                                                                                                                                                            | _        | ns    |                         |  |  |

| IM26          | THD:DAT  | Data Input             | 100 kHz mode              | 0                                                                                                                                                                                                                                              | _        | μS    | _                       |  |  |

|               |          | Hold Time              | 400 kHz mode              | 0                                                                                                                                                                                                                                              | 0.9      | μS    |                         |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | 0                                                                                                                                                                                                                                              | 0.3      | μS    |                         |  |  |

| IM30          | Tsu:sta  | Start Condition        | 100 kHz mode              | Трв * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | Only relevant for       |  |  |

|               |          | Setup Time             | 400 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | Repeated Start          |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | condition               |  |  |

| IM31          | THD:STA  | Start Condition        | 100 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | After this period, the  |  |  |

|               |          | Hold Time              | 400 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | first clock pulse is    |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | generated               |  |  |

| IM33          | Tsu:sto  | Stop Condition         | 100 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | _                       |  |  |

|               |          | Setup Time             | 400 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    |                         |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    |                         |  |  |

| IM34          | THD:STO  | Stop Condition         | 100 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    | _                       |  |  |

|               |          | Hold Time              | 400 kHz mode              | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    |                         |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | TPB * (BRG + 2)                                                                                                                                                                                                                                | _        | ns    |                         |  |  |

| IM40          | TAA:SCL  | Output Valid from      |                           |                                                                                                                                                                                                                                                | 3500     | ns    |                         |  |  |

| IIVI-10       | I/VI.OOL | Clock                  | 400 kHz mode              |                                                                                                                                                                                                                                                | 1000     | ns    |                         |  |  |

|               |          |                        | 1 MHz mode <sup>(2)</sup> | _                                                                                                                                                                                                                                              | 350      | ns    | _                       |  |  |

| IM45          | TBF:SDA  | Bus Free Time          | 100 kHz mode              | 4.7                                                                                                                                                                                                                                            |          | μS    | The amount of time the  |  |  |

|               | 751.054  | 2401100111110          | 400 kHz mode              | 1.3                                                                                                                                                                                                                                            | _        | μS    | bus must be free before |  |  |