Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

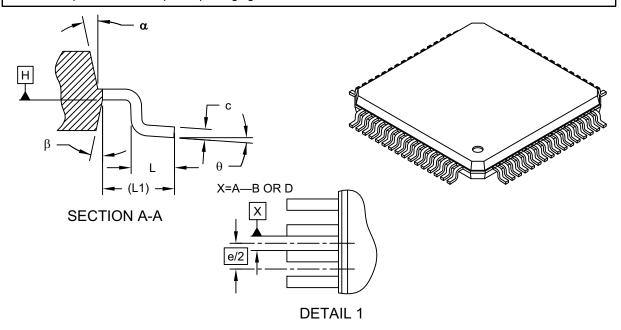

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128ht-v-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**TABLE 7-6:** INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES

| SS                          |                                 |               |         | Bits    |         |                               |                               |                               |                               |                             |                               |                               |                             |                       |            |        |        |        |            |

|-----------------------------|---------------------------------|---------------|---------|---------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14   | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3       | 18/2   | 17/1   | 16/0   | All Resets |

|                             | INTCON                          | 31:16         | _       | _       | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _          | _      | _      | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | _       | _       | _       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | _                             | _                           | INT4EP                | INT3EP     | INT2EP | INT1EP | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | -       | _       | _       | _                             | _                             | -                             | _                             | _                           | _                             | _                             | _                           | _                     | -          | _      | _      | _      | 0000       |

| 1010                        | INTOTAL                         | 15:0          | _       | _       | _       | _                             | _                             |                               | SRIPL<2:0>                    |                             | _                             | _                             |                             |                       | VEC        | <5:0>  |        |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |         |         |                               |                               |                               |                               | IPTMR                       | R<31:0>                       |                               |                             |                       |            |        |        |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF     | OC4IF  | IC4IF  | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF   | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF     | CS1IF  | CS0IF  | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF  | IC1EIF  | ETHIF                         | _                             | -                             | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF     | DMA2IF | DMA1IF | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF  | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF     | PMPIF  | AD1IF  | CNIF   | 0000       |

|                             |                                 | 31:16         | _       | _       | _       |                               | _                             | —                             | - IZC5511                     | —                           | - IZO4WIII                    | - IZC43II                     | —                           | _                     | _          | _      | _      | _      | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _       | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF      | PMPEIF | IC5EIF | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE     | OC4IE  | IC4IE  | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE   | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE     | CS1IE  | CS0IE  | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE  | IC1EIE  | ETHIE                         | _                             | _                             | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE     | DMA2IE | DMA1IE | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE  | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE     | PMPIE  | AD1IE  | CNIE   | 0000       |

| 4000                        | IFOO                            | 31:16         | _       | _       | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _          | _      | _      | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | _       | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE      | PMPEIE | IC5EIE | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         | _       | _       | _       |                               | INT0IP<2:0>                   | •                             | INTOIS                        | S<1:0>                      | _                             | _                             | _                           |                       | CS1IP<2:0> | •      | CS1IS  | S<1:0> | 0000       |

| 1090                        | IFCU                            | 15:0          | _       | _       | _       |                               | CS0IP<2:0>                    |                               | CS0IS                         | S<1:0>                      | _                             | _                             | _                           |                       | CTIP<2:0>  |        | CTIS   | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         | -       | _       | _       |                               | INT1IP<2:0>                   |                               |                               | S<1:0>                      | _                             | _                             | _                           |                       | OC1IP<2:0> | •      | OC1IS  |        | 0000       |

|                             | 0.                              | 15:0          |         | _       | _       |                               | IC1IP<2:0>                    |                               | IC1IS                         |                             | _                             | _                             |                             |                       | T1IP<2:0>  |        | T1IS-  |        | 0000       |

| 10B0                        | IPC2                            | 31:16         | _       |         | _       |                               | INT2IP<2:0>                   |                               | INT2IS                        |                             | _                             | _                             | _                           | '                     | OC2IP<2:0> | •      | OC2IS  |        | 0000       |

|                             | -                               | 15:0          | _       | _       | _       |                               | IC2IP<2:0>                    |                               | IC2IS                         |                             | _                             | _                             | _                           |                       | T2IP<2:0>  |        | T2IS-  |        | 0000       |

| 10C0                        | IPC3                            | 31:16         | _       | _       | _       |                               | INT3IP<2:0>                   |                               | INT3IS                        |                             | _                             | _                             | _                           | '                     | OC3IP<2:0> | •      | OC3IS  |        | 0000       |

|                             |                                 | 15:0          | _       |         | _       |                               | IC3IP<2:0>                    |                               | IC3IS                         |                             | _                             | _                             | _                           |                       | T3IP<2:0>  |        | T3IS-  | <1:0>  | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note Registers" for more information.

These bits are not available on PIC32MX664 devices.

This register does note have associated CLR, SET, and INV registers.

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)

```

bit 12-10 IP01<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 9-8

IS01<1:0>: Interrupt Sub-priority bits

11 = Interrupt sub-priority is 3

10 = Interrupt sub-priority is 2

01 = Interrupt sub-priority is 1

00 = Interrupt sub-priority is 0

bit 7-5

Unimplemented: Read as '0'

bit 4-2

IP00<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 1-0

IS00<1:0>: Interrupt Sub-priority bits

11 = Interrupt sub-priority is 3

10 = Interrupt sub-priority is 2

01 = Interrupt sub-priority is 1

00 = Interrupt sub-priority is 0

```

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | R/W-y             | R/W-y             | R/W-y             | R/W-0             | R/W-0            | R/W-1            |

| 31:24        | -                 | _                 | P                 | LLODIV<2:0        | >                 | F                 | FRCDIV<2:0>      |                  |

| 00.40        | U-0               | R-0               | R-1               | R/W-y             | R/W-y             | R/W-y             | R/W-y            | R/W-y            |

| 23:16        | _                 | SOSCRDY           | PBDIVRDY          | PBDI\             | /<1:0>            | Р                 | LLMULT<2:0>      | •                |

| 45.0         | U-0               | R-0               | R-0               | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y            |

| 15:8         | _                 |                   | COSC<2:0>         |                   |                   |                   | NOSC<2:0>        |                  |

| 7.0          | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0             | R/W-0             | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK             | SLOCK             | SLPEN             | CF                | UFRCEN            | SOSCEN           | OSWEN            |

**Legend:** y = Value set from Configuration bits on POR

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29-27 PLLODIV<2:0>: Output Divider for PLL

111 = PLL output divided by 256

110 = PLL output divided by 64

101 = PLL output divided by 32

100 = PLL output divided by 16

011 = PLL output divided by 8

010 = PLL output divided by 4

001 = PLL output divided by 2

000 = PLL output divided by 1

bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

111 = FRC divided by 256

110 = FRC divided by 64

101 = FRC divided by 32

100 = FRC divided by 16

011 = FRC divided by 8

010 = FRC divided by 4

001 = FRC divided by 2 (default setting)

000 = FRC divided by 1

bit 23 Unimplemented: Read as '0'

bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

1 = Indicates that the Secondary Oscillator is running and is stable

0 = Secondary Oscillator is still warming up or is turned off

bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

1 = PBDIV<1:0> bits can be written

0 = PBDIV<1:0> bits cannot be written

bit 20-19 PBDIV<1:0>: Peripheral Bus Clock (PBCLK) Divisor bits

11 = PBCLK is SYSCLK divided by 8 (default)

10 = PBCLK is SYSCLK divided by 4

01 = PBCLK is SYSCLK divided by 2

00 = PBCLK is SYSCLK divided by 1

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

REGISTER 9-8: CHEW3: CACHE WORD 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |

| 22.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   |                   |                   | CHEW3<            | :23:16>           |                   |                  |                  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   |                   |                   | CHEW3             | <15:8>            |                   |                  |                  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | CHEW3             | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

**Note:** This register is a window into the cache data array and is only readable if the device is not code-protected.

#### **REGISTER 9-9: CHELRU: CACHE LRU REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 31.24        | _                 | _                 | _                 | _                 |                   | _                 | _                | CHELRU<24>       |

| 22,46        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | CHELRI            | J<23:16>          |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHELR             | U<15:8>           |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHELF             | RU<7:0>           |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 CHELRU<24:0>: Cache Least Recently Used State Encoding bits

Indicates the pseudo-LRU state of the cache.

#### REGISTER 9-10: CHEHIT: CACHE HIT STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   |                   | CHEHIT<           | :31:24>           |                   |                  |                  |

| 22:40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   |                   |                   | CHEHIT<           | :23:16>           |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   |                   |                   | CHEHIT            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | CHEHIT            | <7:0>             |                   |                  |                  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 CHEHIT<31:0>: Cache Hit Count bits

Incremented each time the processor issues an instruction fetch or load that hits the prefetch cache from a cacheable region. Non-cacheable accesses do not modify this value.

## REGISTER 9-11: CHEMIS: CACHE MISS STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31.24        |                   |                   |                   | CHEMIS<           | <31:24>           |                   |                  |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23.10        |                   |                   |                   | CHEMIS<           | <23:16>           |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   |                   |                   | CHEMIS            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   |                   | CHEMIS            | S<7:0>            |                   |                  |                  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 CHEMIS<31:0>: Cache Miss Count bits

Incremented each time the processor issues an instruction fetch from a cacheable region that misses the prefetch cache. Non-cacheable accesses do not modify this value.

| TABLE 10-3: DN | IA CHANNELS 0-7 REGISTER MAP ( | (CONTINUED) |

|----------------|--------------------------------|-------------|

|----------------|--------------------------------|-------------|

| ess                         |                                 |               | Bits   |                   |       |            |               |       |      |        |                  |                  |                 |           |                  |        |        |        |              |

|-----------------------------|---------------------------------|---------------|--------|-------------------|-------|------------|---------------|-------|------|--------|------------------|------------------|-----------------|-----------|------------------|--------|--------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14             | 29/13 | 28/12      | 27/11         | 26/10 | 25/9 | 24/8   | 23/7             | 22/6             | 21/5            | 20/4      | 19/3             | 18/2   | 17/1   | 16/0   | All Resets   |

| 3290                        | DCH2DAT                         | 31:16         | _      | _                 | _     | _          | _             | _     | _    | _      | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

| 3230                        | DOMEDA                          | 15:0          | _      | _                 | _     | _          | _             | _     | _    | _      |                  |                  |                 | CHPDA     | \T<7:0>          | •      |        |        | 0000         |

| 32A0                        | DCH3CON                         | 31:16         | _      |                   | _     | _          |               | _     | _    | _      | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

|                             |                                 | 15:0          | CHBUSY |                   | _     |            |               | _     | _    | CHCHNS | CHEN             | CHAED            | CHCHN           | CHAEN     |                  | CHEDET | CHPR   | I<1:0> | 0000         |

| 32B0                        | DCH3ECON                        | 31:16         | _      | _                 | _     | -          |               | _     | _    | _      | OFOROE           | OARORT           | DATEN           | CHAIR     |                  |        |        |        | 00FF         |

| -                           |                                 | 15:0<br>31:16 |        |                   | _     | CHSIR:     |               |       |      |        | CFORCE<br>CHSDIE | CABORT<br>CHSHIE | PATEN<br>CHDDIE | SIRQEN    | AIRQEN<br>CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000         |

| 32C0                        | DCH3INT                         | 15:0          | _      |                   |       |            |               | _     | _    |        | CHSDIF           | CHSHIF           | CHDDIE          | CHDHIF    | CHBCIE           | CHCCIE | CHTAIF | CHERIF | 0000         |

|                             |                                 | 31:16         |        |                   |       |            |               |       |      |        |                  | OFIOTIII         | OFIDDII         | OFIDERIII | OFIDOR           | OHOOH  | OHIAII | OFFERM | 0000         |

| 32D0                        | DCH3SSA                         | 15:0          |        |                   |       |            |               |       |      | CHSSA  | N<31:0>          |                  |                 |           |                  |        |        |        | 0000         |

| 0050                        | DOLLODOA                        | 31:16         |        |                   |       |            |               |       |      | OUDOA  | 04.0             |                  |                 |           |                  |        |        |        | 0000         |

| 32E0                        | DCH3DSA                         | 15:0          |        |                   |       |            |               |       |      | CHDSA  | 1<31:0>          |                  |                 |           |                  |        |        |        | 0000         |

| 32F0                        | DCH3SSIZ                        | 31:16         | _      | _                 | _     | -          | -             | _     | _    | _      | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

| 321 0                       | DOMOGOL                         | 15:0          |        | CHSSIZ<15:0> 0000 |       |            |               |       |      |        |                  |                  |                 |           |                  |        |        |        |              |

| 3300                        | DCH3DSIZ                        | 31:16         | _      | _                 | _     | _          | _             | _     | _    |        | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

|                             |                                 | 15:0          |        |                   |       |            |               |       |      | CHDSIZ | Z<15:0>          |                  |                 |           |                  |        |        |        | 0000         |

| 3310                        | DCH3SPTR                        | 31:16<br>15:0 |        | _                 | _     | _          | _             | _     | _    | CHSPTI | P <15:0>         | _                | _               | _         | _                | _      | _      | _      | 0000         |

|                             |                                 | 31:16         | _      | _                 | _     | _          | _             | _     | _    |        | —<br>—           | _                | _               | _         | _                | _      | _      | _      | 0000         |

| 3320                        | DCH3DPTR                        | 15:0          |        |                   | _     |            |               | _     | _    | CHDPT  |                  |                  | _               | _         | _                |        | _      |        | 0000         |

|                             |                                 | 31:16         | _      | _                 | _     | _          | _             | _     | _    |        | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

| 3330                        | DCH3CSIZ                        | 15:0          |        |                   |       |            |               |       |      | CHCSIZ | Z<15:0>          |                  |                 |           |                  |        |        |        | 0000         |

| 22.40                       | DOLLOODED                       | 31:16         | _      | _                 | _     | _          | _             | _     | _    | _      | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

| 3340                        | DCH3CPTR                        | 15:0          |        |                   |       |            |               |       |      | CHCPT  | R<15:0>          |                  |                 |           |                  |        |        |        | 0000         |

| 3350                        | DCH3DAT                         | 31:16         | _      | _                 | _     | _          | _             | _     | _    | _      | _                | _                | _               | _         | _                | _      | _      | _      | 0000         |

| 0000                        | DONODAN                         | 15:0          | _      | _                 | _     | _          |               | _     | _    | _      |                  |                  | I               | CHPDA     | \T<7:0>          | 1      | 1      |        | 0000         |

| 3360                        | DCH4CON                         | 31:16         |        | _                 | _     | _          | _             | _     | _    |        | _                |                  |                 |           | _                |        | _      |        | 0000         |

|                             |                                 | 15:0          | CHBUSY |                   |       |            |               | _     |      | CHCHNS | CHEN             | CHAED            | CHCHN           | CHAEN     |                  | CHEDET | CHPR   | I<1:0> | 0000         |

| 3370                        | DCH4ECON                        | 31:16<br>15:0 | _      | _                 | _     | —<br>CHSIR | —<br>O < 7:0> | _     | _    | _      | CFORCE           | CABORT           | PATEN           | SIRQEN    | Q<7:0><br>AIRQEN | _      | _      | _      | 00FF<br>FF00 |

|                             |                                 | 31:16         | _      | _                 | _     | — CHSIK    | J<7:0>        | _     | _    | _      | CHSDIE           | CHSHIE           | CHDDIE          | CHDHIE    | CHBCIE           | CHCCIE | CHTAIE | CHERIE | 0000         |

| 3380                        | DCH4INT                         | 15:0          | _      | _                 | _     | _          |               | _     | _    | _      | CHSDIF           | CHSHIF           | CHDDIF          | CHDHIF    | CHBCIF           | CHCCIF | CHTAIF | CHERIF | 0000         |

|                             |                                 | 31:16         |        |                   |       |            |               |       |      |        |                  | 23               |                 |           |                  |        | 2      |        | 0000         |

| 3390                        | DCH4SSA                         | 15:0          |        |                   |       |            |               |       |      | CHSSA  | \<31:0>          |                  |                 |           |                  |        |        |        | 0000         |

| 2240                        | DCH4DC4                         | 31:16         |        |                   |       |            |               |       |      | CHDCA  | -21:0-           |                  |                 |           |                  |        |        |        | 0000         |

| 33A0                        | DCH4DSA                         | 15:0          |        |                   |       |            |               |       |      | CHDSA  | N<01.U>          |                  |                 |           |                  |        |        |        | 0000         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

<sup>2:</sup> DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

- bit 6 CRCAPP: CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but not to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 CRCTYP: CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

#### REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 24.24        | U-0                                           | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                                             | _                |

| 22,46        | U-0                                           | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                                             | _                |

| 15:8         | U-0                                           | U-0              |

| 15.6         |                   | _                 | _                 | _                 | _                 | _                 | _                                             | _                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEE: Bit Stuff Error Interrupt Enable bit

1 = BTSEF interrupt is enabled0 = BTSEF interrupt is disabled

bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

1 = BMXEF interrupt is enabled0 = BMXEF interrupt is disabled

bit 5 DMAEE: DMA Error Interrupt Enable bit

1 = DMAEF interrupt is enabled0 = DMAEF interrupt is disabled

bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

1 = BTOEF interrupt is enabled0 = BTOEF interrupt is disabled

bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

1 = DFN8EF interrupt is enabled0 = DFN8EF interrupt is disabled

bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

1 = CRC16EF interrupt is enabled0 = CRC16EF interrupt is disabled

bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit (1)

1 = CRC5EF interrupt is enabled0 = CRC5EF interrupt is disabled

**EOFEE:** EOF Error Interrupt Enable bit<sup>(2)</sup>

1 = EOF interrupt is enabled0 = EOF interrupt is disabled

bit 0 PIDEE: PID Check Failure Interrupt Enable bit

1 = PIDEF interrupt is enabled0 = PIDEF interrupt is disabled

Note 1: Device mode.

Host mode.

2:

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 PPBRST: Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit(4)

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit (5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

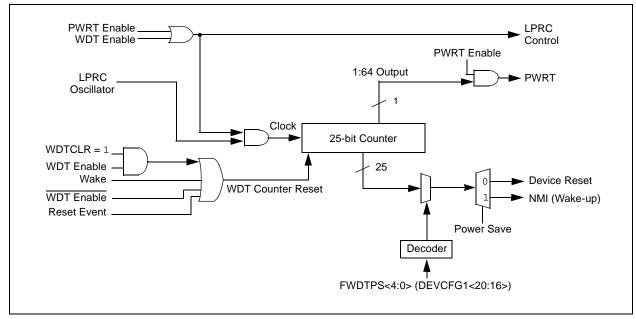

## 15.0 WATCHDOG TIMER (WDT)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Watchdog Timer and Power-up Timer" in the "PIC32 (DS60001114) Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes the operation of the WDT and Power-up Timer of the PIC32MX5XX/6XX/7XX.

The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are key features of the WDT module:

- · Configuration or software controlled

- · User-configurable time-out period

- · Can wake the device from Sleep or Idle mode

FIGURE 15-1: WATCHDOG TIMER AND POWER-UP TIMER BLOCK DIAGRAM

**NOTES:**

# 20.1 Control Registers

# TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP

| 0.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SS                          | LL 20-1.                                |           | Bits   |         |        |       |        |       |       |        |        |         |       |          |          |      |        |       |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------------------|-----------|--------|---------|--------|-------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| 000   01500E    150   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015   015    | Virtual Address<br>(BF80_#) | Register<br>Name                        | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  |        |        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6000                        | U1MODE <sup>(1)</sup>                   |           |        | _       |        |       |        | -     | -     | _      |        |         |       |          |          |      | _      | -     |            |

| 17   17   17   18   17   17   18   17   18   18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             | 01111022                                | _         | ON     | _       | SIDL   | IREN  | RTSMD  |       | UEN-  |        | WAKE   | LPBACK  | ABAUD |          |          | PDSE | L<1:0> | STSEL | 0000       |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 6010                        | U1STA <sup>(1)</sup>                    |           | _      |         |        | _     |        |       |       |        |        |         |       |          |          | 1    | 1      |       | -          |

| Marker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |                                         |           | UTXISE | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA |            |

| 15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 6020                        | U1TXREG                                 |           | _      | _       | _      |       |        |       |       |        |        | _       | _     | _        | _        | _    | _      | _     | 0000       |

| Marker                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                             |                                         |           | _      | _       | _      |       |        |       |       | TX8    |        | ı       |       | Transmit | Register | 1    |        |       | _          |

| March   Marc | 6030                        | U1RXREG                                 |           | _      | _       | _      | _     | _      | _     | _     | _      | _      | _       | _     | _        | _        | _    | _      | _     | _          |

| BRG   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             | • • • • • • • • • • • • • • • • • • • • |           | _      | _       | _      | _     |        |       |       | RX8    |        | ı       |       | Receive  | Register | 1    |        |       |            |

| 0000   04MODE   03116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 6040                        | U1BRG <sup>(1)</sup>                    |           | _      | _       | _      | _     | _      | _     |       | _      |        | _       | _     | _        | _        | _    | _      | _     | _          |

| MANOPETON   15.0   ON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             | •                                       | 15:0      |        | 1       | 1      |       |        |       |       | BRG<   | :15:0> | ı       |       | 1        | 1        | 1    |        |       |            |

| STATE   STAT | 6200                        | U4MODE <sup>(1)</sup>                   |           |        | _       |        | _     |        |       |       | _      |        | _       |       | _        |          | _    | _      |       | 0000       |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                             |                                         | <b></b>   | ON     | _       | SIDL   | IREN  |        |       |       |        | WAKE   | LPBACK  | ABAUD |          |          | PDSE | L<1:0> | STSEL |            |

| 150   UTXINES   UTXINES  | 6210                        | U4STA <sup>(1)</sup>                    |           |        |         |        |       |        |       |       |        |        |         |       |          |          | ı    |        |       | -          |