Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 1:PIC32MX5XX USB AND CAN FEATURES

|                  | USB and CAN |                         |                  |     |      |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|-------------|-------------------------|------------------|-----|------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins        | Program Memory (KB)     | Data Memory (KB) | USB | CAN  | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | Spl <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dWd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX534F064H  | 64          | 64 + 12 <sup>(1)</sup>  | 16               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX564F064H  | 64          | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX564F128H  | 64          | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX575F256H  | 64          | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX575F512H  | 64          | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX534F064L  | 100         | 64 + 12 <sup>(1)</sup>  | 16               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX564F064L  | 100         | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX564F128L  | 100         | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1    | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX575F256L  | 100         | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| PIC32MX575F512L  | 100         | 512 + 12 <b>(1)</b>     | 64               | 1   | 1    | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT,<br>PF,<br>BG        |

| Legend: PF, PT = | TQFP        | MR = Q                  | FN               |     | BG = | TFBG/                  | 4                                        | TL =                  | VTLA               | (5)                             |                              |             |         |      |       |                         |

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

**3:** Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "**Device Pin Tables**" section for more information.

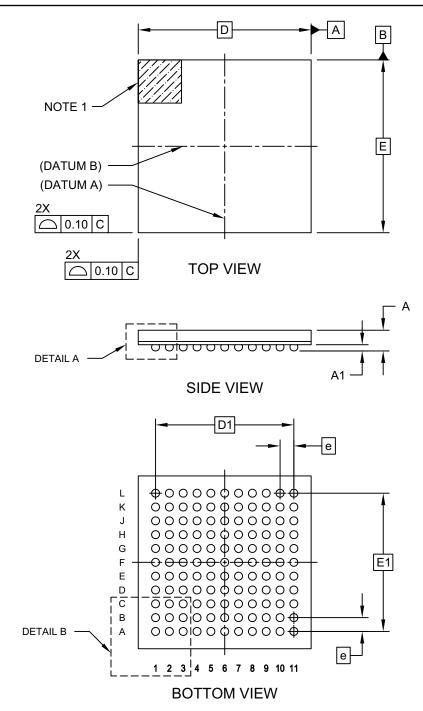

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices in the VTLA package are available upon request. Please contact your local Microchip Sales Office for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | BMXDU             | DBA<15:8>         |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | BMXDUDBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

### Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | —                    |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | -                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   | _                 | _                 | —                 | —                 |                   |                  | SWRST <sup>(1)</sup> |

### REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Le   | gend:          | HC = Cleared by hardware |                           |                    |  |  |  |  |

|------|----------------|--------------------------|---------------------------|--------------------|--|--|--|--|

| R =  | = Readable bit | W = Writable bit         | U = Unimplemented bit, re | ead as '0'         |  |  |  |  |

| -n : | = Value at POR | '1' = Bit is set         | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup> 1 = Enable software Reset event 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

|                             |                                 | P             | IC32M>  | (795F51      | 2H DE      | /ICES                         |                               |                               |                               |                             |                               |                               |                             |                       |                         |          |        |                 |            |

|-----------------------------|---------------------------------|---------------|---------|--------------|------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|----------|--------|-----------------|------------|

| sse                         |                                 |               |         |              |            |                               |                               |                               |                               | В                           | lits                          |                               |                             |                       |                         |          |        |                 |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14        | 29/13      | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2     | 17/1   | 16/0            | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _            | _          | —                             | —                             | —                             | _                             | _                           | —                             | —                             |                             | _                     |                         | _        | _      | SS0             | 0000       |

| 1000                        | INTCOM                          | 15:0          | —       | _            | —          | MVEC                          | —                             |                               | TPC<2:0>                      |                             | -                             | -                             | -                           | INT4EP                | INT3EP                  | INT2EP   | INT1EP | INT0EP          | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | _       | —            | —          | _                             | _                             | —                             | —                             |                             | -                             | _                             | —                           | —                     | —                       | —        | —      | —               | 0000       |

| 1010                        |                                 | 15:0          | —       | —            | —          | _                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC                     | <5:0>    |        |                 | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |              |            |                               |                               |                               |                               | IPTMF                       | R<31:0>                       |                               |                             |                       |                         |          |        |                 | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF      | I2C1BIF    | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | _                             | _                           | _                             | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF    | IC4IF  | T4IF            | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF        | IC3IF      | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF    | CS0IF  | CTIF            | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF       | IC1EIF     | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF   | DMA1IF | DMA0IF          | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF       | _          | _                             | _                             | U2TXIF<br>SPI4TXIF            | U2RXIF<br>SPI4RXIF            | U2EIF<br>SPI4EIF            | U3TXIF<br>SPI2TXIF            | U3RXIF<br>SPI2RXIF            | U3EIF<br>SPI2EIF            | CMP2IF                | CMP1IF                  | PMPIF    | AD1IF  | CNIF            | 0000       |

|                             |                                 | 31:16         | _       |              |            | _                             |                               | I2C5MIF                       | I2C5SIF                       | I2C5BIF                     | I2C4MIF                       | I2C4SIF                       | I2C4BIF                     | _                     |                         | _        | _      | _               | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _            |            |                               | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF   | IC5EIF | IC4EIF          | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE      | I2C1BIE    | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | _                             | -                           | -                             | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE    | IC4IE  | T4IE            | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE        | IC3IE      | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE    | CS0IE  | CTIE            | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE       | IC1EIE     | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE   | DMA1IE | DMA0IE          | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE       | _          | -                             | _                             | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE    | AD1IE  | CNIE            | 0000       |

| 1080                        | IEC2                            | 31:16         | _       | _            | _          | -                             | _                             | _                             | _                             | _                           | _                             | -                             | -                           | _                     | -                       | -        | _      | _               | 0000       |

| 1060                        | IEC2                            | 15:0          | —       | _            | _          | —                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE   | IC5EIE | IC4EIE          | 0000       |

| 1090                        | IPC0                            | 31:16         | —       | —            | —          |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | —                             | —                             | —                           |                       | CS1IP<2:0>              | ,        |        | S<1:0>          | 0000       |

| 1000                        |                                 | 15:0          | _       | _            | —          |                               | CS0IP<2:0>                    |                               |                               | S<1:0>                      | _                             | -                             | _                           |                       | CTIP<2:0>               |          |        | <1:0>           | 0000       |

| 10A0                        | IPC1                            | 31:16         | —       | -            | —          | ļ                             | INT1IP<2:0>                   | •                             |                               | S<1:0>                      | -                             | -                             | _                           |                       | OC1IP<2:0:              | >        |        | S<1:0>          | 0000       |

|                             |                                 | 15:0          | _       | _            | _          |                               | IC1IP<2:0>                    |                               |                               | <1:0>                       | _                             | _                             | _                           |                       | T1IP<2:0>               |          | _      | <1:0>           | 0000       |

| 10B0                        | IPC2                            | 31:16         | _       | _            | _          |                               | INT2IP<2:0>                   | •                             |                               | S<1:0>                      | _                             |                               |                             |                       | OC2IP<2:0:              | <b>`</b> |        | S<1:0>          | 0000       |

|                             |                                 | 15:0          | _       | _            | _          | <u> </u>                      | IC2IP<2:0>                    |                               | IC2IS                         |                             | —                             |                               |                             |                       | T2IP<2:0>               |          | -      | <1:0>           | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 | _       | _            |            |                               | INT3IP<2:0><br>IC3IP<2:0>     | •                             |                               | S<1:0><br><1:0>             |                               |                               |                             |                       | OC3IP<2:0:<br>T3IP<2:0> | >        |        | S<1:0><br><1:0> | 0000       |

| Legend                      | 1: x=1                          |               |         | Reset: — = u | nimplement | ed, read as '                 |                               | ues are sho                   | wn in hexade                  |                             |                               |                               |                             |                       | 1011 \2.02              |          | 1010   | <1.0Z           | 0000       |

### TABLE 7-4: INTERRUPT REGISTER MAP FOR PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. This bit is unimplemented on PIC32MX764F128H device. This register does not have associated CLR, SET, and INV registers.

PIC32MX5XX/6XX/7XX

2:

3:

| Т | ABLE 12 | PORTG REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H | Н. |

|---|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |         | PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES                                                                                                                   | ,  |

|   | ssa     | Bits                                                                                                                                                                                            |    |

| ö                          |                                 | Φ         |       |        |       |       |           |                  |        |                 |        |        | <i>(</i> 0 |      |        |        |      |      |           |

|----------------------------|---------------------------------|-----------|-------|--------|-------|-------|-----------|------------------|--------|-----------------|--------|--------|------------|------|--------|--------|------|------|-----------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13 | 28/12 | 27/11     | 26/10            | 25/9   | 24/8            | 23/7   | 22/6   | 21/5       | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Reset |

| 6180                       | TRISG                           | 31:16     | —     | —      | —     | _     | —         | —                | _      | —               | —      | —      | _          | _    | -      | _      | _    | _    | 0000      |

| 6160                       | TRIBU                           | 15:0      | _     | _      | _     | _     | _         |                  | TRISG9 | TRISG8          | TRISG7 | TRISG6 | _          |      | TRISG3 | TRISG2 | -    |      | 03CC      |

| 6100                       | PORTG                           | 31:16     | _     | _      | _     | _     | _         |                  | _      | _               | _      | _      | _          |      |        |        | -    |      | 0000      |

| 6190                       | PURIG                           | 15:0      | _     | _      | _     | _     | _         |                  | RG9    | RG8             | RG7    | RG6    | _          |      | RG3    | RG2    | -    |      | xxxx      |

| 61A0                       | LATG                            | 31:16     | _     | _      | _     | _     | _         |                  | _      | _               | _      | _      | _          |      |        |        | -    |      | 0000      |

| OTAU                       | LAIG                            | 15:0      | _     | _      | _     | _     | _         |                  | LATG9  | LATG8           | LATG7  | LATG6  | _          |      | LATG3  | LATG2  | -    |      | xxxx      |

| 61B0                       | ODCG                            | 31:16     | _     | _      | _     | _     | -         | _                | _      | _               | _      | -      | _          |      |        | -      | _    |      | 0000      |

| 0180                       | ODCG                            | 15:0      | -     | _      | _     | _     | -         | _                | ODCG9  | ODCG8           | ODCG7  | ODCG6  | _          |      | ODCG3  | ODCG2  | _    |      | 0000      |

| Laware                     |                                 |           |       | Divisi |       |       | fal Deset | all and a second |        | dia statistical |        |        |            |      |        |        |      |      |           |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

### TABLE 12-12: PORTG REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 |           |         |         |         |         |       |       |        | Bi     | ts     |        |      |      |        |        |        |        | 6          |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6180                        | TRISG                           | 31:16     | _       | —       | _       | -       | _     | —     | -      | —      | —      | -      | —    | -    | -      | -      | -      | -      | 0000       |

| 0100                        | TRISG                           | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _     | _     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF       |

| 6100                        | PORTG                           | 31:16     |         | _       |         | _       |       | -     | -      | -      | -      | —      | -    | —    | —      | —      | _      | —      | 0000       |

| 6190                        | PURIG                           | 15:0      | RG15    | RG14    | RG13    | RG12    |       |       | RG9    | RG8    | RG7    | RG6    |      | -    | RG3    | RG2    | RG1    | RG0    | xxxx       |

| 61A0                        | LATG                            | 31:16     | -       | _       |         | _       | -     | -     | -      | -      | -      | —      | -    | —    | —      | —      | —      | —      | 0000       |

| 61A0                        | LAIG                            | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | _    | -    | LATG3  | LATG2  | LATG1  | LATG0  | xxxx       |

| 61B0                        | ODCG                            | 31:16     |         | —       | _       | _       |       | _     |        | _      | _      | —      | _    | —    | —      | —      | —      | —      | 0000       |

| 0160                        | ODCG                            | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | -    | _    | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                 | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

### REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Legend:           | HC = Cleared by hardwar | e                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the I<sup>2</sup>C module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the I<sup>2</sup>C module; all I<sup>2</sup>C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

- bit 12 **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

0 = Hold SCLx clock low (clock stretch)

If STREN = 1:

Bit is R/W (software can write '0' to initiate stretch and write '1' to release clock). Cleared by hardware at the beginning of a slave transmission and at the end of slave reception.

If STREN = 0:

Bit is R/S (software can only write '1' to release clock). Cleared by hardware at the beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C reserved address rule is not enabled

- bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 DISSLW: Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

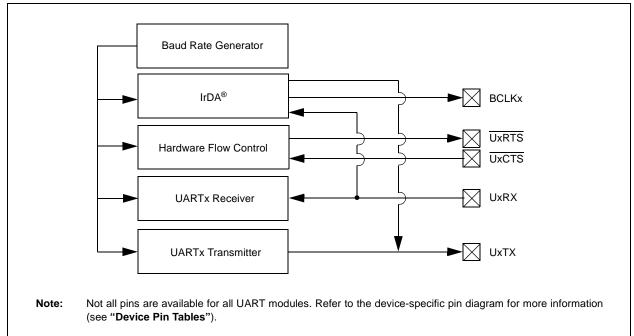

### 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in the PIC32MX5XX/6XX/7XX family of devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN 1.2 and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

The following are primary features of the UART module:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 20 Mbps at 80 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (ninth bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- LIN 2.1 Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 20-1 illustrates a simplified block diagram of the UART module.

### FIGURE 20-1: UART SIMPLIFIED BLOCK DIAGRAM

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24            |                   | YEAR1             | 0<3:0>            |                   | YEAR01<3:0>       |                   |                  |                  |

| 00.40            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16 MC         |                   |                   | 10<3:0>           |                   | MONTH01<3:0>      |                   |                  |                  |

| 45.0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8             |                   | DAY10             | <3:0>             | 3:0>              |                   | DAY01<3:0>        |                  |                  |

| 7.0              | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0              | —                 | —                 | _                 | _                 |                   | WDAYC             | )1<3:0>          |                  |

|                  |                   | •                 |                   |                   | •                 |                   |                  |                  |

| Legend:          |                   |                   |                   |                   |                   |                   |                  |                  |

| R = Readable bit |                   |                   | W = Writable bit  |                   | U = Unimple       | emented bit, re   | ead as '0'       |                  |

0' = Bit is cleared

### REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10 digits

'1' = Bit is set

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1 digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10 digits; contains a value from 0 to 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1 digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10 digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1 digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

-n = Value at POR

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1 digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

x = Bit is unknown

|              |                   |                       |                       |                           |                   | •                 | /                |                  |

|--------------|-------------------|-----------------------|-----------------------|---------------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4         | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0                   | U-0                   | U-0                       | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                     | —                     | _                         | —                 | —                 | _                | —                |

| 00.40        | U-0               | U-0                   | U-0                   | R/W-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | —                 | —                     | —                     | FSIZE<4:0> <sup>(1)</sup> |                   |                   |                  |                  |

| 15.0         | U-0               | S/HC-0                | S/HC-0                | R/W-0                     | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | FRESET                | UINC                  | DONLY <sup>(1)</sup>      | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R-0                   | R-0                   | R-0                       | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | TXEN              | TXABAT <sup>(2)</sup> | TXLARB <sup>(3)</sup> | TXERR <sup>(3)</sup>      | TXREQ             | RTREN             | TXPR             | <1:0>            |

### **REGISTER 24-20:** CiFIFOCONn: CAN FIFO CONTROL REGISTER 'n' (n = 0 THROUGH 31)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-21 Unimplemented: Read as '0'

| bit 20-16 FSIZE<4:0>: FIFO Size bits' | bit 20-16 | E<4:0>: FIFO Size bits <sup>(1)</sup> |

|---------------------------------------|-----------|---------------------------------------|

|---------------------------------------|-----------|---------------------------------------|

- 11111 = FIFO is 32 messages deep

- •

- 00010 = FIFO is 3 messages deep 00001 = FIFO is 2 messages deep

00000 = FIFO is 1 message deep

### bit 15 Unimplemented: Read as '0'

### bit 14 FRESET: FIFO Reset bits

1 = FIFO will be reset when bit is set, cleared by hardware when FIFO is reset. After setting, the user should poll whether this bit is clear before taking any action.

### 0 = No effect

### bit 13 UINC: Increment Head/Tail bit

$\frac{TXEN = 1:}{When this bit is set the FIFO head will increment by a single message$  $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message$ When this bit is set the FIFO tail will increment by a single message $<math display="block">\frac{TXEN = 0:}{When this bit is set the FIFO tail will increment by a single message }$

### bit 12 DONLY: Store Message Data Only bit<sup>(1)</sup>

$\frac{\text{TXEN} = 1:}{\text{This bit is not used and has no effect.}}$   $\frac{\text{TXEN} = 0:}{\text{TXEN} = 0:}$ (FIFO configured as a Receive FIFO)

1 =Only data bytes will be stored in the FIFO

0 = Full message is stored, including identifier

### bit 11-8 Unimplemented: Read as '0'

- bit 7 **TXEN:** TX/RX Buffer Selection bit

- 1 = FIFO is a Transmit FIFO

- 0 = FIFO is a Receive FIFO

- **Note 1:** These bits can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> bits (CiCON<23:21>) = 100).

- 2: This bit is updated when a message completes (or aborts) or when the FIFO is reset.

- 3: This bit is reset on any read of this register or when the FIFO is reset.

### REGISTER 25-17: ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK STATISTICS REGISTER

| Bit<br>Range          | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24                 | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 22:46                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16                 | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |

| 15.0                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8 FRMTXOKCNT<15:8> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0                   |                   | FRMTXOKCNT<7:0>   |                   |                   |                   |                   |                  |                  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

### REGISTER 25-36: EMAC1MIND: ETHERNET CONTROLLER MAC MII MANAGEMENT INDICATORS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   | —                 | _                 | —                 | —                 | -                | —                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | —                 |                   | LINKFAIL          | NOTVALID          | SCAN             | MIIMBUSY         |

### Legend:

| 5                 |                  |                          |                    |   |

|-------------------|------------------|--------------------------|--------------------|---|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown | 1 |

### bit 31-4 Unimplemented: Read as '0'

bit 3 LINKFAIL: Link Fail bit

When '1' is returned - indicates link fail has occurred. This bit reflects the value last read from the PHY status register.

bit 2 NOTVALID: MII Management Read Data Not Valid bit When '1' is returned - indicates an MII management read cycle has not completed and the Read Data is not yet valid.

### bit 1 SCAN: MII Management Scanning bit When '1' is returned - indicates a scan operation (continuous MII Management Read cycles) is in progress.

### bit 0 MIIMBUSY: MII Management Busy bit

When '1' is returned - indicates MII Management module is currently performing an MII Management Read or Write cycle.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   | —                 | —                 | —                 |                  | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | -                 |                   | —                 | —                 |                   |                  | —                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | —                 | —                 | SIDL              | —                 | —                 | —                 |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7:0          | —                 | —                 | —                 | —                 |                   | —                 | C2OUT            | C1OUT            |

### REGISTER 26-2: CMSTAT: COMPARATOR STATUS REGISTER

| -   | -    |  |

|-----|------|--|

|     | ond  |  |

| Leu | ena: |  |

|     |      |  |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Control bit

- 1 = All Comparator modules are disabled while in Idle mode

- 0 = All Comparator modules continue to operate while in Idle mode

### bit 12-2 Unimplemented: Read as '0'

- bit 1 **C2OUT:** Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

- bit 0 C1OUT: Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

### 28.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MX5XX/6XX/7XX family of devices. These devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

### 28.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the Peripheral Bus Clock (PBCLK) and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

### 28.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- **Posc Idle mode:** the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- **Sosc Idle mode:** the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

### 28.3 Power-Saving Operation

Peripherals and the CPU can be halted or disabled to further reduce power consumption.

### 28.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 28.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit, if enabled, remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

### TABLE 32-20: INTERNAL RC ACCURACY

| AC CHA                        | AC CHARACTERISTICS              |      | $\begin{array}{l} \mbox{Standard Operating Conditions: } 2.3V \ to \ 3.6V \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \le TA \le +85^\circ C \ for \ Industrial \\ & -40^\circ C \le TA \le +105^\circ C \ for \ V-Temp \end{array}$ |      |       |            |  |  |  |

|-------------------------------|---------------------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|--|

| Param.<br>No. Characteristics |                                 | Min. | Typical                                                                                                                                                                                                                                                                    | Max. | Units | Conditions |  |  |  |

| LPRC @                        | LPRC @ 31.25 kHz <sup>(1)</sup> |      |                                                                                                                                                                                                                                                                            |      |       |            |  |  |  |

| F21                           | LPRC                            | -15  | -15 — +15 % —                                                                                                                                                                                                                                                              |      |       |            |  |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

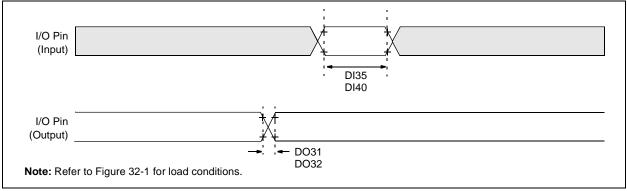

### FIGURE 32-3: I/O TIMING CHARACTERISTICS

### TABLE 32-21: I/O TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                              | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |      |                        |      |         |            |

|--------------------|--------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------------------------|------|---------|------------|

| Param.<br>No.      | Symbol | Characteris                  | stics <sup>(2)</sup>                                                                                                                                                                                                                                                             | Min. | Typical <sup>(1)</sup> | Max. | Units   | Conditions |

| DO31               | TIOR   | Port Output Rise Tin         | ne                                                                                                                                                                                                                                                                               | _    | 5                      | 15   | ns      | Vdd < 2.5V |

|                    |        |                              |                                                                                                                                                                                                                                                                                  | —    | 5                      | 10   | ns      | Vdd > 2.5V |

| DO32               | TIOF   | Port Output Fall Time        |                                                                                                                                                                                                                                                                                  | _    | 5                      | 15   | ns      | Vdd < 2.5V |

|                    |        |                              |                                                                                                                                                                                                                                                                                  | —    | 5                      | 10   | ns      | VDD > 2.5V |

| DI35               | TINP   | INTx Pin High or Low Time    |                                                                                                                                                                                                                                                                                  | 10   | _                      | _    | ns      | —          |

| DI40               | Trbp   | CNx High or Low Time (input) |                                                                                                                                                                                                                                                                                  | 2    | _                      | _    | TSYSCLK | _          |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

### TABLE 32-24: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS (U |           |                                |                                | (unless   | 0 1                                          | ; ≤ TA ≤ | +85°C | <b>6∨</b><br>for Industrial<br>C for V-Temp |                       |  |

|-----------------------|-----------|--------------------------------|--------------------------------|-----------|----------------------------------------------|----------|-------|---------------------------------------------|-----------------------|--|

| Param.<br>No.         | Symbol    | Characteristics <sup>(1)</sup> |                                |           | Min.                                         | Max.     | Units | Condit                                      | ions                  |  |

| TB10                  | ТтхН      | TxCK<br>High Time              | Synchronous, with prescaler    |           | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns            | —        | ns    | Must also meet<br>parameter<br>TB15         | value<br>(1, 2, 4, 8, |  |

| TB11                  | ΤτxL      | TxCK<br>Low Time               | Synchronous, with<br>prescaler |           | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns            |          | ns    | Must also meet<br>parameter<br>TB15         | 16, 32, 64,<br>256)   |  |

| TB15                  | ΤτχΡ      | TxCK<br>Input                  | Synchrono<br>prescaler         | ous, with | [(Greater of [(25 ns or<br>2 Трв)/N] + 30 ns | _        | ns    | VDD > 2.7V                                  |                       |  |

|                       |           | Period                         |                                |           | [(Greater of [(25 ns or<br>2 Трв)/N] + 50 ns | —        | ns    | VDD < 2.7V                                  |                       |  |

| TB20                  | TCKEXTMRL | Delay from<br>Clock Edge       |                                |           | _                                            | 1        | Трв   | _                                           |                       |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

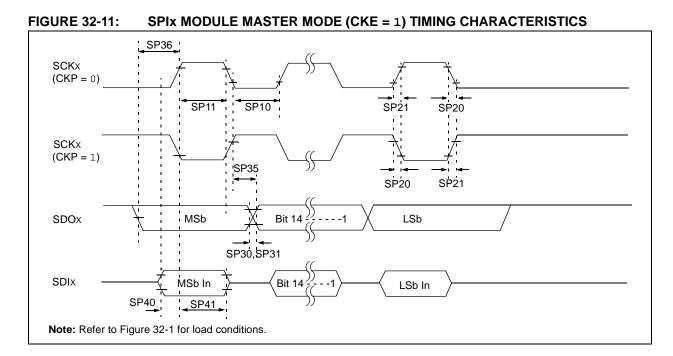

### TABLE 32-29: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                      |                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                     |      |       |                    |

|--------------------|----------------------|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>               | Min.                                                                                                                                                                                                                                                                              | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                 | SCKx Output Low Time <sup>(3)</sup>          | Tsck/2                                                                                                                                                                                                                                                                            | —                   | _    | ns    | —                  |

| SP11               | TscH                 | SCKx Output High Time <sup>(3)</sup>         | Tsck/2                                                                                                                                                                                                                                                                            | —                   | _    | ns    | —                  |

| SP20               | TscF                 | SCKx Output Fall Time <sup>(4)</sup>         | —                                                                                                                                                                                                                                                                                 | —                   | —    | ns    | See parameter DO32 |

| SP21               | TscR                 | SCKx Output Rise Time <sup>(4)</sup>         | _                                                                                                                                                                                                                                                                                 | —                   | _    | ns    | See parameter DO31 |

| SP30               | TDOF                 | SDOx Data Output Fall Time <sup>(4)</sup>    | _                                                                                                                                                                                                                                                                                 | —                   |      | ns    | See parameter DO32 |

| SP31               | TDOR                 | SDOx Data Output Rise Time <sup>(4)</sup>    | —                                                                                                                                                                                                                                                                                 | —                   | —    | ns    | See parameter DO31 |

| SP35               | TscH2doV,            | SDOx Data Output Valid after                 | _                                                                                                                                                                                                                                                                                 | —                   | 15   | ns    | VDD > 2.7V         |

|                    | TscL2doV             | SCKx Edge                                    | —                                                                                                                                                                                                                                                                                 | —                   | 20   | ns    | Vdd < 2.7V         |

| SP36               | TDOV2SC,<br>TDOV2SCL | SDOx Data Output Setup to<br>First SCKx Edge | 15                                                                                                                                                                                                                                                                                | —                   | _    | ns    | —                  |

| SP40               | TDIV2scH,            | Setup Time of SDIx Data Input to             | 15                                                                                                                                                                                                                                                                                | —                   |      | ns    | VDD > 2.7V         |

| TDIV2scL           |                      | SCKx Edge                                    | 20                                                                                                                                                                                                                                                                                | —                   | —    | ns    | Vdd < 2.7V         |

| SP41               | TscH2DIL,            | Hold Time of SDIx Data Input<br>to SCKx Edge | 15                                                                                                                                                                                                                                                                                | —                   |      | ns    | VDD > 2.7V         |

|                    | TscL2DIL             |                                              | 20                                                                                                                                                                                                                                                                                | —                   | _    | ns    | VDD < 2.7V         |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

### TABLE 32-37: 10-BIT ADC CONVERSION RATE PARAMETERS

| Standard Operating Conditions (see Note 3): 2.5V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |                |                             |               |              |                            |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------------------|---------------|--------------|----------------------------|--|--|--|