Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128lt-i-pf |

#### Referenced Sources

This device data sheet is based on the following individual chapters of the "PIC32 Family Reference Manual". These documents should be considered as the general reference for the operation of a particular module or device feature.

Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

TABLE 7-2: INTERRUPT REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H AND PIC32MX575F512H DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |          |       |             |        |         | Bits                 |      |      |      |      |            |      |        |                       |               |

|-----------------------------|---------------------------------|-----------|-------|-------|----------|-------|-------------|--------|---------|----------------------|------|------|------|------|------------|------|--------|-----------------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13    | 28/12 | 27/11       | 26/10  | 25/9    | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3       | 18/2 | 17/1   | 16/0                  | All<br>Resets |

| 10A0                        | IPC1                            | 31:16     | -     | _     | _        |       | INT1IP<2:0> |        | INT1IS  | <1:0>                | _    | _    | -    | С    | C1IP<2:0   | >    | OC1IS  | S<1:0>                | 0000          |

| TUAU                        | IPC1                            | 15:0      | 1     | _     | _        |       | IC1IP<2:0>  |        | IC1IS   | <1:0>                | _    | _    | 1    | •    | T1IP<2:0>  |      | T1IS   | <1:0>                 | 0000          |

| 10B0                        | IPC2                            | 31:16     | I     | _     | _        |       | INT2IP<2:0> |        | INT2IS  | <1:0>                | _    |      | I    | C    | C2IP<2:0>  | >    | OC215  | S<1:0>                | 0000          |

| ТОВО                        | IFC2                            | 15:0      | 1     | _     | _        |       | IC2IP<2:0>  |        | IC2IS   | <1:0>                | _    | _    | 1    | •    | T2IP<2:0>  |      | T2IS   | <1:0>                 | 0000          |

| 10C0                        | IPC3                            | 31:16     | 1     | _     | _        |       | INT3IP<2:0> |        | INT3IS  | <1:0>                | _    | _    | 1    | C    | C3IP<2:0>  | >    | OC3IS  | S<1:0>                | 0000          |

| 1000                        | 11 03                           | 15:0      | _     | _     | _        |       | IC3IP<2:0>  |        | IC3IS   | <1:0>                | _    | _    | _    | •    | T3IP<2:0>  |      | T3IS   | <1:0>                 | 0000          |

| 10D0                        | IPC4                            | 31:16     | _     | _     | _        |       | INT4IP<2:0> |        | INT4IS  | <1:0>                | _    | _    | _    |      | C4IP<2:0>  | >    | OC4IS  | S<1:0>                | 0000          |

| 1000                        | 11 04                           | 15:0      | _     | _     | _        |       | IC4IP<2:0>  |        | IC4IS<  | <1:0>                | _    | _    | _    | •    | T4IP<2:0>  |      | T4IS   | <1:0>                 | 0000          |

| 10E0                        | IPC5                            | 31:16     | _     | _     | _        | _     | _           | _      | _       | _                    | _    | _    | _    |      | C5IP<2:0>  | >    | OC5IS  | S<1:0>                | 0000          |

| 1020                        | 00                              | 15:0      | _     | _     | _        |       | IC5IP<2:0>  |        | IC5IS<  |                      | _    | _    | _    |      | T5IP<2:0>  |      | T5IS   |                       | 0000          |

|                             |                                 | 31:16     | _     | _     | _        |       | AD1IP<2:0>  |        | AD1IS   | <1:0>                | _    | _    | _    |      | CNIP<2:0>  |      |        | <1:0>                 | 0000          |

| 10F0                        | IPC6                            |           |       |       |          |       |             |        |         |                      |      |      |      | ·    | J1IP<2:0>  |      | U1IS   | <1:0>                 |               |

| 1010                        | 00                              | 15:0      | _     | _     | _        |       | I2C1IP<2:0> |        | I2C1IS  | <1:0>                | _    | _    | _    |      | PI3IP<2:0: |      | SPI3IS |                       | 0000          |

|                             |                                 |           |       |       |          |       |             |        |         |                      |      |      |      | 12   | 2C3IP<2:0> | >    | 12C3I3 | S<1:0>                |               |

|                             |                                 |           |       |       |          |       | U3IP<2:0>   |        | U3IS<   |                      |      |      |      |      |            |      |        |                       |               |

| 1100                        | IPC7                            | 31:16     | _     | _     | <u> </u> |       | SPI2IP<2:0> |        | SPI2IS  |                      | _    | _    | _    | Cf   | MP2IP<2:0  | >    | CMP2I  | S<1:0>                | 0000          |

|                             |                                 |           |       |       |          |       | I2C4IP<2:0> |        | I2C4IS  |                      |      |      |      |      |            |      |        |                       |               |

|                             |                                 | 15:0      | 1     | _     | _        |       | CMP1IP<2:0> |        | CMP1IS  |                      | _    | _    | I    |      | MPIP<2:0   |      | PMPIS  |                       | 0000          |

|                             |                                 | 31:16     | -     | _     | _        | F     | RTCCIP<2:0> | •      | RTCCIS  | S<1:0>               | _    | _    | -    |      | SCMIP<2:0  | >    |        | S<1:0>                | 0000          |

| 1110                        | IPC8                            |           |       |       |          |       |             |        |         |                      |      |      |      |      | J2IP<2:0>  |      | U2IS   |                       |               |

|                             | 00                              | 15:0      | _     | _     | _        | _     | _           | _      | _       | -                    | _    | _    | _    |      | PI4IP<2:0  |      |        | S<1:0>                | 0000          |

|                             |                                 |           |       |       |          |       |             |        |         |                      |      |      |      |      | 2C5IP<2:0> |      | 12C518 |                       |               |

| 1120                        | IPC9                            | 31:16     | _     | _     | _        |       | DMA3IP<2:0> |        | DMA3IS  |                      | _    | _    |      |      | MA2IP<2:0  |      |        | S<1:0>                | 0000          |

| 0                           | 00                              | 15:0      | _     | _     | _        |       | DMA1IP<2:0> |        | DMA1IS  |                      | _    | _    |      |      | MA0IP<2:0  |      | DMA0I  |                       | 0000          |

| 1130                        | IPC10                           | 31:16     | _     | _     | _        |       | MA7IP<2:0>( |        | DMA7IS- |                      | _    | _    | _    |      | A6IP<2:0>  |      | DMA6IS |                       | 0000          |

|                             | 0.0                             | 15:0      | 1     | _     | _        | D     | MA5IP<2:0>( | 2)<br> | DMA5IS- | <1:0> <sup>(2)</sup> | _    | _    | I    |      | A4IP<2:0>  |      |        | S<1:0> <sup>(2)</sup> | 0000          |

| 1140                        | IPC11                           | 31:16     |       | _     | _        | _     | _           | _      | _       | _                    | _    | _    | _    |      | AN1IP<2:0  |      | CAN1I  |                       | 0000          |

|                             |                                 | 15:0      | _     | _     |          |       | USBIP<2:0>  |        | USBIS   |                      | _    | _    | _    |      | CEIP<2:0>  | >    | FCEIS  |                       | 0000          |

| 1150                        | IPC12                           | 31:16     | _     | _     | _        |       | U5IP<2:0>   |        | U5IS<   |                      | _    | _    | _    |      | J6IP<2:0>  |      | U6IS   | <1:0>                 | 0000          |

| 1100                        | 0.2                             | 15:0      | _     | _     | _        |       | U4IP<2:0>   |        | U4IS<   | :1:0>                | _    | _    | _    | _    | _          | _    | _      | _                     | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

<sup>2:</sup> These bits are not available on PIC32MX534/564/664/764 devices.

<sup>3:</sup> This register does not have associated CLR, SET, and INV registers.

### 8.1 Control Registers

#### TABLE 8-1: OSCILLATOR REGISTER MAP

| ess                         |                                 | ø        |       |       |           |            |              |       |           | В    | its     |         |       |       |        |        |            |       | (2)        |

|-----------------------------|---------------------------------|----------|-------|-------|-----------|------------|--------------|-------|-----------|------|---------|---------|-------|-------|--------|--------|------------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Rang | 31/15 | 30/14 | 29/13     | 28/12      | 27/11        | 26/10 | 25/9      | 24/8 | 23/7    | 22/6    | 21/5  | 20/4  | 19/3   | 18/2   | 17/1       | 16/0  | All Resets |

| E000                        | OSCCON                          | 31:16    | _     | _     | Р         | LLODIV<2:0 | <b> &gt;</b> | F     | RCDIV<2:0 | >    | _       | SOSCRDY | _     | PBDIV | /<1:0> | Р      | LLMULT<2:0 | )>    | 0000       |

| F000                        | OSCCON                          | 15:0     | -     |       | COSC<2:0> |            | -            |       | NOSC<2:0> |      | CLKLOCK | ULOCK   | SLOCK | SLPEN | CF     | UFRCEN | SOSCEN     | OSWEN | 0000       |

| F010                        | OSCTUN                          | 31:16    | _     | _     | _         | _          |              | _     | _         | _    | _       | _       |       | _     | ı      | _      | _          | _     | 0000       |

| F010                        | OSCION                          | 15:0     | _     | _     | _         |            | TUN<5:0>     |       |           |      |         | 0000    |       |       |        |        |            |       |            |

PIC32MX5XX/6XX/7XX

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | DCSZ             | <b>′</b> <1:0>   |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | _                 | _                 | PREFEN<1:0>       |                   | _                 | PFMWS<2:0>        |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-17 Unimplemented: Write '0'; ignore read

bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

1 = Invalidate all data and instruction lines

0 = Invalidate all data lnes and instruction lines that are not locked

bit 15-10 Unimplemented: Write '0'; ignore read

bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

Changing these bits causes all lines to be reinitialized to the "invalid" state.

11 = Enable data caching with a size of 4 lines

10 = Enable data caching with a size of 2 lines

01 = Enable data caching with a size of 1 line

00 = Disable data caching

bit 7-6 Unimplemented: Write '0'; ignore read

bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

11 = Enable predictive prefetch for both cacheable and non-cacheable regions

10 = Enable predictive prefetch only for non-cacheable regions

01 = Enable predictive prefetch only for cacheable regions

00 = Disable predictive prefetch

bit 3 Unimplemented: Write '0'; ignore read

bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

111 = Seven Wait states

110 = Six Wait states

101 = Five Wait states

100 = Four Wait states

011 = Three Wait states

010 = Two Wait states

001 = One Wait state

000 = Zero Wait state

#### **REGISTER 9-3: CHETAG: CACHE TAG REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | LTAGBOOT          | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15.6         | 15:8 LTAG<11:4>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |  |  |

| 7.0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | _                |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 LTAGBOOT: Line Tag Address Boot bit

1 = The line is in the 0x1D000000 (physical) area of memory

0 = The line is in the 0x1FC00000 (physical) area of memory

bit 30-24 Unimplemented: Write '0'; ignore read

bit 23-4 LTAG<19:0>: Line Tag Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

bit 3 LVALID: Line Valid bit

1 = The line is valid and is compared to the physical address for hit detection

0 = The line is not valid and is not compared to the physical address for hit detection

bit 2 LLOCK: Line Lock bit

1 = The line is locked and will not be replaced

0 = The line is not locked and can be replaced

bit 1 LTYPE: Line Type bit

1 = The line caches instruction words

0 = The line caches data words

bit 0 Unimplemented: Write '0'; ignore read

#### REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER (CONTINUED)

- bit 7 **GCEN:** General Call Enable bit (when operating as I<sup>2</sup>C slave)

- 1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)

- 0 = General call address is disabled

- bit 6 **STREN:** SCLx Clock Stretch Enable bit (when operating as I<sup>2</sup>C slave)

Used in conjunction with SCLREL bit.

- 1 = Enable software or receive clock stretching

- 0 = Disable software or receive clock stretching

- bit 5 **ACKDT:** Acknowledge Data bit (when operating as I<sup>2</sup>C master, applicable during master receive)

Value that is transmitted when the software initiates an acknowledge sequence.

- 1 = Send NACK during an acknowledge

- 0 = Send ACK during an acknowledge

- bit 4 ACKEN: Acknowledge Sequence Enable bit (when operating as I<sup>2</sup>C master, applicable during master receive)

- 1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit. Hardware clear at end of master Acknowledge sequence.

- 0 = Acknowledge sequence not in progress

- bit 3 **RCEN:** Receive Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Enables Receive mode for  $1^2$ C. Hardware clear at end of eighth bit of master receive data byte.

- 0 = Receive sequence is not in progress

- bit 2 **PEN:** Stop Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.

- 0 = Stop condition is not in progress

- bit 1 **RSEN:** Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.

- 0 = Repeated Start condition is not in progress

- bit 0 **SEN:** Start Condition Enable bit (when operating as I<sup>2</sup>C master)

- 1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.

- 0 = Start condition is not in progress

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

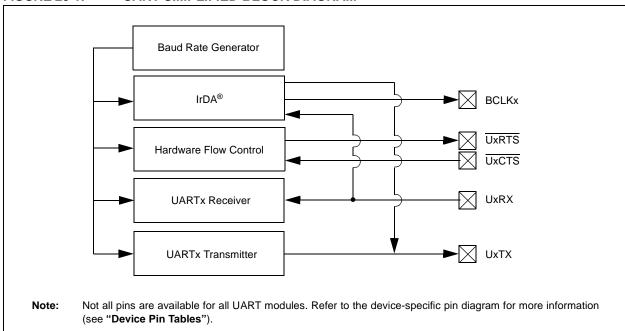

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21.** "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The UART module is one of the serial I/O modules available in the PIC32MX5XX/6XX/7XX family of devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN 1.2 and IrDA®. The module also supports the hardware flow control option, with  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins, and also includes an IrDA encoder and decoder.

The following are primary features of the UART module:

- · Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- · Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 20 Mbps at 80 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- · Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (ninth bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN 2.1 Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 20-1 illustrates a simplified block diagram of the UART module.

FIGURE 20-1: UART SIMPLIFIED BLOCK DIAGRAM

#### REGISTER 20-2: UXSTA: UARTX STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

- 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

- bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit

- 11 = Reserved

- 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters)

- 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters)

- 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect.

- 0 = Address Detect mode is disabled

- bit 4 **RIDLE:** Receiver Idle bit (read-only)

- 1 = Receiver is idle

- 0 = Data is being received

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character

- 0 = Parity error has not been detected

- bit 2 **FERR:** Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character

- 0 = Framing error has not been detected

- bit 1 OERR: Receive Buffer Overrun Error Status bit.

This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

#### REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER (CONTINUED)

bit 13 SIDLE: CAN Stop in Idle bit

1 = CAN Stops operation when system enters Idle mode

0 = CAN continues operation when system enters Idle mode

bit 12 Unimplemented: Read as '0'

bit 11 CANBUSY: CAN Module is Busy bit

1 = The CAN module is active

0 = The CAN module is completely disabled

bit 10-5 Unimplemented: Read as '0'

bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID) 10010 = Compare up to data byte 2 bit 6 with EID17 (CiRXFn<17>)

•

•

•

00001 = Compare up to data byte 0 bit 7 with EID0 (CiRXFn<0>)

00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

#### REGISTER 24-2: CICFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = Length is 8 x TQ

000 = Length is 1 x TQ

bit 7-6 SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

11 = Length is 4 x TQ

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = Length is 1 x TQ

bit 5-0 BRP<5:0>: Baud Rate Prescaler bits

111111 = TQ = (2 x 64)/Fsys

111110 = TQ = (2 x 63)/Fsys

000001 = TQ = (2 x 2)/Fsys

000000 = TQ = (2 x 1)/Fsys

```

- Note 1: SEG2PH ≤ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

- 2: 3 Time bit sampling is not allowed for BRP < 2.

- 3:  $SJW \leq SEG2PH$ .

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

#### REGISTER 24-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN27           | MSEL2             | 27<1:0>           | FSEL27<4:0>       |                   |                   |                  |                  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | FLTEN26           | MSEL2             | 26<1:0>           |                   |                   | FSEL26<4:0>       |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | FLTEN25           | MSEL25<1:0>       |                   | FSEL25<4:0>       |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN24           | MSEL24<1:0>       |                   | FSEL24<4:0>       |                   |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN27: Filter 27 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 30-29 MSEL27<1:0>: Filter 27 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL27<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN26: Filter 26 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 22-21 MSEL26<1:0>: Filter 26 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 20-16 FSEL26<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 25-3: ETHTXST: ETHERNET CONTROLLER TX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | TXSTADDR<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | TXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         | TXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |  |

| 7.0          |                   |                   | TXSTADE           | DR<7:2>           |                   |                   | _                | _                |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-2 TXSTADDR<31:2>: Starting Address of First Transmit Descriptor bits

This register should not be written while any transmit, receive or DMA operations are in progress.

This address must be 4-byte aligned (bits 1-0 must be '00').

bit 1-0 Unimplemented: Read as '0'

Note 1: This register is only used for TX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

# REGISTER 25-4: ETHRXST: ETHERNET CONTROLLER RX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | RXSTADDR<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23.10        | RXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         | RXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |  |  |  |

| 7.0          |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-2 RXSTADDR<31:2>: Starting Address of First Receive Descriptor bits

This register should not be written while any transmit, receive or DMA operations are in progress.

This address must be 4-byte aligned (bits 1-0 must be '00').

bit 1-0 Unimplemented: Read as '0'

**Note 1:** This register is only used for RX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

#### REGISTER 26-2: CMSTAT: COMPARATOR STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                 | _                 | 1                 | -                 | 1                | _                |

| 22,46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 |                   | _                 | _                |                  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | SIDL              | _                 |                   | _                 | _                |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 | _                 | _                 | _                 | C2OUT            | C1OUT            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR 1' = Bit is set 0' = Bit is cleared 0' = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = All Comparator modules are disabled while in Idle mode

0 = All Comparator modules continue to operate while in Idle mode

bit 12-2 **Unimplemented:** Read as '0'

bit 1 **C2OUT:** Comparator Output bit

1 = Output of Comparator 2 is a '1'

0 = Output of Comparator 2 is a '0'

bit 0 C10UT: Comparator Output bit

1 = Output of Comparator 1 is a '1'

0 = Output of Comparator 1 is a '0'

#### REGISTER 29-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | R/P              |

| 31:24        |                   | _                 | _                 | СР                | _                 | _                 | _                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P               | R/P              | R/P              |

| 23:16        |                   |                   | _                 | _                 |                   |                   |                  |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | r-1               | r-1              | r-1              |

| 15:8         |                   | PWP<              | :3:0>             |                   | _                 | _                 | _                | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | R/P               | r-1               | R/P              | R/P              |

| 7:0          |                   | _                 | 1                 | 1                 | ICESEL            | 1                 | DEBU             | G<1:0>           |

| Legend:           | r = Reserved bit | P = Programmable bit     |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

bit 19-12 PWP<7:0>: Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the 1's complement of the number of write-protected program Flash memory pages.

represent the 1's complemen 11111111 = Disabled 11111110 = 0xBD00\_0FFF 11111101 = 0xBD00\_1FFF 11111101 = 0xBD00\_2FFF 11111011 = 0xBD00\_3FFF 11111010 = 0xBD00\_4FFF

11111010 = 0xBD00\_4FF 11111001 = 0xBD00\_5FF 11111000 = 0xBD00\_6FF

11110111 = 0xBD00\_7FFF

11110110 = 0xBD00\_8FFF 11110101 = 0xBD00\_9FFF

11110100 = 0xBD00\_AFFF

11110011 = 0xBD00\_BFFF 11110010 = 0xBD00\_CFFF

11110001 = 0xBD00\_DFFF

11110000 = 0xBD00\_EFFF 11101111 = 0xBD00\_FFFF

• TTT0TTTT = 0XBD00\_FFF

•

$011111111 = 0xBD07_FFFF$

bit 11-4 Reserved: Write '1'

TABLE 32-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

|                |        |                                                                                                                | Standard<br>(unless | -    | _    |         | s: 2.3V to 3.6V                                         |

|----------------|--------|----------------------------------------------------------------------------------------------------------------|---------------------|------|------|---------|---------------------------------------------------------|

| DC CHA         | RACTER | ISTICS                                                                                                         | Operatin            |      |      | -40°C ≤ | ≤ TA ≤ +85°C for Industrial<br>≤ TA ≤ +105°C for V-temp |

| Param.         | Symbol | Characteristic                                                                                                 | Min.                | Тур. | Max. | Units   | Conditions                                              |

| DO10           | Vol    | Output Low Voltage I/O Pins: 4x Sink Driver Pins - All I/O output pins not defined as 8x Sink Driver pins      | _                   | _    | 0.4  | V       | $IOL \le 10 \text{ mA}, VDD = 3.3V$                     |

|                |        | Output Low Voltage I/O Pins: 8x Sink Driver Pins - RC15                                                        | _                   | _    | 0.4  | V       | $IOL \le 15 \text{ mA}, VDD = 3.3V$                     |

| DO20           | Vон    | Output High Voltage I/O Pins: 4x Source Driver Pins - All I/O output pins not defined as 8x Source Driver pins | 2.4                 | _    | _    | V       | IOH ≥ -10 mA, VDD = 3.3V                                |

|                |        | Output High Voltage I/O Pins: 8x Source Driver Pins - RC15                                                     | 2.4                 | _    | _    | V       | IOH ≥ -15 mA, VDD = 3.3V                                |

|                |        | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>  | _    | _    |         | IOH ≥ -14 mA, VDD = 3.3V                                |

|                |        | 4x Source Driver Pins - All I/O                                                                                | 2.0 <sup>(1)</sup>  | _    | _    | V       | IOH ≥ -12 mA, VDD = 3.3V                                |

| DO20A          | Vou1   | output pins not defined as 8x Sink Driver pins                                                                 | 3.0 <sup>(1)</sup>  | _    | _    |         | IOH ≥ -7 mA, VDD = 3.3V                                 |

| DOZUA          | VOHT   | Output High Voltage I/O Pins:                                                                                  | 1.5 <sup>(1)</sup>  | _    | _    |         | IOH ≥ -22 mA, VDD = 3.3V                                |

|                |        | 8x Source Driver Pins - RC15                                                                                   | 2.0 <sup>(1)</sup>  |      | _    | V       | IOH ≥ -18 mA, VDD = 3.3V                                |

| Note 1: Paramo |        | tors are characterized, but not too                                                                            | 3.0 <sup>(1)</sup>  | _    |      |         | IOH ≥ -10 mA, VDD = 3.3V                                |

**Note 1:** Parameters are characterized, but not tested.

#### TABLE 32-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        |                                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +105^{\circ}\text{C}$ for V-Temp |         |      |       |            |  |

|--------------------|--------|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                           | Min. <sup>(1)</sup>                                                                                                                                                                                                                            | Typical | Max. | Units | Conditions |  |

| BO10               | VBOR   | BOR Event on VDD transition high-to-low ( <b>Note 2</b> ) | 2.0                                                                                                                                                                                                                                            | _       | 2.3  | V     | _          |  |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN.

<sup>2:</sup> This driver pin only applies to devices with less than 64 pins.

<sup>3:</sup> This driver pin only applies to devices with 64 pins.

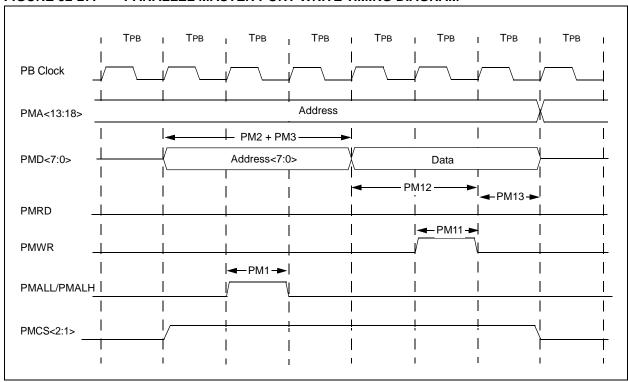

FIGURE 32-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

**TABLE 32-41: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS**

| AC CHARACTERISTICS |         |                                                                     | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{Ta} \le +105^{\circ}\text{C}$ for V-Temp |         |      |       |            |  |

|--------------------|---------|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                      | Min.                                                                                                                                                                                                                                           | Typical | Max. | Units | Conditions |  |

| PM11               | Twr     | PMWR Pulse Width                                                    | _                                                                                                                                                                                                                                              | 1 Трв   | _    | _     | _          |  |

| PM12               | TDVSU   | Data Out Valid before PMWR or PMENB goes Inactive (data setup time) | _                                                                                                                                                                                                                                              | 2 TPB   | _    | _     | _          |  |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)       | _                                                                                                                                                                                                                                              | 1 Трв   |      | _     | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

### TABLE B-3: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                     | Update Description                                                                                    |

|----------------------------------|-------------------------------------------------------------------------------------------------------|

| 1.0 "Electrical Characteristics" | Updated the Typical and Maximum DC Characteristics: Operating Current (IDD) in Table 1-5.             |

|                                  | Updated the Typical and Maximum DC Characteristics: Idle Current (IIDLE) in Table 1-6.                |

|                                  | Updated the Typical and Maximum DC Characteristics: Power-Down Current (IPD) in Table 1-7.            |

|                                  | Added DC Characteristics: Program Memory parameters D130a and D132a in Table 1-11.                    |

|                                  | Added the Internal Voltage Reference parameter (D305) to the Comparator Specifications in Table 1-13. |

| Oscillator Configuration95                         | CiFLTCON4 (CAN Filter Control 4)                    |

|----------------------------------------------------|-----------------------------------------------------|

| Output Compare185                                  | CiFLTCON5 (CAN Filter Control 5)                    |

| P                                                  | CiFLTCON6 (CAN Filter Control 6)                    |

|                                                    | CIFLTCON7 (CAN Filter Control 7)                    |

| Packaging                                          | CIFSTAT (CAN FIFO Status)                           |

| Details                                            | CiINT (CAN Interrupt)                               |

|                                                    | CiRXFn (CAN Acceptance Filter 'n')                  |

| Parallel Master Port (PMP)                         | CiRXMn (CAN Acceptance Filter Mask 'n')             |

| PIC32 Family USB Interface Diagram                 | CiRXOVF (CAN Receive FIFO Overflow Status) 254      |

| PICkit 3 In-Circuit Debugger/Programmer            | CiTMR (CAN Timer)254                                |

| Pinout I/O Descriptions (table)                    | CiTREC (CAN Transmit/Receive Error Count) 253       |

| Power-on Reset (POR)                               | CiVEC (CAN Interrupt Code)252                       |

| and On-Chip Voltage Regulator343                   | CMSTAT (Comparator Control Register)326             |

| Power-Saving Features331                           | CMxCON (Comparator 'x' Control)325                  |

| CPU Halted Methods331                              | CNCON (Change Notice Control)166                    |

| Operation331                                       | CVRCON (Comparator Voltage Reference Control) 329   |

| with CPU Running331                                | DCHxCON (DMA Channel 'x' Control) 124               |

| Prefetch Cache101                                  | DCHxCPTR (DMA Channel 'x' Cell Pointer) 131         |

| Program Flash Memory                               | DCHxCSIZ (DMA Channel 'x' Cell-Size) 131            |

| Wait State Characteristics363                      | DCHxDAT (DMA Channel 'x' Pattern Data) 132          |

| R                                                  | DCHxDPTR (Channel 'x' Destination Pointer) 130      |

|                                                    | DCHxDSA (DMA Channel 'x' Destination                |

| Real-Time Clock and Calendar (RTCC)221             | Start Address)                                      |

| Register Maps55–283                                | DCHxDSIZ (DMA Channel 'x' Destination Size) 129     |

| Registers                                          | DCHxECON (DMA Channel 'x' Event Control) 125        |

| AD1CHS (ADC Input Select)239                       | DCHxINT (DMA Channel 'x' Interrupt Control) 126     |

| AD1CON1 (ADC Control 1)235                         | DCHxSPTR (DMA Channel 'x' Source Pointer) 130       |

| AD1CON2 (ADC Control 2)237                         | DCHxSSA (DMA Channel 'x' Source Start Address) 128  |

| AD1CON3 (ADC Control 3)238                         | DCHxSSIZ (DMA Channel 'x' Source Size)129           |

| AD1CSSL (ADC Input Scan Select)240                 | DCRCCON (DMA CRC Control)121                        |

| ALRMDATE (Alarm Date Value)230                     | DCRCDATA (DMA CRC Data)123                          |

| ALRMTIME (Alarm Time Value)229                     | DCRCXOR (DMA CRCXOR Enable)                         |

| BMXBOOTSZ (Boot Flash (IFM) Size)61                | DDPCON (Debug Data Port Control)                    |

| BMXCON (Bus Matrix Configuration)56                | DEVCFG0 (Device Configuration Word 0                |

| BMXDKPBA (Data RAM Kernel Program                  | DEVCFG1 (Device Configuration Word 1                |

| Base Address)57                                    | DEVCFG2 (Device Configuration Word 2                |

| BMXDRMSZ (Data RAM Size)60                         | DEVCFG2 (Device Configuration Word 2                |

| BMXDUDBA (Data RAM User Data Base Address) 58      | DEVID (Device and Revision ID)                      |

| BMXDUPBA (Data RAM User Program                    | ,                                                   |

| Base Address)59                                    | DMAADDR (DMA Address)                               |

| BMXPFMSZ (Program Flash (PFM) Size)61              | DMACON (DMA Controller Control)                     |

| BMXPUPBA (Program Flash (PFM) User Program         | DMASTAT (DMA Status)                                |

| Base Address)60                                    | EMAC1CFG1 (Ethernet Controller MAC Configuration 1) |

| CHEACC (Cache Access)104                           | 306                                                 |

| CHECON (Cache Control)103                          | EMAC1CFG2 (Ethernet Controller MAC Configuration 2) |

| CHEHIT (Cache Hit Statistics)109                   | 307                                                 |

| · · · · · · · · · · · · · · · · · · ·              | EMAC1CLRT (Ethernet Controller MAC Collision Win-   |

| CHELRU (Cache LRU)                                 | dow/Retry Limit)311                                 |

| CHEMIS (Cache Miss Statistics)                     | EMAC1IPGR (Ethernet Controller MAC Non-Back-to-     |

| CHEMSK (Cache TAG Mask)106                         | Back Interpacket Gap)310                            |

| CHETAG (Cache TAG)                                 | EMAC1IPGT (Ethernet Controller MAC Back-to-Back In- |

| CHEW0 (Cache Word 0)106                            | terpacket Gap)309                                   |

| CHEW1 (Cache Word 1)107                            | EMAC1MADR (Ethernet Controller MAC MII Manage-      |

| CHEW2 (Cache Word 2)107                            | ment Address) 317                                   |

| CHEW3 (Cache Word 3)108                            | EMAC1MAXF (Ethernet Controller MAC Maximum          |

| CiCFG (CAN Baud Rate Configuration)248             | Frame Length)312                                    |

| CiCON (CAN Module Control)246                      | EMAC1MCFG (Ethernet Controller MAC MII Manage-      |

| CiFIFOBA (CAN Message Buffer Base Address) 273     | ment Configuration) 315                             |

| CiFIFOCINn (CAN Module Message Index Register 'n') | EMAC1MCMD (Ethernet Controller MAC MII Manage-      |

| 278                                                | ment Command)316                                    |

| CiFIFOCONn (CAN FIFO Control Register 'n')274      | EMAC1MIND (Ethernet Controller MAC MII Manage-      |

| CiFIFOINTn (CAN FIFO Interrupt Register 'n')276    | ment Indicators)319                                 |

| CiFIFOUAn (CAN FIFO User Address Register 'n') 278 | EMAC1MRDD (Ethernet Controller MAC MII Manage-      |

| CiFLTCON0 (CAN Filter Control 0)256                | ment Read Data)                                     |

| CiFLTCON1 (CAN Filter Control 1)258                | EMAC1MWTD (Ethernet Controller MAC MII Manage-      |

| CiFLTCON2 (CAN Filter Control 2)260                | ment Write Data)                                    |

| CiELTCON3 (CAN Filter Control 3) 262               |                                                     |

#### THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

#### CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- · Distributor or Representative

- · Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support

#### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PIC32 MX 5XX F 512 H T - 80 I      | <u>PT</u> - <u>XXX</u> |

|------------------------------------|------------------------|

| Microchip Brand                    |                        |

| Architecture                       |                        |

| Product Groups                     |                        |

| Flash Memory Family                |                        |

| Program Memory Size (KB)           |                        |

| Pin Count                          |                        |

| Tape and Reel Flag (if applicable) |                        |

| Speed (see Note 1)                 |                        |

| Temperature Range                  |                        |

| Package                            | _                      |

| Pattern                            |                        |

#### Example:

PIC32MX575F256H-80I/PT: General purpose PIC32, 32-bit RISC MCU, 256 KB program memory, 64-pin, Industrial temperature, TQFP package.

#### Flash Memory Family

Architecture MX = 32-bit RISC MCU core

Product Groups 5XX = General purpose microcontroller family

6XX = General purpose microcontroller family

7XX = General purpose microcontroller family

Flash Memory Family F = Flash program memory

Program Memory Size 64 = 64K

128 = 128K 256 = 256K512 = 512K

Pin Count H = 64-pin

= 100-pin, 121-pin, 124-pin

Speed (see Note 1) Blank or 80 = 80 MHz

= -40°C to +85°C (Industrial) Temperature Range

= -40°C to +105°C (V-Temp)

PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack) Package

PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)

PF = 100-Lead (14x14x1 mm) TQFP (Thin Quad Flatpack) MR = 64-Lead (9x9x0.9 mm) QFN (Plastic Quad Flat)

BG = 121-Lead (10x10x1.1 mm) TFBGA (Plastic Thin Profile Ball Grid Array)

TL = 124-Lead (9x9x0.9 mm) VTLA (Very Thin Leadless Array)

Pattern Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)

ES = Engineering Sample

This option is not available for PIC32MX534/564/664/764 devices. Note