Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128lt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | USB, Ethernet, and CAN |                         |                  |     |          |        |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------------------------|-------------------------|------------------|-----|----------|--------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins                   | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | CAN    | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dMd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX764F128H  | 64                     | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F256H  | 64                     | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F512H  | 64                     | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX795F512H  | 64                     | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX764F128L  | 100                    | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/6                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F256L  | 100                    | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F512L  | 100                    | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX795F512L  | 100                    | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFF                   | P MR = C                | QFN              |     | BG       | G = TF | BGA                    |                                          | TL = \                | /TLA               | 5)                              |                              |             |         |      |       |                         |

#### TABLE 3: PIC32MX7XX USB, ETHERNET, AND CAN FEATURES

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to Section 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

PIC32MX795F512L

#### **TABLE 12:** PIN NAMES FOR USB, ETHERNET, AND CAN DEVICES

| 121-PIN TFBGA (BOTTOM VIEW)                           |    | L11 |

|-------------------------------------------------------|----|-----|

| PIC32MX764F128L<br>PIC32MX775F256L<br>PIC32MX775F512L | L1 | A11 |

A1

Note: The TFBGA package skips from row "H" to row "J" and has no "I" row.

| Pin #      | Full Pin Name                                               | Pin # | Full Pin Name                                                |

|------------|-------------------------------------------------------------|-------|--------------------------------------------------------------|

| A1         | PMD4/RE4                                                    | E2    | T4CK/AC2RX <sup>(1)</sup> /RC3                               |

| A2         | PMD3/RE3                                                    | E3    | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                   | E4    | T3CK/AC2TX <sup>(1)</sup> /RC2                               |

| A4         | PMD0/RE0                                                    | E5    | Vdd                                                          |

| A5         | C2RX <sup>(1)</sup> /PMD8/RG0                               | E6    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1                         |

| A6         | C1TX/ETXD0/PMD10/RF1                                        | E7    | Vss                                                          |

| A7         | VDD                                                         | E8    | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                         | E9    | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                        | E10   | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                     | E11   | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                     | F1    | MCLR                                                         |

| B1         | No Connect (NC)                                             | F2    | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8     |

| B2         | AERXERR/RG15                                                | F3    | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                    | F4    | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                    | F5    | Vss                                                          |

| B5         | TRD3/RA7                                                    | F6    | No Connect (NC)                                              |

| B6         | C1RX/ETXD1/PMD11/RF0                                        | F7    | No Connect (NC)                                              |

| B7         | VCAP                                                        | F8    | Vdd                                                          |

| B8         | PMRD/CN14/RD5                                               | F9    | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                     | F10   | Vss                                                          |

| B10        | Vss                                                         | F11   | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                         | G1    | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                    | G2    | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                         | G3    | TMS/RA0                                                      |

| C3         | TRD1/RG12                                                   | G4    | No Connect (NC)                                              |

| C4         | TRD2/RG14                                                   | G5    | Vdd                                                          |

| C5         | TRCLK/RA6                                                   | G6    | Vss                                                          |

| C6         | No Connect (NC)                                             | G7    | Vss                                                          |

| C7         | ETXCLK/PMD15/CN16/RD7                                       | G8    | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                           | G9    | TDO/RA5                                                      |

| C9         | VDD                                                         | G10   | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                              | G11   | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                             | H1    | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                    | H2    | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                    | H3    | Vss                                                          |

| D3         | PMD5/RE5                                                    | H4    | VDD                                                          |

| D4         | Vss                                                         | H5    | No Connect (NC)                                              |

| D5         | Vss                                                         | H6    | VDD                                                          |

| D6         |                                                             | H7    | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                        | H8    | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                       | H9    | VUSB3V3                                                      |

| D9         | SD01/0C1/INT0/RD0                                           | H10   | D+/RG2                                                       |

| D10        | No Connect (NC)<br>SCK1/IC3/PMCS2/PMA15/RD10                | H11   | SCL2/RA2<br>AN3/C2IN+/CN5/RB3                                |

| D11        |                                                             | J1    |                                                              |

| E1<br>Note | T5CK/SDI1/RC4<br>1: This pin is not available on PIC32MX764 | J2    | AN2/C2IN-/CN4/RB2                                            |

2: Shaded pins are 5V tolerant.

#### 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

**Note:** This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

#### 2.1 Basic Connection Requirements

Getting started with the PIC32MX5XX/6XX/7XX family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pin may be required, as well: VREF+/ VREF- pins used when external voltage reference for ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of the ADC use and the ADC voltage reference source.

#### 2.2 Decoupling Capacitors

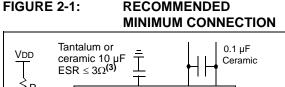

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended to use ceramic capacitors.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- Maximizing performance: On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum, thereby reducing PCB track inductance.

### Note 1: If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than  $3\Omega$  and the inductor capacity greater than 10 mA.

Where:

$$f = \frac{F_{CNV}}{2}$$

(i.e., ADC conversion rate/2)

$$f = \frac{1}{(2\pi\sqrt{LC})}$$

$$L = \left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

3: Aluminum or electrolytic capacitors should not be used. ESR  $\leq 3\Omega$  from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

#### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

### 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (1 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 32.0 "Electrical Characteristics"** for additional information on CEFC specifications.

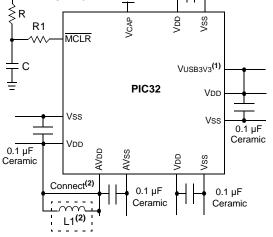

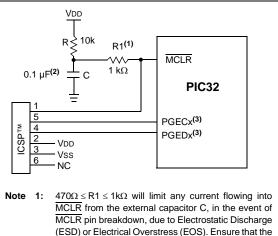

#### 2.4 Master Clear (MCLR) Pin

The MCLR pin provides two specific device functions:

- Device Reset

- Device Programming and Debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

#### FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

MCLR from the external capacitor C, in the event of MCLR pin breakdown, due to Electrostatic Discharge (ESD) or Electrical Overstress (EOS). Ensure that the MCLR pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.

- 2: The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- **3:** No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

#### 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

#### 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

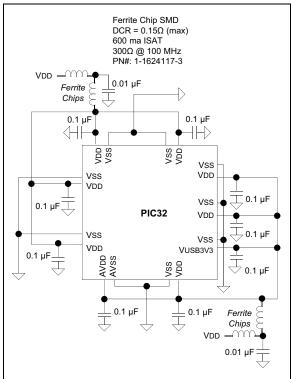

#### 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

#### FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

### 9.0 PREFETCH CACHE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS60001119) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

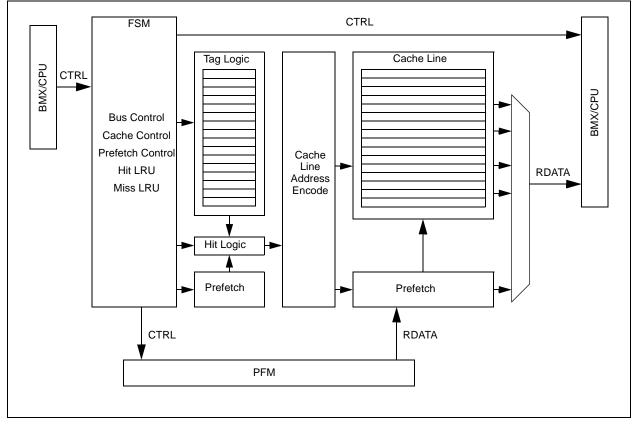

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

#### 9.1 Features

- 16 fully-associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- Pseudo-LRU replacement policy

- All cache lines are software writable

- 16-byte parallel memory fetch

- Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

#### FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

#### **Control Registers** 10.1

#### TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                       | â         |                                                                                      |       |       |         |         |       |      | Bi   | its  |      |      |      |      |      |           |      | ő          |

|-----------------------------|-----------------------|-----------|--------------------------------------------------------------------------------------|-------|-------|---------|---------|-------|------|------|------|------|------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) |                       | Bit Range | 31/15                                                                                | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 0000                        | DMACON <sup>(1)</sup> | 31:16     | _                                                                                    | _     | -     | _       | _       |       | _    | _    | _    | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 3000                        | DMACON                | 15:0      | ON                                                                                   | _     | _     | SUSPEND | DMABUSY | _     | _    | _    | _    | _    | _    | _    | _    | _    | _         | _    | 0000       |

| 2010                        | DMASTAT               | 31:16     | _                                                                                    | _     | _     | _       | —       | _     | _    | _    | _    | -    | _    | _    | —    | _    | _         | _    | 0000       |

| 3010                        | DIVIASTAT             | 15:0      | _                                                                                    | —     |       | —       | —       | —     |      |      |      | —    | _    | _    | RDWR | D    | MACH<2:0> | (2)  | 0000       |

| 2020                        | DMAADDR               | 31:16     |                                                                                      |       |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

| 3020                        | DIVIAADDR             | 15:0      | DMAADDR<31:0>                                                                        |       |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

| Legen                       | <b>d</b> .            | nknown    | value on Reset: — = unimplemented read as '0'. Reset values are shown in hexadecimal |       |       |         |         |       |      |      |      |      |      |      |      |      |           |      |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

DMACH<3> bit is not available on PIC32MX534/564/664/764 devices. 2:

#### TABLE 10-2: DMA CRC REGISTER MAP<sup>(1)</sup>

| ess                         |                                 | 0         |       |               |       |       |                 |           |      | В      | ts       |        |        |      |      |      |           |      | ú          |

|-----------------------------|---------------------------------|-----------|-------|---------------|-------|-------|-----------------|-----------|------|--------|----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11           | 26/10     | 25/9 | 24/8   | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16     | _     | _             | BYTO  | <1:0> | .0> WBO BITO 00 |           |      |        |          |        |        |      |      |      | 0000      |      |            |

| 3030                        | DURCUUN                         | 15:0      | —     | —             | —     |       |                 | PLEN<4:0> |      |        | CRCEN    | CRCAPP | CRCTYP | _    | —    | (    | CRCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA                        | 31:16     |       |               |       |       |                 |           |      | DCRCDA | TA-31:05 |        |        |      |      |      |           |      | 0000       |

| 3040                        | DONODAIA                        | 15:0      |       |               |       |       |                 |           |      | DONODA | 17431.02 |        |        |      |      |      |           |      | 0000       |

| 3050                        | DCRCXOR                         | 31:16     |       | DCRCXOR<31:0> |       |       |                 |           |      |        |          |        |        |      |      |      |           |      |            |

| 3030                        | DUNUAUK                         | 15:0      |       | DCRCXOR<31:0> |       |       |                 |           |      |        |          |        |        |      |      |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |  |

| 31.24        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |  |

| 23.10        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |  |

| 15.0         | _                 | _                 | —                    | _                    | _                 |                   | —                      | _                |  |  |  |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |  |  |  |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |  |  |  |  |

|              | DIGLI             | DIVIALI           |                      | DIOLIN               |                   | ONCIULI           | EOFEF <sup>(3,5)</sup> | TIDLI            |  |  |  |  |  |

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b           | pit                |  |  |  |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

- bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit 1 = Packet is rejected due to bit stuff error 0 = Packet is accepted

bit 6 BMXEF: Bus Matrix Error Flag bit 1 = Invalid base address of the BDT, or the address of an individual buffer pointed to by a BDT entry 0 = No address error

bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup> 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet is rejected due to CRC16 error

0 = Data packet is accepted

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup> 1 = Token packet is rejected due to CRC5 error 0 = Token packet is accepted EOFEF: EOF Error Flag bit<sup>(3,5)</sup> 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

#### 12.1 Parallel I/O (PIO) Ports

All port pins have three registers (TRIS, LAT and PORT) that are directly associated with their operation.

TRIS is a Data Direction or Tri-State Control register that determines whether a digital pin is an input or an output. Setting a TRISx register bit = 1, configures the corresponding I/O pin as an input; setting a TRISx register bit = 0, configures the corresponding I/O pin as an output. All port I/O pins are defined as inputs after a device Reset. Certain I/O pins are shared with analog peripherals and default to analog inputs after a device Reset.

PORT is a register used to read the current state of the signal applied to the port I/O pins. Writing to a PORTx register performs a write to the port's latch, LATx register, latching the data to the port's I/O pins.

LAT is a register used to write data to the port I/O pins. The LATx Latch register holds the data written to either the LATx or PORTx registers. Reading the LATx Latch register reads the last value written to the corresponding PORT or Latch register.

Not all port I/O pins are implemented on some devices, therefore, the corresponding PORTx, LATx and TRISx register bits will read as zeros.

#### 12.1.1 CLR, SET AND INV REGISTERS

Every I/O module register has a corresponding Clear (CLR), Set (SET) and Invert (INV) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

| Note: | Using a PORTxINV register to toggle a bit |

|-------|-------------------------------------------|

|       | is recommended because the operation is   |

|       | performed in hardware atomically, using   |

|       | fewer instructions, as compared to the    |

|       | traditional read-modify-write method, as  |

|       | follows:                                  |

|       | PORTC $^{ = 0x0001:}$                     |

#### 12.1.2 DIGITAL INPUTS

Pins are configured as digital inputs by setting the corresponding TRIS register bits = 1. When configured as inputs, they are either TTL buffers or Schmitt Triggers. Several digital pins share functionality with analog inputs and default to the analog inputs at POR. Setting the corresponding bit in the AD1PCFG register = 1 enables the pin as a digital pin.

The maximum input voltage allowed on the input pins is the same as the maximum VIH specification. Refer to **Section 32.0 "Electrical Characteristics"** for VIH specification details.

| Note: | Analog levels on any pin that is defined as<br>a digital input (including the ANx pins)<br>may cause the input buffer to consume |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | current that exceeds the device specifications.                                                                                  |

#### 12.1.3 ANALOG INPUTS

Certain pins can be configured as analog inputs used by the ADC and comparator modules. Setting the corresponding bits in the AD1PCFG register = 0 enables the pin as an analog input pin and must have the corresponding TRIS bit set = 1 (input). If the TRIS bit is cleared = 0 (output), the digital output level (VOH or VOL) will be converted. Any time a port I/O pin is configured as analog, its digital input is disabled and the corresponding PORTx register bit will read '0'. The AD1PCFG register has a default value of 0x0000; therefore, all pins that share ANx functions are analog (not digital) by default.

#### 12.1.4 DIGITAL OUTPUTS

Pins are configured as digital outputs by setting the corresponding TRIS register bits = 0. When configured as digital outputs, these pins are CMOS drivers or can be configured as open-drain outputs by setting the corresponding bits in the Open-Drain Configuration (ODCx) register.

The open-drain feature allows generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

#### 12.1.5 ANALOG OUTPUTS

Certain pins can be configured as analog outputs, such as the CVREF output voltage used by the comparator module. Configuring the comparator reference module to provide this output will present the analog output voltage on the pin, independent of the TRIS register setting for the corresponding pin.

#### 12.1.6 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports (CNx) allows devices to generate interrupt requests in response to change-of-state on selected pin.

Each CNx pin also has a weak pull-up, which acts as a current source connected to the pin. The pull-ups are enabled by setting the corresponding bit in the CNPUE register.

# TABLE 12-9: PORTF REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX795F512H, DEVICES

| ess                         |                                 | e         |       |       |       |       |       |       |      | Bi   | its  |      |        |        |        |      |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------|--------|--------|------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2 | 17/1   | 16/0   | All Resets |

| 6140                        | TRISF                           | 31:16     | _     | —     | _     | —     | -     | —     | _    | _    | _    | —    | _      | —      | —      | _    | -      | —      | 0000       |

| 6140                        | IRIOF                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | TRISF5 | TRISF4 | TRISF3 | _    | TRISF1 | TRISF0 | 003B       |

| 6150                        | PORTF                           | 31:16     | _     | _     |       | _     |       | _     |      |      |      |      | -      | _      | _      | _    |        | -      | 0000       |

| 6150                        | PURIF                           | 15:0      |       | -     | -     | —     | —     | —     | -    | -    | -    | -    | RF5    | RF4    | RF3    |      | RF1    | RF0    | xxxx       |

| 6160                        | LATF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 6160                        | LAIF                            | 15:0      | -     | _     | —     | _     | _     | _     | _    | _    | _    | _    | LATF5  | LATF4  | LATF3  | —    | LATF1  | LATF0  | xxxx       |

| 6170                        | ODCF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 0170                        | ODCF                            | 15:0      | _     | _     | _     |       | -     |       |      |      |      |      | ODCF5  | ODCF4  | ODCF3  |      | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-10: PORTF REGISTER MAP PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX775F512L, PIC32MX7

| ess                         |       | â         |       |       |         |         |       |       |      | Bi     | ts   |      |        |        |        |        |        |        | - y       |

|-----------------------------|-------|-----------|-------|-------|---------|---------|-------|-------|------|--------|------|------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) |       | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

|                             | TDIOF | 31:16     | _     | _     | _       | _       | _     | _     | _    | _      | _    | _    | _      | _      | _      | _      | _      | _      | 0000      |

| 6140                        | TRISF | 15:0      | -     | _     | TRISF13 | TRISF12 | _     | _     | _    | TRISF8 | _    | _    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 313F      |

| 6150                        | PORTF | 31:16     | -     | _     | _       | _       | _     | -     | _    | _      | -    |      | -      |        | _      |        | _      | _      | 0000      |

| 0150                        | FUNIF | 15:0      | -     | —     | RF13    | RF12    | _     |       | _    | RF8    |      |      | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx      |

| 6160                        | LATF  | 31:16     | —     | —     | _       |         | —     | _     | _    |        | -    | _    | _      | _      | _      | _      | —      | —      | 0000      |

| 0100                        | LAIF  | 15:0      |       | —     | LATF13  | LATF12  |       | -     |      | LATF8  |      | -    | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx      |

| 6170                        | ODCF  | 31:16     | —     | _     | _       | —       | _     |       | _    |        |      |      | _      |        | —      |        |        |        | 0000      |

| 0170                        | ODCF  | 15:0      | _     | _     | ODCF13  | ODCF12  | _     | -     | —    | ODCF8  | _    | -    | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1             | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------|--|--|--|--|

| 31:24        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0               | U-0                          | U-0              |  |  |  |  |

| 31.24        | —                       | _                  | _                 | —                 | —                 | —                 | —                            | —                |  |  |  |  |

| 22:16        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0             | R/W-0                        | R/W-0            |  |  |  |  |

| 23:16        |                         | WAKFIL             |                   | —                 | —                 | SEG               | SEG2PH<2:0> <sup>(1,4)</sup> |                  |  |  |  |  |

| 15.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            |  |  |  |  |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | Ş                 | SEG1PH<2:0        | >                 | PRSEG<2:0>        |                              |                  |  |  |  |  |

| 7.0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            |  |  |  |  |

| 7:0          | SJW<1:                  | 0> <sup>(3)</sup>  |                   |                   | BRP<              | BRP<5:0>          |                              |                  |  |  |  |  |

#### REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER

| Legend:           | HC = Hardware Clear                                 | S = Settable bit     |                    |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |

#### bit 31-23 Unimplemented: Read as '0'

- bit 22 **WAKFIL:** CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|-----------|-------------------------------------------------------------------------------|

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x Tq                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | SAM: Sample of the CAN Bus Line bit <sup>(2)</sup>                            |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x Tq                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | SJW ≤ SEG2PH.                                                                 |

| 4:        | The Time Quanta per bit must be greater than 7 (that is, $TQBIT > 7$ ).       |

|           |                                                                               |

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN31           | MSEL3             | 51<1:0>           |                   | FSEL31<4:0>       |                   |                  |                  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN30           | MSEL3             | 0<1:0>            | FSEL30<4:0>       |                   |                   |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN29           | MSEL2             | 9<1:0>            | FSEL29<4:0>       |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN28           | MSEL2             | 8<1:0>            | FSEL28<4:0>       |                   |                   |                  |                  |  |  |

#### REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

| bit 31    | FLTEN31: Filter 31 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                               |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL31<1:0>: Filter 31 Mask Select bits                                                                                                                                        |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul> |

| bit 28-24 | FSEL31<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           |                                                                                                                                                                                |

|           |                                                                                                                                                                                |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| bit 23    | FLTEN30: Filter 30Enable bit                                                                                                                                                   |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                         |

| bit 22-21 | MSEL30<1:0>: Filter 30Mask Select bits                                                                                                                                         |

|           | 11 = Acceptance Mask 3 selected                                                                                                                                                |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected                                                                                                             |

|           | 00 = Acceptance Mask 0 selected                                                                                                                                                |

| bit 20-16 | FSEL30<4:0>: FIFO Selection bits                                                                                                                                               |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                    |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                    |

|           |                                                                                                                                                                                |

|           | •                                                                                                                                                                              |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                       |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'                                                                          |

#### 25.1 Control Registers

#### TABLE 25-5: ETHERNET CONTROLLER REGISTER SUMMARY FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX695F512L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX764F128H, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

| No.         No. <th>ŝ</th> <th></th> <th>its</th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th> <th></th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ŝ                          |                                 |                                                                                                                                                                                                                             |      |        |        |       |   |      |         |          | its        |         |       |        |         |         |         |         |      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------|--------|-------|---|------|---------|----------|------------|---------|-------|--------|---------|---------|---------|---------|------|

| 900         8116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bring         31/15         30/14         29/13         28/12         27/11         26/10         25/9         24/8         23/7         22/6         21/5         20/4         19/3         18/2         17/1         16/0 |      |        |        |       |   |      |         | 16/0     | All Resets |         |       |        |         |         |         |         |      |

| 100         100         -         SI(1)         -         -         TXT         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         -         - <t< td=""><td></td><td>FTUOONIA</td><td>31:16</td><td></td><td></td><td></td><td></td><td></td><td></td><td></td><td>PTV&lt;</td><td>:15:0&gt;</td><td></td><td></td><td></td><td>1</td><td>1</td><td></td><td>1</td><td>0000</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                            | FTUOONIA                        | 31:16                                                                                                                                                                                                                       |      |        |        |       |   |      |         | PTV<     | :15:0>     |         |       |        | 1       | 1       |         | 1       | 0000 |

| 9010       FTHC012       15.0       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       -       <                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 9000                       | ETHCON1                         | 15:0                                                                                                                                                                                                                        | ON   | _      | SIDL   | _     | — | _    | TXRTS   | RXEN     | AUTOFC     | _       | _     | MANFC  |         | —       | _       | BUFCDEC | 0000 |

| Note       9020     PTHXX     31:6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 9010                       | ETHCON2                         |                                                                                                                                                                                                                             | _    | _      | —      | -     | — | -    | -       |          | _          |         | _     | _      | _       | -       | _       | _       | 0000 |

| 9020       FH/XS1       15.0       -       -       -       -       -       -       -       000       000       000       ETHRS1       31:6       -       -       -       000       000       000       ETHRS1       31:6       -       -       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000       000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3010                       | LINGONZ                         |                                                                                                                                                                                                                             | —    | —      | _      | —     | _ |      |         |          |            | >       |       |        |         | —       | —       | —       | 0000 |

| Image: marrow of the strephysical strep                  | 9020                       | ETHTXST                         |                                                                                                                                                                                                                             |      |        |        |       |   |      |         |          | R<31:16>   |         |       |        |         |         |         |         | 0000 |

| 9030       ETHRNS       15.0       -       -       0       0         9040       ETHRND       31:6       -       -       -       00       00       00       15.0       -       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00       00 <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>TXSTADI</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>_</td> <td>0000</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                            |                                 |                                                                                                                                                                                                                             |      |        |        |       |   |      | TXSTADI |          |            |         |       |        |         |         |         | _       | 0000 |

| 9040         ETHHT0         31:6<br>15:0         Image: State                                               | 9030                       | ETHRXST                         |                                                                                                                                                                                                                             |      |        |        |       |   |      |         |          | )R<31:16>  |         |       |        |         |         |         |         | 0000 |