Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              |                                                                                 |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 16x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 121-TFBGA                                                                       |

| Supplier Device Package    | 121-TFBGA (10x10)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx564f128lt-v-bg |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX5XX/6XX/7XX

|         |                      | Pin Nur         | nber <sup>(1)</sup> |                 | Pin         | Duffer         | Description                       |  |  |

|---------|----------------------|-----------------|---------------------|-----------------|-------------|----------------|-----------------------------------|--|--|

| Pin Nam | e 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type |                                   |  |  |

| RA0     | _                    | 17              | G3                  | B9              | I/O         | ST             | PORTA is a bidirectional I/O port |  |  |

| RA1     | —                    | 38              | J6                  | A26             | I/O         | ST             |                                   |  |  |

| RA2     | —                    | 58              | H11                 | A39             | I/O         | ST             |                                   |  |  |

| RA3     | —                    | 59              | G10                 | B32             | I/O         | ST             |                                   |  |  |

| RA4     | —                    | 60              | G11                 | A40             | I/O         | ST             |                                   |  |  |

| RA5     | —                    | 61              | G9                  | B33             | I/O         | ST             |                                   |  |  |

| RA6     | —                    | 91              | C5                  | B51             | I/O         | ST             |                                   |  |  |

| RA7     | —                    | 92              | B5                  | A62             | I/O         | ST             |                                   |  |  |

| RA9     | —                    | 28              | L2                  | A21             | I/O         | ST             |                                   |  |  |

| RA10    |                      | 29              | K3                  | B17             | I/O         | ST             | ]                                 |  |  |

| RA14    |                      | 66              | E11                 | B36             | I/O         | ST             | ]                                 |  |  |

| RA15    | —                    | 67              | E8                  | A44             | I/O         | ST             |                                   |  |  |

| RB0     | 16                   | 25              | K2                  | B14             | I/O         | ST             | PORTB is a bidirectional I/O port |  |  |

| RB1     | 15                   | 24              | K1                  | A15             | I/O         | ST             |                                   |  |  |

| RB2     | 14                   | 23              | J2                  | B13             | I/O         | ST             |                                   |  |  |

| RB3     | 13                   | 22              | J1                  | A13             | I/O         | ST             |                                   |  |  |

| RB4     | 12                   | 21              | H2                  | B11             | I/O         | ST             |                                   |  |  |

| RB5     | 11                   | 20              | H1                  | A12             | I/O         | ST             |                                   |  |  |

| RB6     | 17                   | 26              | L1                  | A20             | I/O         | ST             |                                   |  |  |

| RB7     | 18                   | 27              | J3                  | B16             | I/O         | ST             |                                   |  |  |

| RB8     | 21                   | 32              | K4                  | A23             | I/O         | ST             |                                   |  |  |

| RB9     | 22                   | 33              | L4                  | B19             | I/O         | ST             |                                   |  |  |

| RB10    | 23                   | 34              | L5                  | A24             | I/O         | ST             | 1                                 |  |  |

| RB11    | 24                   | 35              | J5                  | B20             | I/O         | ST             | ]                                 |  |  |

| RB12    | 27                   | 41              | J7                  | B23             | I/O         | ST             | ]                                 |  |  |

| RB13    | 28                   | 42              | L7                  | A28             | I/O         | ST             | ]                                 |  |  |

| RB14    | 29                   | 43              | K7                  | B24             | I/O         | ST             |                                   |  |  |

| RB15    | 30                   | 44              | L8                  | A29             | I/O         | ST             |                                   |  |  |

| RC1     | —                    | 6               | D1                  | A5              | I/O         | ST             | PORTC is a bidirectional I/O port |  |  |

| RC2     | —                    | 7               | E4                  | B4              | I/O         | ST             |                                   |  |  |

| RC3     | —                    | 8               | E2                  | A6              | I/O         | ST             |                                   |  |  |

| RC4     |                      | 9               | E1                  | B5              | I/O         | ST             | ]                                 |  |  |

| RC12    | 39                   | 63              | F9                  | B34             | I/O         | ST             | ]                                 |  |  |

| RC13    | 47                   | 73              | C10                 | A47             | I/O         | ST             | ]                                 |  |  |

| RC14    | 48                   | 74              | B11                 | B40             | I/O         | ST             | ]                                 |  |  |

|         | -                    | 64              | F11                 | A42             | I/O         | ST             | 1                                 |  |  |

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |

#### REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **BMXDRMSZ<31:0>:** Data RAM Memory (DRM) Size bits Static value that indicates the size of the Data RAM in bytes: 0x00004000 = device has 16 KB RAM 0x00008000 = device has 32 KB RAM 0x00010000 = device has 64 KB RAM

## REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER<sup>(1,2)</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | _                 | _                 | —                 | _                 | —                 |                  | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | _                 | —                 | _                 | —                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | BMXPUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 **BMXPUPBA<10:0>:** Program Flash (PFM) User Program Base Address Read-Only bits Value is always '0', which forces 2 KB increments

- **Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

- **2:** The value in this register must be less than or equal to BMXPFMSZ.

#### **TABLE 7-7:** INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |                            |                            |             |        | В                     | its  |      |             |             |             |                |             |                      |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|----------------------------|----------------------------|-------------|--------|-----------------------|------|------|-------------|-------------|-------------|----------------|-------------|----------------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12                      | 27/11                      | 26/10       | 25/9   | 24/8                  | 23/7 | 22/6 | 21/5        | 20/4        | 19/3        | 18/2           | 17/1        | 16/0                 | All Resets |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |                            | INT4IP<2:0>                |             | INT4IS | S<1:0>                | _    | _    | _           |             | OC4IP<2:0>  |                | OC4IS       | 5<1:0>               | 0000       |

| TODO                        | IPC4                            | 15:0      | _     | _     | —     |                            | IC4IP<2:0>                 |             | IC4IS  | <1:0>                 | _    | _    | -           |             | T4IP<2:0>   |                | T4IS-       | <1:0>                | 0000       |

| 10E0                        | IPC5                            | 31:16     | _     |       | —     |                            | SPI1IP<2:0>                | •           | SPI1IS | S<1:0>                | _    | _    | _           |             | OC5IP<2:0>  | •              | OC5IS       | S<1:0>               | 0000       |

| IUEU                        | IPC5                            | 15:0      | —     | _     | _     |                            | IC5IP<2:0>                 |             | IC5IS  | <1:0>                 | _    | _    | _           |             | T5IP<2:0>   |                | T5IS-       | <1:0>                | 0000       |

|                             |                                 | 31:16     | —     | _     | _     |                            | AD1IP<2:0>                 |             | AD1IS  | S<1:0>                | _    | _    | _           |             | CNIP<2:0>   |                | CNIS        | <1:0>                | 0000       |

| 10F0                        | IPC6                            |           |       |       |       |                            |                            |             |        |                       |      |      |             |             | U1IP<2:0>   |                | U1IS-       | <1:0>                |            |

| 1000                        | IFCO                            | 15:0      | _     | -     | -     | I2C1IP<2:0>                |                            | I2C1IS<1:0> |        | —                     | —    | —    | SPI3IP<2:0> |             | SPI3IS      | SPI3IS<1:0> 00 | 0000        |                      |            |

|                             |                                 |           |       |       |       |                            |                            |             |        |                       |      |      | I2C3IP<2:0> |             | 12C315      | 5<1:0>         |             |                      |            |

|                             |                                 |           |       |       |       |                            | U3IP<2:0>                  |             | U3IS   | <1:0>                 |      |      |             |             |             |                |             |                      |            |

| 1100                        | IPC7                            | 31:16     | —     | —     | -     | SPI2IP<2:0><br>I2C4IP<2:0> |                            | SPI2IS      | S<1:0> | —                     | —    | -    |             | CMP2IP<2:0  | >           | CMP2I          | CMP2IS<1:0> | 0000                 |            |

| 1100                        | 11 07                           |           |       |       |       |                            |                            |             | 12C418 | S<1:0>                |      |      |             |             |             |                |             |                      |            |

|                             |                                 | 15:0      | _     |       |       | (                          | CMP1IP<2:0                 | >           | CMP1I  | S<1:0>                | —    | —    | —           |             | PMPIP<2:0>  | •              | PMPIS       | S<1:0>               | 0000       |

|                             |                                 | 31:16     | _     | —     | —     | F                          | RTCCIP<2:0                 | >           | RTCCI  | S<1:0>                | —    | —    | —           | I           | SCMIP<2:0   | >              | FSCMI       | S<1:0>               | 0000       |

| 1110                        | IPC8                            |           |       |       |       |                            |                            |             |        |                       |      |      |             |             | U2IP<2:0>   |                | U2IS        | <1:0>                |            |

| 1110                        | 11 00                           | 15:0      | —     | —     | -     |                            | I2C2IP<2:0>                |             | 12C218 | S<1:0>                | —    | —    | —           |             | SPI4IP<2:0> | •              | SPI4IS      | S<1:0>               | 0000       |

|                             |                                 |           |       |       |       |                            |                            |             |        |                       |      |      |             |             | I2C5IP<2:0> | •              | 12C518      | 5<1:0>               |            |

| 1120                        | IPC9                            | 31:16     | —     | —     | —     | [                          | DMA3IP<2:0                 | >           | DMA3I  | S<1:0>                | —    | —    | —           | I           | DMA2IP<2:0  | >              | DMA2I       | S<1:0>               | 0000       |

| 1120                        | IFC9                            | 15:0      | —     | -     | —     |                            | DMA1IP<2:0                 |             | DMA1I  | S<1:0>                | —    | —    | _           |             | DMA0IP<2:0  |                | DMA0I       | S<1:0>               | 0000       |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | D                          | MA7IP<2:0>                 | (2)         | DMA7IS | S<1:0> <sup>(2)</sup> | —    | —    | —           | D           | MA6IP<2:0>  | (2)            | DMA6IS      | <1:0> <sup>(2)</sup> | 0000       |

| 1130                        | IFCIU                           | 15:0      | —     | _     | _     | D                          | MA5IP<2:0>                 | (2)         | DMA5IS | S<1:0> <sup>(2)</sup> | _    | _    | _           | D           | MA4IP<2:0>  | (2)            | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |

| 1140                        | IPC11                           | 31:16     |       | -     | —     | C                          | CAN2IP<2:0> <sup>(2)</sup> |             | CAN2IS | S<1:0> <sup>(2)</sup> | _    | _    | _           | CAN1IP<2:0> |             | CAN1           | S<1:0>      | 0000                 |            |

| 1140                        | IFCII                           | 15:0      | —     | _     | —     |                            | USBIP<2:0>                 |             | USBIS  | S<1:0>                | _    | —    | _           |             | FCEIP<2:0>  |                | FCEIS       | <1:0>                | 0000       |

| 1150                        | IPC12                           | 31:16     | _     | _     | —     |                            | U5IP<2:0>                  |             | U5IS   | <1:0>                 | —    | —    | —           |             | U6IP<2:0>   |                | U6IS-       | <1:0>                | 0000       |

| 1150                        | IFC12                           | 15:0      |       | —     | _     |                            | U4IP<2:0>                  |             | U4IS   | <1:0>                 | —    | _    | —           |             | ETHIP<2:0>  |                | ETHIS       | <1:0>                | 0000       |

DS60001156J-page 88

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

## REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31.24        |                   | —                 | —                 |                   | IP03<2:0>         | IS03-             | IS03<1:0>        |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        |                   | —                 | —                 |                   | IP02<2:0>         | IS02<1:0>         |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         |                   | —                 | —                 |                   | IP01<2:0>         | IS01<1:0>         |                  |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          |                   | _                 |                   |                   | IP00<2:0>         |                   | IS00-            | <1:0>            |  |

## Legend:

| 3                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP03<2:0>: Interrupt Priority bits                                   |

|-----------|----------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •<br>010 = Interrupt priority is 2                                   |

|           | 010 = Interrupt priority is 2<br>001 = Interrupt priority is 1       |

|           | 000 = Interrupt is disabled                                          |

| bit 25-24 | <b>IS03&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2                                     |

|           | 01 = Interrupt sub-priority is 1                                     |

|           | 00 = Interrupt sub-priority is 0                                     |

| bit 23-21 | Unimplemented: Read as '0'                                           |

| bit 20-18 | IP02<2:0>: Interrupt Priority bits                                   |

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •                                                                    |

|           | 010 = Interrupt priority is 2                                        |

|           | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled         |

| hit 17 16 | •                                                                    |

| DIL 17-10 | <b>IS02&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2<br>01 = Interrupt sub-priority is 1 |

|           | 00 = Interrupt sub-priority is 0                                     |

| hit 15-13 | Unimplemented: Read as '0'                                           |

| 511 10 10 | Chimpionionicu. Nodu do 0                                            |

| Note:     | This register represents a generic definition                        |

| 1         | · · · ·                                                              |

definitions.

ister represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit ns.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | LTAGBOOT          | —                 | _                 | -                 | —                 | _                 | _                | —                |  |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 10.0         | LTAG<11:4>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |  |

| 7.0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |  |  |  |

## REGISTER 9-3: CHETAG: CACHE TAG REGISTER

## Legend:

| 3                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31 LTAGBOOT: Line Tag Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line Tag Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 |                  | —                |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | CHCSIZ            | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | CHCSIZ<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

111111111111111 = 65,535 bytes transferred on an event

## REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | CHCPTR            | <15:8>            |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | CHCPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

## TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                        |                                 |           |       |       |       |       |       |       |      |      | Bits |      |      |          |        |        |         |        |            |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 53A0                       | U1EP10                          | 31:16     | _     | _     | _     | _     | _     | —     | _    | _    |      | _    | —    | —        | -      |        | _       | _      | 0000       |

| 55A0                       | UIEFIU                          | 15:0      | —     | —     | _     | _     | _     | —     | _    | _    | _    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                       | U1EP11                          | 31:16     | -     | _     | _     |       |       | _     |      |      |      | _    | _    | —        |        |        | _       |        | 0000       |

| 5560                       | UIEFII                          | 15:0      | -     | _     | _     |       |       | _     |      |      |      | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                       | U1EP12                          | 31:16     | Ι     | -     |       | -     |       | _     |      |      | _    | —    | —    | _        | -      | -      | _       | -      | 0000       |

| 5300                       | UTEPTZ                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | _    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5000                       |                                 | 31:16     |       | _     | _     | —     | _     | -     | —    | —    | _    | -    | —    | —        | —      | _      | _       | _      | 0000       |

| 53D0                       | U1EP13                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | _    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

|                            |                                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                       | U1EP14                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                       |                                 | 31:16     | _     | _     | _     |       | -     | _     | _    | _    | -    | _    | —    | _        |        |        | —       | -      | 0000       |

| 53F0                       | U1EP15                          | 15:0      | _     | —     | —     | -     |       | _     | -    | —    |      | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated SET and INV registers. 2:

3: This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined. 4:

## 13.2 Control Registers

## TABLE 13-1: TIMER1 REGISTER MAP

| ess                       |                                 | â         |                | Bits 2          |       |       |       |       |      |      |       |      |      |        | 6    |       |      |      |            |

|---------------------------|---------------------------------|-----------|----------------|-----------------|-------|-------|-------|-------|------|------|-------|------|------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15          | 30/14           | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7  | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0000                      | TACON                           | 31:16     | -              | _               | -     | _     | _     | —     | _    | —    | _     | —    | _    | —      | —    | _     | —    | _    | 0000       |

| 0600                      | T1CON                           | 15:0      | ON             | _               | SIDL  | TWDIS | TWIP  | —     | _    | _    | TGATE | _    | TCKP | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     | _              | Ι               | _     | _     | _     | _     | -    | _    | _     | _    | -    | _      | —    | -     | _    | _    | 0000       |

| 0610                      | I IVIR I                        | 15:0      |                | TMR1<15:0> 0000 |       |       |       |       |      |      |       |      | 0000 |        |      |       |      |      |            |

| 0620                      | PR1                             | 31:16     | —              | -               |       |       |       | _     | _    | _    | _     |      | _    | _      | —    | _     | _    | _    | 0000       |

| 0020                      | FRI                             | 15:0      | PR1<15:0> FFFF |                 |       |       |       |       |      |      | FFFF  |      |      |        |      |       |      |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | -                 | -                 | _                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | _                 | _                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | TWDIS             | TWIP              | -                 |                  | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | —                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | —                |

## REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1)</sup>

- 1 = Timer is enabled 0 = Timer is disabled

#### bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation when device is in Idle mode

## bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

- 1 = Writes to TMR1 are ignored until pending write operation completes

- 0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

## bit 11 TWIP: Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to TMR1 register in progress

0 = Asynchronous write to TMR1 register complete

In Synchronous Timer mode:

This bit is read as '0'.

- bit 10-8 **Unimplemented:** Read as '0'

- bit 7 TGATE: Timer Gated Time Accumulation Enable bit

<u>When TCS = 1:</u> This bit is ignored.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 =Gated time accumulation is disabled

- bit 6 Unimplemented: Read as '0'

- bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

- 11 = 1:256 prescale value

- 10 = 1:64 prescale value

- 01 = 1:8 prescale value

- 00 = 1:1 prescale value

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

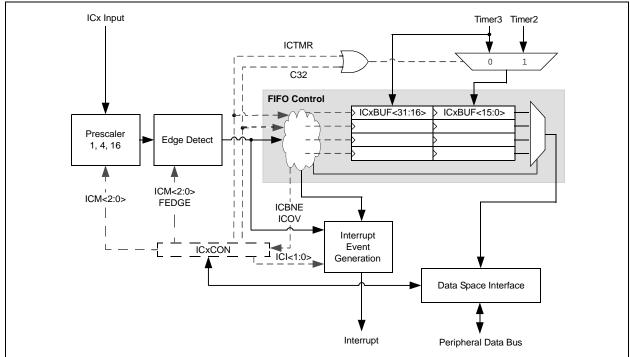

## 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input Capture module can also be used to provide additional sources of external interrupts

## FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

#### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                     | —                     | _                 | —                 | _                 | _                 |                  | _                |

| 22.46        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                     | —                     |                   |                   |                   | -                 |                  | -                |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   |                   |                   | .4.2.0            |                  |                  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   | ADDR              | <13:8>            |                  |                  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | ADDR<7:0>             |                       |                   |                   |                   |                   |                  |                  |

## REGISTER 21-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | mented bit, read as '0' |  |

|-------------------|------------------|--------------------------|-------------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown      |  |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Destination Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- **Note 1:** When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- 3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

## REGISTER 24-10: CIFLTCONO: CAN FILTER CONTROL REGISTER 0 (CONTINUED)

| bit 15    | FLTEN1: Filter 1 Enable bit<br>1 = Filter is enabled               |

|-----------|--------------------------------------------------------------------|

|           | 0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 7     | FLTEN0: Filter 0 Enable bit                                        |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                    |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                    |

| DIL 4-0   | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1    |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           |                                                             |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| r         |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        | HT<31:24>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | HT<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | HT<7:0>           |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 25-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                                                     |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

## REGISTER 25-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24     |                   |                   |                   | HT<6              | 3:56>             |                   |                  |                  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | HT<47:40>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       |                   |                   |                   | HT<3              | 9:32>             |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

## REGISTER 25-34: EMAC1MWTD: ETHERNET CONTROLLER MAC MII MANAGEMENT WRITE DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 | _                 | —                 | —                 |                   | —                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 |                   | —                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | MWTD<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | MWTD<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MWTD<15:0>: MII Management Write Data bits

When written, a MII Management write cycle is performed using the 16-bit data and the pre-configured PHY and Register addresses from the EMAC1MADR register.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## REGISTER 25-35: EMAC1MRDD: ETHERNET CONTROLLER MAC MII MANAGEMENT READ DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 |                   | —                 | —                 |                   | -                | _                |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 | _                 | _                | _                |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | MRDD<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | MRDD              | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MRDD<15:0>: MII Management Read Data bits

Following a MII Management Read Cycle, the 16-bit data can be read from this location.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## PIC32MX5XX/6XX/7XX

NOTES:

## 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC CHARACTERISTICS |        |                                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                        |          |       |                                                   |

|--------------------|--------|---------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|----------|-------|---------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                         | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(1)</sup> | Max.     | Units | Conditions                                        |

|                    | VIL    | Input Low Voltage                                       |                                                                                                                                                                                                                                                                                       |                        |          |       |                                                   |

| DI10               |        | I/O Pins:                                               |                                                                                                                                                                                                                                                                                       |                        |          |       |                                                   |