Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256h-80v-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

1

#### TABLE 8: PIN NAMES FOR 100-PIN USB AND ETHERNET DEVICES (CONTINUED)

#### **100-PIN TQFP (TOP VIEW)**

PIC32MX664F064L PIC32MX664F128L PIC32MX675F256L PIC32MX675F512L PIC32MX695F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name   |

|-------|---------------------------------|-------|-----------------|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD             |

| 72    | SDO1/OC1/INT0/RD0               | 87    | ETXD1/PMD11/RF0 |

| 73    | SOSCI/CN1/RC13                  | 88    | ETXD0/PMD10/RF1 |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | ETXERR/PMD9/RG1 |

| 75    | Vss                             | 90    | PMD8/RG0        |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6       |

| 77    | OC3/RD2                         | 92    | TRD3/RA7        |

| 78    | OC4/RD3                         | 93    | PMD0/RE0        |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1        |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14       |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12       |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13       |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2        |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3        |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4        |

Note 1: Shaded pins are 5V tolerant.

#### **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|           |                    | Pin Number <sup>(1)</sup> |                  |        |     |                |                                                            |  |

|-----------|--------------------|---------------------------|------------------|--------|-----|----------------|------------------------------------------------------------|--|

| Pin Name  | 64-Pin<br>QFN/TQFP | 100-Pin<br>TQFP           | 121-Pin<br>TFBGA |        |     | Buffer<br>Type | Description                                                |  |

| AC2TX     | —                  | 7                         | E4               | B4     | 0   | _              | Alternate CAN2 bus transmit pin                            |  |

| ERXD0     | 61                 | 41                        | J7               | B23    | I   | ST             | Ethernet Receive Data 0 <sup>(2)</sup>                     |  |

| ERXD1     | 60                 | 42                        | L7               | A28    | I   | ST             | Ethernet Receive Data 1 <sup>(2)</sup>                     |  |

| ERXD2     | 59                 | 43                        | K7               | B24    | I   | ST             | Ethernet Receive Data 2 <sup>(2)</sup>                     |  |

| ERXD3     | 58                 | 44                        | L8               | A29    | I   | ST             | Ethernet Receive Data 3 <sup>(2)</sup>                     |  |

| ERXERR    | 64                 | 35                        | J5               | B20    | I   | ST             | Ethernet receive error input <sup>(2)</sup>                |  |

| ERXDV     | 62                 | 12                        | F2               | A8     | I   | ST             | Ethernet receive data valid <sup>(2)</sup>                 |  |

| ECRSDV    | 62                 | 12                        | F2               | A8     | I   | ST             | Ethernet carrier sense data valid <sup>(2)</sup>           |  |

| ERXCLK    | 63                 | 14                        | F3               | A9     | I   | ST             | Ethernet receive clock <sup>(2)</sup>                      |  |

| EREFCLK   | 63                 | 14                        | F3               | A9     | I   | ST             | Ethernet reference clock <sup>(2)</sup>                    |  |

| ETXD0     | 2                  | 88                        | A6               | A60    | 0   | _              | Ethernet Transmit Data 0 <sup>(2)</sup>                    |  |

| ETXD1     | 3                  | 87                        | B6               | B49    | 0   | _              | Ethernet Transmit Data 1 <sup>(2)</sup>                    |  |

| ETXD2     | 43                 | 79                        | A9               | B43    | 0   | _              | Ethernet Transmit Data 2 <sup>(2)</sup>                    |  |

| ETXD3     | 42                 | 80                        | D8               | A54    | 0   | _              | Ethernet Transmit Data 3 <sup>(2)</sup>                    |  |

| ETXERR    | 54                 | 89                        | E6               | B50    | 0   | _              | Ethernet transmit error <sup>(2)</sup>                     |  |

| ETXEN     | 1                  | 83                        | D7               | B45    | 0   | _              | Ethernet transmit enable <sup>(2)</sup>                    |  |

| ETXCLK    | 55                 | 84                        | C7               | A56    | I   | ST             | Ethernet transmit clock <sup>(2)</sup>                     |  |

| ECOL      | 44                 | 10                        | E3               | A7     | I   | ST             | Ethernet collision detect <sup>(2)</sup>                   |  |

| ECRS      | 45                 | 11                        | F4               | B6     | I   | ST             | Ethernet carrier sense <sup>(2)</sup>                      |  |

| EMDC      | 30                 | 71                        | C11              | A46    | 0   | _              | Ethernet management data clock <sup>(2)</sup>              |  |

| EMDIO     | 49                 | 68                        | E9               | B37    | I/O | _              | Ethernet management data <sup>(2)</sup>                    |  |

| AERXD0    | 43                 | 18                        | G1               | A11    | I   | ST             | Alternate Ethernet Receive Data 0 <sup>(2)</sup>           |  |

| AERXD1    | 42                 | 19                        | G2               | B10    | I   | ST             | Alternate Ethernet Receive Data 1 <sup>(2)</sup>           |  |

| AERXD2    | —                  | 28                        | L2               | A21    | I   | ST             | Alternate Ethernet Receive Data 2(2)                       |  |

| AERXD3    | —                  | 29                        | K3               | B17    | I   | ST             | Alternate Ethernet Receive Data 3 <sup>(2)</sup>           |  |

| AERXERR   | 55                 | 1                         | B2               | A2     | I   | ST             | Alternate Ethernet receive error input <sup>(2)</sup>      |  |

| AERXDV    | —                  | 12                        | F2               | A8     | I   | ST             | Alternate Ethernet receive data valid <sup>(2)</sup>       |  |

| AECRSDV   | 44                 | 12                        | F2               | A8     | I   | ST             | Alternate Ethernet carrier sense data valid <sup>(2)</sup> |  |

| AERXCLK   | —                  | 14                        | F3               | A9     | I   | ST             | Alternate Ethernet receive clock <sup>(2)</sup>            |  |

| AEREFCLK  | 45                 | 14                        | F3               | A9     | I   | ST             | Alternate Ethernet reference clock <sup>(2)</sup>          |  |

| AETXD0    | 59                 | 47                        | L9               | B26    | 0   |                | Alternate Ethernet Transmit Data 0 <sup>(2)</sup>          |  |

| AETXD1    | 58                 | 48                        | K9               | A31    | 0   |                | Alternate Ethernet Transmit Data 1 <sup>(2)</sup>          |  |

| AETXD2    |                    | 44                        | L8               | A29    | 0   |                | Alternate Ethernet Transmit Data 2 <sup>(2)</sup>          |  |

| AETXD3    |                    | 43                        | K7               | B24    | 0   |                | Alternate Ethernet Transmit Data 3 <sup>(2)</sup>          |  |

| AETXERR   |                    | 35                        | J5               | B20    | 0   |                | Alternate Ethernet transmit error <sup>(2)</sup>           |  |

| AETXEN    | 54                 | 67                        | E8               | A44    | 0   |                | Alternate Ethernet transmit enable <sup>(2)</sup>          |  |

| AETXCLK   | _                  | 66                        | E11              | B36    | 1   | ST             | Alternate Ethernet transmit clock <sup>(2)</sup>           |  |

| AECOL     |                    | 42                        | L7               | A28    | 1   | ST             | Alternate Ethernet collision detect <sup>(2)</sup>         |  |

| Leaend: C | MOS = CMO          | S compatib                | le input or c    | butput | A   | nalog = A      | Analog input P = Power                                     |  |

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels

Analog = Analog input P = PowerO = Output I = Input

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

# Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | _                 | —                 | -                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23.10        | —                 | —                 | —                 | —                 | _                 | —                 | —                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | —                 | —                 | MVEC              | _                 | TPC<2:0>          |                  |                  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-17 Unimplemented: Read as '0'

- bit 16 **SS0:** Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

- bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multiple Vector Configuration bit

- 1 = Interrupt controller configured for Multi-vector mode

- 0 = Interrupt controller configured for Single-vector mode

- bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer

- 000 = Disables Interrupt Proximity timer

- bit 7-5 Unimplemented: Read as '0'

- bit 4 INT4EP: External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   | —                 | —                 |                   | IP03<2:0>         | IS03<1:0>         |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        |                   | —                 | —                 |                   | IP02<2:0>         | IS02<1:0>         |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         |                   | —                 | —                 |                   | IP01<2:0>         | IS01-             | <1:0>            |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | _                 |                   |                   | IP00<2:0>         | IS00-             | <1:0>            |                  |

#### Legend:

| 3                                 |                  |                                    |                    |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP03<2:0>: Interrupt Priority bits                                   |

|-----------|----------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •<br>010 = Interrupt priority is 2                                   |

|           | 010 = Interrupt priority is 2<br>001 = Interrupt priority is 1       |

|           | 000 = Interrupt is disabled                                          |

| bit 25-24 | <b>IS03&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2                                     |

|           | 01 = Interrupt sub-priority is 1                                     |

|           | 00 = Interrupt sub-priority is 0                                     |

| bit 23-21 | Unimplemented: Read as '0'                                           |

| bit 20-18 | IP02<2:0>: Interrupt Priority bits                                   |

|           | 111 = Interrupt priority is 7                                        |

|           | •                                                                    |

|           | •                                                                    |

|           | •                                                                    |

|           | 010 = Interrupt priority is 2                                        |

|           | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled         |

| hit 17 16 | •                                                                    |

| DIL 17-10 | <b>IS02&lt;1:0&gt;:</b> Interrupt Sub-priority bits                  |

|           | 11 = Interrupt sub-priority is 3                                     |

|           | 10 = Interrupt sub-priority is 2<br>01 = Interrupt sub-priority is 1 |

|           | 00 = Interrupt sub-priority is 0                                     |

| hit 15-13 | Unimplemented: Read as '0'                                           |

| 511 10 10 | Chimpionionicu. Nodu do 0                                            |

| Note:     | This register represents a generic definition                        |

| 1         | · · · ·                                                              |

definitions.

ister represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit ns.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          | CHEW1<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                                                                      |                      |                    |  |  |

|-------------------|----------------------------------------------------------------------|----------------------|--------------------|--|--|

| R = Readable bit  | R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |

| -n = Value at POR | '1' = Bit is set                                                     | '0' = Bit is cleared | x = Bit is unknown |  |  |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

#### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   | CHEW2<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   |                   |                   | CHEW2             | <15:8>            |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

#### **Control Registers** 10.1

#### TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                       | â         |       |               |       |         |         |       |      | Bi   | its  |      |      |      |      |      |      |      | ő          |

|-----------------------------|-----------------------|-----------|-------|---------------|-------|---------|---------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range | 31/15 | 30/14         | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                        | DMACON <sup>(1)</sup> | 31:16     | _     | _             | -     | _       | _       |       | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 3000                        | DMACON                | 15:0      | ON    | _             | _     | SUSPEND | DMABUSY | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 2010                        | DMASTAT               | 31:16     | _     | _             | _     | _       | —       | _     | _    | _    | _    | -    | _    | _    | —    | _    | _    | _    | 0000       |

| 3010                        | DIVIASTAT             | 15:0      | _     | <u> </u>      |       |         |         |       |      |      |      |      |      |      |      |      |      |      |            |

| 2020                        | DMAADDR               | 31:16     |       | DMAADDR<31:0> |       |         |         |       |      |      |      |      |      |      |      |      |      |      |            |

| 3020                        | DIVIAADDR             | 15:0      |       |               |       |         |         |       |      |      |      |      |      |      |      |      |      |      |            |

| Legen                       |                       |           |       |               |       |         |         |       |      |      |      |      |      |      |      |      |      |      |            |

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

DMACH<3> bit is not available on PIC32MX534/564/664/764 devices. 2:

## TABLE 10-2: DMA CRC REGISTER MAP<sup>(1)</sup>

| ess                         |                                                          | 0     |       |                     |       |       |       |           |      | В    | ts       |        |        |      |      |      |           |      | ú          |

|-----------------------------|----------------------------------------------------------|-------|-------|---------------------|-------|-------|-------|-----------|------|------|----------|--------|--------|------|------|------|-----------|------|------------|

| Virtual Address<br>(BF88_#) | (BF88_#)<br>Register<br>Name <sup>(1)</sup><br>Bit Range |       | 31/15 | 30/14               | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7     | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1      | 16/0 | All Resets |

| 2020                        | DCRCCON                                                  | 31:16 | _     | _                   | BYTO  | <1:0> | WBO   | _         | —    | BITO | —        | _      |        | _    | _    | —    | —         | _    | 0000       |

| 3030                        | DURCUUN                                                  | 15:0  | —     | —                   | —     |       |       | PLEN<4:0> |      |      | CRCEN    | CRCAPP | CRCTYP | _    | —    | (    | CRCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA                                                 | 31:16 |       |                     |       |       |       |           |      |      | TA-31:05 |        |        |      |      |      |           |      | 0000       |

| 3040                        | DONODAIA                                                 | 15:0  |       | DCRCDATA<31:0> 0000 |       |       |       |           |      |      |          |        |        |      |      |      |           |      |            |

| 3050                        | DCRCXOR                                                  | 31:16 |       | DCPCYOR-31:0- 0000  |       |       |       |           |      |      |          |        |        |      |      |      |           |      |            |

| 3030                        | DUNUAUK                                                  | 15:0  |       | DCRCXOR<31:0> 0000  |       |       |       |           |      |      |          |        |        |      |      |      |           |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   | _                 |                   | _                    | _                 | _                | —                |

| 22.16        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 23:16        |                   |                   |                   | CHAIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 15.0         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 15:8         |                   |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 7:0          | S-0               | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |

| 7.0          | CFORCE            | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | —                |

#### REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |  |  |  |  |  |

### REGISTER 23-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

1 = Select ANx for input scan

0 =Skip ANx for input scan

Note 1: CSSL = ANx, where 'x' = 0-15.

bit 15-0 CSSL<15:0>: ADC Input Pin Scan Selection bits<sup>(1)</sup>

#### REGISTER 25-9: ETHPMCS: ETHERNET CONTROLLER PATTERN MATCH CHECKSUM REGISTER

| Bit Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|---------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 23:16         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 15:8          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6          |                   | PMCS<15:8>        |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0 PMCS<7:0> |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-8 PMCS<15:8>: Pattern Match Checksum 1 bits

bit 7-0 PMCS<7:0>: Pattern Match Checksum 0 bits

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

#### REGISTER 25-10: ETHPMO: ETHERNET CONTROLLER PATTERN MATCH OFFSET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.6         |                   | PMO<15:8>         |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | 7:0 PMO<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **PMO<15:0>:** Pattern Match Offset 1 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the PMMODE bit (ETHRXFC<11:8>) = 0.

# REGISTER 25-34: EMAC1MWTD: ETHERNET CONTROLLER MAC MII MANAGEMENT WRITE DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | —                 | _                 | —                 | _                 |                   | —                | _                |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | MWTD<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | MWTD<7            | :0>               |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MWTD<15:0>: MII Management Write Data bits

When written, a MII Management write cycle is performed using the 16-bit data and the pre-configured PHY and Register addresses from the EMAC1MADR register.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# REGISTER 25-35: EMAC1MRDD: ETHERNET CONTROLLER MAC MII MANAGEMENT READ DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | —                 |                   | —                 | —                 |                   |                  | _                |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | —                 | _                 | _                 | —                 | _                 | _                | _                |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | MRDD<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | MRDD              | <7:0>             |                   |                  |                  |  |

| Legend:           |                  |                          |                    |  |  |

|-------------------|------------------|--------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | , read as '0'      |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 MRDD<15:0>: MII Management Read Data bits

Following a MII Management Read Cycle, the 16-bit data can be read from this location.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# 27.1 Control Register

# TABLE 27-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| lress<br>¢)              | (BF80_#)<br>Register<br>Name <sup>(1)</sup><br>Bit Range |       | Bits  |       |       |       |       |                        |       |                      |      |       |      |       |      |      |      |      |           |

|--------------------------|----------------------------------------------------------|-------|-------|-------|-------|-------|-------|------------------------|-------|----------------------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addr<br>(BF80_#) |                                                          | Rang  | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10                  | 25/9  | 24/8                 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                     | CVRCON                                                   | 31:16 |       |       | —     | —     | —     | -                      | —     | _                    | _    | _     |      | _     |      | —    |      | —    | 0000      |

| 9800                     | CVRCON                                                   | 15:0  | ON    | -     | _     | —     | _     | VREFSEL <sup>(2)</sup> | BGSEL | <1:0> <sup>(2)</sup> | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0100      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX575/675/695/775/795 devices. On these devices, reset value for CVRCON is '0000'.

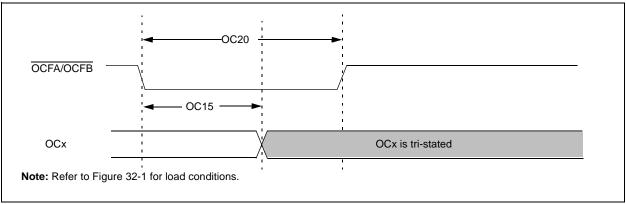

#### FIGURE 32-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 32-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHAF      | RACTERIST                             | rics                          | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |     |       |            |  |  |  |

|--------------|---------------------------------------|-------------------------------|-------------------------------------------------------|------------------------|-----|-------|------------|--|--|--|

| Param<br>No. | Symbol Characteristics <sup>(1)</sup> |                               | Min                                                   | Typical <sup>(2)</sup> | Max | Units | Conditions |  |  |  |

| OC15         | Tfd                                   | Fault Input to PWM I/O Change | —                                                     | —                      | 50  | ns    | _          |  |  |  |

| OC20         | TFLT                                  | Fault Input Pulse Width       | 50                                                    | —                      | _   | ns    | —          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

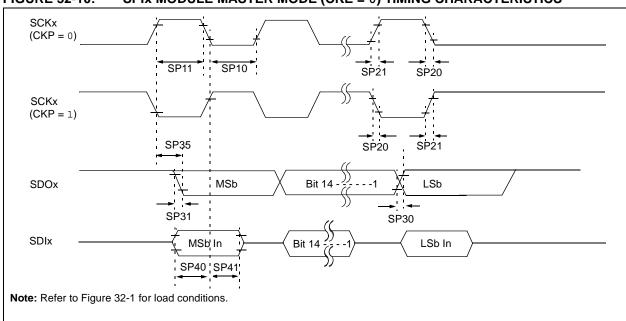

# FIGURE 32-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

#### TABLE 32-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| АС СНА        | ARACTERIST            | TICS                                         | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                        |      |       |                    |  |  |

|---------------|-----------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|--------------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>               | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions         |  |  |

| SP10          | TscL                  | SCKx Output Low Time <sup>(3)</sup>          | Tsck/2                                                                                                                                                                                                                                                                                | _                      | _    | ns    | —                  |  |  |

| SP11          | TscH                  | SCKx Output High Time <sup>(3)</sup>         | Tsck/2                                                                                                                                                                                                                                                                                | _                      |      | ns    | —                  |  |  |

| SP20          | TscF                  | SCKx Output Fall Time <sup>(4)</sup>         | _                                                                                                                                                                                                                                                                                     | _                      |      | ns    | See parameter DO32 |  |  |

| SP21          | TscR                  | SCKx Output Rise Time <sup>(4)</sup>         | -                                                                                                                                                                                                                                                                                     | _                      |      | ns    | See parameter DO31 |  |  |

| SP30          | TDOF                  | SDOx Data Output Fall Time <sup>(4)</sup>    | _                                                                                                                                                                                                                                                                                     | _                      | _    | ns    | See parameter DO32 |  |  |

| SP31          | TDOR                  | SDOx Data Output Rise<br>Time <sup>(4)</sup> | _                                                                                                                                                                                                                                                                                     | —                      | _    | ns    | See parameter DO31 |  |  |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                 | _                                                                                                                                                                                                                                                                                     | —                      | 15   | ns    | VDD > 2.7V         |  |  |

|               | TscL2doV              | SCKx Edge                                    | _                                                                                                                                                                                                                                                                                     | —                      | 20   | ns    | VDD < 2.7V         |  |  |

| SP40          | TDIV2SCH,<br>TDIV2SCL | Setup Time of SDIx Data Input to SCKx Edge   | 10                                                                                                                                                                                                                                                                                    | —                      | _    | ns    | —                  |  |  |

| SP41          | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge    | 10                                                                                                                                                                                                                                                                                    | —                      | —    | ns    | —                  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

4: Assumes 50 pF load on all SPIx pins.

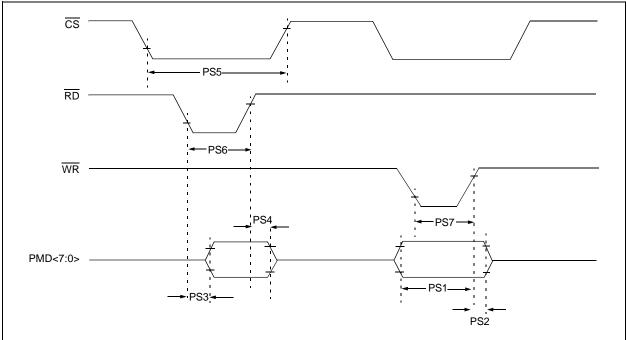

### FIGURE 32-25: PARALLEL SLAVE PORT TIMING

| AC CHA        | RACTERIS | TICS                                                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |      |       |            |  |  |

|---------------|----------|----------------------------------------------------------------------------------|-------------------------------------------------------|---------|------|-------|------------|--|--|

| Param.<br>No. | Symbol   | Characteristics <sup>(1)</sup>                                                   | Min.                                                  | Typical | Max. | Units | Conditions |  |  |

| PS1           | TdtV2wrH | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                    | _       |      | ns    | _          |  |  |

| PS2           | TwrH2dtl | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                    | —       | _    | ns    | —          |  |  |

| PS3           | TrdL2dtV | RD and CS Active to Data-Out<br>Valid                                            | —                                                     | —       | 60   | ns    | —          |  |  |

| PS4           | TrdH2dtl | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                     | —       | 10   | ns    | _          |  |  |

| PS5           | Tcs      | CS Active Time                                                                   | Трв + 40                                              | _       |      | ns    | _          |  |  |

| PS6           | Twr      | WR Active Time                                                                   | Трв + 25                                              | —       | _    | ns    | _          |  |  |

| PS7           | Trd      | RD Active Time                                                                   | Трв + 25                                              | _       | _    | ns    |            |  |  |

#### TABLE 32-39: PARALLEL SLAVE PORT REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

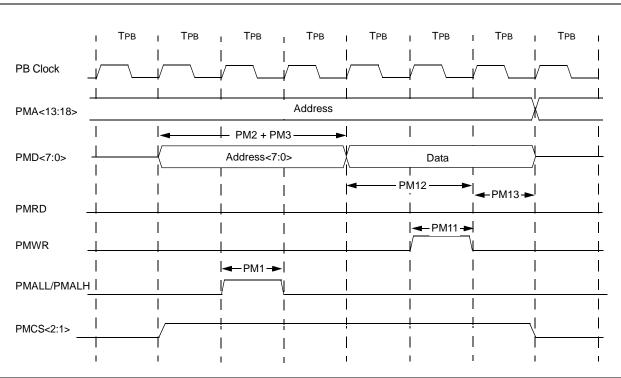

#### FIGURE 32-27: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

### TABLE 32-41: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                                                                     | $\label{eq:constraint} \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |         |      |       |            |  |  |  |

|---------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                                        | Typical | Max. | Units | Conditions |  |  |  |

| PM11          | Twr     | PMWR Pulse Width                                                          | _                                                                                                                                                                                                                                                                                                           | 1 Трв   |      | —     | _          |  |  |  |

| PM12          | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                                                                                                                                                                                                                                                                           | 2 Трв   | _    | —     | _          |  |  |  |

| PM13          | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                                                                                                                                                                                                                                                                           | 1 Трв   |      |       | —          |  |  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

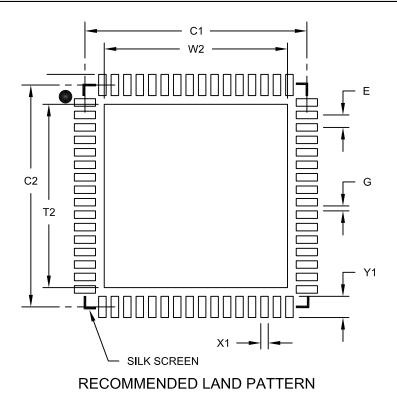

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS      |      |          |      |  |  |

|----------------------------|------------------|------|----------|------|--|--|

| Dimensior                  | Dimension Limits |      |          |      |  |  |

| Contact Pitch              | E                |      | 0.50 BSC |      |  |  |

| Optional Center Pad Width  | W2               |      |          | 7.35 |  |  |

| Optional Center Pad Length | T2               |      |          | 7.35 |  |  |

| Contact Pad Spacing        | C1               |      | 8.90     |      |  |  |

| Contact Pad Spacing        | C2               |      | 8.90     |      |  |  |

| Contact Pad Width (X64)    | X1               |      |          | 0.30 |  |  |

| Contact Pad Length (X64)   | Y1               |      |          | 0.85 |  |  |

| Distance Between Pads      | G                | 0.20 |          |      |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2149A