Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256ht-80i-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES (CONTINUED)

| 1     | 21-PIN TFBGA (BOTTOM VIEW                                                                   | /)         | L11                                         |    |

|-------|---------------------------------------------------------------------------------------------|------------|---------------------------------------------|----|

|       | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |            |                                             | 11 |

| No    | te: The TFBGA package skips from row                                                        | / "H" to r | ow "J" and has no "I" row. A1               |    |

| Pin # | Full Pin Name                                                                               | Pin #      | Full Pin Name                               |    |

| J3    | PGED2/AN7/RB7                                                                               | K8         | VDD                                         |    |

| J4    | AVdd                                                                                        | K9         | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |    |

| J5    | AN11/ERXERR/AETXERR/PMA12/RB11                                                              | K10        | USBID/RF3                                   |    |

| J6    | TCK/RA1                                                                                     | K11        | SDA3/SDI3/U1RX/RF2                          |    |

| J7    | AN12/ERXD0/AECRS/PMA11/RB12                                                                 | L1         | PGEC2/AN6/OCFA/RB6                          |    |

| J8    | No Connect (NC)                                                                             | L2         | VREF-/CVREF-/AERXD2/PMA7/RA9                |    |

| J9    | No Connect (NC)                                                                             | L3         | AVss                                        |    |

| J10   | SCL3/SDO3/U1TX/RF8                                                                          | L4         | AN9/C2OUT/RB9                               |    |

| J11   | D-/RG3                                                                                      | L5         | AN10/CVREFOUT/PMA13/RB10                    |    |

| K1    | PGEC1/AN1/CN3/RB1                                                                           | L6         | SCK4/U5TX/U2RTS/RF13                        |    |

| K2    | PGED1/AN0/CN2/RB0                                                                           | L7         | AN13/ERXD1/AECOL/PMA10/RB13                 |    |

| K3    | VREF+/CVREF+/AERXD3/PMA6/RA10                                                               | L8         | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |    |

| K4    | AN8/C1OUT/RB8                                                                               | L9         | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |    |

| K5    | No Connect (NC)                                                                             | L10        | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |    |

| K6    | SS4/U5RX/U2CTS/RF12                                                                         | L11        | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |    |

| K7    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                                                           |            |                                             |    |

Note 1: Shaded pins are 5V tolerant.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

#### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved.                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved.                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | Ebase                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved.                                                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved.                                                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

|                    | <b>I</b>                |                                                                          |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

## Legend:

| Legena:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

## bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: DRM User Data Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|--------------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0                      | U-0              |

| 31:24        |                   | _                 |                   |                   | _                 |                      | _                        |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0                      | U-0              |

| 23.10        |                   | _                 | _                 | —                 | -                 | _                    | —                        | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                | R/W-0                    | R/W-0            |

| 15:8         | —                 | —                 | —                 | —                 | _                 |                      | RIPL<2:0> <sup>(1)</sup> |                  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0                    | R/W-0            |

| 7:0          |                   | —                 |                   |                   | VEC               | <5:0> <sup>(1)</sup> |                          |                  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

## Legend:

| Legena.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **RIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- **Note 1:** This value should only be used when the interrupt controller is configured for Single-vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | TPTMR<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | TPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | TPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | TPTM              | 1R<7:0>           |                   |                  | •                |  |  |  |  |

#### REGISTER 7-3: TPTMR: TEMPORAL PROXIMITY TIMER REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 TPTMR<31:0>: Temporal Proximity Timer Reload bits

Used by the Temporal Proximity Timer as a reload value when the Temporal Proximity timer is triggered by an interrupt event.

## PIC32MX5XX/6XX/7XX

## REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | —                 | —                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   | —                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | —                 | _                 | —                 | —                 | -                | —                |

| 7:0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7.0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |        |  |

|-------------------|-------------------------|------------------------------------|--------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |        |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared x = Bit is un | nknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

#### bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

- bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

#### bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

## PIC32MX5XX/6XX/7XX

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | -                 | —                        | —                 | _                     | -                     | —                | —                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         |                   |                   | —                        | —                 |                       |                       | —                | —                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | ISTATE            | JSTATE SE0 -      | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNE              |                   | TOKBUSY <sup>(1,5)</sup> | USDKSI            | HUSIEN-               | RESUME                |                  | SOFEN <sup>(5)</sup> |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = JSTATE was not detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-ended zero was detected on the USB

0 = Single-ended zero was not detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

- bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only) 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed) 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit 11 = Reserved 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (has 6 or more data characters) 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (has 4 or more data characters) 00 = Interrupt flag bit is asserted while receive buffer is not empty (has at least 1 data character) **ADDEN:** Address Character Detect bit (bit 8 of received data = 1) bit 5 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect. 0 = Address Detect mode is disabled bit 4 **RIDLE:** Receiver Idle bit (read-only) 1 =Receiver is idle 0 = Data is being received bit 3 PERR: Parity Error Status bit (read-only) 1 = Parity error has been detected for the current character 0 = Parity error has not been detected FERR: Framing Error Status bit (read-only) bit 2 1 = Framing error has been detected for the current character 0 = Framing error has not been detected bit 1 **OERR:** Receive Buffer Overrun Error Status bit. This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to an empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

## TABLE 24-2:CAN2 REGISTER SUMMARY FOR PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX775F512L, PIC32MX775F512L, AND PIC32MX795F512L, DEVICES

| ess                         |                                 |           |          | Bits     |          |            |          |             |           |           |          |          |          |               |           |            |          |          |            |

|-----------------------------|---------------------------------|-----------|----------|----------|----------|------------|----------|-------------|-----------|-----------|----------|----------|----------|---------------|-----------|------------|----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14    | 29/13    | 28/12      | 27/11    | 26/10       | 25/9      | 24/8      | 23/7     | 22/6     | 21/5     | 20/4          | 19/3      | 18/2       | 17/1     | 16/0     | All Resets |

| C000                        | C2CON                           | 31:16     | _        | —        | _        | —          | ABAT     | I           | REQOP<2:0 | >         | 0        | PMOD<2:0 | >        | CANCAP        |           | —          | -        | —        | 0480       |

| 0000                        | CZCON                           | 15:0      | ON       | —        | SIDLE    | —          | CANBUSY  |             | —         | -         | -        |          | -        |               | [         | DNCNT<4:0: | >        |          | 0000       |

| C010                        | C2CFG                           | 31:16     | _        | —        | —        | —          | —        | _           | —         | —         | _        | WAKFIL   | —        | SEG2PH<2:0> 0 |           |            | 0000     |          |            |

| 0010                        | 02010                           | 15:0      | SEG2PHTS | SAM      | S        | SEG1PH<2:0 | )>       |             | PRSEG<2:0 | >         | SJW      | <1:0>    |          |               | BRP       | <5:0>      |          |          | 0000       |

| C020                        | C2INT                           | 31:16     | IVRIE    | WAKIE    | CERRIE   | SERRIE     | RBOVIE   | _           | _         | —         | —        | _        | _        | —             | MODIE     | CTMRIE     | RBIE     | TBIE     | 0000       |

| 0020                        | 021111                          | 15:0      | IVRIF    | WAKIF    | CERRIF   | SERRIF     | RBOVIF   | _           | —         |           |          | _        | —        | _             | MODIF     | CTMRIF     | RBIF     | TBIF     | 0000       |

| C030                        | C2VEC                           | 31:16     | —        | —        | —        | —          | —        | —           | —         | —         | -        | -        | —        | —             | -         | —          | —        | —        | 0000       |

| 0000                        | 02120                           | 15:0      | _        | —        | —        |            |          | FILHIT<4:0: | >         |           | _        |          |          |               | CODE<6:0> | >          |          |          | 0040       |

| C040                        | C2TREC                          | 31:16     | —        | —        | —        | —          | —        | —           | —         | —         | -        | —        | TXBO     | TXBP          | RXBP      | TXWARN     | RXWARN   | EWARN    | 0000       |

| 0010                        |                                 | 15:0      |          | 1        | 1        | -          | CNT<7:0> |             | 1         |           |          |          | 1        | RERRCI        | -         | 1          |          | 1        | 0000       |

| C050                        | C2FSTAT                         | 31:16     | FIFOIP31 | FIFOIP30 | FIFOIP29 | FIFOIP28   | FIFOIP27 | FIFOIP26    | FIFOIP25  | FIFOIP24  | FIFOIP23 | FIFOIP22 | FIFOIP21 | FIFOIP20      | FIFOIP19  | FIFOIP18   | FIFOIP17 | FIFOIP16 | 0000       |

|                             |                                 | 15:0      | FIFOIP15 | FIFOIP14 | FIFOIP13 | FIFOIP12   | FIFOIP11 | FIFOIP10    | FIFOIP9   | FIFOIP8   | FIFOIP7  | FIFOIP6  | FIFOIP5  | FIFOIP4       | FIFOIP3   | FIFOIP2    | FIFOIP1  | FIFOIP0  | 0000       |

| C060                        | C2RXOVF                         | 31:16     | RXOVF31  | RXOVF30  | RXOVF29  | RXOVF28    | RXOVF27  | RXOVF26     | RXOVF25   | RXOVF24   | RXOVF23  | RXOVF22  | RXOVF21  | RXOVF20       | RXOVF19   | RXOVF18    | RXOVF17  | RXOVF16  |            |

|                             |                                 | 15:0      | RXOVF15  | RXOVF14  | RXOVF13  | RXOVF12    | RXOVF11  | RXOVF10     | RXOVF9    | RXOVF8    | RXOVF7   | RXOVF6   | RXOVF5   | RXOVF4        | RXOVF3    | RXOVF2     | RXOVF1   | RXOVF0   |            |

| C070                        | C2TMR                           | 31:16     |          |          |          |            |          |             |           | 0000      |          |          |          |               |           |            |          |          |            |

|                             |                                 | 15:0      |          |          |          |            |          |             | CA        | NTSPRE<15 | 0>       |          |          |               |           |            |          |          | 0000       |

| C080                        | C2RXM0                          | 31:16     |          |          |          |            |          | SID<10:0>   |           |           |          |          |          |               | MIDE      | —          | EID<'    | 17:16>   | XXXX       |

|                             |                                 | 15:0      |          |          |          |            |          |             |           | EID<1     | 5:0>     |          |          |               |           |            |          |          | xxxx       |

| C0A0                        | C2RXM1                          | 31:16     |          |          |          |            |          | SID<10:0>   |           |           |          |          |          |               | MIDE      | —          | EID<'    | 17:16>   | xxxx       |

|                             |                                 | 15:0      |          |          |          |            |          | 015 40.0    |           | EID<1     | 5:0>     |          |          |               |           |            | 510      |          | XXXX       |

| C0B0                        | C2RXM2                          | 31:16     |          |          |          |            |          | SID<10:0>   |           |           |          |          |          |               | MIDE      | —          | EID<'    | 17:16>   | xxxx       |

|                             |                                 | 15:0      |          |          |          |            |          | 010 40.0    |           | EID<1     | 5:0>     |          |          |               | MIDE      |            |          | 7.40     | XXXX       |

| C0B0                        | C2RXM3                          | 31:16     |          |          |          |            |          | SID<10:0>   |           |           |          |          |          |               | MIDE      | _          | EID<     | 17:16>   | XXXX       |

|                             |                                 | 15:0      |          | MODE     | 0.4.0    |            |          |             |           | EID<1     |          | MOL      | 0.4.0    |               |           |            |          |          | xxxx       |

| C0C0                        | C2FLTCON0                       | 31:16     | FLTEN3   | MSEL     |          |            |          | FSEL3<4:0:  |           |           | FLTEN2   | -        | 2<1:0>   |               |           | FSEL2<4:0> |          |          | 0000       |

|                             |                                 | 15:0      | FLTEN1   | MSEL     |          |            |          | FSEL1<4:0:  |           |           | FLTEN0   |          | 0<1:0>   |               |           | FSEL0<4:0> |          |          | 0000       |

| C0D0                        | C2FLTCON1                       | 31:16     | FLTEN7   | MSEL     |          |            |          | FSEL7<4:0:  |           |           | FLTEN6   |          | 6<1:0>   |               |           | FSEL6<4:0> |          |          | 0000       |

|                             |                                 | 15:0      | FLTEN5   | MSEL     |          |            |          | FSEL5<4:0   |           |           | FLTEN4   | MSEL     |          |               |           | FSEL4<4:0> |          |          | 0000       |

| C0E0                        | C2FLTCON2                       | 31:16     | FLTEN11  | -        | 1<1:0>   |            |          | FSEL11<4:0  |           |           | FLTEN10  | MSEL1    |          |               |           | SEL10<4:0  |          |          | 0000       |

|                             |                                 | 15:0      | FLTEN9   |          | 9<1:0>   |            |          | FSEL9<4:0:  |           |           | FLTEN8   | -        | 8<1:0>   |               |           | FSEL8<4:0> |          |          | 0000       |

| C0F0                        | C2FLTCON3                       | 31:16     | FLTEN15  |          | 5<1:0>   |            |          | FSEL15<4:0  |           |           | FLTEN14  | MSEL1    |          |               |           | SEL14<4:0  |          |          | 0000       |

|                             |                                 | 15:0      | FLTEN13  | MSEL1    | 3<1:0>   |            |          | FSEL13<4:0  | >         |           | FLTEN12  | MSEL1    | 2<1:0>   |               | F         | SEL12<4:0  | >        |          | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

## **REGISTER 24-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)

- bit 9 TXHALFIF: FIFO Transmit FIFO Half Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is  $\leq$  half full 0 = FIFO is > half full TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 8 **TXEMPTYIF:** Transmit FIFO Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is empty 0 = FIFO is not empty, at least 1 message queued to be transmitted TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 7-4 Unimplemented: Read as '0' bit 3 **RXOVFLIF:** Receive FIFO Overflow Interrupt Flag bit TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = Overflow event has occurred 0 = No overflow event occured bit 2 **RXFULLIF:** Receive FIFO Full Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is full 0 = FIFO is not full RXHALFIF: Receive FIFO Half Full Interrupt Flag bit<sup>(1)</sup> bit 1 TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is  $\geq$  half full 0 = FIFO is < half full bit 0 **RXNEMPTYIF:** Receive Buffer Not Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is not empty, has at least 1 message 0 = FIFO is empty

- Note 1: This bit is read-only and reflects the status of the FIFO.

#### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1 (CONTINUED)

- bit 7 **AUTOFC:** Automatic Flow Control bit

- 1 = Automatic Flow Control is enabled

- 0 = Automatic Flow Control is disabled

Setting this bit will enable automatic Flow Control. If set, the full and empty watermarks are used to automatically enable and disable the Flow Control, respectively. When the number of received buffers BUFCNT (ETHSTAT<16:23>) rises to the full watermark, Flow Control is automatically enabled. When the BUFCNT falls to the empty watermark, Flow Control is automatically disabled.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 6-5 Unimplemented: Read as '0'

#### bit 4 MANFC: Manual Flow Control bit

- 1 = Manual Flow Control is enabled

- 0 = Manual Flow Control is disabled

Setting this bit will enable manual Flow Control. If set, the Flow Control logic will send a PAUSE frame using the PAUSE timer value in the PTV register. It will then resend a PAUSE frame every 128 \* PTV<15:0>/2 TX clock cycles until the bit is cleared.

**Note:** For 10 Mbps operation, TX clock runs at 2.5 MHz. For 100 Mbps operation, TX clock runs at 25 MHz.

When this bit is cleared, the Flow Control logic will automatically send a PAUSE frame with a 0x0000 PAUSE timer value to disable Flow Control.

This bit is only used for Flow Control operations and affects both TX and RX operations.

#### bit 3-1 Unimplemented: Read as '0'

bit 0 BUFCDEC: Descriptor Buffer Count Decrement bit

The BUFCDEC bit is a write-1 bit that reads as '0'. When written with a '1', the Descriptor Buffer Counter, BUFCNT, will decrement by one. If BUFCNT is incremented by the RX logic at the same time that this bit is written, the BUFCNT value will remain unchanged. Writing a '0' will have no effect.

This bit is only used for RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|------------------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |  |  |

| 23:16        | R/W-0                  | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | BUFCNT<7:0>            |                       |                       |                   |                   |                   |                  |                  |  |  |

| 15:8         | U-0                    | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15.0         | —                      |                       | _                     | _                 | _                 | _                 | _                | _                |  |  |

| 7.0          | R/W-0                  | R/W-0                 | R/W-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | ETHBUSY <sup>(1)</sup> | TXBUSY <sup>(2)</sup> | RXBUSY <sup>(2)</sup> | —                 |                   | _                 |                  | _                |  |  |

## REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER

## Legend:

| Legena.           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-16 **BUFCNT<7:0>:** Packet Buffer Count bits

Number of packet buffers received in memory. Once a packet has been successfully received, this register is incremented by hardware based on the number of descriptors used by the packet. Software decrements the counter (by writing to the BUFCDEC bit (ETHCON1<0>) for each descriptor used) after a packet has been read out of the buffer. The register does not roll over (0xFF to 0x00) when hardware tries to increment the register and the register is already at 0xFF. Conversely, the register does not roll under (0x00 to 0xFF) when software tries to decrement the register and the register is already at 0x000. When software attempts to decrement the same time that the hardware attempts to increment the counter, the counter value will remain unchanged.

When this register value reaches 0xFF, the RX logic will halt (only if automatic Flow Control is enabled) awaiting software to write the BUFCDEC bit in order to decrement the register below 0xFF.

If automatic Flow Control is disabled, the RXDMA will continue processing and the BUFCNT will saturate at a value of 0xFF.

When this register is non-zero, the PKTPEND status bit will be set and an interrupt may be generated, depending on the value of the ETHIEN bit <PKTPENDIE> register.

When the ETHRXST register is written, the BUFCNT counter is automatically cleared to 0x00.

- **Note:** BUFCNT will not be cleared when ON is set to '0'. This enables software to continue to utilize and decrement this count.

- bit 15-8 **Unimplemented:** Read as '0'

- bit 7 ETHBUSY: Ethernet Module busy bit<sup>(1)</sup>

1 = Ethernet logic has been turned on (ON (ETHCON1<15>) = 1) or is completing a transaction 0 = Ethernet logic is idle

This bit indicates that the module has been turned on or is completing a transaction after being turned off.

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2)</sup>

- 1 = TX logic is receiving data

- 0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

### **REGISTER 25-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER (CONTINUED)**

- bit 5 **RXBUSY:** Receive Busy bit<sup>(2)</sup> 1 = RX logic is receiving data

- 0 = RX logic is idle

This bit indicates that a packet is currently being received. A change in this status bit is not necessarily reflected by the RXDONE interrupt, as RX packets may be aborted or rejected by the RX filter.

- bit 4-0 Unimplemented: Read as '0'

- **Note 1:** This bit will be *set* when the ON bit (ETHCON1<15>) = 1.

- **2:** This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE) (CONTINUED)

| DC CHARACT       | ERISTICS                   |            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                     |            |                 |  |

|------------------|----------------------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|-----------------|--|

| Parameter<br>No. | Typical <sup>(2)</sup>     | Max.       | Units                                                                                                                                                                                                                                                                             |                     | Conditions |                 |  |

| Idle Current (li | DLE) <sup>(1)</sup> for PI | C32MX534/5 | 64/664/764 I                                                                                                                                                                                                                                                                      | Family Devices      |            |                 |  |

| DC30a            | 1.5                        | 5          |                                                                                                                                                                                                                                                                                   | -40°C, +25°C, +85°C |            | 4 MHz           |  |

| DC30c            | 3.5                        | 6          | mA                                                                                                                                                                                                                                                                                | +105⁰C              | —          | 4 10172         |  |

| DC31a            | 7                          | 11         |                                                                                                                                                                                                                                                                                   | -40°C, +25°C, +85°C | —          | 25 MHz (Note 3) |  |

| DC32a            | 13                         | 20         | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C | —          | 60 MHz (Note 3) |  |

| DC33a            | 17                         | 25         | - mA                                                                                                                                                                                                                                                                              | -40°C, +25°C, +85°C |            | 80 MHz          |  |

| DC33c            | 20                         | 27         | mA                                                                                                                                                                                                                                                                                | +105°C              | —          | 00 1011 12      |  |

| DC34c            |                            | 40         |                                                                                                                                                                                                                                                                                   | -40°C               |            |                 |  |

| DC34d            |                            | 75         |                                                                                                                                                                                                                                                                                   | +25°C               | 2.3V       |                 |  |

| DC34e            |                            | 800        | μA                                                                                                                                                                                                                                                                                | +85°C               | 2.3V       |                 |  |

| DC34f            |                            | 1000       |                                                                                                                                                                                                                                                                                   | +105°C              |            |                 |  |

| DC35c            | 30                         |            |                                                                                                                                                                                                                                                                                   | -40°C               |            | 1               |  |

| DC35d            | 55                         |            |                                                                                                                                                                                                                                                                                   | +25°C               | 2.21/      | LPRC (31 kHz)   |  |

| DC35e            | 230                        | _          | μA                                                                                                                                                                                                                                                                                | +85°C               | 3.3V       | (Note 3)        |  |

| DC35f            | 800                        |            |                                                                                                                                                                                                                                                                                   | +105°C              |            |                 |  |

| DC36c            |                            | 43         |                                                                                                                                                                                                                                                                                   | -40°C               |            | 1               |  |

| DC36d            |                            | 106        |                                                                                                                                                                                                                                                                                   | +25°C               | 2.01/      |                 |  |

| DC36e            |                            | 800        | μA                                                                                                                                                                                                                                                                                | +85°C               | 3.6V       |                 |  |

| DC36f            |                            | 1000       | 1                                                                                                                                                                                                                                                                                 | +105ºC              |            |                 |  |

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

## TABLE 32-13: COMPARATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                       |                                  | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |      |    |                                                                                        |  |  |

|--------------------|--------|---------------------------------------|----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----|----------------------------------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol | Characteristics                       | Min. Typical Max. Units Comments |                                                                                                                                                                                                                                                                                                    |      |    |                                                                                        |  |  |

| D300               | Vioff  | Input Offset Voltage                  | —                                | ±7.5                                                                                                                                                                                                                                                                                               | ±25  | mV | Avdd = Vdd,<br>Avss = Vss                                                              |  |  |

| D301               | VICM   | Input Common Mode Voltage             | 0                                | _                                                                                                                                                                                                                                                                                                  | Vdd  | V  | Avdd = Vdd,<br>Avss = Vss<br>(Note 2)                                                  |  |  |

| D302               | CMRR   | Common Mode Rejection Ratio           | 55                               | —                                                                                                                                                                                                                                                                                                  | _    | dB | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |  |  |

| D303               | Tresp  | Response Time                         | —                                | 150                                                                                                                                                                                                                                                                                                | 400  | ns | AVDD = VDD,<br>AVss = Vss<br>(Notes 1, 2)                                              |  |  |

| D304               | ON2ov  | Comparator Enabled to Output<br>Valid | —                                |                                                                                                                                                                                                                                                                                                    | 10   | μs | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |  |  |

| D305               | IVref  | Internal Voltage Reference            | 0.57                             | 0.6                                                                                                                                                                                                                                                                                                | 0.63 | V  | For devices without<br>BGSEL<1:0>                                                      |  |  |

|                    |        |                                       | 1.14                             | 1.2                                                                                                                                                                                                                                                                                                | 1.26 | V  | BGSEL<1:0> = 00                                                                        |  |  |

|                    |        |                                       | 0.57                             | 0.6                                                                                                                                                                                                                                                                                                | 0.63 | V  | BGSEL<1:0> = 01                                                                        |  |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

2: These parameters are characterized but not tested.

**3:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

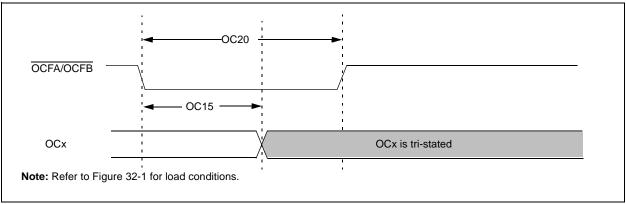

#### FIGURE 32-9: OCx/PWM MODULE TIMING CHARACTERISTICS

#### TABLE 32-27: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                        |     |       |            |  |

|--------------------|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup> | Min                                                                                                                                                                                                                                                                               | Typical <sup>(2)</sup> | Max | Units | Conditions |  |

| OC15               | Tfd    | Fault Input to PWM I/O Change  | —                                                                                                                                                                                                                                                                                 | —                      | 50  | ns    | _          |  |

| OC20               | TFLT   | Fault Input Pulse Width        | 50                                                                                                                                                                                                                                                                                | —                      | _   | ns    | —          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## TABLE 32-31: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                                       | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |                        |      |       |            |  |

|--------------------|----------------------|-------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------------|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup>                        | Min.                                                                                                                                                                                                                                                                                  | Typical <sup>(2)</sup> | Max. | Units | Conditions |  |

| SP51               | TssH2doZ             | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup> | 5                                                                                                                                                                                                                                                                                     | _                      | 25   | ns    | _          |  |

| SP52               | TscH2ssH<br>TscL2ssH | SSx ↑ after SCKx Edge                                 | Тscк +<br>20                                                                                                                                                                                                                                                                          | —                      | _    | ns    | _          |  |

| SP60               | TssL2doV             | SDOx Data Output Valid after<br>SSx Edge              | —                                                                                                                                                                                                                                                                                     | —                      | 25   | ns    | —          |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

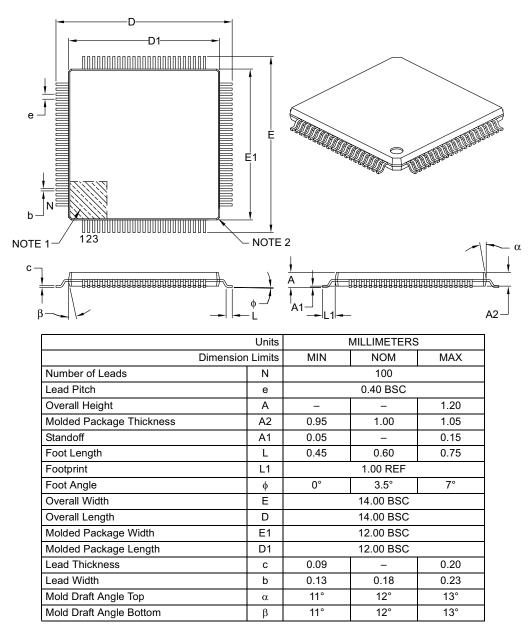

## 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

## PIC32MX5XX/6XX/7XX

| EMAC1SA0 (Ethernet Controller MAC Station Address<br>0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EMAC1SA1 (Ethernet Controller MAC Station Address<br>1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EMAC1SA2 (Ethernet Controller MAC Station Address<br>2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| EMAC1SUPP (Ethernet Controller MAC PHY Support) .<br>313                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| EMAC1TEST (Ethernet Controller MAC Test)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |