Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32 ® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256ht-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES (CONTINUED)

**100-PIN TQFP (TOP VIEW)** PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L 100 1 Pin # **Full Pin Name** Pin # Full Pin Name 71 IC4/PMCS1/PMA14/RD11 86 Vdd 72 SDO1/OC1/INT0/RD0 87 C1RX/PMD11/RF0 SOSCI/CN1/RC13 C1TX/PMD10/RF1 88 73 SOSCO/T1CK/CN0/RC14 74 89 PMD9/RG1 Vss PMD8/RG0 75 90 TRCLK/RA6 76 OC2/RD1 91 77 OC3/RD2 92 TRD3/RA7 78 OC4/RD3 93 PMD0/RE0 PMD1/RE1 79 IC5/PMD12/RD12 94 80 PMD13/CN19/RD13 95 TRD2/RG14 OC5/PMWR/CN13/RD4 96 TRD1/RG12 81 PMRD/CN14/RD5 TRD0/RG13 82 97 PMD14/CN15/RD6 98 PMD2/RE2 83 PMD15/CN16/RD7 PMD3/RE3 84 99 85 VCAP 100 PMD4/RE4

Note 1: Shaded pins are 5V tolerant.

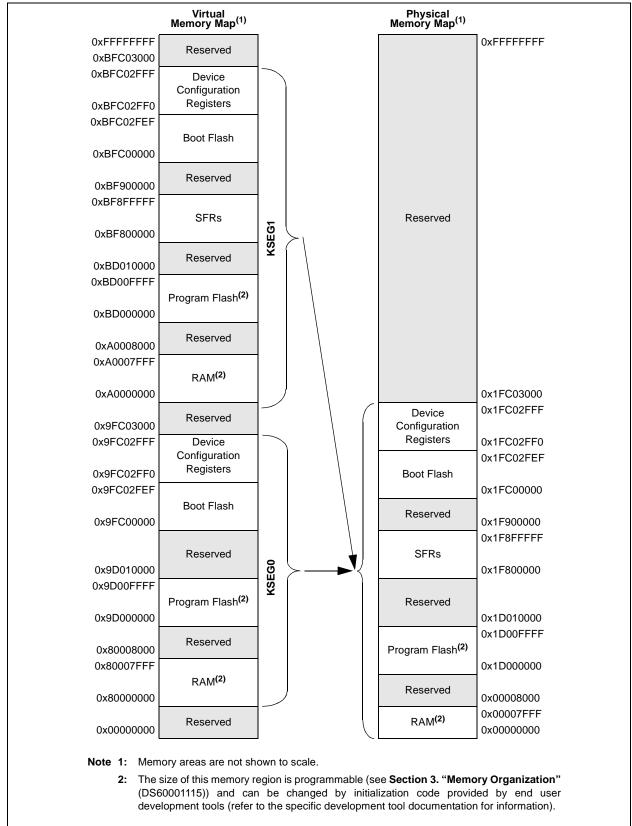

### FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX564F064H, PIC32MX564F064L, PIC32MX664F064H AND PIC32MX664F064L DEVICES

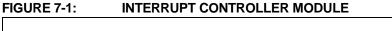

### 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the Even buffer descriptor banks

- 0 = Even/Odd buffer pointers are not reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit(5)

- 1 = SOF token is sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                   | —                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 | —                 | —                 | —                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

#### REGISTER 11-18: U1BDTP2: USB BUFFER DESCRIPTOR TABLE PAGE 2 REGISTER

#### Legend:

| 0                 |                          |                      |                               |  |  |

|-------------------|--------------------------|----------------------|-------------------------------|--|--|

| R = Readable bit  | W = Writable bit U = Uni |                      | nimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared | x = Bit is unknown            |  |  |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

#### REGISTER 11-19: U1BDTP3: USB BUFFER DESCRIPTOR TABLE PAGE 3 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 |                   | —                 |                   |                   | —                | —                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | —                 |                   | —                 |                   |                   | —                | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 10.0         |                   | —                 |                   | —                 |                   |                   | —                | —                |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | BDTPTRU<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

|                             |                                 | PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED) |                      |        |                                                          |       |                     |            |          |           |         |                         |         |       |          |            |             |                |            |

|-----------------------------|---------------------------------|---------------------------------------------------------|----------------------|--------|----------------------------------------------------------|-------|---------------------|------------|----------|-----------|---------|-------------------------|---------|-------|----------|------------|-------------|----------------|------------|

| ess                         |                                 | é                                                       |                      |        |                                                          |       |                     |            |          | Bit       | s       |                         |         |       |          |            |             |                |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                               | 31/15                | 30/14  | 29/13                                                    | 28/12 | 27/11               | 26/10      | 25/9     | 24/8      | 23/7    | 22/6                    | 21/5    | 20/4  | 19/3     | 18/2       | 17/1        | 16/0           | All Resets |

| C100                        | C2FLTCON4                       | 31:16                                                   | FLTEN19              | MSEL1  | 9<1:0>                                                   |       |                     | FSEL19<4:0 | >        |           | FLTEN18 | MSEL1                   | 8<1:0>  |       | F        | SEL18<4:0  | >           |                | 0000       |

| 0100                        | C2FLICON4                       | 15:0                                                    | FLTEN17              | MSEL1  | 7<1:0>                                                   |       |                     | FSEL17<4:0 | >        |           | FLTEN16 | MSEL1                   | 6<1:0>  |       |          | FSEL16<4:0 | ):          |                | 0000       |

| C110                        | C2FLTCON5                       | 31:16                                                   | FLTEN23              | MSEL2  | 3<1:0>                                                   |       |                     | FSEL23<4:0 | >        |           | FLTEN22 | MSEL2                   | 22<1:0> |       | F        | SEL22<4:0  | >           |                | 0000       |

| CIIU                        | CZFLICONS                       | 15:0                                                    | FLTEN21              | MSEL2  | 1<1:0>                                                   |       |                     | FSEL21<4:0 | >        |           | FLTEN20 | MSEL2                   | 20<1:0> |       | F        | SEL20<4:0  | >           |                | 0000       |

| C120                        | C2FLTCON6                       | 31:16                                                   | FLTEN27              | MSEL2  | 7<1:0>                                                   |       |                     | FSEL27<4:0 | >        |           | FLTEN26 | MSEL2                   | 26<1:0> |       | F        | SEL26<4:0  | >           |                | 0000       |

| 0120                        | OZI EI CONO                     | 15:0                                                    | FLTEN25              | MSEL2  | 5<1:0>                                                   |       | FSEL25<4:0> FLTEN24 |            |          |           |         | MSEL24<1:0> FSEL24<4:0> |         |       | 0000     |            |             |                |            |

| C130                        | C2FLTCON7                       | 31:16                                                   | FLTEN31              | MSEL3  | /ISEL31<1:0> FSEL31<4:0> FLTEN30 MSEL30<1:0> FSEL30<4:0> |       |                     |            |          |           |         | 0000                    |         |       |          |            |             |                |            |

| 0100                        |                                 |                                                         | FLTEN29              | MSEL2  | 9<1:0>                                                   |       |                     | FSEL29<4:0 | >        |           | FLTEN28 | MSEL2                   | 28<1:0> |       |          | SEL28<4:0  |             |                | 0000       |

| C140                        | 02.00.11                        | 31:16                                                   |                      |        |                                                          |       |                     | SID<10:0>  |          |           |         |                         |         |       | EXID     | -          | EID<        | 17:16>         | xxxx       |

|                             | (n = 0-31)                      | 15:0                                                    |                      |        |                                                          |       |                     |            |          | EID<1     | 5:0>    |                         |         |       |          |            |             |                | xxxx       |

| C340                        |                                 | 31:16<br>15:0                                           |                      |        |                                                          |       |                     |            |          | C2FIFOB   | A<31:0> |                         |         |       |          |            |             |                | 0000       |

| 0250                        | C2FIFOCONn<br>(n = 0-31)        | 31:16                                                   | _                    | —      | —                                                        | —     | —                   | -          | —        | —         | —       | _                       | —       |       |          | FSIZE<4:0> | <b>&gt;</b> |                | 0000       |

| 0350                        | (n = 0-31)                      | 15:0                                                    |                      | FRESET | UINC                                                     | DONLY |                     | —          | _        |           | TXEN    | TXABAT                  | TXLARB  | TXERR | TXREQ    | RTREN      | TXPR        | l<1:0>         | 0000       |

| C360                        | C2FIFOINTn                      | 31:16                                                   | _                    | —      | —                                                        | —     | _                   | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _       | —                       | -       | _     | RXOVFLIE | RXFULLIE   | RXHALFIE    | RXN<br>EMPTYIE | 0000       |

| 0300                        | (n = 0-31)                      | 15:0                                                    | -                    | —      | —                                                        | -     | -                   | TXNFULLIF  | TXHALFIF | TXEMPTYIF | -       | —                       | -       | -     | RXOVFLIF | RXFULLIF   | RXHALFIF    | RXN<br>EMPTYIF | 0000       |

| C370                        | C2FIFOUAn                       |                                                         | 31:16 C2FIFOUA<31:0> |        |                                                          |       |                     |            |          |           | 0000    |                         |         |       |          |            |             |                |            |

|                             | (n = 0-31)                      | 15:0                                                    |                      |        |                                                          |       |                     |            |          |           |         |                         |         |       |          |            |             |                | 0000       |

| C380                        | C2FIFOCIn<br>(n = 0-31)         | 31:16                                                   |                      | _      | _                                                        | _     | _                   |            | _        | _         | _       | —                       | _       | _     |          |            |             | —              | 0000       |

|                             | (1 = 0.31)                      | 15:0                                                    | —                    | —      | —                                                        | —     | —                   | —          | —        | _         | —       | —                       | —       |       | C        | 2FIFOCI<4: | 0>          |                | 0000       |

## TABLE 24-2: CAN2 REGISTER SUMMARY FOR PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX775F256L, PIC32MX775F512L, AND PIC32MX795F512L, DEVICES (CONTINUED)

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER (CONTINUED)

- bit 14 WAKIF: CAN Bus Activity Wake-up Interrupt Flag bit 1 = A bus wake-up activity interrupt has occurred 0 = A bus wake-up activity interrupt has not occurred CERRIF: CAN Bus Error Interrupt Flag bit bit 13 1 = A CAN bus error has occurred 0 = A CAN bus error has not occurred bit 12 SERRIF: System Error Interrupt Flag bit 1 = A system error occurred (typically an illegal address was presented to the system bus) 0 = A system error has not occurred bit 11 **RBOVIF:** Receive Buffer Overflow Interrupt Flag bit 1 = A receive buffer overflow has occurred 0 = A receive buffer overflow has not occurred bit 10-4 Unimplemented: Read as '0' MODIF: CAN Mode Change Interrupt Flag bit bit 3 1 = A CAN module mode change has occurred (OPMOD<2:0> has changed to reflect REQOP) 0 = A CAN module mode change has not occurred bit 2 CTMRIF: CAN Timer Overflow Interrupt Flag bit 1 = A CAN timer (CANTMR) overflow has occurred 0 = A CAN timer (CANTMR) overflow has not occurred bit 1 **RBIF:** Receive Buffer Interrupt Flag bit 1 = A receive buffer interrupt is pending 0 = A receive buffer interrupt is not pending bit 0 TBIF: Transmit Buffer Interrupt Flag bit 1 = A transmit buffer interrupt is pending

- 1 = A transmit buffer interrupt is pending

0 = A transmit buffer interrupt is not pending

- **Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | —                 | —                       |                   | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                       | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | _                 | _                 |                   |                         | FILHIT<4:0>       |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | l                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

### REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | FLTEN19           | MSEL1             | 9<1:0>            | FSEL19<4:0>       |                   |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN17           | MSEL17<1:0>       |                   |                   | F                 | SEL17<4:0>        | >                |                  |

| 7.0          | R/W-0             | R/W-0 R/W-0       |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN16           | MSEL16<1:0>       |                   | FSEL16<4:0>       |                   |                   |                  |                  |

#### REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 31    | FLTEN19: Filter 19 Enable bit<br>1 = Filter is enabled                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                                                                                              |

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | FSEL19<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | <ul> <li>11111 = Message matching filter is stored in FIFO buffer 31</li> <li>11110 = Message matching filter is stored in FIFO buffer 30</li> <li>•</li> </ul>                     |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

| bit 23    | FLTEN18: Filter 18 Enable bit                                                                                                                                                       |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                                                                                              |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                                                                                                                                             |

|           | <ul> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>      |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                                                                                                                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                                                                                                         |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                                                                                                         |

|           |                                                                                                                                                                                     |

|           | •                                                                                                                                                                                   |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                            |

|           |                                                                                                                                                                                     |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                              |

### REGISTER 24-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5 (CONTINUED)

|           | · · · · · · · · · · · · · · · · · · ·                              |  |

|-----------|--------------------------------------------------------------------|--|

| bit 15    | FLTEN21: Filter 21 Enable bit                                      |  |

|           | 1 = Filter is enabled                                              |  |

|           | 0 = Filter is disabled                                             |  |

| bit 14-13 | MSEL21<1:0>: Filter 21 Mask Select bits                            |  |

|           | 11 = Acceptance Mask 3 selected                                    |  |

|           | 10 = Acceptance Mask 2 selected                                    |  |

|           | 01 = Acceptance Mask 1 selected                                    |  |

|           | 00 = Acceptance Mask 0 selected                                    |  |

| bit 12-8  | FSEL21<4:0>: FIFO Selection bits                                   |  |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |  |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |  |

|           |                                                                    |  |

|           | •                                                                  |  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |  |

| bit 7     | FLTEN20: Filter 20 Enable bit                                      |  |

|           | 1 = Filter is enabled                                              |  |

|           | 0 = Filter is disabled                                             |  |

| bit 6-5   | MSEL20<1:0>: Filter 20 Mask Select bits                            |  |

|           | 11 = Acceptance Mask 3 selected                                    |  |

|           | 10 = Acceptance Mask 2 selected                                    |  |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |  |

| h:+ 4 0   | •                                                                  |  |

| bit 4-0   | FSEL20<4:0>: FIFO Selection bits                                   |  |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |  |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |  |

|           |                                                                    |  |

|           | •                                                                  |  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |  |

|           |                                                                    |  |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        |                   | HT<31:24>         |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | HT<15:8>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | HT<               | 7:0>              |                   |                  |                  |  |  |  |

#### REGISTER 25-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

#### REGISTER 25-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     |                   | HT<63:56>         |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      | HT<47:40>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|           |                   |                   |                   | HT<3              | 9:32>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

The processor will exit, or 'wake-up', from Sleep mode on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep mode. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

#### 28.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- · On any form of device Reset

- On a WDT time-out interrupt

#### 28.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus (PB) can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as USB, interrupt controller, DMA, bus matrix and prefetch cache are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

#### REGISTER 29-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

| DC CHARACT                                                                          | ERISTICS               |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |                     |            |               |  |  |

|-------------------------------------------------------------------------------------|------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|---------------|--|--|

| Parameter<br>No.                                                                    | Typical <sup>(2)</sup> | Max. | Units                                                                                                                                                                                                                                                                             |                     | Conditions |               |  |  |

| Idle Current (IIDLE) <sup>(1,3)</sup> for PIC32MX575/675/695/775/795 Family Devices |                        |      |                                                                                                                                                                                                                                                                                   |                     |            |               |  |  |

| DC30                                                                                | 4.5                    | 6.5  | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C |            | 4 MHz         |  |  |

| DC30b                                                                               | 5                      | 7    | mA                                                                                                                                                                                                                                                                                | +105°C              | —          | 4 MHZ         |  |  |

| DC31                                                                                | 13                     | 15   | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C | —          | 25 MHz        |  |  |

| DC32                                                                                | 28                     | 30   | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C | —          | 60 MHz        |  |  |

| DC33                                                                                | 36                     | 42   | mA                                                                                                                                                                                                                                                                                | -40°C, +25°C, +85°C |            | 80 MHz        |  |  |

| DC33b                                                                               | 39                     | 45   | mA                                                                                                                                                                                                                                                                                | +105°C              | —          |               |  |  |

| DC34                                                                                |                        | 40   |                                                                                                                                                                                                                                                                                   | -40°C               |            |               |  |  |

| DC34a                                                                               |                        | 75   |                                                                                                                                                                                                                                                                                   | +25°C               | 2.3V       |               |  |  |

| DC34b                                                                               |                        | 800  | μA                                                                                                                                                                                                                                                                                | +85°C               | 2.3V       |               |  |  |

| DC34c                                                                               |                        | 1000 |                                                                                                                                                                                                                                                                                   | +105°C              |            |               |  |  |

| DC35                                                                                | 35                     |      |                                                                                                                                                                                                                                                                                   | -40°C               |            |               |  |  |

| DC35a                                                                               | 65                     |      |                                                                                                                                                                                                                                                                                   | +25°C               | 3.3V       | LPRC (31 kHz) |  |  |

| DC35b                                                                               | 600                    | _    | μΑ                                                                                                                                                                                                                                                                                | +85°C               | 3.3V       |               |  |  |

| DC35c                                                                               | 800                    |      |                                                                                                                                                                                                                                                                                   | +105°C              |            |               |  |  |

| DC36                                                                                |                        | 43   |                                                                                                                                                                                                                                                                                   | -40°C               |            |               |  |  |

| DC36a                                                                               |                        | 106  |                                                                                                                                                                                                                                                                                   | +25°C               | 3.6V       |               |  |  |

| DC36b                                                                               |                        | 800  | μA                                                                                                                                                                                                                                                                                | +85°C               | 3.0V       |               |  |  |

| DC36c                                                                               |                        | 1000 |                                                                                                                                                                                                                                                                                   | +105°C              |            |               |  |  |

#### TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

| DC CHA        | RACTERIS               | TICS                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |             |                             |                                                    |  |  |  |  |

|---------------|------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------|----------------------------------------------------|--|--|--|--|

| Param.<br>No. | Typical <sup>(2)</sup> | Max.                      | Units                                                                                                                                                                                                                                                                                 | Conditions  |                             |                                                    |  |  |  |  |

| Power-D       | Oown Curre             | nt (IPD) <sup>(1)</sup> f | or PIC32                                                                                                                                                                                                                                                                              | AX534/564/  | /664/764                    | Family Devices                                     |  |  |  |  |

| DC40g         | 12                     | 40                        |                                                                                                                                                                                                                                                                                       | -40°C       |                             |                                                    |  |  |  |  |

| DC40h         | 20                     | 120                       |                                                                                                                                                                                                                                                                                       | +25°C       | 2.3V                        | Base Power-Down Current (Note 6)                   |  |  |  |  |

| DC40i         | 210                    | 600                       |                                                                                                                                                                                                                                                                                       | +85°C       | 2.30                        | Base Power-Down Current (Note 6)                   |  |  |  |  |

| DC40o         | 400                    | 1000                      |                                                                                                                                                                                                                                                                                       | +105°C      |                             |                                                    |  |  |  |  |

| DC40j         | 20                     | 120                       |                                                                                                                                                                                                                                                                                       | +25°C       | 3.3V                        | Base Power-Down Current                            |  |  |  |  |

| DC40k         | 15                     | 80                        | μA                                                                                                                                                                                                                                                                                    | -40°C       |                             |                                                    |  |  |  |  |

| DC40I         | 20                     | 120                       |                                                                                                                                                                                                                                                                                       | +25°C       |                             |                                                    |  |  |  |  |

| DC40m         | 113                    | 350 <sup>(5)</sup>        |                                                                                                                                                                                                                                                                                       | +70°C       | 3.6V                        | Base Power-Down Current                            |  |  |  |  |

| DC40n         | 220                    | 650                       |                                                                                                                                                                                                                                                                                       | +85°C       |                             |                                                    |  |  |  |  |

| DC40p         | 500                    | 1000                      |                                                                                                                                                                                                                                                                                       | +105°C      |                             |                                                    |  |  |  |  |

| Module        | Differential           | Current fo                | or PIC32N                                                                                                                                                                                                                                                                             | IX534/564/0 | 664/764                     | Family Devices                                     |  |  |  |  |

| DC41c         | _                      | 10                        |                                                                                                                                                                                                                                                                                       |             | 2.5V                        | Watchdog Timer Current: AIWDT (Notes 3,6)          |  |  |  |  |

| DC41d         | 5                      |                           | μA                                                                                                                                                                                                                                                                                    | —           | 3.3V                        | Watchdog Timer Current: AIWDT (Note 3)             |  |  |  |  |

| DC41e         | _                      | 20                        |                                                                                                                                                                                                                                                                                       |             | 3.6V                        | Watchdog Timer Current: ΔIWDT (Note 3)             |  |  |  |  |

| DC42c         | —                      | 40                        |                                                                                                                                                                                                                                                                                       |             | 2.5V                        | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Notes 3,6) |  |  |  |  |

| DC42d         | 23                     | _                         | μA                                                                                                                                                                                                                                                                                    | —           | 3.3V                        | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3)    |  |  |  |  |

| DC42e         | —                      | 50                        |                                                                                                                                                                                                                                                                                       |             | 3.6V                        | RTCC + Timer1 w/32 kHz Crystal: ΔIRTCC (Note 3)    |  |  |  |  |

| DC43c         | —                      | 1300                      |                                                                                                                                                                                                                                                                                       |             | 2.5V                        | ADC: ΔIADC (Notes 3,4,6)                           |  |  |  |  |

| DC43d         | 1100                   |                           | μA                                                                                                                                                                                                                                                                                    | —           | 3.3V                        | ADC: Aladc (Notes 3,4)                             |  |  |  |  |

| DC43e         | _                      | 1300                      |                                                                                                                                                                                                                                                                                       |             | 3.6V ADC: ΔIADC (Notes 3,4) |                                                    |  |  |  |  |

#### TABLE 32-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

Note 1: The test conditions for IPD current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- $\overline{\text{MCLR}} = \text{VDD}$

- RTCC and JTAG are disabled

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: Data is characterized at +70°C and not tested. Parameter is for design guidance only.

- 6: This parameter is characterized, but not tested in manufacturing.

| DC CHA        | RACTER | ISTICS                                                  | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |       |            |    |                                                   |  |

|---------------|--------|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|----|---------------------------------------------------|--|

| Param.<br>No. | Symbol | nbol Characteristics Min. Typical <sup>(1)</sup> Max.   |                                                                                                                                                                                                                                                                                        | Units | Conditions |    |                                                   |  |

|               | VIL    | Input Low Voltage                                       |                                                                                                                                                                                                                                                                                        |       |            |    |                                                   |  |

| DI10          |        | I/O Pins:                                               |                                                                                                                                                                                                                                                                                        |       |            |    |                                                   |  |

|               |        | with TTL Buffer                                         | Vss                                                                                                                                                                                                                                                                                    | —     | 0.15 Vdd   | V  |                                                   |  |

|               |        | with Schmitt Trigger Buffer                             | Vss                                                                                                                                                                                                                                                                                    | —     | 0.2 Vdd    | V  |                                                   |  |

| DI15          |        | MCLR <sup>(2)</sup>                                     | Vss                                                                                                                                                                                                                                                                                    | —     | 0.2 Vdd    | V  |                                                   |  |

| DI16          |        | OSC1 (XT mode)                                          | Vss                                                                                                                                                                                                                                                                                    | —     | 0.2 Vdd    | V  | (Note 4)                                          |  |

| DI17          |        | OSC1 (HS mode)                                          | Vss                                                                                                                                                                                                                                                                                    | —     | 0.2 Vdd    | V  | (Note 4)                                          |  |

| DI18          |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                                                                                                                    | _     | 0.3 Vdd    | V  | SMBus disabled<br>(Note 4)                        |  |

| DI19          |        | SDAx, SCLx                                              | Vss                                                                                                                                                                                                                                                                                    | —     | 0.8        | V  | SMBus enabled<br>(Note 4)                         |  |

|               | Vih    | Input High Voltage                                      |                                                                                                                                                                                                                                                                                        |       |            |    |                                                   |  |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                                                                                                                                                                                                                                                               | —     | Vdd        | V  | (Note 4,6)                                        |  |

|               |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                                                                                                                                                                                                                                                        | _     | 5.5        | V  | (Note 4,6)                                        |  |