Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256ht-80v-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                       |                 | nber <sup>(1)</sup>             |                                                                                                             | Pin                                                                                          | Buffor                                                                                                 |                                                                                                                                                                                                                         |  |

|-----------------------|-----------------|---------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 64-Pin<br>N/TQFP      | 100-Pin<br>TQFP | 121-Pin<br>TFBGA                | 124-pin<br>VTLA                                                                                             | Pin<br>Type                                                                                  | Buffer<br>Type                                                                                         | Description                                                                                                                                                                                                             |  |

| 46                    | 72              | D9                              | B39                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTD is a bidirectional I/O port                                                                                                                                                                                       |  |

| 49                    | 76              | A11                             | A52                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 50                    | 77              | A10                             | B42                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 51                    | 78              | B9                              | A53                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 52                    | 81              | C8                              | B44                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 53                    | 82              | B8                              | A55                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 54                    | 83              | D7                              | B45                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 55                    | 84              | C7                              | A56                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 42                    | 68              | E9                              | B37                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 43                    | 69              | E10                             | A45                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 44                    | 70              | D11                             | B38                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 45                    | 71              | C11                             | A46                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 79              | A9                              | B43                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 80              | D8                              | A54                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 47              | L9                              | B26                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 48              | K9                              | A31                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 60                    | 93              | A4                              | B52                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTE is a bidirectional I/O port                                                                                                                                                                                       |  |

| 61                    | 94              | B4                              | A64                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 62                    | 98              | B3                              | A66                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 63                    | 99              | A2                              | B56                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 64                    | 100             | A1                              | A67                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 1                     | 3               | D3                              | B2                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 2                     | 4               | C1                              | A4                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 3                     | 5               | D2                              | B3                                                                                                          | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 18              | G1                              | A11                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 19              | G2                              | B10                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 58                    | 87              | B6                              | B49                                                                                                         | I/O                                                                                          | ST                                                                                                     | PORTF is a bidirectional I/O port                                                                                                                                                                                       |  |

| 59                    | 88              | A6                              | A60                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 52              | K11                             | A36                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 33                    | 51              | K10                             | A35                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 31                    | 49              | L10                             | B27                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| 32                    | 50              | L11                             | A32                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 53              | J10                             | B29                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 40              | K6                              | A27                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| _                     | 39              | L6                              | B22                                                                                                         | I/O                                                                                          | ST                                                                                                     |                                                                                                                                                                                                                         |  |

| <br><br>S = C<br>Schn | nitt 1          | 53<br>40<br>39<br>CMOS compatib | 53     J10       40     K6       39     L6       CMOS compatible input or contribut Trigger input with CMOS | 53J10B2940K6A2739L6B22CMOS compatible input or output<br>nitt Trigger input with CMOS levels | 53J10B29I/O40K6A27I/O39L6B22I/OCMOS compatible input or output<br>nitt Trigger input with CMOS levelsA | 53     J10     B29     I/O     ST       40     K6     A27     I/O     ST       39     L6     B22     I/O     ST       CMOS compatible input or output nitt Trigger input with CMOS levels     Analog = A     O = Output |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

| AECRS  | 64-Pin<br>QFN/TQFP | 100-Pin                  |                                                      |                                                        | Pin  | Buffer |                                                                                    |

|--------|--------------------|--------------------------|------------------------------------------------------|--------------------------------------------------------|------|--------|------------------------------------------------------------------------------------|

|        |                    | TQFP                     | 121-Pin<br>TFBGA                                     | 124-pin<br>VTLA                                        | Туре | Туре   | Description                                                                        |

|        |                    | 41                       | J7                                                   | B23                                                    | I    | ST     | Alternate Ethernet carrier sense <sup>(2)</sup>                                    |

| AEMDC  | 30                 | 71                       | C11                                                  | A46                                                    | 0    |        | Alternate Ethernet Management Data clock <sup>(2)</sup>                            |

| AEMDIO | 49                 | 68                       | E9                                                   | B37                                                    | I/O  |        | Alternate Ethernet Management Data <sup>(2</sup>                                   |

| TRCLK  | _                  | 91                       | C5                                                   | B51                                                    | 0    |        | Trace clock                                                                        |

| TRD0   |                    | 97                       | A3                                                   | B55                                                    | 0    | _      | Trace Data bits 0-3                                                                |

| TRD1   | _                  | 96                       | C3                                                   | A65                                                    | 0    | _      |                                                                                    |

| TRD2   | _                  | 95                       | C4                                                   | B54                                                    | 0    | _      |                                                                                    |

| TRD3   | _                  | 92                       | B5                                                   | A62                                                    | 0    |        |                                                                                    |

| PGED1  | 16                 | 25                       | K2                                                   | B14                                                    | I/O  | ST     | Data I/O pin for Programming/<br>Debugging Communication Channel 1                 |

| PGEC1  | 15                 | 24                       | K1                                                   | A15                                                    | I    | ST     | Clock input pin for Programming/<br>Debugging Communication Channel 1              |

| PGED2  | 18                 | 27                       | J3                                                   | B16                                                    | I/O  | ST     | Data I/O pin for Programming/<br>Debugging Communication Channel 2                 |

| PGEC2  | 17                 | 26                       | L1                                                   | A20                                                    | Ι    | ST     | Clock input pin for Programming/<br>Debugging Communication Channel 2              |

| MCLR   | 7                  | 13                       | F1                                                   | B7                                                     | I/P  | ST     | Master Clear (Reset) input. This pin is an active-low Reset to the device.         |

| AVdd   | 19                 | 30                       | J4                                                   | A22                                                    | Р    | Р      | Positive supply for analog modules.<br>This pin must be connected at all times     |

| AVss   | 20                 | 31                       | L3                                                   | B18                                                    | Р    | Р      | Ground reference for analog modules                                                |

| Vdd    | 10, 26, 38,<br>57  | 2, 16, 37,<br>46, 62, 86 | A7, C2,<br>C9, E5,<br>K8, F8,<br>G5, H4,<br>H6       | A10, A14,<br>A30, A41,<br>A48, A59,<br>B1, B21,<br>B53 | Ρ    | _      | Positive supply for peripheral logic and I/O pins                                  |

| VCAP   | 56                 | 85                       | B7                                                   | B48                                                    | Р    |        | Capacitor for Internal Voltage Regulato                                            |

| Vss    | 9, 25, 41          | 15, 36, 45,<br>65, 75    | A8, B10,<br>D4, D5,<br>E7, F5,<br>F10, G6,<br>G7, H3 | A3, A25,<br>A43, A63,<br>B8, B12,<br>B25, B41,<br>B46  | Ρ    | _      | Ground reference for logic and I/O pins<br>This pin must be connected at all times |

| Vref+  | 16                 | 29                       | K3                                                   | B17                                                    | I    | Analog | Analog voltage reference (high) input                                              |

| Vref-  | 15                 | 28                       | L2                                                   | A21                                                    | I    | Analog | Analog voltage reference (low) input                                               |

# TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

TTL = TTL input buffer

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# TABLE 7-5: INTERRUPT REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L PIC32MX575F512L AND PIC32MX575F256L DEVICES (CONTINUED)

| ess                         |                                 | â         |       |       |       |       |                            |             |             | В                    | its  |      |      |              |             |             |        |                       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------------------|-------------|-------------|----------------------|------|------|------|--------------|-------------|-------------|--------|-----------------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                      | 26/10       | 25/9        | 24/8                 | 23/7 | 22/6 | 21/5 | 20/4         | 19/3        | 18/2        | 17/1   | 16/0                  | All Resets |

| 10D0                        | IPC4                            | 31:16     | —     | _     | —     |       | INT4IP<2:0>                | <b>`</b>    | INT4IS      | S<1:0>               |      | —    | —    | OC4IP<2:0> 0 |             | OC4I        | S<1:0> | 0000                  |            |

| 1000                        | IFC4                            | 15:0      | -     |       | _     |       | IC4IP<2:0>                 |             | IC4IS       | <1:0>                |      | _    | _    |              | T4IP<2:0>   |             | T4IS   | <1:0>                 | 0000       |

| 4050                        | IDOF                            | 31:16     | Ι     | _     | -     |       | SPI1IP<2:0>                | <b>&gt;</b> | SPI1IS      | S<1:0>               | _    | _    | -    |              | OC5IP<2:0>  |             | OC5I   | S<1:0>                | 0000       |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |       | IC5IP<2:0>                 |             | IC5IS       | <1:0>                |      | _    | _    |              | T5IP<2:0>   |             | T5IS   | <1:0>                 | 0000       |

|                             |                                 | 31:16     | _     | _     | _     |       | AD1IP<2:0>                 |             | AD1IS       | <1:0>                |      | _    | _    |              | CNIP<2:0>   |             | CNIS   | <1:0>                 | 0000       |

| 10F0                        | IPC6                            |           |       |       |       |       |                            |             |             |                      |      |      |      |              | U1IP<2:0>   |             | U1IS   | <1:0>                 |            |

| 10F0                        | IPC6                            | 15:0      | _     | _     | _     |       | I2C1IP<2:0>                | •           | 12C115      | S<1:0>               | _    | _    | —    |              | SPI3IP<2:0> |             | SPI3I  | S<1:0>                | 0000       |

|                             |                                 |           |       |       |       |       |                            |             |             |                      |      |      |      | I2C3IP<2:0>  |             | I2C3IS<1:0> |        |                       |            |

|                             |                                 |           |       |       |       |       | U3IP<2:0>                  |             | U3IS-       | <1:0>                |      |      |      |              |             |             |        |                       |            |

| 1100                        | IPC7                            | 31:16     | _     | —     | —     |       | SPI2IP<2:0>                | <b>`</b>    | SPI2IS      | S<1:0>               | —    | —    | —    |              | CMP2IP<2:0  | >           | CMP2   | S<1:0>                | 0000       |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0>                | •           | 12C415      | S<1:0>               |      |      |      |              |             |             |        |                       |            |

|                             |                                 | 15:0      | —     | —     | —     | (     | CMP1IP<2:0                 | >           | CMP1        | S<1:0>               | _    | _    | —    | PMPIP<2:0>   |             | PMPI        | S<1:0> | 0000                  |            |

|                             |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0                 | >           | RTCCIS<1:0> |                      | _    | _    | —    |              | FSCMIP<2:0  | >           | FSCM   | S<1:0>                | 0000       |

| 1110                        | IPC8                            |           |       |       |       |       |                            |             |             |                      |      |      |      |              | U2IP<2:0>   |             | U2IS   | <1:0>                 |            |

| 1110                        | 11 00                           | 15:0      | -     | —     | -     |       | I2C2IP<2:0>                |             | 12C215      | S<1:0>               | —    | —    | —    |              | SPI4IP<2:0> |             | SPI4I  | S<1:0>                | 0000       |

|                             |                                 |           |       |       |       |       |                            |             |             |                      |      |      |      |              | I2C5IP<2:0> |             | 12C51  | S<1:0>                |            |

| 1120                        | IPC9                            | 31:16     | -     |       | —     | [     | DMA3IP<2:0                 | >           | DMA3I       | S<1:0>               |      | —    | —    |              | DMA2IP<2:0  | >           | DMA2   | S<1:0>                | 0000       |

| 1120                        | 11 00                           | 15:0      | —     | _     | —     |       | DMA1IP<2:0                 |             | DMA1        |                      |      |      | —    |              | DMA0IP<2:0  |             |        | S<1:0>                | 0000       |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     |       | DMA7IP<2:0> <sup>(2)</sup> |             | DMA7IS      | <1:0> <sup>(2)</sup> | _    | _    | —    | D            | MA6IP<2:0>  | (2)         | DMA6IS | 6<1:0> <sup>(2)</sup> | 0000       |

| 1130                        | 1 010                           | 15:0      | _     | —     | —     | D     | DMA5IP<2:0> <sup>(2)</sup> |             | DMA5IS      | <1:0> <sup>(2)</sup> | _    | —    | —    | D            | MA4IP<2:0>  | (2)         | DMA4IS | S<1:0> <sup>(2)</sup> | 0000       |

| 1140                        | IPC11                           | 31:16     | Ι     |       | _     | _     |                            |             | _           | _                    | —    | —    | _    | CAN1IP<2:0>  |             | CAN1        | S<1:0> | 0000                  |            |

| 1140                        | 1011                            | 15:0      | _     | _     | —     |       | USBIP<2:0>                 |             | USBIS       | 5<1:0>               | —    | —    | —    |              | FCEIP<2:0>  |             | FCEIS  | S<1:0>                | 0000       |

| 1150                        | IPC12                           | 31:16     | -     |       | _     |       | U5IP<2:0>                  |             | U5IS-       | <1:0>                | —    | —    | _    |              | U6IP<2:0>   |             | U6IS   | <1:0>                 | 0000       |

| 1150                        | 11 012                          | 15:0      | -     |       | _     |       | U4IP<2:0>                  |             | U4IS-       | <1:0>                | _    | _    | _    | _            | —           |             | —      | _                     | 0000       |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX534/564 devices.

3: This register does not have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | —                 | —                 | _                 | _                 | —                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | —                 | —                 | —                 | _                 | —                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | —                 | _                 | —                 | _                 | —                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

# REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **CHBUSY:** Channel Busy bit 1 = Channel is active or has been enabled 0 = Channel is inactive or has been disabled

- bit 14-9 **Unimplemented:** Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 Chain to channel lower in patteral priority (CH1 will be enabled by C

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

- bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 =Channel is disabled

- bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

#### bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

- 0 = Channel is disabled on block transfer complete

- bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

#### bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- **Note 1:** The chain selection bit takes effect when chaining is enabled (CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

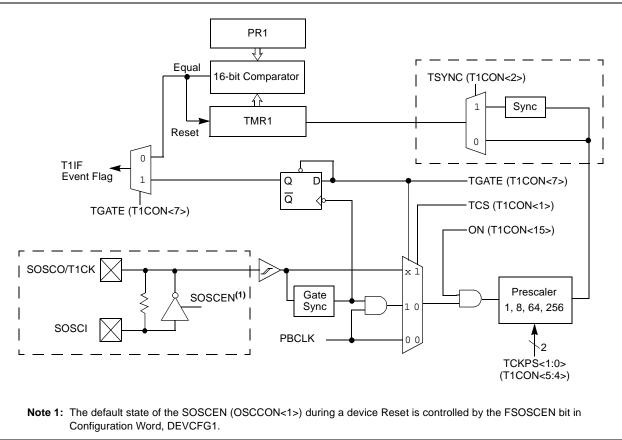

# 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a free-running interval timer for various timing applications and counting external events. This timer can also be used with the low-power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

### FIGURE 13-1: TIMER1 BLOCK DIAGRAM

## 13.1 Additional Supported Features

- Selectable clock prescaler

- Timer operation during Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

A simplified block diagram of the Timer1 module is illustrated in Figure 13-1.

# 15.1 Control Registers

# TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess                      |                                 |           |       | Bits  |       |       |       |       |      |      |      |      |      |           |      | (2)  |      |        |            |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|------|--------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0000                     | WDTOON                          | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | —    | —         | _    | —    | _    | _      | 0000       |

| 0000                     | WDTCON                          | 15:0      | ON    | _     |       | _     | _     | _     | _    | _    | _    |      | S    | WDTPS<4:0 | )>   |      | _    | WDTCLR | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | —                 |                   | _                 | _                 |                   |                  |                  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8      | ON <sup>(1)</sup> | —                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 31-16 | Unimplemented: Read as '0'                                                                                                                                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Input Capture Module Enable bit <sup>(1)</sup>                                                                                                        |

|           | <ul> <li>1 = Module is enabled</li> <li>0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications</li> </ul> |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                |

| bit 13    | SIDL: Stop in Idle Control bit                                                                                                                            |

|           | <ul><li>1 = Halt in Idle mode</li><li>0 = Continue to operate in Idle mode</li></ul>                                                                      |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                |

| bit 9     | FEDGE: First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)                                                                                |

|           | <ul> <li>1 = Capture rising edge first</li> <li>0 = Capture falling edge first</li> </ul>                                                                 |

| bit 8     | C32: 32-bit Capture Select bit                                                                                                                            |

|           | <ul><li>1 = 32-bit timer resource capture</li><li>0 = 16-bit timer resource capture</li></ul>                                                             |

| bit 7     | ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')                                                                     |

|           | <ul> <li>1 = Timer2 is the counter source for capture</li> <li>0 = Timer3 is the counter source for capture</li> </ul>                                    |

| bit 6-5   | ICI<1:0>: Interrupt Control bits                                                                                                                          |

|           | 11 = Interrupt on every fourth capture event                                                                                                              |

|           | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul>                                     |

|           | 00 = Interrupt on every capture event                                                                                                                     |

| bit 4     | ICOV: Input Capture Overflow Status Flag bit (read-only)                                                                                                  |

|           | <ul> <li>1 = Input capture overflow is occurred</li> <li>0 = No input capture overflow is occurred</li> </ul>                                             |

| bit 3     | ICBNE: Input Capture Buffer Not Empty Status bit (read-only)                                                                                              |

|           | <ul> <li>1 = Input capture buffer is not empty; at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>         |

|           |                                                                                                                                                           |

**Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| REGIST    | ER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)                                                                                                                                              |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | <b>ON:</b> SPI Peripheral On bit <sup>(1)</sup>                                                                                                                                                 |

|           | 1 = SPI Peripheral is enabled                                                                                                                                                                   |

| bit 11    | 0 = SPI Peripheral is disabled                                                                                                                                                                  |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 13    | SIDL: Stop in Idle Mode bit<br>1 = Discontinue operation when CPU enters in Idle mode                                                                                                           |

|           | 0 = Continue operation in Idle mode                                                                                                                                                             |

| bit 12    | <b>DISSDO:</b> Disable SDOx pin bit                                                                                                                                                             |

|           | 1 = SDOx pin is not used by the module (pin is controlled by associated PORT register)                                                                                                          |

|           | 0 = SDOx pin is controlled by the module                                                                                                                                                        |

| bit 11-10 | MODE<32,16>: 32/16-Bit Communication Select bits                                                                                                                                                |

|           | MODE32 MODE16 Communication                                                                                                                                                                     |

|           | 1 x 32-bit<br>0 1 16-bit                                                                                                                                                                        |

|           | 0 1 16-bit<br>0 0 8-bit                                                                                                                                                                         |

| bit 9     | SMP: SPI Data Input Sample Phase bit                                                                                                                                                            |

|           | Master mode (MSTEN = 1):                                                                                                                                                                        |

|           | 1 = Input data sampled at end of data output time                                                                                                                                               |

|           | 0 = Input data sampled at middle of data output time                                                                                                                                            |

|           | Slave mode (MSTEN = 0):                                                                                                                                                                         |

|           | SMP value is ignored when SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                            |

| bit 8     | CKE: SPI Clock Edge Select bit <sup>(3)</sup>                                                                                                                                                   |

|           | 1 = Serial output data changes on transition from active clock state to Idle clock state (see CKP bit)                                                                                          |

| h:+ 7     | 0 = Serial output data changes on transition from Idle clock state to active clock state (see CKP bit)                                                                                          |

| bit 7     | SSEN: Slave Select Enable (Slave mode) bit<br>1 = SSx pin used for Slave mode                                                                                                                   |

|           | 0 = SSx pin not used for Slave mode (pin is controlled by port function)                                                                                                                        |

| bit 6     | CKP: Clock Polarity Select bit                                                                                                                                                                  |

|           | 1 = Idle state for clock is a high level; active state is a low level                                                                                                                           |

|           | 0 = Idle state for clock is a low level; active state is a high level                                                                                                                           |

| bit 5     | MSTEN: Master Mode Enable bit                                                                                                                                                                   |

|           | 1 = Master mode<br>0 = Slave mode                                                                                                                                                               |

| bit 4     | Unimplemented: Read as '0'                                                                                                                                                                      |

| bit 3-2   | STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits                                                                                                                                     |

| Dit 0-2   | 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)                                                                                                        |

|           | 10 = Interrupt is generated when the buffer is empty by one-half or more                                                                                                                        |

|           | 01 = Interrupt is generated when the buffer is completely empty                                                                                                                                 |

|           | 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are                                                                                          |

|           | complete                                                                                                                                                                                        |

| bit 1-0   | SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits<br>11 = Interrupt is generated when the buffer is full                                                                                |

|           | 10 = Interrupt is generated when the buffer is full by one-half or more                                                                                                                         |

|           | 01 = Interrupt is generated when the buffer is not empty                                                                                                                                        |

|           | 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)                                                                                            |

|           | When using the 1.1 DPOLK divisor the user's activises should not used anywrite the mentation " OPP i                                                                                            |

| Note 1:   | When using the 1:1 PBCLK divisor, the user's software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. |

| 2:        | This bit can only be written when the ON bit = $0$ .                                                                                                                                            |

| 3:        | This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                         |

| 0.        | mode (FRMEN = 1).                                                                                                                                                                               |

|           |                                                                                                                                                                                                 |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6   | Bit<br>29/21/13/5  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|---------------------|--------------------|-------------------|---------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 31:24        |                   | _                   | _                  |                   | _                   |                   |                  | —                |

| 00.40        | U-0               | U-0                 | U-0                | U-0               | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                   | _                  | -                 | -                   | _                 | _                | —                |

| 45.0         | R/W-0             | U-0                 | R/W-0              | R/W-0             | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | _                   | SIDL               | ADRML             | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0               | R/W-0              | U-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <sup>(2)</sup> | ALP <sup>(2)</sup> | _                 | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

## REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation when device enters Idle mode

#### bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = All 16 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 **PMPTTL:** PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 CSF<1:0>: Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS2 and PMCS1 function as Chip Select

- 01 = PMCS2 functions as Chip Select, PMCS1 functions as address bit 14

- 00 = PMCS2 and PMCS1 function as address bits 15 and  $14^{(2)}$

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 24.24        | U-0                 | U-0                 |

| 31:24        |                   | —                 | —                 |                   | _                 | —                 | —                   | -                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        |                   | —                 | —                 | —                 | _                 | —                 | —                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                 | —                 | F                 | ORM<2:0>            |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           | _                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

#### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- bit 14 Unimplemented: Read as '0'

#### bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 12-11 Unimplemented: Read as '0'

#### bit 10-8 **FORM<2:0>:** Data Output Format bits

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

#### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INT0 pin ends sampling and starts conversion

- 000 = Clearing the SAMP bit ends sampling and starts conversion

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC<2:0> = 000, software can write a '0' to end sampling and start conversion. If SSRC<2:0> ≠ '000', this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when analog-to-digital conversion is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

## REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is } 1 \times TQ

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24        | RXOVF31           | RXOVF30           | RXOVF29           | RXOVF28           | RXOVF27           | RXOVF26           | RXOVF25          | RXOVF24          |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        | RXOVF23           | RXOVF22           | RXOVF21           | RXOVF20           | RXOVF19           | RXOVF18           | RXOVF17          | RXOVF16          |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 10.0         | RXOVF15           | RXOVF14           | RXOVF13           | RXOVF12           | RXOVF11           | RXOVF10           | RXOVF9           | RXOVF8           |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | RXOVF7            | RXOVF6            | RXOVF5            | RXOVF4            | RXOVF3            | RXOVF2            | RXOVF1           | RXOVF0           |

# REGISTER 24-7: CIRXOVF: CAN RECEIVE FIFO OVERFLOW STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 RXOVF<31:0>: FIFOn Receive Overflow Interrupt Pending bit

1 = FIFO has overflowed

0 = FIFO has not overflowed

# REGISTER 24-8: CITMR: CAN TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7                         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0                                     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |