Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | -                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K × 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 121-TFBGA                                                                        |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256l-80i-bg |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

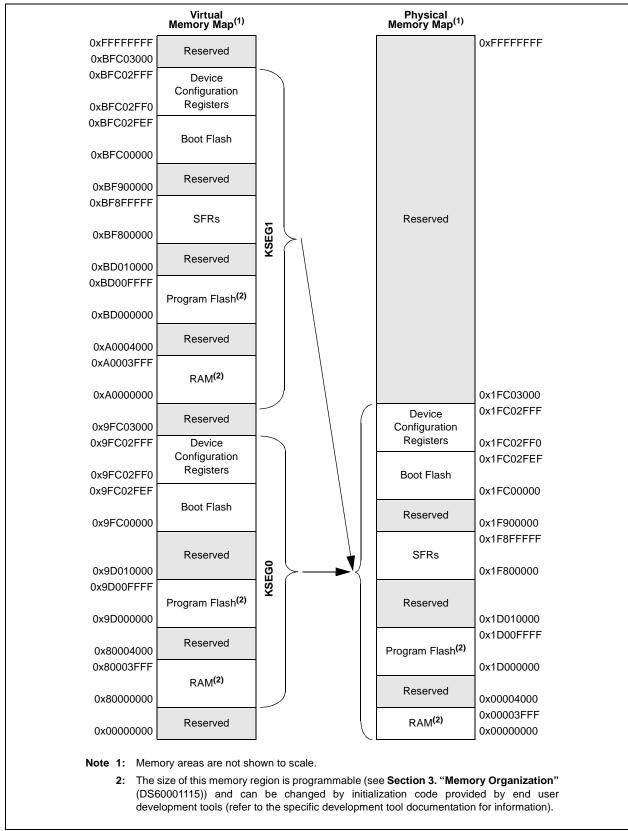

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | —                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | —                 | —                 | _                 | E                 | 3MXARB<2:0       | >                |

## REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

## bit 31-21 **Unimplemented:** Read as '0'

| bit 20   | BMXERRIXI: Enable Bus Error from IXI bit                                                                                                                                                                                              |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus</li> </ul>                 |

| bit 19   | BMXERRICD: Enable Bus Error from ICD Debug Unit bit                                                                                                                                                                                   |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from ICD</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from ICD</li> </ul>                                       |

| bit 18   | BMXERRDMA: Bus Error from DMA bit                                                                                                                                                                                                     |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from DMA</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from DMA</li> </ul>                                       |

| bit 17   | BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)                                                                                                                                                                 |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access</li> </ul>               |

| bit 16   | BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)                                                                                                                                                          |

|          | <ul> <li>1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> <li>0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access</li> </ul> |

| bit 15-7 | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 6    | BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit                                                                                                                                                                 |

|          | <ul> <li>1 = Data RAM accesses from CPU have one wait state for address setup</li> <li>0 = Data RAM accesses from CPU have zero wait states for address setup</li> </ul>                                                              |

| bit 5-3  | Unimplemented: Read as '0'                                                                                                                                                                                                            |

| bit 2-0  | BMXARB<2:0>: Bus Matrix Arbitration Mode bits                                                                                                                                                                                         |

|          | 111 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          |                                                                                                                                                                                                                                       |

|          | •                                                                                                                                                                                                                                     |

|          | 011 = Reserved (using these Configuration modes will produce undefined behavior)                                                                                                                                                      |

|          | 010 = Arbitration Mode 2<br>001 = Arbitration Mode 1 (default)                                                                                                                                                                        |

|          | 000 = Arbitration Mode 0                                                                                                                                                                                                              |

#### 5.1 **Control Registers**

## FLASH CONTROLLER REGISTER MAP

| ess                         |                        |           |       |                  |       |        |         |       |      | Bi          | ts        |      |      |      |      |      |        |      |            |

|-----------------------------|------------------------|-----------|-------|------------------|-------|--------|---------|-------|------|-------------|-----------|------|------|------|------|------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14            | 29/13 | 28/12  | 27/11   | 26/10 | 25/9 | 24/8        | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1   | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     | _     | _                |       | _      | _       |       | —    |             |           |      | —    | _    |      | —    | —      | —    | 0000       |

| F400                        | INVIVICOIN**           | 15:0      | WR    | WREN             | WRERR | LVDERR | LVDSTAT | -     | _    |             |           |      | _    | _    |      | NVMO | P<3:0> |      | 0000       |

| F410                        | NVMKEY                 | 31:16     |       |                  |       |        |         |       |      | NVMKE       | V~31·0>   |      |      |      |      |      |        |      | 0000       |

| 1410                        |                        | 15:0      |       |                  |       |        |         |       |      |             | 1<31.02   |      |      |      |      |      |        |      | 0000       |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                  |       |        |         |       |      | NVMADE      | P-31.0>   |      |      |      |      |      |        |      | 0000       |

| 1 420                       |                        | 15:0      |       |                  |       |        |         |       |      | NVINADL     | //<31.02  |      |      |      |      |      |        |      | 0000       |

| E420                        | NVMDATA                | 31:16     |       |                  |       |        |         |       |      |             | A -21.0   |      |      |      |      |      |        |      | 0000       |

| F430                        | INVIVIDATA             | 15:0      |       | NVMDATA<31:0>    |       |        |         |       |      |             |           |      |      |      |      |      |        |      |            |

| F440                        |                        | 31:16     |       | NVMSRCADDR<31:0> |       |        |         |       |      |             |           |      |      |      |      |      |        |      |            |

| F440                        | ADDR                   | 15:0      |       |                  |       |        |         |       |      | INVIVISICAL | 501451.05 |      |      |      |      |      |        |      | 0000       |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interment Course(1)              | IRQ    | Vector      | Interrupt Bit Location |          |             |              |  |  |  |

|----------------------------------|--------|-------------|------------------------|----------|-------------|--------------|--|--|--|

| Interrupt Source <sup>(1)</sup>  | Number | Number      | Flag                   | Enable   | Priority    | Sub-Priority |  |  |  |

|                                  | Highe  | est Natural | Order Priorit          | y        |             |              |  |  |  |

| CT – Core Timer Interrupt        | 0      | 0           | IFS0<0>                | IEC0<0>  | IPC0<4:2>   | IPC0<1:0>    |  |  |  |

| CS0 – Core Software Interrupt 0  | 1      | 1           | IFS0<1>                | IEC0<1>  | IPC0<12:10> | IPC0<9:8>    |  |  |  |

| CS1 – Core Software Interrupt 1  | 2      | 2           | IFS0<2>                | IEC0<2>  | IPC0<20:18> | IPC0<17:16>  |  |  |  |

| INT0 – External Interrupt 0      | 3      | 3           | IFS0<3>                | IEC0<3>  | IPC0<28:26> | IPC0<25:24>  |  |  |  |

| T1 – Timer1                      | 4      | 4           | IFS0<4>                | IEC0<4>  | IPC1<4:2>   | IPC1<1:0>    |  |  |  |

| IC1 – Input Capture 1            | 5      | 5           | IFS0<5>                | IEC0<5>  | IPC1<12:10> | IPC1<9:8>    |  |  |  |

| OC1 – Output Compare 1           | 6      | 6           | IFS0<6>                | IEC0<6>  | IPC1<20:18> | IPC1<17:16>  |  |  |  |

| INT1 – External Interrupt 1      | 7      | 7           | IFS0<7>                | IEC0<7>  | IPC1<28:26> | IPC1<25:24>  |  |  |  |

| T2 – Timer2                      | 8      | 8           | IFS0<8>                | IEC0<8>  | IPC2<4:2>   | IPC2<1:0>    |  |  |  |

| IC2 – Input Capture 2            | 9      | 9           | IFS0<9>                | IEC0<9>  | IPC2<12:10> | IPC2<9:8>    |  |  |  |

| OC2 – Output Compare 2           | 10     | 10          | IFS0<10>               | IEC0<10> | IPC2<20:18> | IPC2<17:16>  |  |  |  |

| INT2 – External Interrupt 2      | 11     | 11          | IFS0<11>               | IEC0<11> | IPC2<28:26> | IPC2<25:24>  |  |  |  |

| T3 – Timer3                      | 12     | 12          | IFS0<12>               | IEC0<12> | IPC3<4:2>   | IPC3<1:0>    |  |  |  |

| IC3 – Input Capture 3            | 13     | 13          | IFS0<13>               | IEC0<13> | IPC3<12:10> | IPC3<9:8>    |  |  |  |

| OC3 – Output Compare 3           | 14     | 14          | IFS0<14>               | IEC0<14> | IPC3<20:18> | IPC3<17:16>  |  |  |  |

| INT3 – External Interrupt 3      | 15     | 15          | IFS0<15>               | IEC0<15> | IPC3<28:26> | IPC3<25:24>  |  |  |  |

| T4 – Timer4                      | 16     | 16          | IFS0<16>               | IEC0<16> | IPC4<4:2>   | IPC4<1:0>    |  |  |  |

| IC4 – Input Capture 4            | 17     | 17          | IFS0<17>               | IEC0<17> | IPC4<12:10> | IPC4<9:8>    |  |  |  |

| OC4 – Output Compare 4           | 18     | 18          | IFS0<18>               | IEC0<18> | IPC4<20:18> | IPC4<17:16>  |  |  |  |

| INT4 – External Interrupt 4      | 19     | 19          | IFS0<19>               | IEC0<19> | IPC4<28:26> | IPC4<25:24>  |  |  |  |

| T5 – Timer5                      | 20     | 20          | IFS0<20>               | IEC0<20> | IPC5<4:2>   | IPC5<1:0>    |  |  |  |

| IC5 – Input Capture 5            | 21     | 21          | IFS0<21>               | IEC0<21> | IPC5<12:10> | IPC5<9:8>    |  |  |  |

| OC5 – Output Compare 5           | 22     | 22          | IFS0<22>               | IEC0<22> | IPC5<20:18> | IPC5<17:16>  |  |  |  |

| SPI1E – SPI1 Fault               | 23     | 23          | IFS0<23>               | IEC0<23> | IPC5<28:26> | IPC5<25:24>  |  |  |  |

| SPI1RX – SPI1 Receive Done       | 24     | 23          | IFS0<24>               | IEC0<24> | IPC5<28:26> | IPC5<25:24>  |  |  |  |

| SPI1TX – SPI1 Transfer Done      | 25     | 23          | IFS0<25>               | IEC0<25> | IPC5<28:26> | IPC5<25:24>  |  |  |  |

| U1E – UART1 Error                |        |             |                        |          |             |              |  |  |  |

| SPI3E – SPI3 Fault               | 26     | 24          | IFS0<26>               | IEC0<26> | IPC6<4:2>   | IPC6<1:0>    |  |  |  |

| I2C3B – I2C3 Bus Collision Event |        |             |                        |          |             |              |  |  |  |

| U1RX – UART1 Receiver            |        |             |                        |          |             |              |  |  |  |

| SPI3RX – SPI3 Receive Done       | 27     | 24          | IFS0<27>               | IEC0<27> | IPC6<4:2>   | IPC6<1:0>    |  |  |  |

| I2C3S - I2C3 Slave Event         |        |             |                        |          |             |              |  |  |  |

| U1TX – UART1 Transmitter         |        |             |                        |          |             |              |  |  |  |

| SPI3TX – SPI3 Transfer Done      | 28     | 24          | IFS0<28>               | IEC0<28> | IPC6<4:2>   | IPC6<1:0>    |  |  |  |

| I2C3M – I2C3 Master Event        | 1      |             |                        |          |             |              |  |  |  |

| I2C1B – I2C1 Bus Collision Event | 29     | 25          | IFS0<29>               | IEC0<29> | IPC6<12:10> | IPC6<9:8>    |  |  |  |

| I2C1S – I2C1 Slave Event         | 30     | 25          | IFS0<30>               | IEC0<30> | IPC6<12:10> | IPC6<9:8>    |  |  |  |

| I2C1M – I2C1 Master Event        | 31     | 25          | IFS0<31>               | IEC0<31> | IPC6<12:10> | IPC6<9:8>    |  |  |  |

| CN – Input Change Interrupt      | 32     | 26          | IFS1<0>                | IEC1<0>  | IPC6<20:18> | IPC6<17:16>  |  |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

|                             |                                 | P             | IC32M)  | <b>(795F5</b> 1 | 12L DEV | /ICES                         |                               |                               |                               |                             |                               |                               |                             |                       |                         |        |               |        |            |

|-----------------------------|---------------------------------|---------------|---------|-----------------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|-------------------------|--------|---------------|--------|------------|

| SS                          |                                 |               |         |                 |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |                         |        |               |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14           | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3                    | 18/2   | 17/1          | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _       | _               | —       | _                             | _                             | -                             | —                             | _                           | _                             | —                             | —                           | _                     |                         | —      | —             | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | _       | -               | —       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | —                             | _                           | INT4EP                | INT3EP                  | INT2EP | INT1EP        | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         |         | —               | _       | —                             | _                             | _                             | —                             | —                           | _                             | _                             | —                           |                       | —                       | —      | —             |        | 0000       |

|                             |                                 | 15:0          | _       | _               | —       | —                             | —                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC                     | <5:0>  |               |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |         |                 |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |                         |        |               |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF | I2C1SIF         | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | SPI1TXIF                      | SPI1RXIF                    | SPI1EIF                       | OC5IF                         | IC5IF                       | T5IF                  | INT4IF                  | OC4IF  | IC4IF         | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF  | OC3IF           | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | INT0IF                  | CS1IF  | CS0IF         | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF  | IC2EIF          | IC1EIF  | ETHIF                         | CAN2IF <sup>(2)</sup>         | CAN1IF                        | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF                  | DMA2IF | DMA1IF        | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF  | FSCMIF          | I2C2MIF | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF                  | PMPIF  | AD1IF         | CNIF   | 0000       |

|                             |                                 | 31:16         | _       | _               | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1050                        | IFS2                            | 15:0          |         | _               | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF                   | PMPEIF | IC5EIF        | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE | I2C1SIE         | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | SPI1TXIE                      | SPI1RXIE                    | SPI1EIE                       | OC5IE                         | IC5IE                       | T5IE                  | INT4IE                  | OC4IE  | IC4IE         | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE  | OC3IE           | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE                  | CS1IE  | CS0IE         | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE  | IC2EIE          | IC1EIE  | ETHIE                         | CAN2IE <sup>(2)</sup>         | CAN1IE                        | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | DMA3IE                  | DMA2IE | DMA1IE        | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE  | FSCMIE          | I2C2MIE | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE                  | PMPIE  | AD1IE         | CNIE   | 0000       |

|                             | 1500                            | 31:16         | _       | _               | _       | _                             | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     | _                       | _      | _             | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _       | —               | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE                   | PMPEIE | IC5EIE        | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         |         | _               | —       |                               | INT0IP<2:0>                   |                               | INTOIS                        | S<1:0>                      | _                             | —                             | —                           |                       | CS1IP<2:0>              | >      | CS1IS         | S<1:0> | 0000       |

| 1090                        | IFCU                            | 15:0          | —       | —               | —       |                               | CS0IP<2:0>                    |                               | CSOIS                         | 5<1:0>                      | —                             | —                             | —                           |                       | CTIP<2:0>               |        | CTIS          | <1:0>  | 0000       |

| 10A0                        | IPC1                            | 31:16         |         | —               |         |                               | INT1IP<2:0>                   |                               | INT1IS                        |                             | —                             |                               | —                           |                       | OC1IP<2:0>              | >      | OC1IS         |        | 0000       |

|                             |                                 | 15:0          |         | —               | —       |                               | IC1IP<2:0>                    |                               | IC1IS                         |                             | _                             | —                             | —                           |                       | T1IP<2:0>               |        | T1IS          |        | 0000       |

| 10B0                        | IPC2                            | 31:16         |         | —               |         |                               | INT2IP<2:0>                   |                               | INT2IS                        |                             | _                             |                               | —                           |                       | OC2IP<2:0>              | >      | OC2IS         |        | 0000       |

|                             |                                 | 15:0          | _       | _               | _       |                               | IC2IP<2:0>                    |                               | IC2IS                         |                             | _                             | _                             | _                           |                       | T2IP<2:0>               |        | T2IS          |        | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 |         |                 | _       |                               | INT3IP<2:0><br>IC3IP<2:0>     |                               | INT3IS<br>IC3IS               |                             |                               |                               |                             |                       | OC3IP<2:0><br>T3IP<2:0> | >      | OC3IS<br>T3IS |        | 0000       |

| í                           |                                 | 15.0          |         |                 |         |                               | 10315 <2.0>                   |                               | 10313                         | <1.U2                       |                               |                               | _                           |                       | 1015 <2.0>              |        | 1313          | <1.02  | 0000       |

## TABLE 7-7:INTERRUPT REGISTER MAP FOR PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND<br/>PIC32MX795F512L DEVICES

**d:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

PIC32MX5XX/6XX/7XX

2: This bit is unimplemented on PIC32MX764F128L device.

3: This register does not have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW1-            | <15:8>            |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 7:0          |                   | •                 | •                 | CHEW1             | <7:0>             |                   |                  | •                |  |  |  |  |  |

## REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW2<            | :31:24>           |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 23:16        |                   | CHEW2<23:16>      |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW2             | <15:8>            |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 7:0          | CHEW2<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

x = Bit is unknown

|              |                   |                   | •••••••           |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   |                   |                   | CHEHIT<           | :31:24>           |                   |                  |                  |  |  |  |  |

| 00:40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        |                   | CHEHIT<23:16>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         |                   |                   |                   | CHEHIT            | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          |                   |                   |                   | CHEHIT            | <7:0>             |                   |                  |                  |  |  |  |  |

| 1            |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| R = Rea      | dable bit         |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ad as '0'        |                  |  |  |  |  |

## **REGISTER 9-10: CHEHIT: CACHE HIT STATISTICS REGISTER**

### bit 31-0 CHEHIT<31:0>: Cache Hit Count bits

- - - - -

-n = Value at POR

Incremented each time the processor issues an instruction fetch or load that hits the prefetch cache from a cacheable region. Non-cacheable accesses do not modify this value.

-----

'0' = Bit is cleared

| REGIST | ER 9-11: 0 | CHEMIS: CA | CHE MISS | STATISTICS | 6 REGISTEI | ĸ |

|--------|------------|------------|----------|------------|------------|---|

| _      |            |            |          |            |            |   |

'1' = Bit is set

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   |                   |                   | CHEMIS<           | <31:24>                                 |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEMIS<23:16>     |                   |                   |                   |                                         |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEMIS<15:8>      |                   |                   |                   |                                         |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | CHEMIS<7:0>       |                   |                   |                   |                                         |                   |                  |                  |  |  |

|              |                   |                   |                   |                   |                                         |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                                         |                   |                  |                  |  |  |

| R = Rea      | dable bit         |                   | W = Writable bit  |                   | U = Unimplemented bit, read as '0'      |                   |                  |                  |  |  |

| -n = Valu    | le at POR         |                   | '1' = Bit is set  |                   | '0' = Bit is cleared x = Bit is unknown |                   |                  | known            |  |  |

#### bit 31-0 CHEMIS<31:0>: Cache Miss Count bits

Incremented each time the processor issues an instruction fetch from a cacheable region that misses the prefetch cache. Non-cacheable accesses do not modify this value.

## REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | _                 | —                 | —                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   | —                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | —                 | _                 | —                 | —                 | -                | —                |

| 7:0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7.0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          |                  | VBUSVDIF         |

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |        |

|-------------------|-------------------------|------------------------------------|--------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |        |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared x = Bit is un | nknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state detected

- 0 = No change in ID state detected

## bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

- bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1 ms, but different from last time

- 0 = USB line state has not been stable for 1 ms

### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

## bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

## bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input detected

- 0 = No change on the session valid input detected

## REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

- For Slave modes and Master mode 2 (PMMODE<9:8> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (PMMODE<9:8> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

|              |                         | -                    | -                  |                         |                           |                   |                  |                  |  |  |

|--------------|-------------------------|----------------------|--------------------|-------------------------|---------------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3         | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | U-0                     | U-0                  | U-0                | U-0                     | U-0                       | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                       | —                    | —                  | —                       | _                         | —                 | _                | —                |  |  |

| 23:16        | U-0                     | U-0                  | U-0                | U-0                     | U-0                       | U-0               | U-0              | U-0              |  |  |

| 23.10        | —                       | —                    | —                  | —                       | _                         | —                 | _                | —                |  |  |

| 45.0         | R/W-0                   | R/W-0                | R/W-0              | R-0                     | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |  |

| 7.0          | R/W-0                   | R/W-0                | R/W-0              | R/W-0                   | R/W-0                     | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                         |                      |                    | ARPT<7:0                | > <sup>(2)</sup>          |                   |                  |                  |  |  |

## REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 **CHIME:** Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(3)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read.

The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

1111 = Reserved

- 1010 = Reserved

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half-second

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0 > = 0.0 and CHIME = 0.

- **2:** This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is only reset on a Power-on Reset (POR).

## REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is 1 x Tq}

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

## REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3 (CONTINUED)

|                                       | · · · · · · · · · · · · · · · · · · ·                       |

|---------------------------------------|-------------------------------------------------------------|

| bit 15                                | FLTEN13: Filter 13 Enable bit                               |

|                                       | 1 = Filter is enabled                                       |

|                                       | 0 = Filter is disabled                                      |

| bit 14-13                             | MSEL13<1:0>: Filter 13 Mask Select bits                     |

|                                       | 11 = Acceptance Mask 3 selected                             |

|                                       | 10 = Acceptance Mask 2 selected                             |

|                                       | 01 = Acceptance Mask 1 selected                             |

|                                       | 00 = Acceptance Mask 0 selected                             |

| bit 12-8                              | FSEL13<4:0>: FIFO Selection bits                            |

|                                       | 11111 = Message matching filter is stored in FIFO buffer 31 |

|                                       | 11110 = Message matching filter is stored in FIFO buffer 30 |

|                                       | •                                                           |

|                                       | •                                                           |

|                                       | 00001 = Message matching filter is stored in FIFO buffer 1  |

|                                       | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7                                 | FLTEN12: Filter 12 Enable bit                               |

|                                       | 1 = Filter is enabled                                       |

|                                       | 0 = Filter is disabled                                      |

| bit 6-5                               | MSEL12<1:0>: Filter 12 Mask Select bits                     |

|                                       | 11 = Acceptance Mask 3 selected                             |

|                                       | 10 = Acceptance Mask 2 selected                             |

|                                       | 01 = Acceptance Mask 1 selected                             |

|                                       | 00 = Acceptance Mask 0 selected                             |

| bit 4-0                               | FSEL12<4:0>: FIFO Selection bits                            |

|                                       | 11111 = Message matching filter is stored in FIFO buffer 31 |

|                                       | 11110 = Message matching filter is stored in FIFO buffer 30 |

|                                       | •                                                           |

|                                       |                                                             |

|                                       | 00001 = Message matching filter is stored in FIFO buffer 1  |

|                                       | 00000 = Message matching filter is stored in FIFO buffer 0  |

|                                       |                                                             |

| · · · · · · · · · · · · · · · · · · · |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 25-19: ETHMCOLFRM: ETHERNET CONTROLLER MULTIPLE COLLISION FRAMES STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 0.61         | MCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | MCOLFRM           | CNT<7:0>          |                   |                  |                  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **MCOLFRMCNT<15:0>:** Multiple Collision Frame Count bits Increment count for frames that were successfully transmitted after there was more than one collision.

**Note 1:** This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

## REGISTER 25-26: EMAC1IPGR: ETHERNET CONTROLLER MAC NON-BACK-TO-BACK INTERPACKET GAP REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   |                   |                   |                   |                   |                   | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        |                   |                   |                   |                   |                   |                   | —                | —                |  |

| 15:8         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1             | R/W-0            | R/W-0            |  |

| 10.0         | —                 | NB2BIPKTGP1<6:0>  |                   |                   |                   |                   |                  |                  |  |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |  |

| 7.0          |                   |                   |                   | NB2E              | BIPKTGP2<6:       | 0>                |                  |                  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-15 Unimplemented: Read as '0'

## bit 14-8 NB2BIPKTGP1<6:0>: Non-Back-to-Back Interpacket Gap Part 1 bits

This is a programmable field representing the optional carrierSense window referenced in section 4.2.3.2.1 "Deference" of the IEEE 80.23 Specification. If the carrier is detected during the timing of IPGR1, the MAC defers to the carrier. If, however, the carrier comes after IPGR1, the MAC continues timing IPGR2 and transmits, knowingly causing a collision, thus ensuring fair access to the medium. Its range of values is 0x0 to IPGR2. Its recommend value is 0xC (12d).

#### bit 7 Unimplemented: Read as '0'

## bit 6-0 NB2BIPKTGP2<6:0>: Non-Back-to-Back Interpacket Gap Part 2 bits

This is a programmable field representing the non-back-to-back Inter-Packet-Gap. Its recommended value is 0x12 (18d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps).

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## REGISTER 25-31: EMAC1MCFG: ETHERNET CONTROLLER MAC MII MANAGEMENT CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 51.24        | —                 | —                 | _                 | _                 | _                     | _                 |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 15:8         | R/W-0             | U-0               | U-0               | U-0               | U-0                   | U-0               | U-0              | U-0              |

| 15.0         | RESETMGMT         | —                 | —                 | —                 | —                     | —                 | _                | —                |

| 7:0          | U-0               | U-0               | R/W-1             | R/W-0             | R/W-0                 | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   | —                 |                   | CLKSEL            | _<3:0> <sup>(1)</sup> |                   | NOPRE            | SCANINC          |

#### Legend:

| - 5               |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 RESETMGMT: Test Reset MII Management bit

- 1 = Reset the MII Management module

- 0 = Normal Operation

## bit 14-6 **Unimplemented:** Read as '0'

bit 5-2 CLKSEL<3:0>: MII Management Clock Select 1 bits<sup>(1)</sup>

These bits are used by the clock divide logic in creating the MII Management Clock (MDC), which the IEEE 802.3 Specification defines to be no faster than 2.5 MHz. Some PHYs support clock rates up to 12.5 MHz.

## bit 1 NOPRE: Suppress Preamble bit

- 1 = The MII Management will perform read/write cycles without the 32-bit preamble field. Some PHYs support suppressed preamble

- 0 = Normal read/write cycles are performed

## bit 0 SCANINC: Scan Increment bit

- 1 = The MII Management module will perform read cycles across a range of PHYs. The read cycles will start from address 1 through the value set in EMAC1MADR<PHYADDR>

- 0 = Continuous reads of the same PHY

- Note 1: Table 25-7 provides a description of the clock divider encoding.

| Note: | Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). |

|-------|------------------------------------------------------------------------------------------------------------|

|       | 8-bit accesses are not allowed and are ignored by the hardware.                                            |

## TABLE 25-7: MIIM CLOCK SELECTION

| MIIM Clock Select    | EMAC1MCFG<5:2>        |

|----------------------|-----------------------|

| SYSCLK divided by 4  | 000x                  |

| SYSCLK divided by 6  | 0010                  |

| SYSCLK divided by 8  | 0011                  |

| SYSCLK divided by 10 | 0100                  |

| SYSCLK divided by 14 | 0101                  |

| SYSCLK divided by 20 | 0110                  |

| SYSCLK divided by 28 | 0111                  |

| SYSCLK divided by 40 | 1000                  |

| Undefined            | Any other combination |

| DC CHARACT       | ERISTICS                     |            | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |       |               |  |

|------------------|------------------------------|------------|-------------------------------------------------------|---------------------|-------|---------------|--|

| Parameter<br>No. | Typical <sup>(2)</sup>       | Max.       | Units                                                 | Conditions          |       |               |  |

| Idle Current (I  | IDLE) <sup>(1,3)</sup> for P | PIC32MX575 | /675/695/775                                          | 795 Family Devices  |       |               |  |

| DC30             | 4.5                          | 6.5        | mA                                                    | -40°C, +25°C, +85°C |       | 4 MHz         |  |

| DC30b            | 5                            | 7          | mA                                                    | +105°C              | —     | 4 MHZ         |  |

| DC31             | 13                           | 15         | mA                                                    | -40°C, +25°C, +85°C | —     | 25 MHz        |  |

| DC32             | 28                           | 30         | mA                                                    | -40°C, +25°C, +85°C | —     | 60 MHz        |  |

| DC33             | 36                           | 42         | mA                                                    | -40°C, +25°C, +85°C |       | 80 MHz        |  |

| DC33b            | 39                           | 45         | mA                                                    | +105°C              | —     |               |  |

| DC34             |                              | 40         |                                                       | -40°C               |       |               |  |

| DC34a            |                              | 75         |                                                       | +25°C               | 2.3V  |               |  |

| DC34b            |                              | _          | 800                                                   | μA                  | +85°C | 2.3V          |  |

| DC34c            |                              | 1000       | ]                                                     | +105°C              |       |               |  |

| DC35             | 35                           |            |                                                       | -40°C               |       |               |  |

| DC35a            | 65                           |            |                                                       | +25°C               | 3.3V  | LPRC (31 kHz) |  |

| DC35b            | 600                          | _          | μA                                                    | +85°C               | 3.3V  |               |  |

| DC35c            | 800                          |            |                                                       | +105°C              |       |               |  |

| DC36             |                              | 43         |                                                       | -40°C               |       |               |  |

| DC36a            |                              | 106        |                                                       | +25°C               | 3.6V  |               |  |

| DC36b            |                              | 800        | μA                                                    | +85°C               | 3.0V  |               |  |

| DC36c            |                              | 1000       |                                                       | +105°C              |       |               |  |

## TABLE 32-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE current measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode, program Flash memory Wait states = 111, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0)

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

- **4:** All parameters are characterized, but only those parameters listed for 4 MHz and 80 MHz are tested at 3.3V in manufacturing.

| DC CHARACTERISTICS |        |                                                                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |                          |          |                                                                                                                                                                         |

|--------------------|--------|-----------------------------------------------------------------------|-------------------------------------------------------|------------------------|--------------------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                                                       | Min.                                                  | Typical <sup>(1)</sup> | Max.                     | Units    | Conditions                                                                                                                                                              |

| DI50               | lil    | Input Leakage Current <sup>(3)</sup><br>I/O Ports                     | _                                                     | _                      | <u>+</u> 1               | μA       | Vss $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |

| DI51               |        | Analog Input Pins                                                     | —                                                     | —                      | <u>+</u> 1               | μΑ       | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance                                                                                                                    |

| DI55<br>DI56       |        | MCLR <sup>(2)</sup><br>OSC1                                           | —                                                     | _                      | <u>+</u> 1<br><u>+</u> 1 | μΑ<br>μΑ | $\label{eq:VSS} \begin{array}{l} \forall SS \leq VPIN \leq VDD \\ \forall SS \leq VPIN \leq VDD, \\ XT \text{ and } HS \text{ modes} \end{array}$                       |