Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256l-80v-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual chapters of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

- Note 1: To access the documents listed below, browse to the documentation section of the PIC32MX795F512L product page on the Microchip web site (www.microchip.com) or select a family reference manual section from the following list. In addition to parameters, features, and other documentation, the resulting page provides links to the related family

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 3. "Memory Organization" (DS60001115)

reference manual sections.

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Capture" (DS60001111)

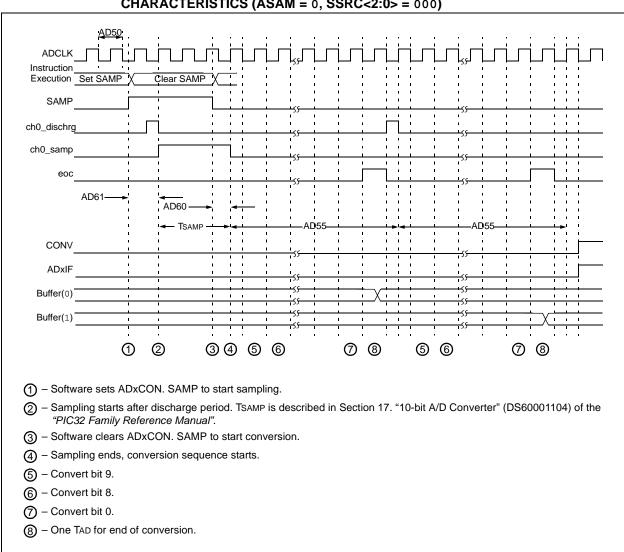

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I2C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

| TABLE 1- | <u>I: PINOU</u>                               | T I/O DES       | CRIPTION            | NS (CONT        | INUED | )                    |                                                   |  |  |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|-------|----------------------|---------------------------------------------------|--|--|--|

|          |                                               | Pin Nur         | nber <sup>(1)</sup> |                 | Pin   | Buffer               |                                                   |  |  |  |

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре  | Туре                 | Description                                       |  |  |  |

| SDI1     | —                                             | 9               | E1                  | B5              | I     | ST                   | SPI1 data in                                      |  |  |  |

| SDO1     | —                                             | 72              | D9                  | B39             | 0     | _                    | SPI1 data out                                     |  |  |  |

| SS1      | _                                             | 69              | E10                 | A45             | I/O   | ST                   | SPI1 slave synchronization or frame pulse I/O     |  |  |  |

| SCK3     | 49                                            | 48              | K9                  | A31             | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI3 |  |  |  |

| SDI3     | 50                                            | 52              | K11                 | A36             | I     | ST                   | SPI3 data in                                      |  |  |  |

| SDO3     | 51                                            | 53              | J10                 | B29             | 0     |                      | SPI3 data out                                     |  |  |  |

| SS3      | 43                                            | 47              | L9                  | B26             | I/O   | ST                   | SPI3 slave synchronization or frame pulse I/O     |  |  |  |

| SCK2     | 4                                             | 10              | E3                  | A7              | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI2 |  |  |  |

| SDI2     | 5                                             | 11              | F4                  | B6              | I     | ST                   | SPI2 data in                                      |  |  |  |

| SDO2     | 6                                             | 12              | F2                  | A8              | 0     |                      | SPI2 data out                                     |  |  |  |

| SS2      | 8                                             | 14              | F3                  | A9              | I/O   | ST                   | SPI2 slave synchronization or frame pulse I/O     |  |  |  |

| SCK4     | 29                                            | 39              | L6                  | B22             | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI4 |  |  |  |

| SDI4     | 31                                            | 49              | L10                 | B27             | I     | ST                   | SPI4 data in                                      |  |  |  |

| SDO4     | 32                                            | 50              | L11                 | A32             | 0     |                      | SPI4 data out                                     |  |  |  |

| SS4      | 21                                            | 40              | K6                  | A27             | I/O   | ST                   | SPI4 slave synchronization or frame pulse I/O     |  |  |  |

| SCL1     | 44                                            | 66              | E11                 | B36             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C1 |  |  |  |

| SDA1     | 43                                            | 67              | E8                  | A44             | I/O   | ST                   | Synchronous serial data input/output for I2C1     |  |  |  |

| SCL3     | 51                                            | 53              | J10                 | B29             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C3 |  |  |  |

| SDA3     | 50                                            | 52              | K11                 | A36             | I/O   | ST                   | Synchronous serial data input/output for I2C3     |  |  |  |

| SCL2     | _                                             | 58              | H11                 | A39             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C2 |  |  |  |

| SDA2     | _                                             | 59              | G10                 | B32             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C2  |  |  |  |

| SCL4     | 6                                             | 12              | F2                  | A8              | I/O   | ST                   | Synchronous serial clock input/outpu<br>for I2C4  |  |  |  |

| SDA4     | 5                                             | 11              | F4                  | B6              | I/O   | ST                   | Synchronous serial data input/output<br>for I2C4  |  |  |  |

| SCL5     | 32                                            | 50              | L11                 | A32             | I/O   | ST                   | Synchronous serial clock input/outpu<br>for I2C5  |  |  |  |

| SDA5     | 31                                            | 49              | L10                 | B27             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C5  |  |  |  |

| -        | CMOS = CMO<br>ST = Schmitt 1<br>TTL = TTL inp | Frigger input   |                     |                 |       | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input             |  |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

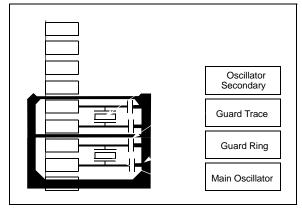

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS09            | IFS08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IFS07             | IFS06             | IFS05             | IFS04             | IFS03             | IFS02             | IFS01            | IFS00            |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-0 IFS31-IFS00: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

# REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC09            | IEC08            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC07             | IEC06             | IEC05             | IEC04             | IEC03             | IEC02             | IEC01            | IEC00            |

# Legend:

| · J · · ·                         |                  |                                    |                    |  |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-0 IEC31-IEC00: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

# TABLE 10-3: DMA CHANNELS 0-7 REGISTER MAP (CONTINUED)

| ess                         |                                 |                          |             |              |             |                |                |              |              | В       | its     |        |        |        |                  |        |        |         |              |

|-----------------------------|---------------------------------|--------------------------|-------------|--------------|-------------|----------------|----------------|--------------|--------------|---------|---------|--------|--------|--------|------------------|--------|--------|---------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                | 31/15       | 30/14        | 29/13       | 28/12          | 27/11          | 26/10        | 25/9         | 24/8    | 23/7    | 22/6   | 21/5   | 20/4   | 19/3             | 18/2   | 17/1   | 16/0    | All Resets   |

|                             |                                 | 31:16                    | _           |              | _           | _              | _              | _            | _            | _       | —       | _      | _      | _      | _                | _      | _      | _       | 0000         |

| 3290                        | DCH2DAT                         | 15:0                     | _           |              | _           | _              | _              | _            | _            | _       |         |        |        | CHPDA  | AT<7:0>          |        |        |         | 0000         |

| 32A0                        | DCH3CON                         | 31:16                    | _           | 0000         |             |                |                |              |              |         |         |        |        |        |                  |        |        |         |              |

| 32A0                        | Denseon                         | 15:0                     | CHBUSY      | -            | —           | —              | —              | —            | —            | CHCHNS  | CHEN    | CHAED  | CHCHN  | CHAEN  | —                | CHEDET | CHPR   | l<1:0>  | 0000         |

| 32B0                        | DCH3ECON                        | 31:16                    |             |              |             |                |                |              |              |         |         |        |        |        |                  |        |        |         |              |

|                             |                                 | 15:0                     |             |              |             |                | Q<7:0>         |              |              | -       | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN           | _      | —      | —       | FF00         |

| 32C0                        | <b>DCH3INT</b>                  | 31:16                    | —           | _            | —           | —              | _              | _            | _            | —       | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE           | CHCCIE | CHTAIE | CHERIE  | 0000         |

|                             |                                 | 15:0                     |             |              |             |                |                |              |              |         |         |        |        |        |                  |        |        |         |              |

| 32D0                        | DCH3SSA                         | 31:16                    |             | CHSSA<31:0>  |             |                |                |              |              |         |         |        |        |        |                  |        |        |         |              |

|                             |                                 | 15:0<br>31:16            |             | 0000         |             |                |                |              |              |         |         |        |        |        |                  |        |        |         |              |

| 32E0                        | DCH3DSA                         | 15:0                     |             |              |             |                |                |              |              | CHDSA   | A<31:0> |        |        |        |                  |        |        |         | 0000         |

|                             |                                 | 31:16                    | _           | _            | _           | _              | _              | _            | _            | _       | _       | _      | _      | _      | _                | _      | _      | _       | 0000         |

| 32F0                        | DCH3SSIZ                        | I3SSIZ 15:0 CHSSIZ<15:0> |             |              |             |                |                |              |              |         | 0000    |        |        |        |                  |        |        |         |              |

|                             |                                 | 31:16                    | _           | _            | _           | _              | _              | _            |              | _       | _       |        | _      | _      | _                | _      | _      |         | 0000         |

| 3300                        | DCH3DSIZ                        | 15:0                     |             |              |             |                |                |              |              | CHDSI   | Z<15:0> |        |        |        |                  |        |        |         | 0000         |

|                             | DOLIGODITO                      | 31:16                    | _           | _            | _           | _              | _              | —            | _            | _       | _       | _      | _      | _      | _                | _      | _      | _       | 0000         |

| 3310                        | DCH3SPTR                        | 15:0                     |             |              |             | •              | •              |              |              | CHSPT   | R<15:0> |        | •      |        | •                |        |        |         | 0000         |

| 2220                        | DCH3DPTR                        | 31:16                    | _           |              | _           | —              | —              | _            | _            | —       | _       | _      | _      | _      | —                | —      | _      | _       | 0000         |

| 3320                        | DCH3DFTK                        | 15:0                     |             |              |             |                |                |              |              | CHDPT   | R<15:0> |        |        |        |                  |        |        |         | 0000         |

| 3330                        | DCH3CSIZ                        | 31:16                    | —           | —            | —           | —              | —              | —            | —            | —       | —       | —      | —      | —      | —                | —      | —      | —       | 0000         |

| 0000                        | DOI 130012                      | 15:0                     |             |              |             |                |                |              |              | CHCSI   | Z<15:0> |        | -      |        | -                |        |        |         | 0000         |

| 3340                        | DCH3CPTR                        | 31:16                    | —           | —            | —           | —              | —              | —            | —            | —       | —       | —      | -      | —      | —                | —      | —      | —       | 0000         |

|                             |                                 | 15:0                     |             |              |             | -              | -              |              |              | CHCPT   | R<15:0> |        | -      |        | -                |        |        |         | 0000         |

| 3350                        | DCH3DAT                         | 31:16                    | _           | _            | —           |                |                | _            | _            |         | _       |        | —      | —      | —                | _      | _      |         | 0000         |

|                             |                                 | 15:0                     | _           |              | _           |                |                | _            | -            |         |         |        |        |        | AT<7:0>          | 1      |        |         | 0000         |

| 3360                        | DCH4CON                         | 31:16                    | -           |              | _           | _              | _              | _            | _            | -       | -       | -      | -      | -      | -                |        | -      | —       | 0000         |

|                             |                                 | 15:0                     | CHBUSY      |              | _           |                | _              |              | _            | CHCHNS  | CHEN    | CHAED  | CHCHN  | CHAEN  | -                | CHEDET | CHPR   | (1<1:0> | 0000         |

| 3370                        | DCH4ECON                        | 31:16<br>15:0            | _           |              |             |                | <br>Q<7:0>     |              |              | —       | CFORCE  | CABORT | PATEN  | SIRQEN | Q<7:0><br>AIRQEN |        | _      | _       | 00FF<br>FF00 |

|                             |                                 | 31:16                    | _           | _            |             |                |                |              |              | _       | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE           | CHCCIE | CHTAIE | CHERIE  | 0000         |

| 3380                        | DCH4INT                         | 15:0                     |             |              |             |                |                |              |              |         |         |        |        | 0000   |                  |        |        |         |              |

|                             |                                 | 31:16                    |             |              |             |                |                |              |              |         |         | 0000   |        |        |                  |        |        |         |              |

| 3390                        | DCH4SSA                         | 15:0                     |             |              |             |                |                |              |              | CHSSA   | A<31:0> |        |        |        |                  |        |        |         | 0000         |

|                             |                                 | 31:16                    |             |              |             |                |                |              |              |         |         |        |        |        |                  |        |        |         | 0000         |

| 33A0                        | DCH4DSA                         | 15:0                     |             |              |             |                |                |              |              | CHDSA   | \<31:0> |        |        |        |                  |        |        |         | 0000         |

| Legen                       | <b>d:</b> x = u                 | nknown                   | value on Re | eset; — = ur | nimplemente | ed, read as '0 | )'. Reset valu | ues are show | vn in hexade | ecimal. |         |        |        |        |                  |        |        |         | <u>ا</u> ا   |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

2: DMA channels 4-7 are not available on PIC32MX534/564/664/764 devices.

# 14.2 Control Registers

| TABLE 14-1: | TIMER2 THROUGH TIMER5 REGISTER MAP |

|-------------|------------------------------------|

|             |                                    |

|                             |                                 | ••            |       |                |       |       |       |       |      |          |            |      |                |          |      |      |                         |      |            |

|-----------------------------|---------------------------------|---------------|-------|----------------|-------|-------|-------|-------|------|----------|------------|------|----------------|----------|------|------|-------------------------|------|------------|

| ess                         |                                 |               |       |                |       |       |       |       |      | В        | ts         |      |                |          |      |      |                         |      |            |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14          | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8     | 23/7       | 22/6 | 21/5           | 20/4     | 19/3 | 18/2 | 17/1                    | 16/0 | All Resets |

| 0800                        | T2CON                           | 31:16         | —     | _              | —     | —     |       | —     |      |          | —          | —    | —              |          | —    | -    | —                       |      | 0000       |

| 0800                        | 12001                           | 15:0          | ON    | _              | SIDL  | _     | -     | —     | 1    |          | TGATE      |      | TCKPS<2:0>     |          | T32  |      | TCS <sup>(2)</sup>      |      | 0000       |

| 0810                        | TMR2                            | 31:16         | _     | —              | —     | —     | _     | —     | _    | —        | —          | _    | —              | _        | —    | _    | —                       | _    | 0000       |

| 0010                        | T IVIT VZ                       | 15:0          |       | TMR2<15:0> 000 |       |       |       |       |      |          |            | 0000 |                |          |      |      |                         |      |            |

| 0820                        | PR2                             | 31:16         | —     | —              | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

| 0020                        | 1112                            | 15:0          |       |                |       |       |       |       |      | PR2<     | 15:0>      |      | •              |          |      |      |                         |      | FFFF       |

| 0A00                        | T3CON                           | 31:16         | —     | —              | —     | —     | —     | —     | —    | _        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

| 0,100                       | 100011                          | 15:0          | ON    | —              | SIDL  | _     | _     | —     | _    | _        | TGATE      |      | TCKPS<2:0>     | <b>`</b> | —    | —    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0A10                        | TMR3                            | 31:16         | —     | —              | —     | _     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             |                                 | 15:0          |       |                | 1     |       |       |       |      | TMR3     | <15:0>     |      |                |          |      |      |                         |      | 0000       |

| 0A20                        | PR3                             | 31:16         | —     | —              | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        | —    | —    | —                       | —    | 0000       |

|                             | -                               | 15:0          |       |                |       |       |       |       |      | PR3<     | 15:0>      |      | -              |          |      |      |                         |      | FFFF       |

| 0C00                        | T4CON                           | 31:16         | _     | —              | —     | —     | —     | —     | —    | —        | —          | —    | —              | —        |      | —    |                         | —    | 0000       |

|                             |                                 | 15:0          | ON    | _              | SIDL  | —     | _     | _     |      | _        | TGATE      |      | TCKPS<2:0>     | >        | T32  | _    | TCS <sup>(2)</sup>      | _    | 0000       |

| 0C10                        | TMR4                            | 31:16         | —     | —              |       | —     | —     | _     | _    |          |            | —    | —              | —        |      | _    | —                       | _    | 0000       |

|                             |                                 | 15:0          |       |                |       |       |       |       |      | TMR4     |            |      |                |          |      |      |                         |      | 0000       |

| 0C20                        | PR4                             | 31:16         | -     | —              | —     | —     | _     | _     | _    | -        | -          | _    | —              | _        | —    | _    | _                       | —    | 0000       |

|                             |                                 | 15:0          | _     |                |       | _     |       |       |      | PR4<     |            |      |                | _        |      | _    | _                       | _    | FFFF       |

| 0E00                        | T5CON                           | 31:16<br>15:0 | ON    |                |       |       |       |       |      |          | —<br>TGATE |      | <br>TCKPS<2:0> |          |      |      | —<br>TCS <sup>(2)</sup> |      | 0000       |

| <u> </u>                    |                                 | 31:16         | - UN  |                | SIDL  |       |       |       |      | _        | IGATE      | _    |                | ,<br>    | _    |      | -                       | _    | 0000       |

| 0E10                        | TMR5                            | 15:0          | _     |                | _     | _     |       | —     |      | <br>TMR5 |            | _    | _              |          | _    | _    |                         | _    | 0000       |

|                             |                                 | 31:16         | _     | _              |       | _     | _     | _     | _    | —        |            | _    | _              | _        | _    | _    | _                       | _    | 0000       |

| 0E20                        | PR5                             | 15:0          |       |                |       |       |       |       |      |          |            |      | _              |          |      |      |                         |      |            |

|                             |                                 | 13.0          |       | PR5<15:0> FFFF |       |       |       |       |      |          |            |      |                |          |      |      |                         |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on 64-pin devices.

# 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) in the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32). The  $l^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $l^2C$  serial communication standard. Figure 19-1 illustrates the  $l^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

# 22.1 Control Registers

# TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 |           |              |        |         |          |       |            |        | В    | its          |          |        |      |            |                   |         |       |            |

|-----------------------------|---------------------------------|-----------|--------------|--------|---------|----------|-------|------------|--------|------|--------------|----------|--------|------|------------|-------------------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14  | 29/13   | 28/12    | 27/11 | 26/10      | 25/9   | 24/8 | 23/7         | 22/6     | 21/5   | 20/4 | 19/3       | 18/2              | 17/1    | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     |              |        |         | —        |       |            |        |      |              |          | CAL<   | 9:0> |            |                   |         |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON           | -      | SIDL    | —        | —     | —          |        | _    | RTSECSEL     | RTCCLKON | —      |      | RTCWREN    | RTCSYNC           | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _            | -      | _       | —        | —     | —          |        | _    | —            | _        | —      |      | _          | _                 | _       | —     | 0000       |

| 0210                        | RICALKI                         | 15:0      | ALRMEN       | CHIME  | PIV     | ALRMSYNC |       | AMASK<3:0> |        |      |              |          |        | ARPT | <7:0>      |                   |         |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     |              | HR10   | 0<3:0>  |          |       | HR01       | <3:0>  |      | MIN10<3:0>   |          |        |      | MIN01<3:0> |                   |         |       | xxxx       |

| 0220                        | RICTIVIE                        | 15:0      |              | SEC1   | 0<3:0>  |          |       | SEC01      | <3:0>  |      | _            | _        | —      | -    | _          | —                 | —       | —     | xx00       |

| 0000                        | DTODATE                         | 31:16     |              | YEAR'  | 10<3:0> |          |       | YEAR0      | 1<3:0> |      | MONTH10<3:0> |          |        |      |            | MONTH             | 01<3:0> |       | xxxx       |

| 0230                        | RTCDATE                         | 15:0      |              | DAY1   | 0<3:0>  |          |       | DAY01      | l<3:0> |      | -            | _        | _      | _    |            | WDAY(             | )1<3:0> |       | xx00       |

| 0040                        |                                 | 31:16     |              | HR10   | )<3:0>  |          |       | HR01       | <3:0>  |      |              | MIN10<   | 3:0>   |      |            | MIN0 <sup>2</sup> | <3:0>   |       | xxxx       |

| 0240                        | ALRMTIME                        | 15:0      |              | SEC1   | 0<3:0>  |          |       | SEC01<3:0> |        |      | _            | —        | _      | _    | _          | _                 | _       | _     | xx00       |

| 0050                        |                                 | 31:16     | _            | _      | _       | —        | _     |            |        |      |              | MONTH1   | )<3:0> |      |            | MONTH             | 01<3:0> |       | 00xx       |

| 0250                        | ALRMDATE                        | 15:0      |              | DAY1   | 0<3:0>  |          |       | DAY01<3:0> |        |      |              | _        | _      | _    |            | WDAY              | )1<3:0> |       | xx0x       |

|                             | ، بام                           | unknow    | n voluo on D | Reset: |         |          |       |            |        |      |              |          |        |      |            |                   |         |       |            |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | _                 | —                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

# REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by                                                                                             |

**Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |  |  |

| 23:16        | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23.10        | —                 | —                 | ТХВО              | TXBP              | RXBP              | TXWARN            | RXWARN           | EWARN            |  |  |

| 15:8         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 10.6         | TERRCNT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | RERRCNT<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

# REGISTER 24-5: CITREC: CAN TRANSMIT/RECEIVE ERROR COUNT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-22 Unimplemented: Read as '0'

bit 21 **TXBO:** Transmitter in Error State Bus OFF (TERRCNT  $\geq$  256)

- bit 20 **TXBP:** Transmitter in Error State Bus Passive (TERRCNT  $\geq$  128)

- bit 19 **RXBP:** Receiver in Error State Bus Passive (RERRCNT  $\geq$  128)

- bit 18 **TXWARN:** Transmitter in Error State Warning (128 > TERRCNT ≥ 96)

- bit 17 **RXWARN:** Receiver in Error State Warning  $(128 > \text{RERRCNT} \ge 96)$

- bit 16 EWARN: Transmitter or Receiver is in Error State Warning

- bit 15-8 TERRCNT<7:0>: Transmit Error Counter

- bit 7-0 RERRCNT<7:0>: Receive Error Counter

### REGISTER 24-6: CIFSTAT: CAN FIFO STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 31.24        | FIFOIP31          | FIFOIP30          | FIFOIP29          | FIFOIP28          | FIFOIP27          | FIFOIP26          | FIFOIP25         | FIFOIP24         |

| 23:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23.10        | FIFOIP23          | FIFOIP22          | FIFOIP21          | FIFOIP20          | FIFOIP19          | FIFOIP18          | FIFOIP17         | FIFOIP16         |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | FIFOIP15          | FIFOIP14          | FIFOIP13          | FIFOIP12          | FIFOIP11          | FIFOIP10          | FIFOIP9          | FIFOIP8          |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | FIFOIP7           | FIFOIP6           | FIFOIP5           | FIFOIP4           | FIFOIP3           | FIFOIP2           | FIFOIP1          | FIFOIP0          |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 FIFOIP<31:0>: FIFOn Interrupt Pending bits

1 = One or more enabled FIFO interrupts are pending

0 = No FIFO interrupts are pending

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN15           |                   | MSEL15<1:0>       |                   | F                 | SEL15<4:0>        |                  |                  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN14           | MSEL14<1:0>       |                   | FSEL14<4:0>       |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN13           | MSEL1             | 3<1:0>            | FSEL13<4:0>       |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN12           | MSEL1             | 2<1:0>            | FSEL12<4:0>       |                   |                   |                  |                  |

# REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31    | FLTEN15: Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN14: Filter 14 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| Note:     | The hits in this register can only be modified if the correspondir                                                                                                                                                                                                                         |

**Note:** The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

|              |                   |                   |                   |                   |                   | •                 |                    | ,                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |

| 31:24        | R-x                | R-x                |  |

| 31.24        |                   |                   |                   | CiFIFOUA          | n<31:24>          |                   |                    | •                  |  |

| 23:16        | R-x                | R-x                |  |

| 23.10        | CiFIFOUAn<23:16>  |                   |                   |                   |                   |                   |                    |                    |  |

| 45.0         | R-x                | R-x                |  |

| 15:8         | CiFIFOUAn<15:8>   |                   |                   |                   |                   |                   |                    |                    |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |

| 7:0          |                   | •                 |                   | CiFIFOU           | IAn<7:0>          |                   |                    |                    |  |

## REGISTER 24-22: CiFIFOUAn: CAN FIFO USER ADDRESS REGISTER 'n' (n = 0 THROUGH 31)

# Legend:

| 3                 |                  |                        |                                    |  |

|-------------------|------------------|------------------------|------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |

bit 31-0 CiFIFOUAn<31:0>: CAN FIFO User Address bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return the address where the next message is to be written (FIFO head).

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return the address where the next message is to be read (FIFO tail).

**Note 1:** This bit will always read '0', which forces byte-alignment of messages.

**Note:** This register is not guaranteed to read correctly in Configuration mode, and should only be accessed when the module is not in Configuration mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          | _                 | _                 | _                 |                   | (                 | CiFIFOCI<4:0:     | >                |                  |

### **REGISTER 24-23:** CiFIFOCIN: CAN MODULE MESSAGE INDEX REGISTER 'n' (n = 0 THROUGH 31)

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 CiFIFOCIn<4:0>: CAN Side FIFO Message Index bits

TXEN = 1: (FIFO configured as a transmit buffer)

A read of this register will return an index to the message that the FIFO will next attempt to transmit.

TXEN = 0: (FIFO configured as a receive buffer)

A read of this register will return an index to the message that the FIFO will use to save the next message.

# REGISTER 25-11: ETHRXFC: ETHERNET CONTROLLER RECEIVE FILTER CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 | _                 |                   | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 |                   |                   |                   |                   | —                |                  |

| 15:8         | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | HTEN              | MPEN              | _                 | NOTPM             |                   | PMMODE            | <3:0>            |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | CRCERREN          | CRCOKEN           | RUNTERREN         | RUNTEN            | UCEN              | NOTMEEN           | MCEN             | BCEN             |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **HTEN:** Enable Hash Table Filtering bit

- 1 = Enable Hash Table Filtering

- 0 = Disable Hash Table Filtering

- bit 14 **MPEN:** Magic Packet<sup>™</sup> Enable bit 1 = Enable Magic Packet Filtering 0 = Disable Magic Packet Filtering

- bit 13 Unimplemented: Read as '0'

- bit 12 **NOTPM:** Pattern Match Inversion bit

- 1 = The Pattern Match Checksum must not match for a successful Pattern Match to occur

- 0 = The Pattern Match Checksum must match for a successful Pattern Match to occur

This bit determines whether Pattern Match Checksum must match in order for a successful Pattern Match to occur.

- bit 11-8 PMMODE<3:0>: Pattern Match Mode bits

- 1001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Packet = Magic Packet)<sup>(1,3)</sup>

- 1000 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Hash Table Filter match)<sup>(1,2)</sup>

- 0111 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0110 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Broadcast Address)<sup>(1)</sup>

- 0101 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0100 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Unicast Address)<sup>(1)</sup>

- 0011 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0010 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches) AND (Destination Address = Station Address)<sup>(1)</sup>

- 0001 = Pattern match is successful if (NOTPM = 1 XOR Pattern Match Checksum matches)<sup>(1)</sup>

- 0000 = Pattern Match is disabled; pattern match is always unsuccessful

### **Note 1:** XOR = True when either one or the other conditions are true, but not both.

- 2: This Hash Table Filter match is active regardless of the value of the HTEN bit.

- 3: This Magic Packet Filter match is active regardless of the value of the MPEN bit.

**Note 1:** This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2      | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0              |

| 31.24        | —                 | —                 | —                 | —                 | —                 | —                      | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0              | U-0              |

| 23.10        |                   |                   | _                 |                   | —                 | _                      |                  |                  |

| 15.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | R/W-0                  | R/W-0            | R/W-1            |

| 15:8         | ON <sup>(1)</sup> | —                 | —                 | —                 | —                 | VREFSEL <sup>(2)</sup> | BGSEL            | <1:0> <b>(2)</b> |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0            | R/W-0            |

| 7.0          | _                 | CVROE             | CVRR              | CVRSS             |                   | CVR<                   | :3:0>            |                  |

#### REGISTER 27-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER

#### Legend:

| 0                 |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

ON: Comparator Voltage Reference On bit<sup>(1)</sup> bit 15 Setting or clearing this bit does not affect the other bits in this register. 1 = Module is enabled0 = Module is disabled and does not consume current bit 14-11 Unimplemented: Read as '0' VREFSEL: Voltage Reference Select bit<sup>(2)</sup> bit 10 1 = CVREF = VREF+0 = CVREF is generated by the resistor network BGSEL<1:0>: Band Gap Reference Source bits<sup>(2)</sup> bit 9-8 11 = IVRFF = VRFF+10 = Reserved 01 = IVREF = 0.6V (nominal, default)

- 00 = IVREF = 1.2V (nominal)

- bit 7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

#### bit 5 **CVRR:** CVREF Range Selection bit

- 1 = 0 to 0.625 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.719 CVRSRC, with CVRSRC/32 step size

#### bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)0 = Comparator voltage reference source, CVRSRC = AVDD - AVSS **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

- bit 3-0 When CVRR = 1:  $CVREF = (CVR < 3:0 > /24) \bullet (CVRSRC)$ When CVRR = 0:  $CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)$

- Note 1: When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: These bits are not available on PIC32MX575/675/775/795 devices. On these devices, the reset value for CVRON is '0000'.

# 31.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

# 31.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

# 31.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.