Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256lt-80i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES (CONTINUED)

**100-PIN TQFP (TOP VIEW)** PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L 100 1 Pin # **Full Pin Name** Pin # Full Pin Name 71 IC4/PMCS1/PMA14/RD11 86 Vdd 72 SDO1/OC1/INT0/RD0 87 C1RX/PMD11/RF0 SOSCI/CN1/RC13 C1TX/PMD10/RF1 88 73 SOSCO/T1CK/CN0/RC14 74 89 PMD9/RG1 Vss PMD8/RG0 75 90 TRCLK/RA6 76 OC2/RD1 91 77 OC3/RD2 92 TRD3/RA7 78 OC4/RD3 93 PMD0/RE0 PMD1/RE1 79 IC5/PMD12/RD12 94 80 PMD13/CN19/RD13 95 TRD2/RG14 OC5/PMWR/CN13/RD4 96 TRD1/RG12 81 PMRD/CN14/RD5 TRD0/RG13 82 97 PMD14/CN15/RD6 98 PMD2/RE2 83 PMD15/CN16/RD7 PMD3/RE3 84 99 85 VCAP 100 PMD4/RE4

Note 1: Shaded pins are 5V tolerant.

# PIC32MX5XX/6XX/7XX

NOTES:

# 2.9 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the Analog-to-Digital input pins (ANx) as "digital" pins by setting all bits in the AD1PCFG register.

The bits in this register that correspond to the Analogto-Digital pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain ADC pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFG register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFG register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all ADC pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.10 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 2.11 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

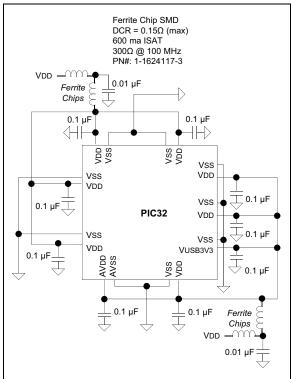

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-4. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

# FIGURE 2-4: EMI/EMC/EFT SUPPRESSION CIRCUIT

# 3.2 Architecture Overview

The MIPS32 M4K processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

# 3.2.1 EXECUTION UNIT

The MIPS32 M4K processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bit-wise logical operations

- Shifter and store aligner

# 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

MIPS32 M4K processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16 bit wide *rs*, 15 iterations are skipped and for a 24 bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Opcode                  | Operand Size (mul rt) (div rs) | Latency | Repeat Rate |

|-------------------------|--------------------------------|---------|-------------|

| MULT/MULTU, MADD/MADDU, | 16 bits                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                        | 2       | 2           |

| MUL                     | 16 bits                        | 2       | 1           |

|                         | 32 bits                        | 3       | 2           |

| DIV/DIVU                | 8 bits                         | 12      | 11          |

|                         | 16 bits                        | 19      | 18          |

|                         | 24 bits                        | 26      | 25          |

|                         | 32 bits                        | 33      | 32          |

# TABLE 3-1:MIPS32<sup>®</sup> M4K<sup>®</sup> CORE HIGH-PERFORMANCE INTEGER MULTIPLY/DIVIDE UNIT<br/>LATENCIES AND REPEAT RATES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   |                   |                   | CHEW3<            | :23:16>           |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   |                   |                   | CHEW3             | <15:8>            |                   |                  |                  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   | •                 | •                 | CHEW3             | <7:0>             |                   | •                |                  |

# REGISTER 9-8: CHEW3: CACHE WORD 3

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is only readable if the device is not code-protected.

### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 31.24        | —                 | —                 |                   |                   | —                 | _                 | —                | CHELRU<24>       |

| 22:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 23:16        |                   |                   |                   | CHELRI            | J<23:16>          |                   |                  |                  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHELR             | U<15:8>           |                   |                  |                  |

| 7:0          | 7:0 R-0           |                   | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7.0          |                   |                   |                   | CHELF             | RU<7:0>           |                   |                  |                  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

# 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded Host, full-speed Device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

The USB module includes the following features:

- USB Full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- Transaction handshaking performed by hardware

- Endpoint buffering anywhere in system RAM

- Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, as well as other third party may specifications or technologies, require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

#### 11.1 **Control Registers**

# TABLE 11-1: USB REGISTER MAP

| Signature         Signature           5040         U10TGIR <sup>(2)</sup> 5050         U10TGIR <sup>(2)</sup> 5060         U10TGSTAT           5070         U10TGCO           5080         U11PWRC           5200         U11R <sup>(2)</sup> 5210         U11EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> 5220         U1EIR <sup>(2)</sup> | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | i:16       5:0       1:16       5:0       1:16       5:0       1:16       5:0       1:16 | 31/15<br>        | 30/14<br> | 29/13<br> | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | Bits<br>23/7           | 22/6               | 04/5                 |            |           |          |                 | r        | Resets |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------------|-----------|-----------|-------|-------|-------|------|------|------------------------|--------------------|----------------------|------------|-----------|----------|-----------------|----------|--------|

| 5040         U10TGIR <sup>(2)</sup> 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                      | 2) 31:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>15:<br>1                                | 1:16<br>5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                        |                  | -         |           | -     |       |       | 25/9 | 24/8 | 23/7                   | 22/6               | 04/5                 |            |           | ļ        |                 |          | eset   |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 2) 15<br>31:<br>15<br>(3) 31:<br>(3) 31:<br>15<br>15<br>31:<br>31:<br>31                    | 5:0<br>1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                | —<br>—<br>—<br>— | -         | _         |       | _     |       |      |      |                        | 22/0               | 21/5                 | 20/4       | 19/3      | 18/2     | 17/1            | 16/0     | All Re |

| 5050         U10TGIE           5060         U10TGSTAT           5070         U10TGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                          | 15<br>31:<br>15<br>(3)<br>31:<br>15<br>31:<br>Ν<br>31:<br>31:                               | 1:16<br>5:0<br>1:16<br>5:0<br>1:16                                                       | -<br>-<br>-      |           |           |       |       | —     | -    | _    | _                      | —                  | —                    | —          | _         | —        | —               | —        | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15<br>(3) 31:<br>15:<br>Ν 31:<br>15:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31:<br>31 | 5:0<br>1:16<br>5:0<br>1:16                                                               | -                | —         |           |       | -     |       |      | —    | IDIF                   | T1MSECIF           | LSTATEIF             | ACTVIF     | SESVDIF   | SESENDIF | _               | VBUSVDIF | 0000   |

| 5060         U1OTGSTAT           5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                         | 15:<br>T <sup>(3)</sup> 31:<br>15:<br>N 31:<br>15:<br>31:<br>31:                            | 1:16<br>5:0<br>1:16                                                                      | -                | -         | —         |       | -     |       |      | —    | _                      | —                  | _                    | -          | _         | —        | _               | _        | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 15:<br>31:<br>31:<br>31:                                                                  | 5:0<br>1:16                                                                              |                  |           |           | _     | _     |       | _    | _    | IDIE                   | T1MSECIE           | LSTATEIE             | ACTVIE     | SESVDIE   | SESENDIE | _               | VBUSVDIE | 0000   |

| 5070         U1OTGCO           5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                          | N 31:<br>31:<br>31:<br>31:                                                                  | 1:16                                                                                     |                  | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | —        |                 | —        | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | N 15                                                                                        |                                                                                          | _                | -         | _         |       | -     |       |      | —    | ID                     | —                  | LSTATE               | -          | SESVD     | SESEND   |                 | VBUSVD   | 0000   |

| 5080         U1PWRC           5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                         | 31                                                                                          | E:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | -    |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       | 31:                                                                                         | 5.0                                                                                      | _                | _         | _         | _     | —     | _     |      |      | DPPULUP                | DMPULUP            | DPPULDWN             | DMPULDWN   | VBUSON    | OTGEN    | VBUSCHG         | VBUSDIS  | 0000   |

| 5200         U1IR <sup>(2)</sup> 5210         U1IE           5220         U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                       |                                                                                             | 1:16                                                                                     | _                | -         | _         |       | -     |       |      | —    | _                      | —                  | _                    | -          | —         | _        |                 | —        | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | —     | _     | _    | -    | UACTPND <sup>(4)</sup> | _                  | —                    | USLPGRD    | USBBUSY   | —        | USUSPEND        | USBPWR   | 0000   |

| 5210 U1IE<br>5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                               | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | —     | _     |      |      |                        | _                  | —                    | —          | —         | —        | —               | —        | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 15                                                                                          | 5:0                                                                                      | _                | _         | _         |       | _     |       |      | _    | STALLIF                | ATTACHIF           | RESUMEIF             | IDLEIF     | TRNIF     | SOFIF    | UERRIF          | URSTIF   | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | _                                                                                           |                                                                                          |                  |           |           |       |       |       |      |      | -                      |                    |                      |            |           |          |                 | DETACHIF | 0000   |

| 5220 U1EIR <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                            | 31:                                                                                         | 1:16                                                                                     | _                | _         | —         | —     | —     | —     | —    | _    | —                      | —                  | —                    | —          | —         | —        | —               |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    | STALLIE                | ATTACHIE           | RESUMEIE             | IDLEIE     | TRNIE     | SOFIE    | UERRIE          | URSTIE   | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          |                 |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 31:                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | —                      |                    | —                    | —          | _         |          | _               | —        | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 15                                                                                          | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | —    | BTSEF                  | BMXEF              | DMAEF                | BTOEF      | DFN8EF    | CRC16EF  | CRC5EF<br>EOFEF | PIDEF    | 0000   |

| 5230 U1EIE                                                                                                                                                                                                                                                                                                                                           | 31.                                                                                         | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    |      | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| SZSO OTELE                                                                                                                                                                                                                                                                                                                                           | 51.                                                                                         | 1.10                                                                                     |                  |           |           |       |       |       |      |      |                        |                    |                      |            |           |          | CRC5EE          |          | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | 15                                                                                          | 5:0                                                                                      | —                | —         | —         | —     | —     | —     | —    | —    | BTSEE                  | BMXEE              | DMAEE                | BTOEE      | DFN8EE    | CRC16EE  | EOFEE           | PIDEE    | 0000   |

| (2)                                                                                                                                                                                                                                                                                                                                                  | 、 31:                                                                                       | 1:16                                                                                     | _                | _         | _         | _     | _     |       | _    | _    | _                      | _                  | _                    | _          | _         |          | _               | _        | 0000   |

| 5240 U1STAT <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                           | ,                                                                                           | 5:0                                                                                      | _                | _         | _         | _     | _     | _     | _    | _    |                        | ENDPT              | <3:0> <sup>(4)</sup> |            | DIR       | PPBI     | _               | _        | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      | -                                                                                           | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    | _                      | _                  | _                    | _          | _         | _        | _               | _        | 0000   |

| 5250 U1CON                                                                                                                                                                                                                                                                                                                                           |                                                                                             |                                                                                          |                  |           |           |       |       |       |      |      | 10TATE(4)              | 0.5 0(4)           | PKTDIS               |            |           |          |                 | USBEN    | 0000   |

|                                                                                                                                                                                                                                                                                                                                                      |                                                                                             | 5:0                                                                                      | —                | _         | _         | —     | —     | —     | —    |      | JSTATE <sup>(4)</sup>  | SE0 <sup>(4)</sup> | TOKBUSY              | USBRST     | HOSTEN    | RESUME   | PPBRST          | SOFEN    | 0000   |

| 5260 U1ADDR                                                                                                                                                                                                                                                                                                                                          | 15                                                                                          | 1:16                                                                                     | _                | _         | _         | _     | _     | _     | _    | _    |                        | —                  | _                    | _          | —         | —        | _               | —        | 0000   |

| 5200 UTADDR                                                                                                                                                                                                                                                                                                                                          | 31:                                                                                         | 5:0                                                                                      | —                | _         | —         | _     | —     | _     | _    | _    | LSPDEN                 |                    |                      | DE         | VADDR<6:0 | 1>       |                 |          | 0000   |

| 5270 U1BDTP1                                                                                                                                                                                                                                                                                                                                         | 31:                                                                                         |                                                                                          | —                | _         | —         | _     | —     | _     | _    | _    | _                      | _                  | —                    | _          | _         | —        |                 | —        | 0000   |

| JZIU UIBDIPI                                                                                                                                                                                                                                                                                                                                         | 31:<br>15:                                                                                  | 1:16                                                                                     |                  | _         | _         | _     | _     | _     |      | _    |                        |                    | BD                   | TPTRL<7:1> |           |          |                 |          | 0000   |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for Note 1: more information.

2:

This register does not have associated SET and INV registers. This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

# TABLE 12-5: PORTD REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, AND PIC32MX795F512H DEVICES

| ess                         |                                 |           |       |       |       |       |         |         |        | Bi     | ts     |        |        |        |        |        |        |        | ú          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 60C0                        | TRISD                           | 31:16     | -     | -     | -     | _     | _       | -       | —      | —      | —      | —      | —      | -      | _      | -      | -      | —      | 0000       |

| 6000                        | TRISD                           | 15:0      | _     | _     | _     | -     | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | OFFF       |

| 6000                        | PORTD                           | 31:16     | _     |       |       | _     | _       |         | -      |        |        |        |        | _      | _      |        | _      | _      | 0000       |

| 6000                        | PORID                           | 15:0      | -     | -     | _     | _     | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx       |

| 60E0                        | LATD                            | 31:16     | _     | _     | _     | -     | _       | -       | _      | _      | _      | _      | _      | _      | -      | _      | _      | _      | 0000       |

| 60E0                        | LAID                            | 15:0      | _     | _     | _     | -     | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx       |

| 60F0                        | ODCD                            | 31:16     | _     | -     | _     | _     | _       | —       | -      | -      | -      |        |        | —      | _      | _      | _      | -      | 0000       |

| OUFU                        | ODCD                            | 15:0      |       | _     | —     | _     | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-6: PORTD REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F512L, AND PIC32MX795F512L DEVICES

| ess                         |                                 | Ċ,        |         |         |         |         |         |         |        | Bi     | ts     |        |        |        |        |        |        |        | 6         |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

| 60C0                        | TRISD                           | 31:16     | _       | _       | _       | -       | -       | _       |        | _      | -      | -      | _      |        | -      | -      | —      | —      | 0000      |

| 6000                        | TRISD                           | 15:0      | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF      |

| 60D0                        | PORTD                           | 31:16     | _       | _       |         |         |         | -       |        |        |        |        | -      |        |        |        | _      | _      | 0000      |

| 0000                        | FORID                           | 15:0      | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx      |

| 60E0                        | LATD                            | 31:16     | —       | _       | _       | _       | _       | _       | _      | _      | -      | _      | _      | _      | _      | _      | —      | —      | 0000      |

| OUEU                        | LAID                            | 15:0      | LAT15   | LAT14   | LAT13   | LAT12   | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx      |

| 60F0                        | ODCD                            | 31:16     | _       | _       |         |         |         | _       | -      |        |        |        | _      | -      |        |        | _      |        | 0000      |

| OUFU                        | ODCD                            | 15:0      | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000      |

Ļ

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0 R/W-0 F     |                  | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

# REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

#### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

# TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                       |           |                                                                                                |       |       |               |       |       |       | Bi     | ts    |        |       |          |          |      |        |       |            |

|-----------------------------|-----------------------|-----------|------------------------------------------------------------------------------------------------|-------|-------|---------------|-------|-------|-------|--------|-------|--------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15                                                                                          | 30/14 | 29/13 | 28/12         | 27/11 | 26/10 | 25/9  | 24/8   | 23/7  | 22/6   | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6620                        | U6TXREG               | 31:16     | _                                                                                              | _     | —     | —             |       |       | —     | —      |       | —      | _     |          | —        | —    | —      | —     | 0000       |

| 0020                        | UUTAREG               | 15:0      | _                                                                                              | _     | _     | —             | _     | _     | _     | TX8    |       |        |       | Transmit | Register | -    |        | -     | 0000       |

| 6630                        | U6RXREG               | 31:16     | _                                                                                              | -     | _     | —             | _     | _     | _     |        | _     | —      | _     |          | _        | _    | —      | _     | 0000       |

| 0030                        | UUKAREG               | 15:0      | _                                                                                              | _     | —     | —             | —     | —     | _     | RX8    |       |        |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U6BRG <sup>(1)</sup>  | 31:16     | _                                                                                              | _     | —     | —             | —     | —     | _     |        | _     | —      | —     | —        | —        | _    | —      | _     | 0000       |

| 0040                        | OODING                | 15:0      |                                                                                                |       | -     | -             |       |       |       | BRG<   | 15:0> |        |       |          | -        | -    |        | -     | 0000       |

| 6800                        | U2MODE <sup>(1)</sup> | 31:16     | _                                                                                              | _     | _     | —             | _     | _     | _     | —      | _     | -      | —     | _        | _        | _    | -      | _     | 0000       |

| 0000                        | OZIVIODE              | 15:0      | ON - SIDL IREN RTSMD - UEN<1:0> WAKE LPBACK ABAUD RXINV BRGH PDSEL<1:0> STSEL                  |       |       |               |       |       |       |        |       | 0000   |       |          |          |      |        |       |            |

| 6810                        | U2STA <sup>(1)</sup>  | 31:16     | ADDR<7:0>                                                                                      |       |       |               |       |       |       |        | -     | 0000   |       |          |          |      |        |       |            |

| 0010                        | 02017                 | 15:0      | UTXISEL<1:0> UTXINV URXEN UTXBRK UTXEN UTXBF TRMT URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXI |       |       |               |       |       | URXDA | 0110   |       |        |       |          |          |      |        |       |            |

| 6820                        | U2TXREG               | 31:16     | _                                                                                              | _     | _     | —             | _     | _     | _     | —      | _     | -      | —     | _        | —        | —    | -      | —     | 0000       |

| 0020                        | OZTARLO               | 15:0      | -                                                                                              | _     |       | —             | _     | —     | _     | TX8    |       |        |       | Transmit | Register | -    |        | -     | 0000       |

| 6830                        | U2RXREG               | 31:16     | -                                                                                              | _     |       | —             | _     | —     | _     | —      | _     | -      | —     | _        | _        | _    | -      |       | 0000       |

| 0000                        | OZIVAREO              | 15:0      | -                                                                                              | _     |       | —             | —     | —     | _     | RX8    |       |        |       | Receive  | Register | -    |        | -     | 0000       |

| 6840                        | U2BRG <sup>(1)</sup>  | 31:16     | —                                                                                              | —     | —     | —             | —     | —     | —     | —      | —     | —      | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        |                       | 15:0      |                                                                                                |       |       |               |       |       |       | BRG<   | 15:0> |        |       |          |          |      |        |       | 0000       |

| 6A00                        | U5MODE <sup>(1)</sup> | 31:16     | —                                                                                              | —     | —     | —             | —     | —     | —     | —      | —     | —      | —     | —        | —        | —    | —      | —     | 0000       |

| 0/100                       |                       | 15:0      | ON                                                                                             | _     | SIDL  | IREN          | _     | —     | _     | —      | WAKE  | LPBACK | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6A10                        | U5STA <sup>(1)</sup>  | 31:16     | —                                                                                              | —     | —     | —             | _     | —     | —     | ADM_EN |       |        |       | ADDR     |          | -    |        | -     | 0000       |

| 0,110                       |                       |           |                                                                                                |       |       |               |       |       | URXDA | 0110   |       |        |       |          |          |      |        |       |            |

| 6A20                        | U5TXREG               | 31:16     | -                                                                                              | _     | _     | _             | _     | _     |       | —      | _     | -      | —     | _        |          |      | -      |       | 0000       |

|                             |                       | 15:0      | —                                                                                              | _     | _     | _             | _     | _     |       | TX8    |       |        | 1     | Transmit | Register | 1    |        | 1     | 0000       |

| 6A30                        | U5RXREG               | 31:16     | -                                                                                              | _     | _     | _             | _     | _     |       | —      | _     | -      | —     | _        |          |      | -      |       | 0000       |

|                             |                       | 15:0      | —                                                                                              | —     | —     | —             | —     | —     | —     | RX8    |       |        |       | Receive  | Register |      |        |       | 0000       |

| 6A40                        | U5BRG <sup>(1)</sup>  | 31:16     | —                                                                                              | —     |       | —             | —     | —     | —     | —      | —     | —      | —     | _        |          |      | —      |       | 0000       |

| Legen                       |                       | 15:0      |                                                                                                |       |       | d, read as '0 |       |       |       | BRG<   | 15:0> |        |       |          |          |      |        |       | 0000       |

DS60001156J-page 206

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   |                   |                   |                  | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

# REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (ONLY SLAVE MODES)

| Legend: HS = Set by Hardware |                  | SC = Cleared by software  |                    |  |  |  |

|------------------------------|------------------|---------------------------|--------------------|--|--|--|

| R = Readable bit             | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |  |  |

| -n = Value at POR            | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **IBF:** Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

- 0 = An overflow has not occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = An underflow has not occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

# 22.1 Control Registers

# TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 |           |              |         |         |               |          |                   |                   | В        | its               |          |        |      |              |         |         |       |            |

|-----------------------------|---------------------------------|-----------|--------------|---------|---------|---------------|----------|-------------------|-------------------|----------|-------------------|----------|--------|------|--------------|---------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14   | 29/13   | 28/12         | 27/11    | 26/10             | 25/9              | 24/8     | 23/7              | 22/6     | 21/5   | 20/4 | 19/3         | 18/2    | 17/1    | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | _            | _       | —       | —             | _        |                   |                   |          |                   |          | CAL<   | 9:0> |              |         |         |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON           | _       | SIDL    | —             | —        | _                 |                   |          | RTSECSEL          | RTCCLKON |        |      | RTCWREN      | RTCSYNC | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _            | _       | _       | —             | —        | _                 |                   |          | —                 | _        |        |      | —            |         | _       | —     | 0000       |

| 0210                        | RICALKI                         | 15:0      | ALRMEN       | CHIME   | PIV     | ALRMSYNC      |          | AMASI             | <b>&lt;</b> <3:0> |          |                   |          |        | ARPT | <7:0>        |         |         |       | 0000       |

| 0220                        | RTCTIME                         | 31:16     |              | HR10    | 0<3:0>  |               |          | HR01              | <3:0>             |          | MIN10<3:0>        |          |        |      | MIN01<3:0>   |         |         |       | xxxx       |

| 0220                        | RICTIVIE                        | 15:0      |              | SEC1    | 0<3:0>  |               |          | SEC0 <sup>2</sup> | <3:0>             |          | _                 | _        | -      |      | -            | -       | _       | —     | xx00       |

| 0000                        | RTCDATE                         | 31:16     |              | YEAR'   | 10<3:0> |               |          | YEAR0             | 1<3:0>            |          | MONTH10<3:0>      |          |        |      | MONTH01<3:0> |         |         | xxxx  |            |

| 0230                        | RICDATE                         | 15:0      |              | DAY1    | 0<3:0>  |               |          | DAY01             | l<3:0>            |          | _                 | _        | -      |      |              | WDAYC   | )1<3:0> |       | xx00       |

| 0040                        |                                 | 31:16     |              | HR10    | )<3:0>  |               |          | HR01<3:0>         |                   |          |                   | MIN10<   | :3:0>  |      |              | MIN01   | <3:0>   |       | xxxx       |

| 0240                        | ALRMTIME                        | 15:0      |              | SEC1    | 0<3:0>  |               |          | SEC0 <sup>2</sup> | <3:0>             |          | _                 | _        | _      | —    | _            | —       | _       | _     | xx00       |

| 0050                        |                                 | 31:16     | _            |         | _       | —             | _        | _                 | _                 | _        |                   | MONTH1   | 0<3:0> |      |              | MONTH   | 01<3:0> |       | 00xx       |

| 0250                        | ALRMDATE                        | 15:0      |              | DAY1    | 0<3:0>  |               |          | DAY01<3:0>        |                   |          | — — — WDAY01<3:0> |          |        |      | xx0x         |         |         |       |            |

| l egen                      | ، بام                           |           | n voluo on D | aaati u |         | 0' as hear ha | Desetual |                   | المعديم والمرا    | alian al |                   |          |        |      |              |         |         |       |            |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|--------------------------|----------------------|--------------------|-------------------------|-----------------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0                      | U-0                  | U-0                | U-0                     | U-0                         | U-0               | U-0              | U-0              |  |

| 31.24        | _                        | —                    | —                  | —                       | —                           | —                 | _                | —                |  |

| 00.40        | U-0                      | U-0                  | U-0                | U-0                     | U-0                         | U-0               | U-0              | U-0              |  |

| 23:16        | _                        |                      | —                  | —                       | —                           |                   | _                | —                |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0                       | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | ) AMASK<3:0> <sup>(2)</sup> |                   |                  |                  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0                       | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | ARPT<7:0> <sup>(2)</sup> |                      |                    |                         |                             |                   |                  |                  |  |

## REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | U = Unimplemented bit, read as '0' |  |  |  |  |  |

|-------------------|-------------------------------|----------------------|------------------------------------|--|--|--|--|--|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown                 |  |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 **CHIME:** Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(3)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read.

The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

1111 = Reserved

- 1010 = Reserved

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half-second

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0 > = 0.0 and CHIME = 0.

- **2:** This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is only reset on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | _                 | -                 | ABAT              | REQOP<2:0>        |                  |                  |

| 22:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | _                 | —                | —                |