Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | -                                                                                 |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256lt-80v-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

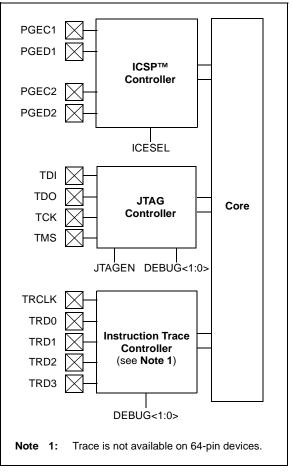

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB<sup>®</sup> REAL ICE<sup>TM</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) (DS50001765)

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" (DS50001764)

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" (DS50001616)

- "Using MPLAB<sup>®</sup> REAL ICE™ Emulator" (poster) (DS50001749)

### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 Trace

The trace pins can be connected to a hardware-traceenabled programmer to provide a compress real time instruction trace. When used for trace the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a  $22\Omega$  series resistor between the trace pins and the trace connector.

## 2.8 External Oscillator Pins

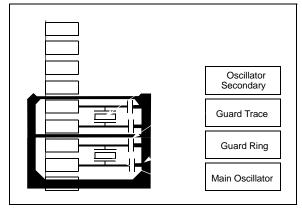

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator. Refer to **Section 8.0 "Oscillator Configuration"** for details.

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

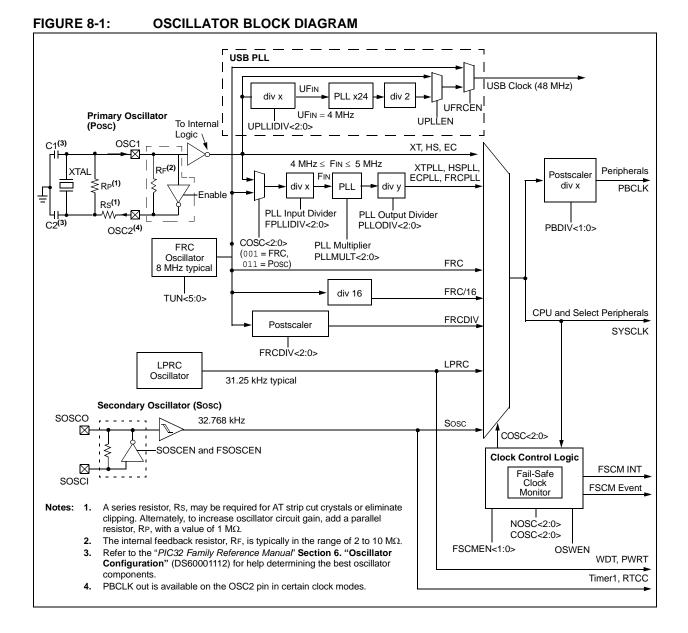

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

## PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 21.24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | CHEWEN            | —                 | _                 | —                 | —                 | -                 | —                | —                |  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | -                 | —                 |                   | —                 | —                 |                   | —                | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         |                   | —                 |                   | —                 | —                 |                   | —                | —                |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | —                 |                   | CHEID             | X<3:0>           |                  |  |  |  |  |  |

#### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31 CHEWEN: Cache Access Enable bits

- These bits apply to registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3.

- 1 = The cache line selected by CHEIDX<3:0> is writeable

- 0 = The cache line selected by CHEIDX<3:0> is not writeable

- bit 30-4 **Unimplemented:** Write '0'; ignore read

#### bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

#### 15.1 Control Registers

## TABLE 15-1: WATCHDOG TIMER REGISTER MAP

| ess                      |                                 |           |       |       |       |       |       |       |      | В    | its  |      |      |           |      |      |      |        | (2)        |

|--------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|-----------|------|------|------|--------|------------|

| Virtual Addr<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4      | 19/3 | 18/2 | 17/1 | 16/0   | All Resets |

| 0000                     | WDTOON                          | 31:16     | _     | —     | —     | —     | _     | _     | _    | _    | _    | _    | —    | —         | _    | —    | _    | _      | 0000       |

| 0000                     | WDTCON                          | 15:0      | ON    | _     |       | _     | _     | _     | _    | _    | _    |      | S    | WDTPS<4:0 | )>   |      | _    | WDTCLR | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of Reset.

#### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### 17.1 **Control Registers**

| ess                         |                                 |               |       |             |       |       |       |       |      | Bi    | ts       |      |          |       |        |      |              |      |            |

|-----------------------------|---------------------------------|---------------|-------|-------------|-------|-------|-------|-------|------|-------|----------|------|----------|-------|--------|------|--------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7     | 22/6 | 21/5     | 20/4  | 19/3   | 18/2 | 17/1         | 16/0 | All Resets |

|                             | OC1CON                          | 31:16         | _     | —           |       | —     | —     | _     |      | _     | _        |      | —        | -     | —      | _    | _            | _    | 0000       |

| 3000                        | OCICON                          | 15:0          | ON    | _           | SIDL  | _     | -     | -     | -    |       | _        |      | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

| 3010                        | OC1R                            | 31:16         |       |             |       |       |       |       |      | OC1R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

| 00.0                        |                                 | 15:0          |       |             |       |       |       |       |      | 00.11 | 101107   |      |          |       |        |      |              |      | XXXX       |

| 3020                        | OC1RS                           | 31:16         |       | OC1RS<31:0> |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

|                             |                                 | 15:0<br>31:16 | _     |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      |            |

| 3200                        | OC2CON                          | 15:0          | ON    | _           | SIDL  |       |       |       |      |       |          |      | <br>OC32 | OCFLT | OCTSEL |      | <br>OCM<2:0> | _    | 0000       |

|                             |                                 | 31:16         |       |             | OIDE  |       |       |       |      |       |          |      | 0002     | OOLEI | OUTOLL |      | 0011112.02   |      | xxxx       |

| 3210                        | OC2R                            | 15:0          |       |             |       |       |       |       |      | OC2R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

| 0000                        | 000000                          | 31:16         |       |             |       |       |       |       |      | 00000 |          |      |          |       |        |      |              |      | xxxx       |

| 3220                        | OC2RS                           | 15:0          |       |             |       |       |       |       |      | OC2RS | <31:0>   |      |          |       |        |      |              |      | xxxx       |

| 3400                        | OC3CON                          | 31:16         | -     | _           | _     | —     | —     | _     | _    | _     | _        | —    | —        | -     | —      | _    | —            | _    | 0000       |

| 3400                        | 003001                          | 15:0          | ON    | _           | SIDL  | —     | _     |       |      | _     | —        | —    | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

| 3410                        | OC3R                            | 31:16         |       |             |       |       |       |       |      | OC3R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

|                             |                                 | 15:0          |       |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      | XXXX       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |       |             |       |       |       |       |      | OC3R5 | <31:0>   |      |          |       |        |      |              |      | XXXX       |

|                             |                                 | 31:16         | _     | _           |       | _     | _     | _     | _    | _     |          | _    | _        | _     | _      |      |              | _    | xxxx 0000  |

| 3600                        | OC4CON                          | 15:0          | ON    |             | SIDL  | _     | _     | _     | _    | _     | _        | _    | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

|                             |                                 | 31:16         |       |             |       |       |       |       |      |       |          |      |          |       | ]      |      |              |      | xxxx       |

| 3610                        | OC4R                            | 15:0          |       |             |       |       |       |       |      | OC4R  | <31:0>   |      |          |       |        |      |              |      | xxxx       |

| 3620                        | OC4RS                           | 31:16         |       |             |       |       |       |       |      | OC4RS | -21:0    |      |          |       |        |      |              |      | xxxx       |

| 3020                        | 004K3                           | 15:0          |       |             |       |       |       |       |      | 00463 | \$<31.0> |      |          |       |        |      |              |      | xxxx       |

| 3800                        | OC5CON                          | 31:16         | _     | —           |       | —     | —     | _     |      | _     | _        | _    | —        | —     | —      |      | —            |      | 0000       |

| 0000                        |                                 | 15:0          | ON    | —           | SIDL  | —     | —     | —     | _    | —     | —        | —    | OC32     | OCFLT | OCTSEL |      | OCM<2:0>     |      | 0000       |

| 3810                        | OC5R                            | 31:16         |       |             |       |       |       |       |      | OC5R  | <31:0>   |      |          |       |        |      |              |      | XXXX       |

|                             |                                 | 15:0          |       |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      | xxxx       |

| 3820                        | OC5RS                           | 31:16<br>15:0 |       |             |       |       |       |       |      | OC5RS | 6<31:0>  |      |          |       |        |      |              |      | xxxx       |

|                             |                                 | 10.0          |       |             |       |       |       |       |      |       |          |      |          |       |        |      |              |      | 1 4444     |

PIC32MX5XX/6XX/7

### TABLE 17-1: OUTPUT COMPARE 1-OUTPUT COMPARE 5 REGISTER MAP

Legend:

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        |                   | —                 | _                 | _                 | —                 | —                 | —                | ADM_EN           |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | ADDR<7:0>         |                   |                   |                   |                   |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0             | R-0              | R-1              |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0, HS        | R-0              |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

| Legend:           | HS = Set by hardware | HC = Cleared by hardwar  | re                 |

|-------------------|----------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

- bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

- bit 13 UTXINV: Transmit Polarity Inversion bit

- If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

- bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by port.

- bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion.

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by port.

- bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

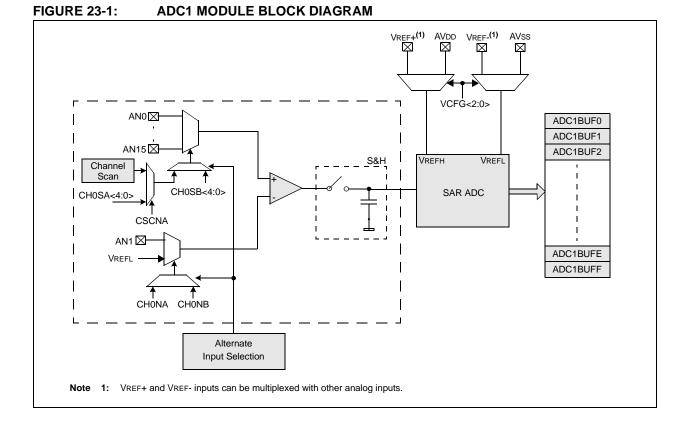

## 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104) in the "PIC32 Family Reference Manual", which is available from Microchip web the site (www.microchip.com/PIC32).

The PIC32MX5XX/6XX/7XX 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- Up to 16 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold (S&H) circuit

- Automatic Channel Scan mode

- Selectable conversion trigger source

- 16-word conversion result buffer

- · Selectable buffer fill modes

- Eight conversion result format options

- · Operation during Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 16 analog input pins, designated AN0-AN15. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

The analog inputs are connected through two multiplexers to one S&H. The analog input multiplexers can be switched between two sets of analog inputs between conversions. Unipolar differential conversions are possible on all channels, other than the pin used as the reference, using a reference input pin (see Figure 23-1).

The Analog Input Scan mode sequentially converts user-specified channels. A control register specifies which analog input channels will be included in the scanning sequence.

The 10-bit ADC is connected to a 16-word result buffer. Each 10-bit result is converted to one of eight 32-bit output formats when it is read from the result buffer.

## PIC32MX5XX/6XX/7XX

| REGIST | ER 24-21:  | CiFIFOIN   | Tn: CAN F  |            |            | GISTER 'n' (n | = 0 THROU | GH 31)    |

|--------|------------|------------|------------|------------|------------|---------------|-----------|-----------|

| Bit    | Bit        | Bit        | Bit        | Bit        | Bit        | Bit           | Bit       | Bit       |

| Range  | 31/23/15/7 | 30/22/14/6 | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2    | 25/17/9/1 | 24/16/8/0 |

| Range | 31/23/15/7 | 30/22/14/6      | 29/21/13/5 | 28/20/12/4 | 27/19/11/3 | 26/18/10/2               | 25/17/9/1               | 24/16/8/0                 |

|-------|------------|-----------------|------------|------------|------------|--------------------------|-------------------------|---------------------------|

| 24.24 | U-0        | U-0             | U-0        | U-0        | U-0        | R/W-0                    | R/W-0                   | R/W-0                     |

| 31:24 | —          | - <u> </u>      |            |            | TXNFULLIE  | TXHALFIE                 | TXEMPTYIE               |                           |

| 00.40 | U-0        | U-0             | U-0        | U-0        | R/W-0      | R/W-0                    | R/W-0                   | R/W-0                     |

| 23:16 | —          |                 |            |            | RXOVFLIE   | RXFULLIE                 | RXHALFIE                | RXNEMPTYIE                |

| 15.0  | U-0        | U-0             | U-0        | U-0        | U-0        | R-0                      | R-0                     | R-0                       |

| 15:8  | —          | _               |            | _          |            | TXNFULLIF <sup>(1)</sup> | TXHALFIF                | TXEMPTYIF <sup>(1)</sup>  |

| 7.0   | U-0        | U-0 U-0 U-0 R/W |            | R/W-0      | R-0        | R-0                      | R-0                     |                           |

| 7:0   | _          | _               | _          | _          | RXOVFLIF   | RXFULLIF <sup>(1)</sup>  | RXHALFIF <sup>(1)</sup> | RXNEMPTYIF <sup>(1)</sup> |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

|-------------------|------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-27 Unimplemented: Read as '0'

| bit 26    | TXNFULLIE: Transmit FIFO Not Full Interrupt Enable bit                                                          |

|-----------|-----------------------------------------------------------------------------------------------------------------|

|           | <ol> <li>Interrupt enabled for FIFO not full</li> <li>Interrupt disabled for FIFO not full</li> </ol>           |

| bit 25    | TXHALFIE: Transmit FIFO Half Full Interrupt Enable bit                                                          |

|           | <ul> <li>1 = Interrupt enabled for FIFO half full</li> <li>0 = Interrupt disabled for FIFO half full</li> </ul> |

| bit 24    | TXEMPTYIE: Transmit FIFO Empty Interrupt Enable bit                                                             |

|           | <ul> <li>1 = Interrupt enabled for FIFO empty</li> <li>0 = Interrupt disabled for FIFO empty</li> </ul>         |

| bit 23-20 | Unimplemented: Read as '0'                                                                                      |

| bit 19    | RXOVFLIE: Overflow Interrupt Enable bit                                                                         |

|           | 1 = Interrupt enabled for overflow event                                                                        |

|           | 0 = Interrupt disabled for overflow event                                                                       |

| bit 18    | RXFULLIE: Full Interrupt Enable bit                                                                             |

|           | 1 = Interrupt enabled for FIFO full                                                                             |

| L:47      | 0 = Interrupt disabled for FIFO full                                                                            |

| bit 17    | RXHALFIE: FIFO Half Full Interrupt Enable bit                                                                   |

|           | <ul> <li>1 = Interrupt enabled for FIFO half full</li> <li>0 = Interrupt disabled for FIFO half full</li> </ul> |

| bit 16    | <b>RXNEMPTYIE:</b> Empty Interrupt Enable bit                                                                   |

|           | 1 = Interrupt enabled for FIFO not empty                                                                        |

|           | 0 = Interrupt disabled for FIFO not empty                                                                       |

| bit 15-11 | Unimplemented: Read as '0'                                                                                      |

| bit 10    | TXNFULLIF: Transmit FIFO Not Full Interrupt Flag bit <sup>(1)</sup>                                             |

|           | <u>TXEN = 1:</u> (FIFO configured as a transmit buffer)                                                         |

|           | 1 = FIFO is not full<br>0 = FIFO is full                                                                        |

|           |                                                                                                                 |

|           | <u>TXEN = 0:</u> (FIFO configured as a receive buffer)<br>Unused, reads '0'                                     |

|           |                                                                                                                 |

**Note 1:** This bit is read-only and reflects the status of the FIFO.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|--|--|

| 24.24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |

| 31:24     |                   | PTV<15:8>         |                   |                   |                   |                   |                  |                     |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |  |  |

| 23:16     |                   |                   |                   | PTV<              | :7:0>             |                   |                  |                     |  |  |

| 45.0      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0               |  |  |

| 15:8      | ON                | —                 | SIDL              | _                 | _                 | _                 | TXRTS            | RXEN <sup>(1)</sup> |  |  |

| 7:0       | R/W-0             | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0               |  |  |

| 7:0       | AUTOFC            |                   | _                 | MANFC             | _                 |                   |                  | BUFCDEC             |  |  |

#### REGISTER 25-1: ETHCON1: ETHERNET CONTROLLER CONTROL REGISTER 1

#### Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 PTV<15:0>: PAUSE Timer Value bits PAUSE Timer Value used for Flow Control. This register should only be written when RXEN (ETHCON1<8>) is not set. These bits are only used for Flow Control operations. bit 15 **ON:** Ethernet ON bit 1 = Ethernet module is enabled 0 = Ethernet module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Ethernet Stop in Idle Mode bit 1 = Ethernet module transfers are paused during Idle mode 0 = Ethernet module transfers continue during Idle mode bit 12-10 Unimplemented: Read as '0' bit 9 TXRTS: Transmit Request to Send bit 1 = Activate the TX logic and send the packet(s) defined in the TX EDT 0 = Stop transmit (when cleared by software) or transmit done (when cleared by hardware)

After the bit is written with a '1', it will clear to a '0' whenever the transmit logic has finished transmitting the requested packets in the Ethernet Descriptor Table (EDT). If a '0' is written by the CPU, the transmit logic finishes the current packet's transmission and then stops any further.

This bit only affects TX operations.

#### bit 8 **RXEN:** Receive Enable bit<sup>(1)</sup>

- 1 = Enable RX logic, packets are received and stored in the RX buffer as controlled by the filter configuration

- 0 = Disable RX logic, no packets are received in the RX buffer

This bit only affects RX operations.

**Note 1:** It is not recommended to clear the RXEN bit and then make changes to any RX related field/register. The Ethernet Controller must be reinitialized (ON cleared to '0'), and then the RX changes applied.

## PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31.24        |                   |                   |                   | HT<3              | 1:24>             |                   |                  |                  |  |  |  |

| 22.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | HT<23:16>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | HT<1              | 5:8>              |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | HT<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 25-5: ETHHT0: ETHERNET CONTROLLER HASH TABLE 0 REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 HT<31:0>: Hash Table Bytes 0-3 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

#### REGISTER 25-6: ETHHT1: ETHERNET CONTROLLER HASH TABLE 1 REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24     |                   |                   |                   | HT<6              | 3:56>             |                   |                  |                  |  |  |

| 00.40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | HT<55:48>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | HT<47:40>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | HT<39:32>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 HT<63:32>: Hash Table Bytes 4-7 bits

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0 or the HTEN bit (ETHRXFC<15>) = 0.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | _                 | _                 | -                 |                   |                   |                   |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | _                 | _                 | _                 | _                 | —                 | -                 | _                | _                |

| 15:8      | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 10.0      | _                 | TXBUSE            | RXBUSE            | _                 | _                 | _                 | EWMARK           | FWMARK           |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0       | RXDONE            | PKTPEND           | RXACT             | _                 | TXDONE            | TXABORT           | RXBUFNA          | RXOVFLW          |

#### **REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

| bit 31-15 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14    | TXBUSE: Transmit BVCI Bus Error Interrupt bit                                                                                                                                                                                                                   |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the TX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 13    | RXBUSE: Receive BVCI Bus Error Interrupt bit                                                                                                                                                                                                                    |

|           | 1 = BVCI Bus Error has occurred<br>0 = BVCI Bus Error has not occurred                                                                                                                                                                                          |

|           | This bit is set when the RX DMA encounters a BVCI Bus error during a memory access. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                  |

| bit 12-10 | Unimplemented: Read as '0'                                                                                                                                                                                                                                      |

| bit 9     | EWMARK: Empty Watermark Interrupt bit                                                                                                                                                                                                                           |

|           | <ul><li>1 = Empty Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                          |

|           | This bit is set when the RX Descriptor Buffer Count is less than or equal to the value in the RXEWM bit (ETHRXWM<0:7>) value. It is cleared by BUFCNT bit (ETHSTAT<16:23>) being incremented by hardware. Writing a '0' or a '1' has no effect.                 |

| bit 8     | FWMARK: Full Watermark Interrupt bit                                                                                                                                                                                                                            |

|           | <ul><li>1 = Full Watermark pointer reached</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                           |

|           | This bit is set when the RX Descriptor Buffer Count is greater than or equal to the value in the RXFWM bit (ETHRXWM<16:23>) field. It is cleared by writing the BUFCDEC (ETHCON1<0>) bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect. |

| bit 7     | RXDONE: Receive Done Interrupt bit                                                                                                                                                                                                                              |

|           | <ul><li>1 = RX packet was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                                      |

|           | This bit is set whenever an RX packet is successfully received. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                      |

|           |                                                                                                                                                                                                                                                                 |

| Note:     | It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.                                                                    |

## REGISTER 25-27: EMAC1CLRT: ETHERNET CONTROLLER MAC COLLISION WINDOW/RETRY LIMIT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 15:8         | U-0               | U-0               | R/W-1             | R/W-1             | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 10.0         |                   | —                 |                   |                   | CWINDO            | W<5:0>            |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 7.0          | _                 |                   | _                 | _                 |                   | RETX<             | <3:0>            |                  |

#### Legend:

| Logonal           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13-8 **CWINDOW<5:0>:** Collision Window bits

This is a programmable field representing the slot time or collision window during which collisions occur in properly configured networks. Since the collision window starts at the beginning of transmission, the preamble and SFD is included. Its default of 0x37 (55d) corresponds to the count of frame bytes at the end of the window.

bit 7-4 Unimplemented: Read as '0'

#### bit 3-0 RETX<3:0>: Retransmission Maximum bits

This is a programmable field specifying the number of retransmission attempts following a collision before aborting the packet due to excessive collisions. The Standard specifies the maximum number of attempts (attemptLimit) to be 0xF (15d). Its default is '0xF'.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

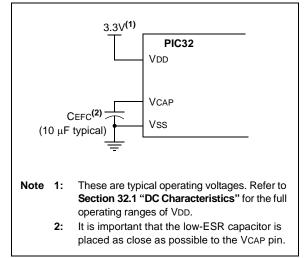

## 29.2 On-Chip Voltage Regulator

All PIC32MX5XX/6XX/7XX devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX-5XX/6XX/7XX family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 29-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 32.1 "DC Characteristics"**.

Note: It is important that the low-ESR capacitor is placed as close as possible to the VCAP pin.

### 29.2.1 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

#### 29.2.2 ON-CHIP REGULATOR AND BOR

PIC32MX5XX/6XX/7XX devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset (BOR). This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specified in **Section 32.1 "DC Characteristics"**.

## FIGURE 29-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

#### 29.3 **Programming and Diagnostics**

PIC32MX5XX/6XX/7XX devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 29-2:

PROGRAMMING, DEBUGGING, AND TRACE PORTS BLOCK DIAGRAM

#### TABLE 32-14: VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        | RACTERI | STICS                                                        | Standard<br>(unless of<br>Operating | otherwise | ture -40°C         | $\leq$ TA $\leq$ +8 | <b>to 3.6V</b><br>85°C for Industrial<br>105°C for V-Temp       |

|---------------|---------|--------------------------------------------------------------|-------------------------------------|-----------|--------------------|---------------------|-----------------------------------------------------------------|

| Param.<br>No. | Symbol  | Characteristics                                              | Min.                                | Typical   | Max.               | Units               | Comments                                                        |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                   | _         | 10                 | μs                  | See Note 1                                                      |

| D313          | DACREFH | CVREF Input Voltage                                          | AVss                                | _         | AVdd               | V                   | CVRSRC with CVRSS = 0                                           |

|               |         | Reference Range                                              | VREF-                               | _         | VREF+              | V                   | CVRSRC with CVRSS = 1                                           |

| D314          | DVref   | CVREF Programmable<br>Output Range                           | 0                                   | —         | 0.625 x<br>DACREFH | V                   | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |

|               |         |                                                              | 0.25 x<br>DACREFH                   | —         | 0.719 x<br>DACREFH | V                   | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/32<br>step size |

| D315          | DACRES  | Resolution                                                   | —                                   | _         | DACREFH/<br>24     |                     | CVRCON <cvrr> = 1</cvrr>                                        |

|               |         |                                                              | —                                   | —         | DACREFH/<br>32     |                     | CVRCON <cvrr> = 0</cvrr>                                        |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                             | —                                   | _         | 1/4                | LSB                 | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |

|               |         |                                                              | —                                   | _         | 1/2                | LSB                 | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

2: These parameters are characterized but not tested.

#### TABLE 32-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | (unles                           | ard Operat<br>s otherwis<br>ing temper | se stated<br>ature | <b>d)</b><br>-40°C ≤ <sup>·</sup> | : <b>2.3V to 3.6V</b><br>TA $\leq$ +85°C for Industrial<br>TA $\leq$ +105°C for V-Temp |

|--------------------|--------|---------------------------------|----------------------------------|----------------------------------------|--------------------|-----------------------------------|----------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | Min. Typical Max. Units Comments |                                        |                    |                                   | Comments                                                                               |

| D321               | Cefc   | External Filter Capacitor Value | 8                                | 10                                     | —                  | μF                                | Capacitor must be low series resistance (1 ohm)                                        |

| D322               | TPWRT  | Power-up Timer Period           | _                                | 64                                     | _                  | ms                                | —                                                                                      |

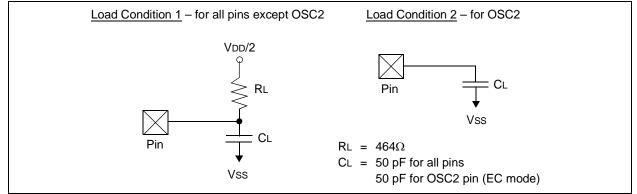

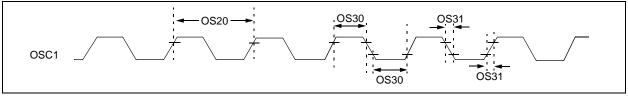

#### 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX5XX/6XX/7XX AC characteristics and timing parameters.

#### FIGURE 32-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

#### TABLE 32-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       | $\label{eq:standard operating Conditions: 2.3V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                        |      |       |                                                                         |

|--------------------|--------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|-------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics       | Min.                                                                                                                       | Typical <sup>(1)</sup> | Max. | Units | Conditions                                                              |

| DO50               | Cosco  | OSC2 pin              |                                                                                                                            | _                      | 15   | pF    | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1 |

| DO56               | Сю     | All I/O pins and OSC2 |                                                                                                                            | —                      | 50   | pF    | In EC mode                                                              |

| DO58               | Св     | SCLx, SDAx            |                                                                                                                            | —                      | 400  | pF    | In I <sup>2</sup> C mode                                                |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

#### FIGURE 32-2: EXTERNAL CLOCK TIMING

#### 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 7.15 x 7.15 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units    | Ν        | <b>ILLIMETER</b> | S    |

|------------------------|----------|----------|------------------|------|

| Dimensio               | n Limits | MIN      | NOM              | MAX  |

| Number of Pins         | N        |          | 64               |      |

| Pitch                  | е        |          | 0.50 BSC         |      |

| Overall Height         | A        | 0.80     | 0.90             | 1.00 |

| Standoff               | A1       | 0.00     | 0.02             | 0.05 |

| Contact Thickness      | A3       | 0.20 REF |                  |      |

| Overall Width          | E        |          | 9.00 BSC         |      |

| Exposed Pad Width      | E2       | 7.05     | 7.15             | 7.50 |

| Overall Length         | D        | 9.00 BSC |                  |      |

| Exposed Pad Length     | D2       | 7.05     | 7.15             | 7.50 |

| Contact Width          | b        | 0.18     | 0.25             | 0.30 |

| Contact Length         | L        | 0.30     | 0.40             | 0.50 |

| Contact-to-Exposed Pad | K        | 0.20     | -                | -    |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Package is saw singulated.

- 3. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-149C Sheet 2 of 2

## APPENDIX B: REVISION HISTORY

## **Revision A (August 2009)**

This is the initial released version of this document.

## **Revision B (November 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits.

Other major changes are referenced by their respective chapter/section in Table B-1.

| Section Name                                                                  | Update Description                                                                                                                                                       |

|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, USB, CAN and<br>Ethernet 32-bit Flash<br>Microcontrollers" | Added the following devices:<br>- PIC32MX575F256L<br>- PIC32MX695F512L                                                                                                   |

|                                                                               | <ul> <li>PIC32MX695F512H</li> <li>The 100-pin TQFP pin diagrams have been updated to reflect the current pin name locations (see the "Pin Diagrams" section).</li> </ul> |

|                                                                               | Added the 121-pin Ball Grid Array (XBGA) pin diagram.                                                                                                                    |

|                                                                               | Updated Table 1: "PIC32 USB and CAN – Features"                                                                                                                          |

|                                                                               | Added the following tables:                                                                                                                                              |

|                                                                               | <ul> <li>Table 4: "Pin Names: PIC32MX534F064L, PIC32MX564F064L,<br/>PIC32MX564F128L, PIC32MX575F256L and PIC32MX575F512L<br/>Devices"</li> </ul>                         |

|                                                                               | <ul> <li>Table 5: "Pin Names: PIC32MX664F064L, PIC32MX664F128L,<br/>PIC32MX675F256L, PIC32MX675F512L and PIC32MX695F512L<br/>Devices"</li> </ul>                         |

|                                                                               | <ul> <li>Table 6: "Pin Names: PIC32MX775F256L, PIC32MX775F512L and<br/>PIC32MX795F512L Devices"</li> </ul>                                                               |

|                                                                               | Updated the following pins as 5V tolerant:                                                                                                                               |

|                                                                               | - 64-pin QFN: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)                                                                                                                        |

|                                                                               | <ul> <li>64-pin TQFP: Pin 36 (D-/RG3) and Pin 37 (D+/RG2)</li> <li>100-pin TQFP: Pin 56 (D-/RG3) and Pin 57 (D+/RG2)</li> </ul>                                          |

| 1.0 "Guidelines for Getting Started                                           | Removed the last sentence of 1.3.1 "Internal Regulator Mode".                                                                                                            |

| with 32-bit Microcontrollers"                                                 | Removed Section 2.3.2 "External Regulator Mode"                                                                                                                          |

#### TABLE B-1: MAJOR SECTION UPDATES

### **Revision J (September 2016)**

This revision includes typographical and formatting updates throughout the data sheet text. In addition, all SFR Register maps were moved from the Memory chapter to their respective peripheral chapters.

All other major updates are referenced by their respective section in Table B-7.

| Section Name                                                                     | Update Description                                                                                                      |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 512                                              | Updated Communication Interfaces for LIN support to 2.1.                                                                |

| KB Flash and 128 KB SRAM) with<br>Graphics Interface, USB, CAN, and<br>Ethernet" | Updated Qualification and Class B Support to AEC-Q100 REVH.                                                             |

| 2.0 "Guidelines for Getting Started with 32-bit MCUs"                            | The Recommended Minimum Connection diagram was updated (see Figure 2-1).                                                |

|                                                                                  | The Example of MCLR Pin Connections diagram was updated (see Figure 2-<br>2).                                           |

|                                                                                  | 2.11 "EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations" was added.                              |

| 4.0 "Memory Organization"                                                        | The SFR Memory Map was added (see Table 4-1).                                                                           |

| 7.0 "Interrupt Controller"                                                       | The UART interrupt sources were updated in the Interrupt IRQ, Vector, and Bit location table (see Table 7-1).           |

| 8.0 "Oscillator Configuration"                                                   | Updated the bit value definitions for the TUN<5:0> bits in the OCSTUN register (see Register 8-2).                      |

| 15.0 "Watchdog Timer (WDT)"                                                      | The content in this chapter was relocated from the Special Features chapter to its own chapter.                         |

| 18.0 "Serial Peripheral Interface (SPI)"                                         | The register map tables were combined (see Table 18-1).                                                                 |

| 19.0 "Inter-Integrated Circuit (I <sup>2</sup> C)"                               | The register map tables were combined (see Table 19-1).                                                                 |

|                                                                                  | The PMADDR register was updated (see Register 21-3).                                                                    |

| 21.0 "Parallel Master Port (PMP)"                                                | The bit value definitions for the ADRMUX<1:0> and CSF<1:0> bits in the PMCON register were updated (see Register 21-1). |

| 29.0 "Special Features"                                                          | Removed the duplicate bit value definition for '010' in the DEVCFG2 register (see Register 29-3).                       |

|                                                                                  | Note 1 was added to the Programming, Debugging, and Trace Ports block diagram (see Figure 29-2).                        |

|                                                                                  | The DDPCON register was relocated (see Register 29-6).                                                                  |

|                                                                                  | The Device ID, Revision, and Configuration Summary was updated (see Table 29-2).                                        |

# PIC32MX5XX/6XX/7XX

| Oscillator Configuration                | 95  |

|-----------------------------------------|-----|

| Output Compare                          | 185 |

| Ρ                                       |     |

| Packaging                               | 401 |

| Details                                 |     |

| Marking                                 | 401 |

| Parallel Master Port (PMP)              | 211 |

| PIC32 Family USB Interface Diagram      | 134 |

| PICkit 3 In-Circuit Debugger/Programmer |     |

| Pinout I/O Descriptions (table)         | 26  |

| Power-on Reset (POR)                    |     |

| and On-Chip Voltage Regulator           | 343 |

| Power-Saving Features                   | 331 |

| CPU Halted Methods                      | 331 |

| Operation                               | 331 |

| with CPU Running                        | 331 |

| Prefetch Cache                          | 101 |

| Program Flash Memory                    |     |

| Wait State Characteristics              | 363 |

## R

| Real-Time Clock and Calendar (RTCC)                  | .221   |

|------------------------------------------------------|--------|

| Register Maps 55-                                    | -283   |

| Registers                                            |        |

| AD1CHS (ADC Input Select)                            | . 239  |

| AD1CON1 (ADC Control 1)                              | . 235  |

| AD1CON2 (ADC Control 2)                              |        |

| AD1CON3 (ADC Control 3)                              |        |

| AD1CSSL (ADC Input Scan Select)                      | . 240  |

| ALRMDATE (Alarm Date Value)                          | . 230  |

| ALRMTIME (Alarm Time Value)                          | . 229  |

| BMXBOOTSZ (Boot Flash (IFM) Size)                    | 61     |

| BMXCON (Bus Matrix Configuration)                    | 56     |

| BMXDKPBA (Data RAM Kernel Program                    |        |

| Base Address)                                        | 57     |

| BMXDRMSZ (Data RAM Size)                             | 60     |

| BMXDUDBA (Data RAM User Data Base Address)           | 58     |

| BMXDUPBA (Data RAM User Program                      |        |

| Base Address)                                        | 59     |

| BMXPFMSZ (Program Flash (PFM) Size)                  | 61     |

| BMXPUPBA (Program Flash (PFM) User Program           |        |

| Base Address)                                        | 60     |

| CHEACC (Cache Access)                                | . 104  |

| CHECON (Cache Control)                               | . 103  |

| CHEHIT (Cache Hit Statistics)                        | . 109  |

| CHELRU (Cache LRU)                                   | . 108  |

| CHEMIS (Cache Miss Statistics)                       | . 109  |

| CHEMSK (Cache TAG Mask)                              | . 106  |

| CHETAG (Cache TAG)                                   | . 105  |

| CHEW0 (Cache Word 0)                                 | . 106  |

| CHEW1 (Cache Word 1)                                 | . 107  |

| CHEW2 (Cache Word 2)                                 | . 107  |

| CHEW3 (Cache Word 3)                                 |        |

| CiCFG (CAN Baud Rate Configuration)                  | . 248  |

| CiCON (CAN Module Control)                           | .246   |

| CiFIFOBA (CAN Message Buffer Base Address)           | .273   |

| CiFIFOCINn (CAN Module Message Index Register<br>278 | ′ 'n') |

| CiFIFOCONn (CAN FIFO Control Register 'n')           | .274   |

| CiFIFOINTn (CAN FIFO Interrupt Register 'n')         |        |

| CiFIFOUAn (CAN FIFO User Address Register 'n').      |        |

| CiFLTCON0 (CAN Filter Control 0)                     |        |

| CiFLTCON1 (CAN Filter Control 1)                     |        |

| CiFLTCON2 (CAN Filter Control 2)                     |        |

| CiFLTCON3 (CAN Filter Control 3)                     |        |

|                                                      |        |