Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256lt-80v-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX5XX/6XX/7XX

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                               | Pin Nun         | nber <sup>(1)</sup> |                 | D:          | Duffer               |                                                   |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|-------------|----------------------|---------------------------------------------------|

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                       |

| RG0      | —                                             | 90              | A5                  | A61             | I/O         | ST                   | PORTG is a bidirectional I/O port                 |

| RG1      | —                                             | 89              | E6                  | B50             | I/O         | ST                   |                                                   |

| RG6      | 4                                             | 10              | E3                  | A7              | I/O         | ST                   |                                                   |

| RG7      | 5                                             | 11              | F4                  | B6              | I/O         | ST                   |                                                   |

| RG8      | 6                                             | 12              | F2                  | A8              | I/O         | ST                   |                                                   |

| RG9      | 8                                             | 14              | F3                  | A9              | I/O         | ST                   |                                                   |

| RG12     | —                                             | 96              | C3                  | A65             | I/O         | ST                   |                                                   |

| RG13     | —                                             | 97              | A3                  | B55             | I/O         | ST                   | -                                                 |

| RG14     | —                                             | 95              | C4                  | B54             | I/O         | ST                   |                                                   |

| RG15     | —                                             | 1               | B2                  | A2              | I/O         | ST                   |                                                   |

| RG2      | 37                                            | 57              | H10                 | B31             | Ι           | ST                   | PORTG input pins                                  |

| RG3      | 36                                            | 56              | J11                 | A38             | I           | ST                   |                                                   |

| T1CK     | 48                                            | 74              | B11                 | B40             |             | ST                   | Timer1 external clock input                       |

| T2CK     | —                                             | 6               | D1                  | A5              | I           | ST                   | Timer2 external clock input                       |

| T3CK     | —                                             | 7               | E4                  | B4              |             | ST                   | Timer3 external clock input                       |

| T4CK     | —                                             | 8               | E2                  | A6              |             | ST                   | Timer4 external clock input                       |

| T5CK     | —                                             | 9               | E1                  | B5              |             | ST                   | Timer5 external clock input                       |

| U1CTS    | 43                                            | 47              | L9                  | B26             |             | ST                   | UART1 clear to send                               |

| U1RTS    | 49                                            | 48              | K9                  | A31             | 0           |                      | UART1 ready to send                               |

| U1RX     | 50                                            | 52              | K11                 | A36             | I           | ST                   | UART1 receive                                     |

| U1TX     | 51                                            | 53              | J10                 | B29             | 0           | _                    | UART1 transmit                                    |

| U3CTS    | 8                                             | 14              | F3                  | A9              | I           | ST                   | UART3 clear to send                               |

| U3RTS    | 4                                             | 10              | E3                  | A7              | 0           | _                    | UART3 ready to send                               |

| U3RX     | 5                                             | 11              | F4                  | B6              | I           | ST                   | UART3 receive                                     |

| U3TX     | 6                                             | 12              | F2                  | A8              | 0           | _                    | UART3 transmit                                    |

| U2CTS    | 21                                            | 40              | K6                  | A27             | I           | ST                   | UART2 clear to send                               |

| U2RTS    | 29                                            | 39              | L6                  | B22             | 0           |                      | UART2 ready to send                               |

| U2RX     | 31                                            | 49              | L10                 | B27             | I           | ST                   | UART2 receive                                     |

| U2TX     | 32                                            | 50              | L11                 | A32             | 0           |                      | UART2 transmit                                    |

| U4RX     | 43                                            | 47              | L9                  | B26             | 1           | ST                   | UART4 receive                                     |

| U4TX     | 49                                            | 48              | K9                  | A31             | 0           | _                    | UART4 transmit                                    |

| U6RX     | 8                                             | 14              | F3                  | A9              | I           | ST                   | UART6 receive                                     |

| U6TX     | 4                                             | 10              | E3                  | A7              | 0           | _                    | UART6 transmit                                    |

| U5RX     | 21                                            | 40              | K6                  | A27             | 1           | ST                   | UART5 receive                                     |

| U5TX     | 29                                            | 39              | L6                  | B22             | 0           |                      | UART5 transmit                                    |

| SCK1     | _                                             | 70              | D11                 | B38             | I/O         | ST                   | Synchronous serial clock input/output<br>for SPI1 |

| 5        | CMOS = CMO<br>ST = Schmitt T<br>TL = TTL inpu | rigger input    |                     |                 |             | nalog = A<br>= Outpu | Analog input P = Power                            |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

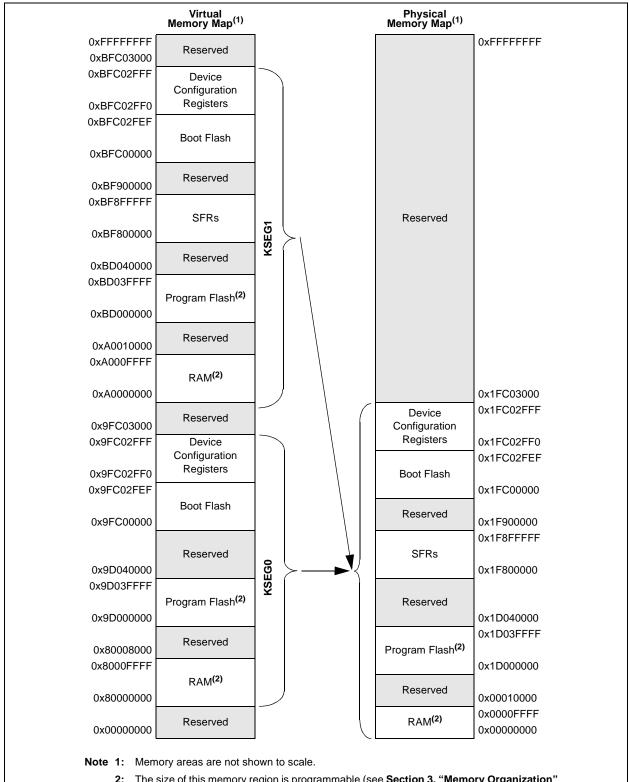

#### FIGURE 4-4: MEMORY MAP ON RESET FOR PIC32MX575F256H, PIC32MX575F256L, PIC32MX675F256H, PIC32MX675F256L, PIC32MX775F256H AND PIC32MX775F256L DEVICES

2: The size of this memory region is programmable (see Section 3. "Memory Organization" (DS60001115)) and can be changed by initialization code provided by end user development tools (refer to the specific development tool documentation for information).

# TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |                                                                                  |             |             |             | Bi                    | its         |                                        |             |             |             |              |                |             |            |             |             |             |        |        |      |   |            |   |       |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|----------------------------------------------------------------------------------|-------------|-------------|-------------|-----------------------|-------------|----------------------------------------|-------------|-------------|-------------|--------------|----------------|-------------|------------|-------------|-------------|-------------|--------|--------|------|---|------------|---|-------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12                                                                            | 27/11       | 26/10       | 25/9        | 24/8                  | 23/7        | 22/6                                   | 21/5        | 20/4        | 19/3        | 18/2         | 17/1           | 16/0        | All Resets |             |             |             |        |        |      |   |            |   |       |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |                                                                                  | INT4IP<2:0> |             | INT4IS      | S<1:0>                | _           | —                                      | -           |             | OC4IP<2:0>  |              | OC4IS          | 6<1:0>      | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |                                                                                  | IC4IP<2:0>  |             | IC4IS       | <1:0>                 | _           | _                                      | _           |             | T4IP<2:0>   |              | T4IS-          | <1:0>       | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     | SPI1IP<2:0>                                                                      |             |             | SPI1IP<2:0> |                       | SPI1IP<2:0> |                                        | 6<1:0>      | _           | _           | _            |                | OC5IP<2:0>  |            | OC5IS       | S<1:0>      | 0000        |        |        |      |   |            |   |       |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |                                                                                  | IC5IP<2:0>  |             | IC5IS       | <1:0>                 | -           |                                        | _           | T5IP<2:0>   |             |              | T5IS-          | <1:0>       | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

|                             |                                 | 31:16     | _     | _     | _     |                                                                                  | AD1IP<2:0>  |             | AD1IS       | S<1:0>                | _           | _                                      | _           |             | CNIP<2:0>   |              | CNIS           | <1:0>       | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 10F0                        | IPC6                            |           |       |       |       |                                                                                  |             |             |             |                       |             |                                        |             |             | U1IP<2:0>   |              | U1IS-          | <1:0>       |            |             |             |             |        |        |      |   |            |   |       |        |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |                                                                                  | I2C1IP<2:0> |             | I2C1IP<2:0> |                       | I2C1IP<2:0> |                                        | I2C1IP<2:0> |             | 12C115      | S<1:0>       | —              | —           | —          |             | SPI3IP<2:0> | •           | SPI3IS | S<1:0> | 0000 |   |            |   |       |        |      |

|                             |                                 |           |       |       |       |                                                                                  |             |             |             |                       |             |                                        |             |             | I2C3IP<2:0> |              | 12C315         | S<1:0>      |            |             |             |             |        |        |      |   |            |   |       |        |      |

|                             |                                 |           |       |       |       |                                                                                  | U3IP<2:0>   |             | U3IS        | <1:0>                 |             |                                        |             |             |             |              |                |             |            |             |             |             |        |        |      |   |            |   |       |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |                                                                                  | SPI2IP<2:0> |             | SPI2IS      | S<1:0>                | —           | —                                      | —           | (           | CMP2IP<2:0  | >            | CMP2I          | S<1:0>      | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1100                        | 11 07                           |           |       |       |       |                                                                                  | I2C4IP<2:0> |             | 12C415      | S<1:0>                |             |                                        |             |             |             |              |                |             |            |             |             |             |        |        |      |   |            |   |       |        |      |

|                             |                                 | 15:0      | _     |       |       | (                                                                                | CMP1IP<2:0> |             | CMP1I       | S<1:0>                | _           | _                                      |             |             | PMPIP<2:0>  |              | PMPIS          | S<1:0>      | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

|                             |                                 | 31:16     | _     |       |       | RTCCIP<2:0>                                                                      |             | RTCCIP<2:0> |             | RTCCIP<2:0>           |             | RTCCIP<2:0>                            |             | RTCCIP<2:0> |             | RTCCIP<2:0>  |                | RTCCIP<2:0> |            | RTCCIS<1:0> |             | RTCCIS<1:0> |        | _      |      | I | FSCMIP<2:0 | > | FSCMI | S<1:0> | 0000 |

| 1110                        | IPC8                            |           |       |       |       |                                                                                  |             |             |             |                       |             |                                        |             |             | U2IP<2:0>   |              | U2IS-          | <1:0>       |            |             |             |             |        |        |      |   |            |   |       |        |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     | I2C2IP<2:0>                                                                      |             |             | I2C2IP<2:0> |                       |             | I2C2IP<2:0>                            |             |             | 12C215      | 6<1:0>       | —              | —           | —          |             | SPI4IP<2:0> |             | SPI4IS | S<1:0> | 0000 |   |            |   |       |        |      |

|                             |                                 |           |       |       |       |                                                                                  |             |             |             |                       |             |                                        |             |             | I2C5IP<2:0> |              | 12C515         | S<1:0>      |            |             |             |             |        |        |      |   |            |   |       |        |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |                                                                                  | DMA3IP<2:0  |             | DMA3I       | S<1:0>                | _           |                                        |             |             | DMA2IP<2:0  |              | DMA2I          | S<1:0>      | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |                                                                                  | DMA1IP<2:0  |             | DMA1I       |                       | _           |                                        |             |             | DMA0IP<2:0  |              | DMA0I          | S<1:0>      | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DMA7IP<2:0> <sup>(2)</sup> DMA7IS<1:0> <sup>(2)</sup> DMA6IP<2:0> <sup>(2)</sup> |             | (2)         | DMA6IS      | <1:0> <sup>(2)</sup>  | 0000        |                                        |             |             |             |              |                |             |            |             |             |             |        |        |      |   |            |   |       |        |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI                                                                               | MA5IP<2:0>  | (2)         | DMA5IS      | i<1:0> <sup>(2)</sup> | _           | _                                      | —           | D           | MA4IP<2:0>  | (2)          | DMA4IS<1:0>(2) |             | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _                                                                                | _           |             | _           |                       |             |                                        | _           | _           | —           |              |                |             | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     | USBIP<2:0>                                                                       |             | USBIP<2:0>  |             | USBIP<2:0>            |             | USBIP<2:0> USBIS<1:0> — — — FCEIP<2:0> |             | USBIP<2:0>  |             | – FCEIP<2:0> |                | FCEIS<1:0>  |            | 0000        |             |             |        |        |      |   |            |   |       |        |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |                                                                                  | U5IP<2:0>   |             | U5IS-       | <1:0>                 | _           |                                        | -           |             | U6IP<2:0>   |              | U6IS-          | <1:0>       | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

| 1150                        | IFUIZ                           | 15:0      | _     | -     | -     |                                                                                  | U4IP<2:0>   |             | U4IS-       | <1:0>                 |             |                                        |             |             | ETHIP<2:0>  |              | ETHIS          | i<1:0>      | 0000       |             |             |             |        |        |      |   |            |   |       |        |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | LTAGBOOT          | _                 | _                 | -                 | —                 | _                 | _                | —                |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23.10        |                   |                   |                   | LTAG<1            | 9:12>             |                   |                  |                  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 10.0         |                   |                   |                   | LTAG<             | 11:4>             |                   |                  |                  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |

| 7.0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |

#### REGISTER 9-3: CHETAG: CACHE TAG REGISTER

# Legend:

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31 LTAGBOOT: Line Tag Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line Tag Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

#### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

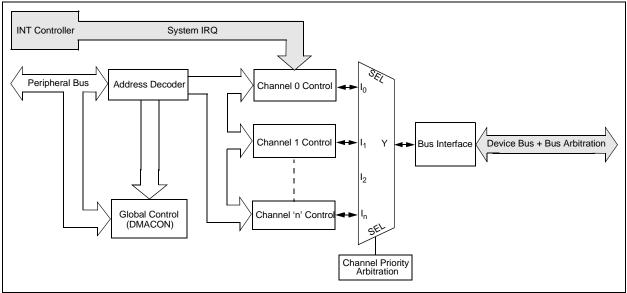

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Mem-Access (DMA) Controller" ory (DS60001117) in the "PIC32 Family Reference Manual", which is available from Microchip web the site (www.microchip.com/PIC32).

The Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

# FIGURE 10-1: DMA BLOCK DIAGRAM

© 2009-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 31.24        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 23.10        |                   |                   | —                    |                      | —                 | —                 | —                      | —                |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 15.0         | _                 | _                 | —                    | _                    | _                 |                   | —                      | _                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | DIGLI             | DIVIALI           |                      | DIOLIN               |                   | ONCIULI           | EOFEF <sup>(3,5)</sup> | TIDLI            |

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | pit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

- bit 31-8 Unimplemented: Read as '0'

bit 7 BTSEF: Bit Stuff Error Flag bit 1 = Packet is rejected due to bit stuff error 0 = Packet is accepted

bit 6 BMXEF: Bus Matrix Error Flag bit 1 = Invalid base address of the BDT, or the address of an individual buffer pointed to by a BDT entry 0 = No address error

bit 5 DMAEF: DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup> 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

- bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

- bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet is rejected due to CRC16 error

0 = Data packet is accepted

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup> 1 = Token packet is rejected due to CRC5 error 0 = Token packet is accepted EOFEF: EOF Error Flag bit<sup>(3,5)</sup> 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

# PIC32MX5XX/6XX/7XX

## TABLE 20-1: UART1 THROUGH UART6 REGISTER MAP (CONTINUED)

| ess                         |                       |           |        |        |        |               |        |       |       | Bi     | ts     |         |       |          |          |      |        |       |            |

|-----------------------------|-----------------------|-----------|--------|--------|--------|---------------|--------|-------|-------|--------|--------|---------|-------|----------|----------|------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12         | 27/11  | 26/10 | 25/9  | 24/8   | 23/7   | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1   | 16/0  | All Resets |

| 6620                        | U6TXREG               | 31:16     | _      | _      | —      | —             |        |       | —     | —      |        | —       | _     |          | —        | —    | —      | —     | 0000       |

| 0020                        | UUTAREG               | 15:0      | _      | _      | _      | —             | _      | _     | _     | TX8    |        |         |       | Transmit | Register | -    |        | -     | 0000       |

| 6630                        | U6RXREG               | 31:16     | _      | -      | _      | —             | _      | —     | _     |        | _      | —       | _     |          | _        | _    | —      | _     | 0000       |

| 0030                        | UUKAREG               | 15:0      | _      | _      | —      | —             | —      | —     | _     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6640                        | U6BRG <sup>(1)</sup>  | 31:16     | _      | _      | —      | —             | —      | —     | _     | —      | _      | —       | —     | —        | —        | _    | —      | _     | 0000       |

| 0040                        | OODING                | 15:0      |        |        | -      | -             |        |       |       | BRG<   | 15:0>  |         |       |          | -        | -    |        | -     | 0000       |

| 6800                        | U2MODE <sup>(1)</sup> | 31:16     | _      | _      | _      | —             | _      | _     | _     | —      | _      | -       | —     | _        | _        | —    | -      | _     | 0000       |

| 0000                        | OZIVIODE              | 15:0      | ON     | _      | SIDL   | IREN          | RTSMD  | _     | UEN   | <1:0>  | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6810                        | U2STA <sup>(1)</sup>  | 31:16     | -      | _      |        | _             | —      | —     | _     | ADM_EN |        |         |       | ADDR     | R<7:0>   | -    |        | -     | 0000       |

| 0010                        | 02017                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN         | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6820                        | U2TXREG               | 31:16     | _      | _      | _      | —             | _      | _     | _     | —      | _      | -       | —     | _        | —        | —    | -      | —     | 0000       |

| 0020                        | OZTARLO               | 15:0      | -      | _      |        | _             | —      | —     | _     | TX8    |        |         |       | Transmit | Register | -    |        | -     | 0000       |

| 6830                        | U2RXREG               | 31:16     | -      | _      |        | _             | —      | —     | _     | —      | _      | -       | —     | _        | _        | _    | -      | -     | 0000       |

| 0000                        | OZIVAREO              | 15:0      | -      | _      |        | _             | —      | —     | _     | RX8    |        |         |       | Receive  | Register | -    |        | -     | 0000       |

| 6840                        | U2BRG <sup>(1)</sup>  | 31:16     | —      | —      | —      | —             | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0010                        |                       | 15:0      |        |        |        |               |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

| 6A00                        | U5MODE <sup>(1)</sup> | 31:16     | —      | —      | —      | —             | —      | —     | —     | —      | —      | —       | —     | —        | —        | —    | —      | —     | 0000       |

| 0/100                       |                       | 15:0      | ON     | _      | SIDL   | IREN          | _      | —     | _     | —      | WAKE   | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0> | STSEL | 0000       |

| 6A10                        | U5STA <sup>(1)</sup>  | 31:16     | —      | —      | —      | —             | _      | —     | —     | ADM_EN |        |         |       | ADDR     |          | -    |        | -     | 0000       |

| 0,110                       |                       | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN         | UTXBRK | UTXEN | UTXBF | TRMT   | URXISI | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR   | URXDA | 0110       |

| 6A20                        | U5TXREG               | 31:16     | -      | _      | _      | _             | _      | _     |       | —      | _      | -       | —     | _        |          |      | -      |       | 0000       |

|                             |                       | 15:0      | —      | _      | _      | —             | _      | _     |       | TX8    |        |         | 1     | Transmit | Register | 1    |        | 1     | 0000       |

| 6A30                        | U5RXREG               | 31:16     | -      | _      | _      | _             | _      | _     |       | —      | _      | -       | —     | _        |          |      | -      |       | 0000       |

|                             |                       | 15:0      | —      | —      | —      | —             | —      | —     | —     | RX8    |        |         |       | Receive  | Register |      |        |       | 0000       |

| 6A40                        | U5BRG <sup>(1)</sup>  | 31:16     | —      | —      |        | —             | —      | —     | —     | —      | —      | —       | —     | _        |          |      | —      |       | 0000       |

| Legen                       |                       | 15:0      |        |        |        | d, read as '0 |        |       |       | BRG<   | 15:0>  |         |       |          |          |      |        |       | 0000       |

DS60001156J-page 206

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information. Note 1:

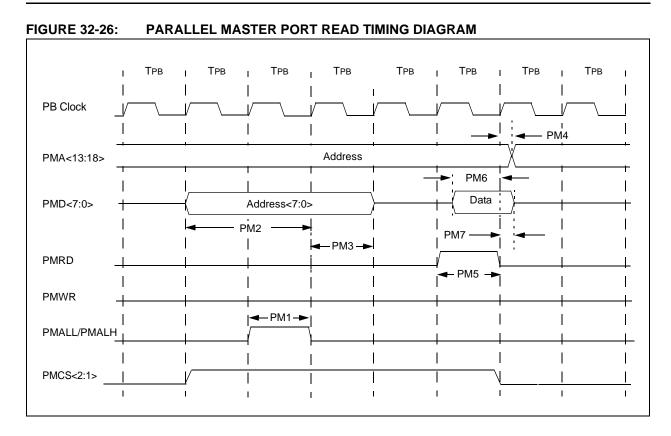

# 21.1 Control Registers

# TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

|                                         |                                 |           |           |           |       |       |         |        |        | Bi     | ts      |        |      |       |        |      |       |       |            |

|-----------------------------------------|---------------------------------|-----------|-----------|-----------|-------|-------|---------|--------|--------|--------|---------|--------|------|-------|--------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#)<br>Register | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4  | 19/3   | 18/2 | 17/1  | 16/0  | All Resets |

| 7000 PM0                                | /CON                            | 31:16     | _         | _         | _     | _     | _       | _      | _      | _      |         | _      | _    | _     | —      | _    | —     | _     | 0000       |

| 7000 1 100                              |                                 | 15:0      | ON        | —         | SIDL  | ADRMU | IX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P  | CS1P   | —    | WRSP  | RDSP  | 0000       |

| 7010 PMM                                | MODE                            | 31:16     | —         | —         | —     | —     | —       | —      | —      | —      | —       | —      | —    | —     | —      | —    | —     | —     | 0000       |

| 7010 Pivily                             | NODE                            | 15:0      | BUSY      | IRQM      | <1:0> | INCM  | <1:0>   | MODE16 | MODE   | <1:0>  | WAITE   | 3<1:0> |      | WAITM | A<3:0> |      | WAITE | <1:0> | 0000       |

| 7020 PMA                                |                                 | 31:16     |           | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _     | _      | _    | _     | _     | 0000       |

| 7020 PINA                               | IADDR                           | 15:0      | CS2EN/A15 | CS1EN/A14 |       |       |         |        |        |        | ADDR    | <13:0> |      |       |        |      |       |       | 0000       |

| 7000 040                                |                                 | 31:16     |           |           |       |       |         |        |        | DATAOU | T 04.0  |        |      |       |        |      |       |       | 0000       |

| 7030 PMD                                |                                 | 15:0      |           |           |       |       |         |        |        | DATAOU | 1<31:0> |        |      |       |        |      |       |       | 0000       |

| 7040 DM                                 | MDIN                            | 31:16     |           |           |       |       |         |        |        |        | .01.0   |        |      |       |        |      |       |       | 0000       |

| 7040 PM                                 |                                 | 15:0      |           |           |       |       |         |        |        | DATAIN | <31:0>  |        |      |       |        |      |       |       | 0000       |

| 7050 014                                | MAEN                            | 31:16     |           | _         | _     | _     | _       | _      | _      |        | _       | -      | -    | _     | _      | _    | _     | _     | 0000       |

| 7050 PM/                                | VIAEN                           | 15:0      |           |           |       |       |         |        |        | PTEN<  | :15:0>  |        |      |       |        |      |       |       | 0000       |

| 7000 0140                               | 10TAT                           | 31:16     | _         | _         | _     | _     | _       | _      | _      | _      | _       | _      | —    | _     | _      | _    | _     | _     | 0000       |

| 7060 PMS                                | ISTAL                           | 15:0      | IBF       | IBOV      | _     | -     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | —    | -     | OB3E   | OB2E | OB1E  | OB0E  | 008F       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### **Control Registers** 24.1

#### TABLE 24-1: CAN1 REGISTER SUMMARY FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX764F128L, PIC32MX775F256L, PIC32MX775F512L AND PIC32MX795F512L DEVICES

PIC32MX5XX/6XX/7XX

| ess                         |                                 |           |          |          |         |           |         |             |           | Bit       | 5        |          |          |          |           |            |           |          |            |

|-----------------------------|---------------------------------|-----------|----------|----------|---------|-----------|---------|-------------|-----------|-----------|----------|----------|----------|----------|-----------|------------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14    | 29/13   | 28/12     | 27/11   | 26/10       | 25/9      | 24/8      | 23/7     | 22/6     | 21/5     | 20/4     | 19/3      | 18/2       | 17/1      | 16/0     | All Resets |

| B000                        | C1CON                           | 31:16     | —        | —        | —       | —         | ABAT    |             | REQOP<2:0 | >         | C        | PMOD<2:0 | >        | CANCAP   |           | _          | —         | —        | 0480       |

| DUUU                        | CICON                           | 15:0      | ON       | _        | SIDLE   | _         | CANBUSY | _           | —         | _         | _        | _        | _        |          | D         | NCNT<4:0>  |           |          | 0000       |

| B010                        | C1CFG                           | 31:16     | —        | _        | _       | —         | —       | _           | —         | _         | _        | WAKFIL   | _        | —        | _         |            | EG2PH<2:0 | >        | 0000       |

| DUIU                        | CICIO                           | 15:0      | SEG2PHTS | SAM      | -       | EG1PH<2:0 |         | I           | PRSEG<2:0 | >         | SJW      | <1:0>    |          |          | BRP<      |            |           |          | 0000       |

| B020                        | C1INT                           | 31:16     | IVRIE    | WAKIE    | CERRIE  | SERRIE    | RBOVIE  | _           | —         | _         | _        | _        | _        | _        | MODIE     | CTMRIE     | RBIE      | TBIE     | 0000       |

| D020                        | Onivi                           | 15:0      | IVRIF    | WAKIF    | CERRIF  | SERRIF    | RBOVIF  | _           | —         | _         | _        | _        | _        | _        | MODIF     | CTMRIF     | RBIF      | TBIF     | 0000       |

| B030                        | C1VEC                           | 31:16     | —        | _        | —       | _         | _       | _           | —         | _         | _        | _        | —        | —        | _         | _          | -         | -        | 0000       |

| D030                        | CIVEC                           | 15:0      | —        | _        | —       |           | -       | FILHIT<4:0: | >         |           |          |          |          | 10       | CODE<6:0> |            | -         |          | 0040       |

| B040                        | C1TREC                          | 31:16     | —        | _        | —       | —         | _       | _           | —         | _         | _        | —        | TXBO     | TXBP     | RXBP      | TXWARN     | RXWARN    | EWARN    | 0000       |

| D040                        | OTINEO                          | 15:0      |          |          | -       | TERRC     | NT<7:0> |             |           |           |          |          |          | RERRCN   | IT<7:0>   |            | -         |          | 0000       |

| B050                        | C1FSTAT                         | 31:16     | FIFOIP31 | FIFOIP30 |         | FIFOIP28  | -       | FIFOIP26    | FIFOIP25  | FIFOIP24  | FIFOIP23 | FIFOIP22 | FIFOIP21 | FIFOIP20 | FIFOIP19  | FIFOIP18   | FIFOIP17  | FIFOIP16 | 0000       |

| D030                        | CHISTAI                         |           |          | FIFOIP14 |         | FIFOIP12  |         | FIFOIP10    | FIFOIP9   | FIFOIP8   | FIFOIP7  | FIFOIP6  | FIFOIP5  | FIFOIP4  | FIFOIP3   | FIFOIP2    | FIFOIP1   | FIFOIP0  | 0000       |

| B060                        | C1RXOVF                         |           |          |          | RXOVF29 |           |         |             |           | RXOVF24   | RXOVF23  | RXOVF22  | RXOVF21  | RXOVF20  | RXOVF19   | RXOVF18    | RXOVF17   | RXOVF16  | 0000       |

| D000                        | CIRAOVI                         | 15:0      | RXOVF15  | RXOVF14  | RXOVF13 | RXOVF12   | RXOVF11 | RXOVF10     | RXOVF9    | RXOVF8    | RXOVF7   | RXOVF6   | RXOVF5   | RXOVF4   | RXOVF3    | RXOVF2     | RXOVF1    | RXOVF0   | 0000       |

| B070                        | C1TMR                           | 31:16     |          |          |         |           |         |             |           | CANTS<    |          |          |          |          |           |            |           |          | 0000       |

| DOIO                        | OTTWIC                          | 15:0      |          |          |         |           |         |             | CA        | NTSPRE<15 | :0>      |          |          |          |           |            |           |          | 0000       |

| B080                        | C1RXM0                          | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          |          | MIDE      | -          | EID<1     | 7:16>    | xxxx       |

| DUUU                        | OTIVINO                         | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

| B090                        | C1RXM1                          | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          |          | MIDE      | —          | EID<1     | 7:16>    | xxxx       |

| D030                        | CIICAI                          | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

| BOVO                        | C1RXM2                          | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          | -        | MIDE      | -          | EID<1     | 7:16>    | xxxx       |

| B0A0                        | CIRAMZ                          | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

|                             | 0402440                         | 31:16     |          |          |         |           |         | SID<10:0>   |           |           |          |          |          |          | MIDE      | _          | EID<1     | 7:16>    | xxxx       |

| B0B0                        | C1RXM3                          | 15:0      |          |          |         |           |         |             |           | EID<1     | 5:0>     |          |          |          |           |            |           |          | xxxx       |

|                             |                                 | 31:16     | FLTEN3   | MSEL:    | 3<1:0>  |           |         | FSEL3<4:0:  | >         |           | FLTEN2   | MSEL:    | 2<1:0>   |          | F         | SEL2<4:0>  |           |          | 0000       |

| R0C0                        | C1FLTCON0                       | 15:0      | FLTEN1   | MSEL     | 1<1:0>  |           |         | FSEL1<4:0:  | >         |           | FLTEN0   | MSEL     | 0<1:0>   |          | F         | SEL0<4:0>  |           |          | 0000       |

|                             |                                 | 31:16     | FLTEN7   | MSEL     | 7<1:0>  |           |         | FSEL7<4:0:  | >         |           | FLTEN6   | MSEL     | 6<1:0>   |          | F         | SEL6<4:0>  |           |          | 0000       |

| R0D0                        | C1FLTCON1                       | 15:0      | FLTEN5   | MSEL     | 5<1:0>  |           |         | FSEL5<4:0:  |           |           | FLTEN4   | MSEL     | 4<1:0>   |          | F         | SEL4<4:0>  |           |          | 0000       |

| DOFC                        |                                 | 31:16     | FLTEN11  | MSEL1    | 1<1:0>  |           |         | FSEL11<4:0  | >         |           | FLTEN10  | MSEL1    | 0<1:0>   |          | F         | SEL10<4:0> | <b>,</b>  |          | 0000       |

| R0F0                        | C1FLTCON2                       | 15:0      | FLTEN9   | MSEL     | 9<1:0>  |           |         | FSEL9<4:0:  | >         |           | FLTEN8   | MSEL     | 8<1.0>   |          | F         | SEL8<4:0>  |           |          | 0000       |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

#### REGISTER 24-12: CIFLTCON2: CAN FILTER CONTROL REGISTER 2 (CONTINUED)

| bit 15    | FLTEN9: Filter 9 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                            |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14-13 | MSEL9<1:0>: Filter 9 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                         |

| bit 12-8  | FSEL9<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•                                                                                                                        |

|           | 00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                  |

| bit 7     | FLTEN8: Filter 8 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                            |

| bit 6-5   | MSEL8<1:0>: Filter 8 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                         |

| bit 4-0   | FSEL8<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| r         |                                                                                                                                                                                                                                                                                           |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN15           | MSEL1             | 5<1:0>            |                   | F                 | SEL15<4:0>        |                  |                  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN14           | MSEL1             | 4<1:0>            |                   | F                 | SEL14<4:0>        |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN13           | MSEL1             | 3<1:0>            |                   | F                 | SEL13<4:0>        |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN12           | MSEL1             | 2<1:0>            |                   | F                 | SEL12<4:0>        |                  |                  |

#### REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | <b>FLTEN15:</b> Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | <pre>FSEL15&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>           |

| bit 23    | <b>FLTEN14:</b> Filter 14 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                             |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 20-16 | <pre>FSEL14&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>           |

| Note:     | The hits in this register can only be modified if the correspondir                                                                                                                  |

**Note:** The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

#### REGISTER 25-3: ETHTXST: ETHERNET CONTROLLER TX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | TXSTADD           | R<31:24>          |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | TXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15.0         | TXSTADDR<15:8>    |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |

| 7.0          |                   |                   | TXSTAD            | DR<7:2>           |                   |                   |                  |                  |

# Legend:

| Legenu.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-2 **TXSTADDR<31:2>:** Starting Address of First Transmit Descriptor bits This register should not be written while any transmit, receive or DMA operations are in progress. This address must be 4-byte aligned (bits 1-0 must be '00').

#### bit 1-0 Unimplemented: Read as '0'

Note 1: This register is only used for TX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

#### REGISTER 25-4: ETHRXST: ETHERNET CONTROLLER RX PACKET DESCRIPTOR START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        |                   |                   |                   | RXSTADE           | )R<31:24>         |                   |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | RXSTADDR<23:16>   |                   |                   |                   |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 0.61         |                   |                   |                   | RXSTADI           | DR<15:8>          |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | U-0              |

| 7.0          |                   |                   | RXSTAD            | DR<7:2>           |                   |                   |                  |                  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-2 **RXSTADDR<31:2>:** Starting Address of First Receive Descriptor bits

This register should not be written while any transmit, receive or DMA operations are in progress. This address must be 4-byte aligned (bits 1-0 must be '00').

#### bit 1-0 Unimplemented: Read as '0'

Note 1: This register is only used for RX operations.

2: This register will be updated by hardware with the last descriptor used by the last successfully transmitted packet.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                     | _                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                   | -                 | —                 | —                 | —                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

| 15:8         | 0N <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | -                 | —                 | —                 | —                | COUT             |

| 7.0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

| 7:0          | EVPOL             | _<1:0>            |                     | CREF              | _                 |                   | CCH              | <1:0>            |

#### REGISTER 26-1: CMxCON: COMPARATOR 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Comparator ON bit<sup>(1)</sup>

Clearing this bit does not affect the other bits in this register.

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current.

- bit 14 COE: Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

#### bit 12-9 Unimplemented: Read as '0'

- bit 8 COUT: Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

#### bit 5 Unimplemented: Read as '0'

- bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CxIN+ pin

- bit 3-2 Unimplemented: Read as '0'

- bit 1-0 **CCH<1:0>:** Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the C2IN+ pin for C1 and C1IN+ pin for C2

- 01 = Comparator inverting input is connected to the C1IN+ pin for C1 and C2IN+ pin for C2

- 00 = Comparator inverting input is connected to the C1IN- pin for C1 and C2IN- pin for C2

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

## 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 32.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX5XX/6XX/7XX electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX5XX/6XX/7XX devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias<br>Storage temperature                           |                      |

|---------------------------------------------------------------------------------|----------------------|

| Voltage on VDD with respect to Vss                                              |                      |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge$ 2.3V (Note 3) | 0.3V to +5.5V        |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V        |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V        |