Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256КВ (256К х 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

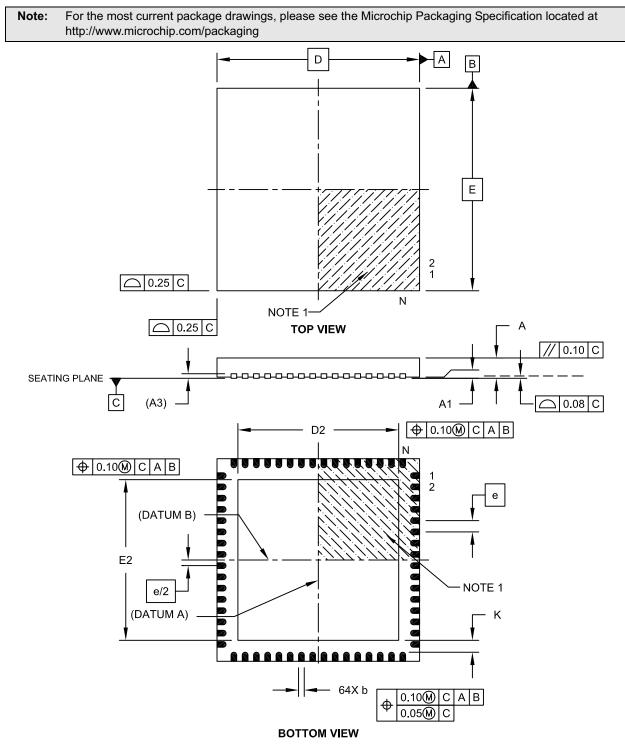

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f256lt-80v-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  |      |                         |                  |     | USE      | B and E                | therne                                   | t                     |                    |                                 |                              |             |         |      |       |                         |

|------------------|------|-------------------------|------------------|-----|----------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSP/PMP | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX664F064H  | 64   | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F128H  | 64   | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F256H  | 64   | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX675F512H  | 64   | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX695F512H  | 64   | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX664F064L  | 100  | 64 + 12 <sup>(1)</sup>  | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX664F128L  | 100  | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 5/5/5                  | 4/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F256L  | 100  | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX675F512L  | 100  | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| PIC32MX695F512L  | 100  | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 5/5/5                  | 8/4                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFP | MR = QF                 | N                |     | BG =     | TFBGA                  | 4                                        | TL =                  | VTL/               | ų( <del>5</del> )               |                              |             |         |      |       |                         |

| TABLE 2: PIC32MX6XX USB AND ETHERNET FEATURES |

|-----------------------------------------------|

|-----------------------------------------------|

Legend: PF, PT = TQFP MR = QFN BG = Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

#### TABLE 6:PIN NAMES FOR 64-PIN USB, ETHERNET, AND CAN DEVICES

# 64-PIN QFN<sup>(3)</sup> AND TQFP (TOP VIEW)

# PIC32MX764F128H PIC32MX775F256H PIC32MX775F512H PIC32MX795F512H

|       | 64                                                        | 1                  |                                               |

|-------|-----------------------------------------------------------|--------------------|-----------------------------------------------|

|       |                                                           | QFN <sup>(3)</sup> | 64<br>TQFP                                    |

| Pin # | Full Pin Name                                             | Pin #              | Full Pin Name                                 |

| 1     | ETXEN/PMD5/RE5                                            | 33                 | USBID/RF3                                     |

| 2     | ETXD0/PMD6/RE6                                            | 34                 | VBUS                                          |

| 3     | ETXD1/PMD7/RE7                                            | 35                 | VUSB3V3                                       |

| 4     | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                              | 36                 | D-/RG3                                        |

| 5     | SDA4/SDI2/U3RX/PMA4/CN9/RG7                               | 37                 | D+/RG2                                        |

| 6     | SCL4/SDO2/U3TX/PMA3/CN10/RG8                              | 38                 | Vdd                                           |

| 7     | MCLR                                                      | 39                 | OSC1/CLKI/RC12                                |

| 8     | SS2/U6RX/U3CTS/PMA2/CN11/RG9                              | 40                 | OSC2/CLKO/RC15                                |

| 9     | Vss                                                       | 41                 | Vss                                           |

| 10    | Vdd                                                       | 42                 | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |

| 11    | AN5/C1IN+/VBUSON/CN7/RB5                                  | 43                 | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |

| 12    | AN4/C1IN-/CN6/RB4                                         | 44                 | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |

| 13    | AN3/C2IN+/CN5/RB3                                         | 45                 | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |

| 14    | AN2/C2IN-/CN4/RB2                                         | 46                 | OC1/INT0/RD0                                  |

| 15    | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                            | 47                 | SOSCI/CN1/RC13                                |

| 16    | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                       | 48                 | SOSCO/T1CK/CN0/RC14                           |

| 17    | PGEC2/AN6/OCFA/RB6                                        | 49                 | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |

| 18    | PGED2/AN7/RB7                                             | 50                 | SDA3/SDI3/U1RX/OC3/RD2                        |

| 19    | AVdd                                                      | 51                 | SCL3/SDO3/U1TX/OC4/RD3                        |

| 20    | AVss                                                      | 52                 | OC5/IC5/PMWR/CN13/RD4                         |

| 21    | AN8/C2TX <sup>(2)</sup> /SS4/U5RX/U2CTS/C1OUT/RB8         | 53                 | PMRD/CN14/RD5                                 |

| 22    | AN9/C2OUT/PMA7/RB9                                        | 54                 | AETXEN/ETXERR/CN15/RD6                        |

| 23    | TMS/AN10/CVREFOUT/PMA13/RB10                              | 55                 | ETXCLK/AERXERR/CN16/RD7                       |

| 24    | TDO/AN11/PMA12/RB11                                       | 56                 | VCAP                                          |

| 25    | Vss                                                       | 57                 | VDD                                           |

| 26    | Vdd                                                       | 58                 | C1RX/AETXD1/ERXD3/RF0                         |

| 27    | TCK/AN12/PMA11/RB12                                       | 59                 | C1TX/AETXD0/ERXD2/RF1                         |

| 28    | TDI/AN13/PMA10/RB13                                       | 60                 | ERXD1/PMD0/RE0                                |

| 29    | AN14/C2RX <sup>(2)</sup> /SCK4/U5TX/U2RTS/PMALH/PMA1/RB14 | 61                 | ERXD0/PMD1/RE1                                |

| 30    | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                 | 62                 | ERXDV/ECRSDV/PMD2/RE2                         |

| 31    | AC1TX/SDA5/SDI4/U2RX/PMA9/CN17/RF4                        | 63                 | ERXCLK/EREFCLKPMD3/RE3                        |

| 32    | AC1RX/SCL5/SDO4/U2TX/PMA8/CN18/RF5                        | 64                 | ERXERR/PMD4/RE4                               |

| Note  | 1: Shaded pins are 5V tolerant.                           |                    |                                               |

Note 1: Shaded pins are 5V tolerant.

2: This pin is not available on PIC32MX765F128H devices.

3: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

1

# TABLE 9: PIN NAMES FOR 100-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

# **100-PIN TQFP (TOP VIEW)**

PIC32MX764F128L PIC32MX775F256L PIC32MX775F512L PIC32MX795F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name                        |  |  |

|-------|---------------------------------|-------|--------------------------------------|--|--|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD                                  |  |  |

| 72    | SDO1/OC1/INT0/RD0               | 87    | C1RX/ETXD1/PMD11/RF0                 |  |  |

| 73    | SOSCI/CN1/RC13                  | 88    | C1TX/ETXD0/PMD10/RF1                 |  |  |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | C2TX <sup>(1)</sup> /ETXERR/PMD9/RG1 |  |  |

| 75    | Vss                             | 90    | C2RX <sup>(1)</sup> /PMD8/RG0        |  |  |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6                            |  |  |

| 77    | OC3/RD2                         | 92    | TRD3/RA7                             |  |  |

| 78    | OC4/RD3                         | 93    | PMD0/RE0                             |  |  |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1                             |  |  |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14                            |  |  |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12                            |  |  |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13                            |  |  |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2                             |  |  |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3                             |  |  |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4                             |  |  |

Note 1: This pin is not available on PIC32MX764F128L devices.

2: Shaded pins are 5V tolerant.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Program Memory" (DS60001121) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). PIC32MX5XX/6XX/7XX devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the "*PIC32 Flash Programming Specification*" (DS60001145), which can be downloaded from the Microchip web site.

Note: For PIC32MX5XX/6XX/7XX devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

#### **TABLE 7-2:** INTERRUPT REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H AND PIC32MX575F512H DEVICES (CONTINUED)

| ess                         |                                 | 0         |       |       |              |                            |             |         |                      | Bits   |      |            |             |             |            |                       |        |        |               |

|-----------------------------|---------------------------------|-----------|-------|-------|--------------|----------------------------|-------------|---------|----------------------|--------|------|------------|-------------|-------------|------------|-----------------------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13        | 28/12                      | 27/11       | 26/10   | 25/9                 | 24/8   | 23/7 | 22/6       | 21/5        | 20/4        | 19/3       | 18/2                  | 17/1   | 16/0   | All<br>Resets |

| 10A0                        | IPC1                            | 31:16     | _     | —     | —            |                            | INT1IP<2:0> |         | INT1IS               | <1:0>  | -    | _          | _           | OC1IP<2:0>  |            | OC1IS                 | S<1:0> | 0000   |               |

| TUAU                        | IFCI                            | 15:0      |       | _     | _            | IC1IP<2:0>                 |             | IC1IS<  | <1:0>                | _      | _    |            | T1IP<2:0>   |             | T1IS       | <1:0>                 | 0000   |        |               |

| 10B0                        | IPC2 31:16                      |           |       | —     | —            |                            | INT2IP<2:0> |         | INT2IS               | <1:0>  | —    | _          | -           | C           | C2IP<2:0>  | >                     | OC2IS  | S<1:0> | 0000          |

| тово                        | IF 02                           | 15:0      |       | _     | _            |                            | IC2IP<2:0>  |         | IC2IS<               | <1:0>  | _    | -          |             | -           | T2IP<2:0>  |                       | T2IS   | <1:0>  | 0000          |

| 10C0                        | IPC3                            | 31:16     |       | _     | _            | 111011 (210)               |             |         | INT3IS               | <1:0>  | —    | _          |             | C           | C3IP<2:0>  | >                     | OC3IS  | S<1:0> | 0000          |

| 1000                        | 11 00                           | 15:0      | —     | —     | —            | IC3IP<2:0>                 |             | IC3IS<  | <1:0>                | —      | —    | —          | -           | T3IP<2:0>   |            | T3IS                  | <1:0>  | 0000   |               |

| 10D0                        | IPC4                            | 31:16     | —     | —     | —            |                            | INT4IP<2:0> |         | INT4IS               | <1:0>  | —    | —          | —           | C           | C4IP<2:0>  | <b>&gt;</b>           | OC4IS  | S<1:0> | 0000          |

| TODO                        | 11 04                           | 15:0      | —     | —     | —            |                            | IC4IP<2:0>  |         | IC4IS<               | <1:0>  | —    | —          | —           | -           | T4IP<2:0>  |                       | T4IS   | <1:0>  | 0000          |

| 10E0                        | IPC5                            | 31:16     | —     | —     | —            |                            | —           | —       | —                    | —      | —    | —          | _           | -           | C5IP<2:0>  | >                     | OC5IS  | S<1:0> | 0000          |

| IOLO                        | 1 00                            | 15:0      | —     | —     | —            |                            | IC5IP<2:0>  |         | IC5IS<               | <1:0>  | —    | —          | —           |             | T5IP<2:0>  |                       | T5IS   |        | 0000          |

|                             |                                 | 31:16     | —     | —     | —            |                            | AD1IP<2:0>  |         | AD1IS-               | <1:0>  | —    | —          | —           | (           | CNIP<2:0>  |                       | CNIS   | -      | 0000          |

| 10F0                        | IPC6                            |           |       |       |              |                            |             |         |                      |        |      |            |             | l           | J1IP<2:0>  |                       | U1IS   | <1:0>  |               |

| 101.0                       | 1 00                            | 15:0      | —     | —     | —            |                            | I2C1IP<2:0> |         | 12C1IS               |        | —    | —          | —           | S           | PI3IP<2:0: | >                     | SPI3IS | S<1:0> | 0000          |

|                             |                                 |           |       |       |              |                            |             |         |                      |        |      |            |             | I2C3IP<2:0> |            | I2C3IS<1:0>           |        |        |               |

|                             |                                 |           |       |       |              | U3IP<2:0>                  |             | U3IS<   | U3IS<1:0>            |        |      |            |             |             |            |                       |        |        |               |

| 1100                        | IPC7                            | 31:16     | —     | —     | —            |                            | SPI2IP<2:0> |         | SPI2IS               | <1:0>  | —    | —          | —           | C           | MP2IP<2:0  | >                     | CMP2I  | S<1:0> | 0000          |

| 1100                        | 11 07                           |           |       |       |              |                            | I2C4IP<2:0> |         | I2C4IS               | -      |      |            |             |             |            |                       |        |        |               |

|                             |                                 | 15:0      | —     | —     | —            | (                          | CMP1IP<2:0> | •       | CMP1IS               |        | —    | —          | _           |             | MPIP<2:0   |                       | PMPIS  | S<1:0> | 0000          |

|                             |                                 | 31:16     | —     | —     | —            | F                          | RTCCIP<2:0> | •       | RTCCIS               | S<1:0> | —    | —          | _           |             | SCMIP<2:0  | >                     |        | S<1:0> | 0000          |

| 1110                        | IPC8                            |           |       |       |              |                            |             |         |                      |        |      |            |             |             | J2IP<2:0>  |                       | U2IS   |        |               |

|                             | 11 00                           | 15:0      | —     | —     | —            | —                          | —           | —       | —                    | —      | —    | —          | —           | S           | PI4IP<2:0; | >                     | SPI4IS | S<1:0> | 0000          |

|                             |                                 |           |       |       |              |                            |             |         |                      |        |      |            |             |             | 2C5IP<2:0> |                       | 12C515 |        |               |

| 1120                        | IPC9                            | 31:16     | _     | —     | —            |                            | DMA3IP<2:0> |         | DMA3IS               |        | _    | —          | _           | DMA2IP<2:0> |            | DMA2I                 |        | 0000   |               |

| 1120                        | 11 00                           | 15:0      | _     | —     | —            |                            | DMA1IP<2:0> |         | DMA1IS               |        | _    | —          | _           | DMA0IP<2:0> |            | DMA0I                 |        | 0000   |               |

| 1130                        | IPC10                           | 31:16     | —     | —     | —            | DMA7IP<2:0> <sup>(2)</sup> |             | DMA7IS- | -                    | —      | —    | —          |             |             |            | S<1:0> <sup>(2)</sup> | 0000   |        |               |

| 1100                        | 1 010                           | 15:0      | —     | —     | —            | DMA5IP<2:0> <sup>(2)</sup> |             | DMA5IS- | <1:0> <sup>(2)</sup> | —      | —    | —          | -           |             | DMA4IS     | S<1:0> <sup>(2)</sup> | 0000   |        |               |

| 1140                        | IPC11                           | 31:16     | _     | _     | _            |                            |             | _       | _                    | —      | _    | _          | CAN1IP<2:0> |             | CAN1I      | S<1:0>                | 0000   |        |               |

| 1140                        |                                 | 15:0      | _     | —     | — USBIP<2:0> |                            | USBIS       | <1:0>   | —                    | —      | _    | FCEIP<2:0> |             | FCEIS       | S<1:0>     | 0000                  |        |        |               |

| 1150                        | IPC12                           | 31:16     | _     | —     | —            |                            | U5IP<2:0>   |         | U5IS<                | :1:0>  | —    | —          | —           | l           | J6IP<2:0>  |                       | U6IS   | <1:0>  | 0000          |

| 1100                        | IPC12                           | 15:0      | —     | —     | —            |                            | U4IP<2:0>   |         | U4IS<                | :1:0>  | —    | —          | _           | —           | —          | -                     | -      | —      | 0000          |

PIC32MX5XX/6XX/7XX

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET Note 1: and INV Registers" for more information.

These bits are not available on PIC32MX534/564/664/764 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

|                             | PIC32MX695F512H DEVICES                                                                                   |               |               |         |         |                               |                               |                               |                               |                             |                               |                               |                             |                       |               |           |        |        |            |

|-----------------------------|-----------------------------------------------------------------------------------------------------------|---------------|---------------|---------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|---------------|-----------|--------|--------|------------|

| ess                         |                                                                                                           |               |               |         |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |               |           |        |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                                           | Bit Range     | 31/15         | 30/14   | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3          | 18/2      | 17/1   | 16/0   | All Resets |

| 1000                        | INTCON                                                                                                    | 31:16         |               |         | —       | —                             | _                             |                               | _                             |                             | _                             | —                             |                             | _                     |               |           | _      | SS0    | 0000       |

| 1000                        | INTCON                                                                                                    | 15:0          | —             | _       | _       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | _                             |                             | INT4EP                | INT3EP        | INT2EP    | INT1EP | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>                                                                                    | 31:16         | —             | —       | —       | —                             | —                             | —                             | —                             | —                           | —                             | —                             | —                           | —                     | —             | —         | —      | —      | 0000       |

| 1010                        |                                                                                                           | 15:0          |               | —       | —       | —                             | _                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC           | <5:0>     |        |        | 0000       |

| 1020                        | IPTMR                                                                                                     | 31:16<br>15:0 |               |         |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |               |           |        |        | 0000       |

| 1030                        | IFS0                                                                                                      | 31:16         | I2C1MIF       | I2C1SIF | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | _                             | _                           | _                             | OC5IF                         | IC5IF                       | T5IF                  | INT4IF        | OC4IF     | IC4IF  | T4IF   | 0000       |

|                             |                                                                                                           | 15:0          | INT3IF        | OC3IF   | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | <b>INT0IF</b> | CS1IF     | CS0IF  | CTIF   | 0000       |

|                             |                                                                                                           | 31:16         | <b>IC3EIF</b> | IC2EIF  | IC1EIF  | ETHIF                         | —                             | _                             | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF        | DMA2IF    | DMA1IF | DMA0IF | 0000       |

| 1040                        | IFS1                                                                                                      | 15:0          | RTCCIF        | FSCMIF  | _       | _                             | _                             | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF        | PMPIF     | AD1IF  | CNIF   | 0000       |

|                             |                                                                                                           | 31:16         |               |         |         |                               | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     |               | _         | _      | _      | 0000       |

| 1050                        | IFS2                                                                                                      | 15:0          | _             | _       | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF         | PMPEIF    | IC5EIF | IC4EIF | 0000       |

| 1060                        | IEC0                                                                                                      | 31:16         | I2C1MIE       | I2C1SIE | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | _                             |                             | _                             | OC5IE                         | IC5IE                       | T5IE                  | INT4IE        | OC4IE     | IC4IE  | T4IE   | 0000       |

|                             |                                                                                                           | 15:0          | INT3IE        | OC3IE   | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE        | CS1IE     | CS0IE  | CTIE   | 0000       |

|                             |                                                                                                           | 31:16         | IC3EIE        | IC2EIE  | IC1EIE  | ETHIE                         | —                             | _                             | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b> | DMA2IE    | DMA1IE | DMA0IE | 0000       |

| 1070                        | IEC1                                                                                                      | 15:0          | RTCCIE        | FSCMIE  | _       | _                             | -                             | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE        | PMPIE     | AD1IE  | CNIE   | 0000       |

|                             |                                                                                                           | 31:16         |               |         | _       | _                             | _                             | _                             |                               | _                           | _                             | _                             | _                           | _                     |               | _         | _      | _      | 0000       |

| 1080                        | IEC2                                                                                                      | 15:0          | _             | _       | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE         | PMPEIE    | IC5EIE | IC4EIE | 0000       |

|                             |                                                                                                           | 31:16         | _             | _       | _       |                               | INT0IP<2:0>                   |                               | INTOIS                        |                             | _                             | _                             | _                           |                       | CS1IP<2:0>    |           | CS1IS  |        | 0000       |

| 1090                        | IPC0                                                                                                      | 15:0          | _             | _       | _       |                               | CS0IP<2:0>                    |                               | CSOIS                         | S<1:0>                      | _                             | _                             | _                           | - CTIP<2:0> CTIS<1    |               |           | 0000   |        |            |

| 1040                        | IPC1                                                                                                      | 31:16         | _             | _       | _       |                               | INT1IP<2:0>                   |                               | INT1IS                        | S<1:0>                      | _                             | _                             | _                           | (                     | OC1IP<2:0>    |           | OC1IS  | S<1:0> | 0000       |

| 10A0                        | IPUT                                                                                                      | 15:0          | _             | _       | _       |                               | IC1IP<2:0>                    | IC1IS<1:0>                    |                               | <1:0>                       | _                             | _                             |                             | T1IP<2:0>             |               | T1IS<1:0> |        | 0000   |            |

| 10B0                        | IPC2                                                                                                      | 31:16         |               | —       | _       |                               | INT2IP<2:0>                   |                               |                               | —                           | —                             | _                             | OC2IP<2:0>                  |                       | OC2IS<1:0>    |           | S<1:0> | 0000   |            |

| 10D0                        | 1602                                                                                                      | 15:0          | _             | —       | —       |                               | IC2IP<2:0>                    |                               |                               | —                           | —                             | _                             | T2IP<2:0>                   |                       | T2IS-         | <1:0>     | 0000   |        |            |

| 10C0                        | IPC3                                                                                                      | 31:16         | —             | —       | -       |                               | INT3IP<2:0>                   |                               |                               | S<1:0>                      | —                             | —                             |                             | OC3IP<2:0>            |               | OC3IS     | S<1:0> | 0000   |            |

| 1000                        | 1 00                                                                                                      | 15:0          |               | —       | —       |                               | IC3IP<2:0>                    |                               | IC3IS                         | <1:0>                       | —                             | —                             | —                           |                       | T3IP<2:0>     |           | T3IS-  | <1:0>  | 0000       |

| Legend                      | egend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |               |               |         |         |                               |                               |                               |                               |                             |                               |                               |                             |                       |               |           |        |        |            |

#### **TABLE 7-3:** INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND DIC22MV605E512U DEVICES

DS60001156J-page 79

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

© 2009-2016 Microchip Technology Inc.

x = Bit is unknown

|                  |                   |                   | •••••••           |                   |                                    |                   |                  |                  |  |  |  |

|------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04-04            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24            |                   |                   |                   | CHEHIT<           | :31:24>                            |                   |                  |                  |  |  |  |

| 00:40            | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16            |                   |                   |                   | CHEHIT<           | :23:16>                            |                   |                  |                  |  |  |  |

| 45.0             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8             | CHEHIT<15:8>      |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| 7.0              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0              | 7:0 CHEHIT<7:0>   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| 1                |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| Legend:          |                   |                   |                   |                   |                                    |                   |                  |                  |  |  |  |

| R = Readable bit |                   |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0' |                   |                  |                  |  |  |  |

## **REGISTER 9-10: CHEHIT: CACHE HIT STATISTICS REGISTER**

#### bit 31-0 CHEHIT<31:0>: Cache Hit Count bits

- - - - -

-n = Value at POR

Incremented each time the processor issues an instruction fetch or load that hits the prefetch cache from a cacheable region. Non-cacheable accesses do not modify this value.

-----

'0' = Bit is cleared

| REGIST | ER 9-11: 0 | CHEMIS: CA | CHE MISS | STATISTICS | 6 REGISTEI | ĸ |

|--------|------------|------------|----------|------------|------------|---|

|        |            |            |          |            |            |   |

'1' = Bit is set

| Bit<br>Range      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-------------------|-------------------|-------------------|-------------------|-------------------|------------------------------------------|-------------------|------------------|------------------|--|--|--|

| 24.24             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24             | CHEMIS<31:24>     |                   |                   |                   |                                          |                   |                  |                  |  |  |  |

| 00.40             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16             | CHEMIS<23:16>     |                   |                   |                   |                                          |                   |                  |                  |  |  |  |

| 15:8              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8              | CHEMIS<15:8>      |                   |                   |                   |                                          |                   |                  |                  |  |  |  |

| 7.0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                    | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0               |                   |                   |                   | CHEMIS<7:0>       |                                          |                   |                  |                  |  |  |  |

|                   |                   |                   |                   |                   |                                          |                   |                  |                  |  |  |  |

| Legend:           |                   |                   |                   |                   |                                          |                   |                  |                  |  |  |  |

| R = Rea           | R = Readable bit  |                   |                   | e bit             | U = Unimplemented bit, read as '0'       |                   |                  |                  |  |  |  |

| -n = Value at POR |                   |                   | '1' = Bit is se   | t                 | 0' = Bit is cleared $x = Bit is unknown$ |                   |                  |                  |  |  |  |

#### bit 31-0 CHEMIS<31:0>: Cache Miss Count bits

Incremented each time the processor issues an instruction fetch from a cacheable region that misses the prefetch cache. Non-cacheable accesses do not modify this value.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | DCRCDATA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

## REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

# REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        |                   |                   |                   | DCRCXOF           | R<31:24>          |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

## 1 = Enable the XOR input to the Shift register

0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

# PIC32MX5XX/6XX/7XX

# REGISTER 11-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | -                 | —                        | —                 | _                     | -                     | —                | —                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         |                   |                   | —                        | —                 |                       |                       | —                | —                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          |                   | ISTATE SE0        | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JSIAIE            |                   | TOKBUSY <sup>(1,5)</sup> |                   |                       | KESUME"               | FFDKOI           | SOFEN <sup>(5)</sup> |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = JSTATE was not detected

- bit 6 **SE0:** Live Single-Ended Zero flag bit 1 = Single-ended zero was detected on the USB 0 = Single-ended zero was not detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

- bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

# bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 |                   |                   | _                 |                   |                  | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | SIDL              | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 |                   |                   | _                 |                   | _                | _                |

# REGISTER 12-1: CNCON: CHANGE NOTICE CONTROL REGISTER

# Legend:

| R = Readable bit  | adable bit W = Writable bit |                      | ad as '0'          |

|-------------------|-----------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle mode does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

# REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

#### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |

| 31:24        | —                 | —                 | _                 | -                 | ABAT              | F                 | REQOP<2:0>       | >                |

| 22:16        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |

| 23:16        | OPMOD<2:0>        |                   |                   | CANCAP            | —                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDLE             | -                 | CANBUSY           | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 |                   |                   | DNCNT<4:0>        |                  |                  |

# REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER

| Legend:           | HC = Hardware Clear S = Settable bit |                           |                    |

|-------------------|--------------------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit                     | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                     | '0' = Bit is cleared      | x = Bit is unknown |

## bit 31-28 Unimplemented: Read as '0'

- bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

# bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 ON: CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|------------------------------|------------------|------------------|

| 24.24        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0                          | U-0              | U-0              |

| 31:24        | _                       |                    | _                 | _                 | _                 | —                            | _                | —                |

| 22:16        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0                        | R/W-0            | R/W-0            |

| 23:16        | —                       | WAKFIL             | _                 | —                 | _                 | SEG2PH<2:0> <sup>(1,4)</sup> |                  | ,4)              |

| 15.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            | R/W-0            |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | 5                 | SEG1PH<2:0:       | >                 | Р                            | RSEG<2:0>        |                  |

| 7.0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            | R/W-0            |

| 7:0          | SJW<1:                  | 0> <sup>(3)</sup>  |                   |                   | BRP<              | 5:0>                         |                  |                  |

# REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER

| Legend:           | HC = Hardware Clear | S = Settable bit                       |  |  |

|-------------------|---------------------|----------------------------------------|--|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, read as '0'     |  |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared x = Bit is unknow |  |  |

#### bit 31-23 Unimplemented: Read as '0'

- bit 22 **WAKFIL:** CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| 011 21 10 | Chimplemented. Read as 0                                                      |

|-----------|-------------------------------------------------------------------------------|

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x TQ                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | <b>SAM:</b> Sample of the CAN Bus Line bit <sup>(2)</sup>                     |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x Tq                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | $SJW \leq SEG2PH.$                                                            |

| 4:        | The Time Quanta per bit must be greater than 7 (that is, $TQBIT > 7$ ).       |

|           |                                                                               |

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

# **REGISTER 24-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)