Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E•>< Fl

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

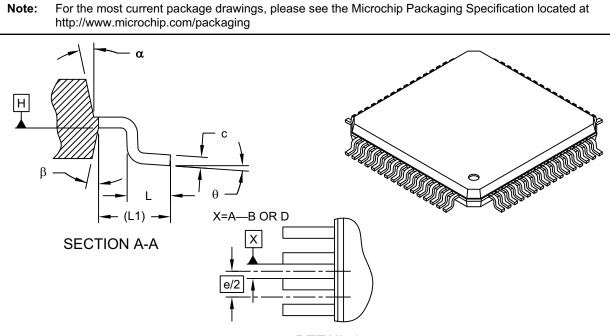

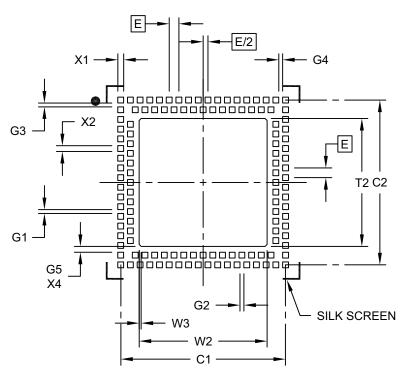

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-VFQFN Exposed Pad                                                              |

| Supplier Device Package    | 64-VQFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512ht-80v-mr |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **TABLE 13:** PIN NAMES FOR 124-PIN USB, ETHERNET, AND CAN DEVICES (CONTINUED)

| 124               | 4-PIN VTLA (BOTTOM VIEW) <sup>(2,3)</sup>             |     |                   | A34                       |                           |  |

|-------------------|-------------------------------------------------------|-----|-------------------|---------------------------|---------------------------|--|

|                   |                                                       | B13 | B29               |                           | Conductive<br>Thermal Pad |  |

|                   | PIC32MX675F512L<br>PIC32MX695F512L<br>PIC32MX795F512L | B1  | B56               | B41                       | A51                       |  |

|                   | A1                                                    |     |                   |                           |                           |  |

|                   | Polarity Indicator                                    |     | A68               |                           |                           |  |

| Package<br>Bump # | Full Pin Name                                         |     | Package<br>Bump # | F                         | ull Pin Name              |  |

| B8                | Vss                                                   |     | B33               | TDO/RA5                   |                           |  |

| B9                | TMS/RA0                                               |     | B34               | OSC1/CLKI/RC              | 212                       |  |

| B10               | AERXD1/INT2/RE9                                       |     | B35               | No Connect (N             | C)                        |  |

| B11               | AN4/C1IN-/CN6/RB4                                     |     | B36               | AETXCLK/SCL               | .1/INT3/RA14              |  |

| B12               | Vss                                                   |     | B37               | RTCC/EMDIO/               | AEMDIO/IC1/RD8            |  |

| B13               | AN2/C2IN-/CN4/RB2                                     |     | B38               | SCK1/IC3/PMC              | CS2/PMA15/RD10            |  |

| B14               | PGED1/AN0/CN2/RB0                                     |     | B39               | SDO1/OC1/INT              | [0/RD0                    |  |

| B15               | No Connect (NC)                                       |     | B40               | SOSCO/T1CK/               | CN0/RC14                  |  |

| B16               | PGED2/AN7/RB7                                         |     | B41               | Vss                       |                           |  |

| B17               | VREF+/CVREF+/AERXD3/PMA6/RA10                         |     | B42               | OC3/RD2                   |                           |  |

| B18               | AVss                                                  |     | B43               | ETXD2/IC5/PN              | ID12/RD12                 |  |

| B19               | AN9/C2OUT/RB9                                         |     | B44               | OC5/PMWR/CI               | N13/RD4                   |  |

| B20               | AN11/ERXERR/AETXERR/PMA12/RB11                        |     | B45               | ETXEN/PMD14               | 4/CN15/RD6                |  |

| B21               | Vdd                                                   |     | B46               | Vss                       |                           |  |

| B22               | AC1TX/SCK4/U5TX/U2RTS/RF13                            |     | B47               | No Connect (N             | C)                        |  |

| B23               | AN12/ERXD0/AECRS/PMA11/RB12                           |     | B48               | VCAP                      |                           |  |

| B24               | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14                     |     | B49               | C1RX <sup>(1)</sup> /ETXD | 1/PMD11/RF0               |  |

| B25               | Vss                                                   |     | B50               | C2TX <sup>(1)</sup> /ETXE | RR/PMD9/RG1               |  |

| B26               | AETXD0/SS3/U4RX/U1CTS/CN20/RD14                       |     | B51               | TRCLK/RA6                 |                           |  |

| B27               | SDA5/SDI4/U2RX/PMA9/CN17/RF4                          |     | B52               | PMD0/RE0                  |                           |  |

| B28               | No Connect (NC)                                       |     | B53               | Vdd                       |                           |  |

| B29               | SCL3/SDO3/U1TX/RF8                                    |     | B54               | TRD2/RG14                 |                           |  |

| B30               | VUSB3V3                                               |     | B55               | TRD0/RG13                 |                           |  |

| B31               | D+/RG2                                                |     | B56               | PMD3/RE3                  |                           |  |

This pin is only available on PIC32MX795F512L devices. Note 1:

2:

Shaded package bumps are 5V tolerant. It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout. 3:

# PIC32MX5XX/6XX/7XX

NOTES:

I

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 31:24        | —                 | _                 |                   |                   | _                 | —                 |                  | —                |  |  |  |  |  |  |  |  |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   | BMXDUPBA<7:0>    |                  |  |  |  |  |  |  |  |  |  |

# REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

# Legend:

| Legena.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 **BMXDUPBA<9:0>:** DRM User Program Base Address Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernal mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

|                             | PIC32MX695F512H DEVICES         |               |               |              |             |                               |                               |                               |                               |                             |                               |                               |                             |                       |               |        |        |        |            |

|-----------------------------|---------------------------------|---------------|---------------|--------------|-------------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|---------------|--------|--------|--------|------------|

| ess                         |                                 |               |               |              |             |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |               |        |        |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14        | 29/13       | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3          | 18/2   | 17/1   | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         |               |              | —           | —                             | _                             |                               | _                             |                             | _                             | —                             |                             | _                     |               |        | _      | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | —             | _            | _           | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | -                             |                             | INT4EP                | INT3EP        | INT2EP | INT1EP | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —             | —            | —           | —                             | —                             | —                             | —                             | —                           | —                             | —                             | —                           | —                     | —             | —      | —      | —      | 0000       |

| 1010                        |                                 | 15:0          |               | —            | —           | —                             | _                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC           | <5:0>  |        |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |               |              |             |                               | IPTMR<31:0>                   |                               |                               |                             |                               |                               | 0000                        |                       |               |        |        |        |            |

| 1030                        | IFS0                            | 31:16         | I2C1MIF       | I2C1SIF      | I2C1BIF     | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | _                             | _                           | _                             | OC5IF                         | IC5IF                       | T5IF                  | INT4IF        | OC4IF  | IC4IF  | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF        | OC3IF        | IC3IF       | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | <b>INT0IF</b> | CS1IF  | CS0IF  | CTIF   | 0000       |

|                             |                                 | 31:16         | <b>IC3EIF</b> | IC2EIF       | IC1EIF      | ETHIF                         | —                             | _                             | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF        | DMA2IF | DMA1IF | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF        | FSCMIF       | _           | _                             | _                             | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF        | PMPIF  | AD1IF  | CNIF   | 0000       |

|                             |                                 | 31:16         |               |              |             |                               | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     |               | _      | _      | _      | 0000       |

| 1050                        | IFS2                            | 15:0          | _             | _            | _           | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF         | PMPEIF | IC5EIF | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE       | I2C1SIE      | I2C1BIE     | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | _                             |                             | _                             | OC5IE                         | IC5IE                       | T5IE                  | INT4IE        | OC4IE  | IC4IE  | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE        | OC3IE        | IC3IE       | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE        | CS1IE  | CS0IE  | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE        | IC2EIE       | IC1EIE      | ETHIE                         | —                             | _                             | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b> | DMA2IE | DMA1IE | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE        | FSCMIE       | _           | _                             | -                             | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE        | PMPIE  | AD1IE  | CNIE   | 0000       |

|                             |                                 | 31:16         |               |              | _           | _                             | _                             | _                             |                               | _                           | _                             | _                             | _                           | _                     |               | _      | _      | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _             | _            | _           | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE         | PMPEIE | IC5EIE | IC4EIE | 0000       |

|                             |                                 | 31:16         | _             | _            | _           |                               | INT0IP<2:0>                   |                               | INTOIS                        |                             | _                             | _                             | _                           |                       | CS1IP<2:0>    |        | CS1IS  |        | 0000       |

| 1090                        | IPC0                            | 15:0          | _             | _            | _           |                               | CS0IP<2:0>                    |                               | CSOIS                         | S<1:0>                      | _                             | _                             | _                           |                       | CTIP<2:0>     |        | CTIS   |        | 0000       |

| 1040                        | IPC1                            | 31:16         | _             | _            | _           |                               | INT1IP<2:0>                   |                               | INT1IS                        | S<1:0>                      | _                             | _                             | _                           | (                     | OC1IP<2:0>    |        | OC1IS  | S<1:0> | 0000       |

| 10A0                        | IPUT                            | 15:0          | _             | _            | _           |                               | IC1IP<2:0>                    |                               | IC1IS                         | <1:0>                       | _                             | _                             |                             |                       | T1IP<2:0>     |        | T1IS-  | <1:0>  | 0000       |

| 10B0                        | IPC2                            | 31:16         |               | —            | _           |                               | INT2IP<2:0>                   |                               | INT2IS                        | S<1:0>                      | —                             | —                             | _                           | (                     | OC2IP<2:0>    | •      | OC2IS  | S<1:0> | 0000       |

| IUD0                        | 1602                            | 15:0          | _             | —            | —           |                               | IC2IP<2:0>                    |                               | IC2IS                         | <1:0>                       | —                             | —                             | _                           |                       | T2IP<2:0>     |        | T2IS-  | <1:0>  | 0000       |

| 10C0                        | IPC3                            | 31:16         | —             | —            | -           |                               | INT3IP<2:0>                   |                               | INT3IS                        | S<1:0>                      | —                             | —                             |                             | (                     | OC3IP<2:0>    |        | OC3IS  | S<1:0> | 0000       |

| 1000                        | 1 00                            | 15:0          |               | —            | —           |                               | IC3IP<2:0>                    |                               | IC3IS                         | <1:0>                       | —                             | —                             | —                           |                       | T3IP<2:0>     |        | T3IS-  | <1:0>  | 0000       |

| Legend                      | <b>d:</b> x =                   | unknow        | n value on    | Reset; — = I | unimplement | ted, read as                  | '0'. Reset va                 | lues are sho                  | wn in hexad                   | ecimal.                     |                               |                               |                             |                       |               |        |        |        |            |

#### **TABLE 7-3:** INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND DIC22MV605E512U DEVICES

DS60001156J-page 79

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

© 2009-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00:40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

|              |                   | •                 | •                 | CHEW1             | <7:0>             |                   |                  | •                |  |  |  |

# REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   | CHEW2<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

|              |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | _                 |                   | _                 |                   |                   |                  | _                |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | -                 |                   | -                 |                   |                   |                  |                  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |  |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | LSPD              | RETRYDIS          | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |  |

# REGISTER 11-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

### Legend:

bit 1

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device enabled

- 0 = Direct connection to a low-speed device disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NACK'd transactions disabled

- 0 = Retry NACK'd transactions enabled; retry done in hardware

- bit 5 Unimplemented: Read as '0'

- bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

- If EPTXEN = 1 and EPRXEN = 1:

- 1 = Disable Endpoint 'n' from control transfers; only TX and RX transfers are allowed

- 0 = Enable Endpoint 'n' for control (SETUP) transfers; TX and RX transfers are also allowed Otherwise, this bit is ignored.

- bit 3 EPRXEN: Endpoint Receive Enable bit

- 1 = Endpoint 'n' receive is enabled

- 0 = Endpoint 'n' receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint 'n' transmit is enabled

- 0 = Endpoint 'n' transmit is disabled

- EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint 'n' was stalled

- 0 = Endpoint 'n' was not stalled

- bit 0 **EPHSHK:** Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

| Т | ABLE 12 | PORTG REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H | Н. |

|---|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   |         | PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES                                                                                                                   | ,  |

|   | ssa     | Bits                                                                                                                                                                                            |    |

| ö                          |                                 | Φ         |       |       |       |       |           |                    |        |                 |        | <i>(</i> 0 |      |      |        |        |      |      |           |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-----------|--------------------|--------|-----------------|--------|------------|------|------|--------|--------|------|------|-----------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11     | 26/10              | 25/9   | 24/8            | 23/7   | 22/6       | 21/5 | 20/4 | 19/3   | 18/2   | 17/1 | 16/0 | All Reset |

| 6180                       | TRISG                           | 31:16     | —     | —     | —     | _     | —         | —                  | _      | —               | —      | —          | _    | _    | -      | _      | _    | _    | 0000      |

| 6160                       | TRIBU                           | 15:0      | _     | _     | _     | _     | _         |                    | TRISG9 | TRISG8          | TRISG7 | TRISG6     | _    |      | TRISG3 | TRISG2 | -    |      | 03CC      |

| 6100                       | PORTG                           | 31:16     | _     | _     | _     | _     | _         |                    | _      | _               | _      | _          | _    |      |        |        | -    |      | 0000      |

| 6190                       | PURIG                           | 15:0      | _     | _     | _     | _     | _         |                    | RG9    | RG8             | RG7    | RG6        | _    |      | RG3    | RG2    | -    |      | xxxx      |

| 61A0                       | LATG                            | 31:16     | _     | _     | _     | _     | _         |                    | _      | _               | _      | _          | _    |      |        |        | -    |      | 0000      |

| OTAU                       | LAIG                            | 15:0      | _     | _     | _     | _     | _         |                    | LATG9  | LATG8           | LATG7  | LATG6      | _    |      | LATG3  | LATG2  | -    |      | xxxx      |

| 61B0                       | ODCG                            | 31:16     | _     | _     | _     | _     | -         | _                  | _      | _               | _      | -          | _    |      |        | -      | _    |      | 0000      |

| 01B0                       | ODCG                            | 15:0      | _     | _     | _     | _     | -         | _                  | ODCG9  | ODCG8           | ODCG7  | ODCG6      | _    |      | ODCG3  | ODCG2  | _    |      | 0000      |

| Laware                     |                                 |           |       | Deret |       |       | fal Deset | alter a successful |        | dia statistical |        |            |      |      |        |        |      |      |           |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

### TABLE 12-12: PORTG REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 |           |         | Bits    |         |         |       |       |        |        |        |        |      |      |        |        | <i>(</i> 0 |        |            |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|--------|--------|--------|--------|------|------|--------|--------|------------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9   | 24/8   | 23/7   | 22/6   | 21/5 | 20/4 | 19/3   | 18/2   | 17/1       | 16/0   | All Resets |

| 6180                        | TRISG                           | 31:16     | _       | —       | _       | -       | _     | —     | -      | —      | —      | -      | —    | -    | -      | -      | -          | -      | 0000       |

| 0100                        | TRISG                           | 15:0      | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _     | _     | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _    | _    | TRISG3 | TRISG2 | TRISG1     | TRISG0 | F3CF       |

| 6100                        | PORTG                           | 31:16     |         | _       |         | _       |       | -     | -      | -      | -      | —      | -    | —    | —      | —      | _          | —      | 0000       |

| 6190                        | PURIG                           | 15:0      | RG15    | RG14    | RG13    | RG12    |       |       | RG9    | RG8    | RG7    | RG6    |      |      | RG3    | RG2    | RG1        | RG0    | xxxx       |

| 61A0                        | LATG                            | 31:16     | -       | _       |         | _       | -     | -     | -      | -      | -      | —      | -    | —    | —      | —      | —          | —      | 0000       |

| 61A0                        | LAIG                            | 15:0      | LATG15  | LATG14  | LATG13  | LATG12  | _     | _     | LATG9  | LATG8  | LATG7  | LATG6  | _    | -    | LATG3  | LATG2  | LATG1      | LATG0  | xxxx       |

| 61B0                        | ODCG                            | 31:16     |         | —       | _       | _       |       | _     |        | _      | _      | —      | _    | —    | —      | —      | —          | —      | 0000       |

| 0160                        | ODCG                            | 15:0      | ODCG15  | ODCG14  | ODCG13  | ODCG12  | _     | -     | ODCG9  | ODCG8  | ODCG7  | ODCG6  | -    | _    | ODCG3  | ODCG2  | ODCG1      | ODCG0  | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                    | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | —                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

# REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Module On bit<sup>(1)</sup>

- 1 = Output Compare module is enabled

- 0 = Output Compare module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation when CPU is in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 **OC32:** 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisons to the 32-bit timer source

- 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 **OCFLT:** PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (only cleared in hardware)

- 0 = PWM Fault condition has not occurred

### bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin enabled

- 110 = PWM mode on OCx; Fault pin disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM < 2:0 > = 111. It is read as '0' in all other modes.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN15 MSEL15<1:0> |                   |                   | FSEL15<4:0>       |                   |                   |                  |                  |  |  |

| 22:46        | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN14             | MSEL1             | 4<1:0>            |                   | F                 | SEL14<4:0>        |                  |                  |  |  |

| 15:8         | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN13             | MSEL1             | 3<1:0>            |                   | F                 | SEL13<4:0>        |                  |                  |  |  |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN12             | MSEL1             | 2<1:0>            |                   | F                 | SEL12<4:0>        |                  |                  |  |  |

# REGISTER 24-13: CIFLTCON3: CAN FILTER CONTROL REGISTER 3

### Legend:

| R = Readable bit  | W = Writable bit | le bit U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|-------------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                      | x = Bit is unknown |  |  |

| bit 31    | FLTEN15: Filter 15 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | MSEL15<1:0>: Filter 15 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 28-24 | FSEL15<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| bit 23    | FLTEN14: Filter 14 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                           |

| bit 22-21 | MSEL14<1:0>: Filter 14 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                        |

| bit 20-16 | FSEL14<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0 |

| Note:     | The hits in this register can only be modified if the correspondir                                                                                                                                                                                                                         |

**Note:** The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 24-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4 (CONTINUED)

|           | (                                                           |

|-----------|-------------------------------------------------------------|

| bit 15    | FLTEN17: Filter 13 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 14-13 | MSEL17<1:0>: Filter 17 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 12-8  | FSEL17<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 7     | FLTEN16: Filter 16 Enable bit                               |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 6-5   | MSEL16<1:0>: Filter 16 Mask Select bits                     |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 4-0   | FSEL16<4:0>: FIFO Selection bits                            |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

|           |                                                             |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# PIC32MX5XX/6XX/7XX

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31.24        | FLTEN31           | MSEL3             | 51<1:0>           | FSEL31<4:0>       |                   |                   |                  |                  |  |  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | FLTEN30           | MSEL3             | 0<1:0>            |                   |                   | FSEL30<4:0>       |                  |                  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | FLTEN29           | MSEL2             | 9<1:0>            |                   |                   | FSEL29<4:0>       |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | FLTEN28           | MSEL2             | 8<1:0>            |                   |                   | FSEL28<4:0>       |                  |                  |  |  |

# REGISTER 24-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

|           |                                                                          | 0 – Dit is cleared           |                                       |

|-----------|--------------------------------------------------------------------------|------------------------------|---------------------------------------|

| bit 31    | <b>FLTEN31:</b> Filter 31 Enable bit<br>1 = Filter is enabled            |                              |                                       |

|           | 0 = Filter is disabled                                                   |                              |                                       |

| bit 30-29 | MSEL31<1:0>: Filter 31 Mask Select                                       | t bits                       |                                       |

|           | 11 = Acceptance Mask 3 selected                                          |                              |                                       |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected       |                              |                                       |

|           | 00 = Acceptance Mask 0 selected                                          |                              |                                       |

| bit 28-24 | FSEL31<4:0>: FIFO Selection bits                                         |                              |                                       |

|           | 11111 = Message matching filter is                                       |                              |                                       |

|           | 11110 = Message matching filter is                                       | stored in FIFO buffer 30     |                                       |

|           | •                                                                        |                              |                                       |

|           | •                                                                        | atored in FIFO buffer (      |                                       |

|           | 00001 = Message matching filter is<br>00000 = Message matching filter is |                              |                                       |

| bit 23    | FLTEN30: Filter 30Enable bit                                             |                              |                                       |

|           | 1 = Filter is enabled                                                    |                              |                                       |

|           | 0 = Filter is disabled                                                   |                              |                                       |

| bit 22-21 | MSEL30<1:0>: Filter 30Mask Select                                        | t bits                       |                                       |

|           | 11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected       |                              |                                       |

|           | 01 = Acceptance Mask 2 selected                                          |                              |                                       |

|           | 00 = Acceptance Mask 0 selected                                          |                              |                                       |

| bit 20-16 | FSEL30<4:0>: FIFO Selection bits                                         |                              |                                       |

|           | 11111 = Message matching filter is                                       |                              |                                       |

|           | 11110 = Message matching filter is                                       | stored in FIFO buffer 30     |                                       |

|           | •                                                                        |                              |                                       |

|           | • 0.0001 - Magazara matching filter is                                   | stored in EIEO buffer 1      |                                       |

|           | 00001 = Message matching filter is<br>00000 = Message matching filter is |                              |                                       |

|           |                                                                          |                              |                                       |

| Note:     | The bits in this register can only be                                    | modified if the correspondir | ng filter enable (FLTENn) bit is '0'. |

# REGISTER 25-27: EMAC1CLRT: ETHERNET CONTROLLER MAC COLLISION WINDOW/RETRY LIMIT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   | —                 |                  | —                |

| 15:8         | U-0               | U-0               | R/W-1             | R/W-1             | R/W-0             | R/W-1             | R/W-1            | R/W-1            |

| 10.0         |                   | —                 |                   |                   | CWINDO            | W<5:0>            |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 7.0          | _                 |                   | _                 | _                 |                   | RETX<             | <3:0>            |                  |

### Legend:

| Logonal           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

### bit 31-14 Unimplemented: Read as '0'

bit 13-8 **CWINDOW<5:0>:** Collision Window bits

This is a programmable field representing the slot time or collision window during which collisions occur in properly configured networks. Since the collision window starts at the beginning of transmission, the preamble and SFD is included. Its default of 0x37 (55d) corresponds to the count of frame bytes at the end of the window.

bit 7-4 Unimplemented: Read as '0'

### bit 3-0 RETX<3:0>: Retransmission Maximum bits

This is a programmable field specifying the number of retransmission attempts following a collision before aborting the packet due to excessive collisions. The Standard specifies the maximum number of attempts (attemptLimit) to be 0xF (15d). Its default is '0xF'.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

# 28.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This section describes power-saving features for the PIC32MX5XX/6XX/7XX family of devices. These devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 28.1 Power-Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the Peripheral Bus Clock (PBCLK) and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

# 28.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- **Posc Idle mode:** the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- **Sosc Idle mode:** the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock running.

- Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 28.3 Power-Saving Operation

Peripherals and the CPU can be halted or disabled to further reduce power consumption.

# 28.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is halted

- The system clock source is typically shutdown. See Section 28.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode

- The BOR circuit, if enabled, remains operative during Sleep mode

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption

# REGISTER 29-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

- bit 3 ICESEL: In-Circuit Emulator/Debugger Communication Channel Select bit

- 1 = PGEC2/PGED2 pair is used

- 0 = PGEC1/PGED1 pair is used

- bit 2 Reserved: Write '1'

- bit 1-0 DEBUG<1:0>: Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 11 = Debugger is disabled

- 10 = Debugger is enabled

- 01 = Reserved (same as '11' setting)

- 00 = Reserved (same as '11' setting)

# 31.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

# 31.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

# 31.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

# 31.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

# 31.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| DC CHARACTERISTICS |        |                                                         | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |          |       |                                                   |  |

|--------------------|--------|---------------------------------------------------------|------------------------------------------------------|------------------------|----------|-------|---------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                         | Min.                                                 | Typical <sup>(1)</sup> | Max.     | Units | Conditions                                        |  |

|                    | VIL    | Input Low Voltage                                       |                                                      |                        |          |       |                                                   |  |

| DI10               |        | I/O Pins:                                               |                                                      |                        |          |       |                                                   |  |

|                    |        | with TTL Buffer                                         | Vss                                                  | —                      | 0.15 Vdd | V     |                                                   |  |

|                    |        | with Schmitt Trigger Buffer                             | Vss                                                  | —                      | 0.2 Vdd  | V     |                                                   |  |

| DI15               |        | MCLR <sup>(2)</sup>                                     | Vss                                                  | —                      | 0.2 Vdd  | V     |                                                   |  |

| DI16               |        | OSC1 (XT mode)                                          | Vss                                                  | —                      | 0.2 Vdd  | V     | (Note 4)                                          |  |

| DI17               |        | OSC1 (HS mode)                                          | Vss                                                  | —                      | 0.2 Vdd  | V     | (Note 4)                                          |  |

| DI18               |        | SDAx, SCLx                                              | Vss                                                  | _                      | 0.3 Vdd  | V     | SMBus disabled<br>(Note 4)                        |  |

| DI19               |        | SDAx, SCLx                                              | Vss                                                  | —                      | 0.8      | V     | SMBus enabled<br>(Note 4)                         |  |

|                    | Vih    | Input High Voltage                                      |                                                      |                        |          |       |                                                   |  |

| DI20               |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.65 VDD                                             | —                      | Vdd      | V     | (Note 4,6)                                        |  |

|                    |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.25 VDD + 0.8V                                      | _                      | 5.5      | V     | (Note 4,6)                                        |  |

|                    |        | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.65 Vdd                                             | _                      | 5.5      | V     |                                                   |  |

| DI28               |        | SDAx, SCLx                                              | 0.65 Vdd                                             | —                      | 5.5      | V     | SMBus disabled (Note 4,6)                         |  |

| DI29               |        | SDAx, SCLx                                              | 2.1                                                  | _                      | 5.5      | V     | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |  |

| DI30               | ICNPU  | Change Notification Pull-up Current                     | —                                                    | —                      | -50      | μA    | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |  |

| DI31               | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup> | —                                                    | 50                     | —        | μA    | VDD = 3.3V, VPIN = VDD                            |  |

# TABLE 32-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V-tolerant pins.