Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | ·                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512l-80i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES

| 1          | 21-PIN TFBGA (BOTTOM VIEW)                                                                  |          | L11                                                          |

|------------|---------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|

|            | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |          | L1 A11                                                       |

|            | te: The TFBGA package skips from row "H                                                     |          |                                                              |

| Pin #      | Full Pin Name                                                                               | Pin #    | Full Pin Name                                                |

| A1         | PMD4/RE4                                                                                    | E2       | T4CK/RC3                                                     |

| A2         | PMD3/RE3                                                                                    | E3       | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                                                   | E4       | T3CK/RC2                                                     |

| A4         | PMD0/RE0                                                                                    | E5       | VDD                                                          |

| A5         | PMD8/RG0                                                                                    | E6       | ETXERR/PMD9/RG1                                              |

| A6         | ETXD0/PMD10/RF1                                                                             | E7       | Vss                                                          |

| A7         | Vdd                                                                                         | E8       | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                                                         | E9       | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                                                        | E10      | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                                                     | E11      | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                                                     | F1       | MCLR                                                         |

| B1         | No Connect (NC)                                                                             | F2       | ERXDV/AERXDV/ECRSDV/AECRSDV//SCL4/SDO2/U3TX/PMA3/CN10/RG8    |

| B2         | AERXERR/RG15                                                                                | F3       | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                                                    | F4       | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                                                    | F5       | Vss                                                          |

| B5         | TRD3/RA7                                                                                    | F6       | No Connect (NC)                                              |

| B6         | ETXD1/PMD11/RF0                                                                             | F7       | No Connect (NC)                                              |

| B7         | VCAP                                                                                        | F8       | VDD                                                          |

| B8         | PMRD/CN14/RD5                                                                               | F9       | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                                                     | F10      | Vss                                                          |

| B10        | Vss                                                                                         | F11      | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                                                         | G1       | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                                                    | G2       | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                                                         | G3       | TMS/RA0                                                      |

| C3<br>C4   | TRD1/RG12<br>TRD2/RG14                                                                      | G4<br>G5 | No Connect (NC)<br>VDD                                       |

| C4         | TRCLK/RA6                                                                                   | G5<br>G6 | Vss                                                          |

|            | No Connect (NC)                                                                             | G0<br>G7 | Vss                                                          |

| C0<br>C7   | ETXCLK/PMD15/CN16/RD7                                                                       | G7<br>G8 | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9       | TDO/RA5                                                      |

| C9         | VDD                                                                                         | G10      | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                                                              | G11      | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                                                             | H1       | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                                                    | H2       | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                                                    | H3       | Vss                                                          |

| D3         | PMD5/RE5                                                                                    | H4       | VDD                                                          |

| D4         | Vss                                                                                         | H5       | No Connect (NC)                                              |

| D5         | Vss                                                                                         | H6       | VDD                                                          |

| D6         | No Connect (NC)                                                                             | H7       | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                                                        | H8       | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                                                       | H9       | VUSB3V3                                                      |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10      | D+/RG2                                                       |

| D10        | No Connect (NC)                                                                             | H11      | SCL2/RA2                                                     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1       | AN3/C2IN+/CN5/RB3                                            |

| E1<br>Note | T5CK/SDI1/RC4<br>1: Shaded pins are 5V tolerant.                                            | J2       | AN2/C2IN-/CN4/RB2                                            |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                               | Pin Nun         | nber <sup>(1)</sup> |                 | Pin  | Duffer               |                                                   |  |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|------|----------------------|---------------------------------------------------|--|--|

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре | Buffer<br>Type       | Description                                       |  |  |

| RG0      | —                                             | 90              | A5                  | A61             | I/O  | ST                   | PORTG is a bidirectional I/O port                 |  |  |

| RG1      | —                                             | 89              | E6                  | B50             | I/O  | ST                   |                                                   |  |  |

| RG6      | 4                                             | 10              | E3                  | A7              | I/O  | ST                   |                                                   |  |  |

| RG7      | 5                                             | 11              | F4                  | B6              | I/O  | ST                   |                                                   |  |  |

| RG8      | 6                                             | 12              | F2                  | A8              | I/O  | ST                   |                                                   |  |  |

| RG9      | 8                                             | 14              | F3                  | A9              | I/O  | ST                   |                                                   |  |  |

| RG12     | —                                             | 96              | C3                  | A65             | I/O  | ST                   |                                                   |  |  |

| RG13     | —                                             | 97              | A3                  | B55             | I/O  | ST                   | -                                                 |  |  |

| RG14     | —                                             | 95              | C4                  | B54             | I/O  | ST                   |                                                   |  |  |

| RG15     | —                                             | 1               | B2                  | A2              | I/O  | ST                   |                                                   |  |  |

| RG2      | 37                                            | 57              | H10                 | B31             | Ι    | ST                   | PORTG input pins                                  |  |  |

| RG3      | 36                                            | 56              | J11                 | A38             | I    | ST                   |                                                   |  |  |

| T1CK     | 48                                            | 74              | B11                 | B40             |      | ST                   | Timer1 external clock input                       |  |  |

| T2CK     | —                                             | 6               | D1                  | A5              | I    | ST                   | Timer2 external clock input                       |  |  |

| T3CK     | —                                             | 7               | E4                  | B4              |      | ST                   | Timer3 external clock input                       |  |  |

| T4CK     | —                                             | 8               | E2                  | A6              |      | ST                   | Timer4 external clock input                       |  |  |

| T5CK     | —                                             | 9               | E1                  | B5              |      | ST                   | Timer5 external clock input                       |  |  |

| U1CTS    | 43                                            | 47              | L9                  | B26             |      | ST                   | UART1 clear to send                               |  |  |

| U1RTS    | 49                                            | 48              | K9                  | A31             | 0    |                      | UART1 ready to send                               |  |  |

| U1RX     | 50                                            | 52              | K11                 | A36             | I    | ST                   | UART1 receive                                     |  |  |

| U1TX     | 51                                            | 53              | J10                 | B29             | 0    | _                    | UART1 transmit                                    |  |  |

| U3CTS    | 8                                             | 14              | F3                  | A9              | I    | ST                   | UART3 clear to send                               |  |  |

| U3RTS    | 4                                             | 10              | E3                  | A7              | 0    | _                    | UART3 ready to send                               |  |  |

| U3RX     | 5                                             | 11              | F4                  | B6              | I    | ST                   | UART3 receive                                     |  |  |

| U3TX     | 6                                             | 12              | F2                  | A8              | 0    | _                    | UART3 transmit                                    |  |  |

| U2CTS    | 21                                            | 40              | K6                  | A27             | I    | ST                   | UART2 clear to send                               |  |  |

| U2RTS    | 29                                            | 39              | L6                  | B22             | 0    |                      | UART2 ready to send                               |  |  |

| U2RX     | 31                                            | 49              | L10                 | B27             | I    | ST                   | UART2 receive                                     |  |  |

| U2TX     | 32                                            | 50              | L11                 | A32             | 0    |                      | UART2 transmit                                    |  |  |

| U4RX     | 43                                            | 47              | L9                  | B26             | 1    | ST                   | UART4 receive                                     |  |  |

| U4TX     | 49                                            | 48              | K9                  | A31             | 0    | _                    | UART4 transmit                                    |  |  |

| U6RX     | 8                                             | 14              | F3                  | A9              | I    | ST                   | UART6 receive                                     |  |  |

| U6TX     | 4                                             | 10              | E3                  | A7              | 0    | _                    | UART6 transmit                                    |  |  |

| U5RX     | 21                                            | 40              | K6                  | A27             | I    | ST                   | UART5 receive                                     |  |  |

| U5TX     | 29                                            | 39              | L6                  | B22             | 0    |                      | UART5 transmit                                    |  |  |

| SCK1     | _                                             | 70              | D11                 | B38             | I/O  | ST                   | Synchronous serial clock input/output<br>for SPI1 |  |  |

| 5        | CMOS = CMO<br>ST = Schmitt T<br>TL = TTL inpu | rigger input    |                     |                 |      | nalog = A<br>= Outpu | Analog input P = Power                            |  |  |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

## 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved.                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved.                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | Ebase                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved.                                                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved.                                                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

|                    | <b>I</b>                |                                                                          |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

## REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | -                 | -                 | —                 | —                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 |                   |                   |                   | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                   | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | [<7:0>            |                   |                  |                  |

# Legend:

| 5                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits <u>Pattern Terminate mode:</u> Data to be matched must be stored in this register to allow terminate on match.

> All other modes: Unused.

| Bit<br>Range |       |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------|-----|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0   | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _     | _   | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0   | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |       | _   |                   |                   | _                 |                   |                  | —                |

| 45.0         | R/W-0 | U-0 | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON    | —   | SIDL              | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0   | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _     | _   |                   |                   | _                 |                   | _                | _                |

## REGISTER 12-1: CNCON: CHANGE NOTICE CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = Idle mode halts CN operation

- 0 = Idle mode does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

NOTES:

## REGISTER 18-2: SPIxSTAT: SPI STATUS REGISTER

- bit 1 SPITBF: SPI Transmit Buffer Full Status bit

- 1 = Transmit not yet started, SPITXB is full

- 0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

### Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

Standard Buffer Mode:

bit 0

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | U-0               | U-0               | U-0               | U-0 R/W-0         |                   | R/W-0 R/W-0      |                  |  |  |  |  |  |

| 31:24        | CH0NB             | —                 | —                 | —                 |                   | CH0SB             | <3:0>            |                  |  |  |  |  |  |

| 00.40        | R/W-0 U-0         |                   | U-0               | U-0               | R/W-0 R/W-0       |                   | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | CH0NA             | _                 | —                 | _                 | CH0SA<3:0>        |                   |                  |                  |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                  | U-0              |  |  |  |  |  |

| 15:8         | _                 | —                 | —                 | —                 | _                 |                   | _                | _                |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 7:0          | _                 | _                 |                   | _                 |                   |                   | _                | _                |  |  |  |  |  |

## REGISTER 23-4: AD1CHS: ADC INPUT SELECT REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | CHONB: Negative Input Select bit for Sample B                           |

|-----------|-------------------------------------------------------------------------|

|           | 1 = Channel 0 negative input is AN1                                     |

|           | 0 = Channel 0 negative input is VREFL                                   |

| bit 30-28 | Unimplemented: Read as '0'                                              |

| bit 27-24 | CH0SB<3:0>: Positive Input Select bits for Sample B                     |

|           | 1111 = Channel 0 positive input is AN15                                 |

|           | •                                                                       |

|           | •                                                                       |

|           | •                                                                       |

|           | 0001 = Channel 0 positive input is AN1                                  |

|           | 0000 = Channel 0 positive input is AN0                                  |

| bit 23    | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting       |

|           | 1 = Channel 0 negative input is AN1                                     |

|           | 0 = Channel 0 negative input is VREFL                                   |

| bit 22-20 | Unimplemented: Read as '0'                                              |

| bit 19-16 | CH0SA<3:0>: Positive Input Select bits for Sample A Multiplexer Setting |

|           | 1111 = Channel 0 positive input is AN15                                 |

|           | •                                                                       |

|           | •                                                                       |

|           | •                                                                       |

|           | 0001 = Channel 0 positive input is AN1                                  |

|           | 0000 = Channel 0 positive input is AN0                                  |

| bit 15-0  | Unimplemented: Read as '0'                                              |

|           |                                                                         |

|                             | PIC32MX775F512L AND PIC32MX795F512L DEVICES (CONTINUED) |               |         |               |        |                                                  |       |            |          |           |         |                         |         |       |          |            |             |                |            |

|-----------------------------|---------------------------------------------------------|---------------|---------|---------------|--------|--------------------------------------------------|-------|------------|----------|-----------|---------|-------------------------|---------|-------|----------|------------|-------------|----------------|------------|

| ess                         |                                                         | é             |         |               |        |                                                  |       |            |          | Bit       | s       |                         |         |       |          |            |             |                |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                         | Bit Range     | 31/15   | 30/14         | 29/13  | 28/12                                            | 27/11 | 26/10      | 25/9     | 24/8      | 23/7    | 22/6                    | 21/5    | 20/4  | 19/3     | 18/2       | 17/1        | 16/0           | All Resets |

| C100                        | C2FLTCON4                                               | 31:16         | FLTEN19 | MSEL1         | 9<1:0> |                                                  |       | FSEL19<4:0 | >        |           | FLTEN18 | MSEL1                   | 8<1:0>  |       | F        | SEL18<4:0  | >           |                | 0000       |

| 0100                        | C2FLICON4                                               | 15:0          | FLTEN17 | MSEL1         | 7<1:0> |                                                  |       | FSEL17<4:0 | >        |           | FLTEN16 | MSEL1                   | 6<1:0>  |       |          | FSEL16<4:0 | ):          |                | 0000       |

| C110                        | C2FLTCON5                                               | 31:16         | FLTEN23 | MSEL2         | 3<1:0> |                                                  |       | FSEL23<4:0 | >        |           | FLTEN22 | MSEL2                   | 22<1:0> |       | F        | SEL22<4:0  | >           |                | 0000       |

| CIIU                        | CZFLICONS                                               | 15:0          | FLTEN21 | MSEL2         | 1<1:0> |                                                  |       | FSEL21<4:0 | >        |           | FLTEN20 | MSEL2                   | 20<1:0> |       | F        | SEL20<4:0  | >           |                | 0000       |

| C120                        | C2FLTCON6                                               | 31:16         | FLTEN27 | MSEL2         | 7<1:0> |                                                  |       | FSEL27<4:0 | >        |           | FLTEN26 | MSEL2                   | 26<1:0> |       | F        | SEL26<4:0  | >           |                | 0000       |

| 0120                        | OZI EI CONO                                             | 15:0          | FLTEN25 | MSEL2         | 5<1:0> | 1:0> FSEL25<4:0>                                 |       |            |          |           |         | MSEL24<1:0> FSEL24<4:0> |         |       |          | 0000       |             |                |            |

| C130                        | C2FLTCON7                                               | 31:16         | FLTEN31 | MSEL3         | 1<1:0> | <1:0> FSEL31<4:0>                                |       |            |          |           |         | MSEL30<1:0> FSEL30<4:0> |         |       |          | 0000       |             |                |            |

| 0100                        |                                                         |               | FLTEN29 | MSEL2         | 9<1:0> | 1:0> FSEL29<4:0> FLTEN28 MSEL28<1:0> FSEL28<4:0> |       |            |          |           |         |                         |         |       |          | 0000       |             |                |            |

| C140                        | 02.00.11                                                | 31:16         |         |               |        |                                                  |       | SID<10:0>  |          |           |         |                         |         |       | EXID     | -          | EID<        | 17:16>         | xxxx       |

|                             | (n = 0-31)                                              | 15:0          |         |               |        |                                                  |       |            |          | EID<1     | 5:0>    |                         |         |       |          |            |             |                | xxxx       |

| C340                        |                                                         | 31:16<br>15:0 |         |               |        |                                                  |       |            |          | C2FIFOB   | A<31:0> |                         |         |       |          |            |             |                | 0000       |

| 0250                        | C2FIFOCONn<br>(n = 0-31)                                | 31:16         | _       | —             | —      | —                                                | —     | -          | —        | —         | —       | _                       | —       |       |          | FSIZE<4:0> | <b>&gt;</b> |                | 0000       |

| 0350                        | (n = 0-31)                                              | 15:0          |         | FRESET        | UINC   | DONLY                                            |       | —          | _        |           | TXEN    | TXABAT                  | TXLARB  | TXERR | TXREQ    | RTREN      | TXPR        | l<1:0>         | 0000       |

| C360                        | C2FIFOINTn                                              | 31:16         | _       | —             | —      | —                                                | _     | TXNFULLIE  | TXHALFIE | TXEMPTYIE | _       | —                       | -       | _     | RXOVFLIE | RXFULLIE   | RXHALFIE    | RXN<br>EMPTYIE | 0000       |

| 0300                        | (n = 0-31)                                              | 15:0          | -       | —             | —      | -                                                | -     | TXNFULLIF  | TXHALFIF | TXEMPTYIF | -       | —                       | -       | -     | RXOVFLIF | RXFULLIF   | RXHALFIF    | RXN<br>EMPTYIF | 0000       |

| C370                        | C2FIFOUAn                                               |               |         |               |        |                                                  |       |            |          | C2FIFOU   | A<31:0> |                         |         |       |          |            |             |                | 0000       |

|                             | (n = 0-31)                                              | 15:0          |         |               |        |                                                  |       |            |          |           |         |                         |         |       |          |            |             |                | 0000       |

| C380                        | C2FIFOCIn<br>(n = 0-31)                                 | 31:16         |         | _             | _      | _                                                | _     |            | _        | _         | _       | —                       | _       | _     |          | -          |             | —              | 0000       |

|                             | (1 = 0.31)                                              | 15:0          | —       | C2FIFOCI<4:0> |        |                                                  |       |            |          |           |         |                         |         | 0000  |          |            |             |                |            |

# TABLE 24-2: CAN2 REGISTER SUMMARY FOR PIC32MX775F256H, PIC32MX775F512H, PIC32MX795F512H, PIC32MX775F256L, PIC32MX775F512L, AND PIC32MX795F512L, DEVICES (CONTINUED)

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more Note 1: information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 31.24        | IVRIE             | WAKIE             | CERRIE            | SERRIE                | RBOVIE            | _                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | —                 | _                 | _                     | MODIE             | CTMRIE            | RBIE             | TBIE             |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | IVRIF             | WAKIF             | CERRIF            | SERRIF <sup>(1)</sup> | RBOVIF            | —                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                       | MODIF             | CTMRIF            | RBIF             | TBIF             |

## REGISTER 24-3: CIINT: CAN INTERRUPT REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | IVRIE: Invalid Message Received Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30    | WAKIE: CAN Bus Activity Wake-up Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                 |

| bit 29    | <b>CERRIE:</b> CAN Bus Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 28    | SERRIE: System Error Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                            |

| bit 27    | <b>RBOVIE:</b> Receive Buffer Overflow Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                          |

| bit 26-20 | Unimplemented: Read as '0'                                                                                                                                       |

| bit 19    | <b>MODIE:</b> Mode Change Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                       |

| bit 18    | <b>CTMRIE:</b> CAN Timestamp Timer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                              |

| bit 17    | <b>RBIE:</b> Receive Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                     |

| bit 16    | <b>TBIE:</b> Transmit Buffer Interrupt Enable bit<br>1 = Interrupt request is enabled<br>0 = Interrupt request is not enabled                                    |

| bit 15    | <b>IVRIF:</b> Invalid Message Received Interrupt Flag bit<br>1 = An invalid messages interrupt has occurred<br>0 = An invalid message interrupt has not occurred |

| Note 1:   | This bit can only be cleared by turning the CAN module Off and On by                                                                                             |

**Note 1:** This bit can only be cleared by turning the CAN module Off and On by clearing or setting the ON bit (CiCON<15>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                       |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

|              | —                 | _                 | _                 | —                 | _                       | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | _                 |                   |                         | FILHIT<4:0>       |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | l                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

## REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN7            | MSEL7<1:0>        |                   | FSEL7<4:0>        |                   |                   |                  |                  |

| 22:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN6            | MSEL6<1:0>        |                   | FSEL6<4:0>        |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN5            | MSEL5<1:0>        |                   | FSEL5<4:0>        |                   |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            | FSEL4<4:0>        |                   |                   |                  |                  |

## **REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | FLTEN7: Filter 7 Enable bit                                 |

|-----------|-------------------------------------------------------------|

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 28-24 | FSEL7<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 = Message matching filter is stored in FIFO buffer 30 |

|           | •                                                           |

|           | •                                                           |

|           | 00001 = Message matching filter is stored in FIFO buffer 1  |

|           | 00000 = Message matching filter is stored in FIFO buffer 0  |

| bit 23    | FLTEN6: Filter 6 Enable bit                                 |

|           | 1 = Filter is enabled                                       |

|           | 0 = Filter is disabled                                      |

| bit 22-21 | MSEL6<1:0>: Filter 6 Mask Select bits                       |

|           | 11 = Acceptance Mask 3 selected                             |

|           | 10 = Acceptance Mask 2 selected                             |

|           | 01 = Acceptance Mask 1 selected                             |

|           | 00 = Acceptance Mask 0 selected                             |

| bit 20-16 | FSEL6<4:0>: FIFO Selection bits                             |

|           | 11111 = Message matching filter is stored in FIFO buffer 31 |

|           | 11110 - Massage matching filter is stored in EIEO buffer 30 |

uffer 31 11110 = Message matching filter is stored in FIFO buffer 30

•

•

00001 = Message matching filter is stored in FIFO buffer 1 00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

## REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER

| bit 6 | PKTPEND: Packet Pending Interrupt bit                                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = RX packet pending in memory                                                                                                                                                                                                                     |

|       | 0 = RX packet is not pending in memory                                                                                                                                                                                                              |

|       | This bit is set when the BUFCNT counter has a value other than '0'. It is cleared by either a Reset or by writing the BUFCDEC bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.                                            |

| bit 5 | RXACT: Receive Activity Interrupt bit                                                                                                                                                                                                               |

|       | <ul><li>1 = RX packet data was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                     |

|       | This bit is set whenever RX packet data is stored in the RXBM FIFO. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

| bit 3 | TXDONE: Transmit Done Interrupt bit                                                                                                                                                                                                                 |

|       | <ul><li>1 = TX packet was successfully sent</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                              |

|       | This bit is set when the currently transmitted TX packet completes transmission, and the Transmit Status Vector is loaded into the first descriptor used for the packet. It is cleared by either a Reset or CPU write of a '1' to the CLR register. |

| bit 2 | TXABORT: Transmit Abort Condition Interrupt bit                                                                                                                                                                                                     |

|       | <ul><li>1 = TX abort condition occurred on the last TX packet</li><li>0 = No interrupt pending</li></ul>                                                                                                                                            |

|       | This bit is set when the MAC aborts the transmission of a TX packet for one of the following reasons:                                                                                                                                               |

|       | Jumbo TX packet abort                                                                                                                                                                                                                               |

|       | Underrun abort                                                                                                                                                                                                                                      |

|       | Excessive defer abort                                                                                                                                                                                                                               |

|       | Late collision abort                                                                                                                                                                                                                                |

|       | Excessive collisions abort                                                                                                                                                                                                                          |

|       | This bit is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                                                                    |

| bit 1 | RXBUFNA: Receive Buffer Not Available Interrupt bit                                                                                                                                                                                                 |

|       | <ul> <li>1 = RX Buffer Descriptor Not Available condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                 |

|       | This bit is set by a RX Buffer Descriptor Overrun condition. It is cleared by either a Reset or a CPU write of a '1' to the CLR register.                                                                                                           |

| bit 0 | RXOVFLW: Receive FIFO Over Flow Error bit                                                                                                                                                                                                           |

|       | <ul> <li>1 = RX FIFO Overflow Error condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                             |

|       | RXOVFLW is set by the RXBM Logic for an RX FIFO Overflow condition. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

|       |                                                                                                                                                                                                                                                     |

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

### REGISTER 25-20: ETHFRMRXOK: ETHERNET CONTROLLER FRAMES RECEIVED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | FRMRXOKCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | FRMRXOKCNT<7:0>   |                   |                   |                   |                   |                  |                  |  |  |

### Legend:

| 3                 |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 FRMRXOKCNT<15:0>: Frames Received OK Count bits

Increment count for frames received successfully by the RX Filter. This count will not be incremented if there is a Frame Check Sequence (FCS) or Alignment error.

Note 1: This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

The processor will exit, or 'wake-up', from Sleep mode on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep mode. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

### 28.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- · On any form of device Reset

- On a WDT time-out interrupt

### 28.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus (PB) can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as USB, interrupt controller, DMA, bus matrix and prefetch cache are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

### TABLE 32-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                               | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-Temp |         |       |       |            |  |

|--------------------|--------|---------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                               | Min.                                                                                                                                                                                               | Typical | Max.  | Units | Conditions |  |

| Operating Voltage  |        |                                                               |                                                                                                                                                                                                    |         |       |       |            |  |

| DC10               | Vdd    | Supply Voltage                                                | 2.3                                                                                                                                                                                                |         | 3.6   | V     |            |  |

| DC12               | Vdr    | RAM Data Retention Voltage <sup>(1)</sup>                     | 1.75                                                                                                                                                                                               |         |       | V     |            |  |

| DC16               | VPOR   | VDD Start Voltage to Ensure<br>Internal Power-on Reset Signal | 1.75                                                                                                                                                                                               |         | 2.1   | V     |            |  |

| DC17               | SVDD   | VDD Rise Rate to Ensure<br>Internal Power-on Reset Signal     | 0.00005                                                                                                                                                                                            |         | 0.115 | V/µs  | —          |  |

**Note 1:** This is the limit to which VDD can be lowered without losing RAM data.

2: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 32-10 for BOR values.

## 32.2 AC Characteristics and Timing Parameters

The information contained in this section defines PIC32MX5XX/6XX/7XX AC characteristics and timing parameters.

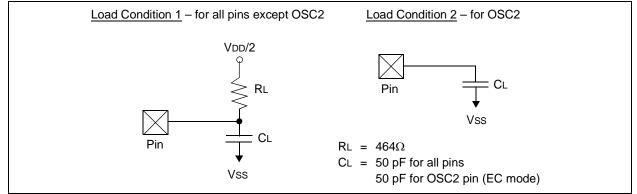

### FIGURE 32-1: LOAD CONDITIONS FOR DEVICE TIMING SPECIFICATIONS

### TABLE 32-16: CAPACITIVE LOADING REQUIREMENTS ON OUTPUT PINS

| AC CHARACTERISTICS |        |                       | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                                               |     |            |                                                                         |

|--------------------|--------|-----------------------|-------------------------------------------------------|-----------------------------------------------|-----|------------|-------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics       | Min.                                                  | . Typical <sup>(1)</sup> Max. Units Condition |     | Conditions |                                                                         |

| DO50               | Cosco  | OSC2 pin              |                                                       | _                                             | 15  | pF         | In XT and HS modes when an<br>external crystal is used to drive<br>OSC1 |

| DO56               | Сю     | All I/O pins and OSC2 |                                                       | —                                             | 50  | pF         | In EC mode                                                              |

| DO58               | Св     | SCLx, SDAx            |                                                       | —                                             | 400 | pF         | In I <sup>2</sup> C mode                                                |