Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512l-80i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 7: PIN NAMES FOR 100-PIN USB AND CAN DEVICES (CONTINUED)

**100-PIN TQFP (TOP VIEW)** PIC32MX534F064L PIC32MX564F064L PIC32MX564F128L PIC32MX575F512L PIC32MX575F256L 100 1 Pin # **Full Pin Name** Pin # Full Pin Name 71 IC4/PMCS1/PMA14/RD11 86 Vdd 72 SDO1/OC1/INT0/RD0 87 C1RX/PMD11/RF0 SOSCI/CN1/RC13 C1TX/PMD10/RF1 88 73 SOSCO/T1CK/CN0/RC14 74 89 PMD9/RG1 Vss PMD8/RG0 75 90 TRCLK/RA6 76 OC2/RD1 91 77 OC3/RD2 92 TRD3/RA7 78 OC4/RD3 93 PMD0/RE0 PMD1/RE1 79 IC5/PMD12/RD12 94 80 PMD13/CN19/RD13 95 TRD2/RG14 OC5/PMWR/CN13/RD4 96 TRD1/RG12 81 PMRD/CN14/RD5 TRD0/RG13 82 97 PMD14/CN15/RD6 98 PMD2/RE2 83 PMD15/CN16/RD7 PMD3/RE3 84 99 85 VCAP 100 PMD4/RE4

Note 1: Shaded pins are 5V tolerant.

1

### TABLE 8: PIN NAMES FOR 100-PIN USB AND ETHERNET DEVICES (CONTINUED)

# **100-PIN TQFP (TOP VIEW)**

PIC32MX664F064L PIC32MX664F128L PIC32MX675F256L PIC32MX675F512L PIC32MX695F512L

100

| Pin # | Full Pin Name                   | Pin # | Full Pin Name   |

|-------|---------------------------------|-------|-----------------|

| 71    | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11 | 86    | VDD             |

| 72    | SDO1/OC1/INT0/RD0               | 87    | ETXD1/PMD11/RF0 |

| 73    | SOSCI/CN1/RC13                  | 88    | ETXD0/PMD10/RF1 |

| 74    | SOSCO/T1CK/CN0/RC14             | 89    | ETXERR/PMD9/RG1 |

| 75    | Vss                             | 90    | PMD8/RG0        |

| 76    | OC2/RD1                         | 91    | TRCLK/RA6       |

| 77    | OC3/RD2                         | 92    | TRD3/RA7        |

| 78    | OC4/RD3                         | 93    | PMD0/RE0        |

| 79    | ETXD2/IC5/PMD12/RD12            | 94    | PMD1/RE1        |

| 80    | ETXD3/PMD13/CN19/RD13           | 95    | TRD2/RG14       |

| 81    | OC5/PMWR/CN13/RD4               | 96    | TRD1/RG12       |

| 82    | PMRD/CN14/RD5                   | 97    | TRD0/RG13       |

| 83    | ETXEN/PMD14/CN15/RD6            | 98    | PMD2/RE2        |

| 84    | ETXCLK/PMD15/CN16/RD7           | 99    | PMD3/RE3        |

| 85    | VCAP/VDDCORE                    | 100   | PMD4/RE4        |

Note 1: Shaded pins are 5V tolerant.

# TABLE 11: PIN NAMES FOR USB AND ETHERNET DEVICES

| 1          | 21-PIN TFBGA (BOTTOM VIEW)                                                                  |          | L11                                                          |

|------------|---------------------------------------------------------------------------------------------|----------|--------------------------------------------------------------|

|            | PIC32MX664F064L<br>PIC32MX664F128L<br>PIC32MX675F256L<br>PIC32MX675F512L<br>PIC32MX695F512L |          | L1 A11                                                       |

|            | te: The TFBGA package skips from row "H                                                     |          |                                                              |

| Pin #      | Full Pin Name                                                                               | Pin #    | Full Pin Name                                                |

| A1         | PMD4/RE4                                                                                    | E2       | T4CK/RC3                                                     |

| A2         | PMD3/RE3                                                                                    | E3       | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| A3         | TRD0/RG13                                                                                   | E4       | T3CK/RC2                                                     |

| A4         | PMD0/RE0                                                                                    | E5       | VDD                                                          |

| A5         | PMD8/RG0                                                                                    | E6       | ETXERR/PMD9/RG1                                              |

| A6         | ETXD0/PMD10/RF1                                                                             | E7       | Vss                                                          |

| A7         | Vdd                                                                                         | E8       | AETXEN/SDA1/INT4/RA15                                        |

| A8         | Vss                                                                                         | E9       | RTCC/EMDIO/AEMDIO/IC1/RD8                                    |

| A9         | ETXD2/IC5/PMD12/RD12                                                                        | E10      | SS1/IC2/RD9                                                  |

| A10        | OC3/RD2                                                                                     | E11      | AETXCLK/SCL1/INT3/RA14                                       |

| A11        | OC2/RD1                                                                                     | F1       | MCLR                                                         |

| B1         | No Connect (NC)                                                                             | F2       | ERXDV/AERXDV/ECRSDV/AECRSDV//SCL4/SDO2/U3TX/PMA3/CN10/RG8    |

| B2         | AERXERR/RG15                                                                                | F3       | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| B3         | PMD2/RE2                                                                                    | F4       | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| B4         | PMD1/RE1                                                                                    | F5       | Vss                                                          |

| B5         | TRD3/RA7                                                                                    | F6       | No Connect (NC)                                              |

| B6         | ETXD1/PMD11/RF0                                                                             | F7       | No Connect (NC)                                              |

| B7         | VCAP                                                                                        | F8       | VDD                                                          |

| B8         | PMRD/CN14/RD5                                                                               | F9       | OSC1/CLKI/RC12                                               |

| B9         | OC4/RD3                                                                                     | F10      | Vss                                                          |

| B10        | Vss                                                                                         | F11      | OSC2/CLKO/RC15                                               |

| B11        | SOSCO/T1CK/CN0/RC14                                                                         | G1       | AERXD0/INT1/RE8                                              |

| C1         | PMD6/RE6                                                                                    | G2       | AERXD1/INT2/RE9                                              |

| C2         | VDD                                                                                         | G3       | TMS/RA0                                                      |

| C3<br>C4   | TRD1/RG12<br>TRD2/RG14                                                                      | G4<br>G5 | No Connect (NC)<br>VDD                                       |

| C4         | TRCLK/RA6                                                                                   | G5<br>G6 | Vss                                                          |

|            | No Connect (NC)                                                                             | G0<br>G7 | Vss                                                          |

| C0<br>C7   | ETXCLK/PMD15/CN16/RD7                                                                       | G7<br>G8 | No Connect (NC)                                              |

| C8         | OC5/PMWR/CN13/RD4                                                                           | G9       | TDO/RA5                                                      |

| C9         | VDD                                                                                         | G10      | SDA2/RA3                                                     |

| C10        | SOSCI/CN1/RC13                                                                              | G11      | TDI/RA4                                                      |

| C11        | EMDC/AEMDC/IC4/PMCS1/PMA14/RD11                                                             | H1       | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| D1         | T2CK/RC1                                                                                    | H2       | AN4/C1IN-/CN6/RB4                                            |

| D2         | PMD7/RE7                                                                                    | H3       | Vss                                                          |

| D3         | PMD5/RE5                                                                                    | H4       | VDD                                                          |

| D4         | Vss                                                                                         | H5       | No Connect (NC)                                              |

| D5         | Vss                                                                                         | H6       | VDD                                                          |

| D6         | No Connect (NC)                                                                             | H7       | No Connect (NC)                                              |

| D7         | ETXEN/PMD14/CN15/RD6                                                                        | H8       | VBUS                                                         |

| D8         | ETXD3/PMD13/CN19/RD13                                                                       | H9       | VUSB3V3                                                      |

| D9         | SDO1/OC1/INT0/RD0                                                                           | H10      | D+/RG2                                                       |

| D10        | No Connect (NC)                                                                             | H11      | SCL2/RA2                                                     |

| D11        | SCK1/IC3/PMCS2/PMA15/RD10                                                                   | J1       | AN3/C2IN+/CN5/RB3                                            |

| E1<br>Note | T5CK/SDI1/RC4<br>1: Shaded pins are 5V tolerant.                                            | J2       | AN2/C2IN-/CN4/RB2                                            |

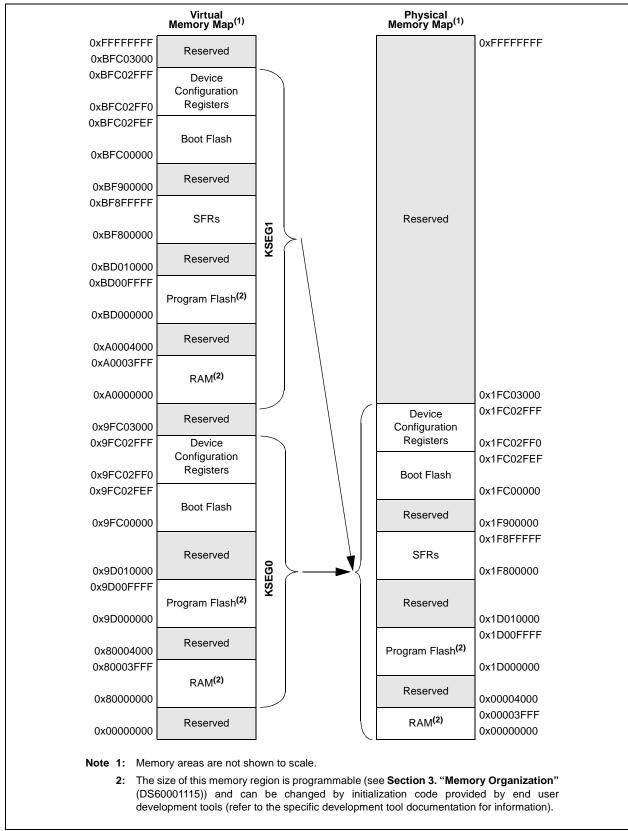

# FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 |                   | _                 |                   |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | —                 | _                 | _                 | —                 | _                 |                   | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | _                 | —                 | —                 | _                 | DCSZ             | <u>Z</u> <1:0>   |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   | _                 | PREFE             | N<1:0>            |                   | F                 | PFMWS<2:0>       | >                |

#### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 Unimplemented: Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- Changing these bits causes all lines to be reinitialized to the "invalid" state.

- 11 = Enable data caching with a size of 4 lines

- 10 = Enable data caching with a size of 2 lines

- 01 = Enable data caching with a size of 1 line

- 00 = Disable data caching

- bit 7-6 Unimplemented: Write '0'; ignore read

- bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch only for non-cacheable regions

- 01 = Enable predictive prefetch only for cacheable regions

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

# PIC32MX5XX/6XX/7XX

#### 12.2 Control Registers

# TABLE 12-1: PORTA REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX695F512L, PIC32MX764F128L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX795F512L, PIC32MX764F128L, PIC32MX775F512L, PIC32MX775F512L, PIC32MX795F512L, PIC32MX795F512L, PIC32MX775F512L, PIC32MX795F512L, PIC32MX79F5F512L, PIC32MX79FF512L, PIC32MX79FF512MX79FF512L, PIC32MX79FF512MX79FF512MX79FF512L, PIC32

| ess                        |                                 |           |         |         |       |       |       |         |        | Bi   | ts     |        |        |        |        |        |        |        | 6          |

|----------------------------|---------------------------------|-----------|---------|---------|-------|-------|-------|---------|--------|------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13 | 28/12 | 27/11 | 26/10   | 25/9   | 24/8 | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 6000                       | TRISA                           | 31:16     |         | —       |       | _     | —     | —       | _      | _    |        | —      |        | _      |        | —      | —      | —      | 0000       |

| 6000                       | IRISA                           | 15:0      | TRISA15 | TRISA14 |       | _     |       | TRISA10 | TRISA9 | _    | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | C6FF       |

| 6010                       | PORTA                           | 31:16     |         | _       |       | _     |       | _       | _      | _    |        | _      |        | _      |        | _      | _      | _      | 0000       |

| 0010                       | FURIA                           | 15:0      | RA15    | RA14    |       | -     |       | RA10    | RA9    | _    | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx       |

| 6020                       | LATA                            | 31:16     | -       | _       | -     | —     | _     | _       |        |      | -      | —      | -      |        | -      | —      | —      | —      | 0000       |

| 0020                       | LAIA                            | 15:0      | LATA15  | LATA14  | -     | —     | _     | LATA10  | LATA9  |      | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx       |

| 6030                       | ODCA                            | 31:16     |         | _       |       | -     |       | —       | _      | _    |        | _      |        | _      | _      | _      | -      | -      | 0000       |

| 6030                       | UDCA                            | 15:0      | ODCA15  | ODCA14  | _     | _     | —     | ODCA10  | ODCA9  | _    | ODCA7  | ODCA6  | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 12-2:PORTB REGISTER MAP

|                           |                                 |           | -       |         |         |         |         |         |        |        |        |        |        |        |        |        |        |        |            |

|---------------------------|---------------------------------|-----------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| ess                       |                                 |           |         |         |         |         |         |         |        | Bi     | its    |        |        |        |        |        |        |        |            |

| Virtual Addre<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11   | 26/10   | 25/9   | 24/8   | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 00.40                     | TRIOR                           | 31:16     |         |         | _       | _       | _       | _       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6040                      | TRISB                           | 15:0      | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF       |

| COEO                      | PORTB                           | 31:16     | _       | _       | _       | _       | _       | -       | _      | _      | _      | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 6050                      | PURID                           | 15:0      | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx       |

| 6060                      | LATB                            | 31:16     | _       | —       | _       | _       | _       | _       | _      | _      | _      | _      | —      | _      | _      | _      | _      | _      | 0000       |

| 6060                      | LAID                            | 15:0      | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx       |

| 6070                      | ODCB                            | 31:16     | _       |         | _       | _       | _       | —       | —      | _      | _      | —      | —      | _      | —      | _      | —      | —      | 0000       |

| 6070                      | ODCB                            | 15:0      | ODCB15  | ODCB14  | ODCB13  | ODCB12  | ODCB11  | ODCB10  | ODCB9  | ODCB8  | ODCB7  | ODCB6  | ODCB5  | ODCB4  | ODCB3  | ODCB2  | ODCB1  | ODCB0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-9: PORTF REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX775F512H, PIC32MX795F512H, DEVICES

| ess                         |                                 | e         |       |       |       |       |       |       |      | Bi   | its  |      |        |        |        |      |        |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------|--------|--------|------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2 | 17/1   | 16/0   | All Resets |

| 6140                        | TRISF                           | 31:16     | _     | —     | _     | —     | -     | —     | —    | —    | _    | —    | _      | —      | —      | _    | -      | —      | 0000       |

| 6140                        | IRIOF                           | 15:0      |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | TRISF5 | TRISF4 | TRISF3 | _    | TRISF1 | TRISF0 | 003B       |

| 6150                        | PORTF                           | 31:16     | _     | _     |       | _     |       | _     |      |      |      |      | -      | _      | _      | _    |        |        | 0000       |

| 6150                        | PURIF                           | 15:0      |       | -     | -     | —     | —     | —     | -    | -    | -    | -    | RF5    | RF4    | RF3    |      | RF1    | RF0    | xxxx       |

| 6160                        | LATF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 6160                        | LAIF                            | 15:0      | -     | _     | —     | _     | _     | _     | _    | _    | _    | _    | LATF5  | LATF4  | LATF3  | —    | LATF1  | LATF0  | xxxx       |

| 6170                        | ODCF                            | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | -      | _      | _      | _    | _      | _      | 0000       |

| 0170                        | ODCF                            | 15:0      | _     | _     | _     |       | -     |       |      |      |      |      | ODCF5  | ODCF4  | ODCF3  |      | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# TABLE 12-10: PORTF REGISTER MAP PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX775F512L, PIC32MX7

| ess                         |                                 | â         |       |       |         |         |       |       |      | Bi     | ts   |      |        |        |        |        |        |        | - y       |

|-----------------------------|---------------------------------|-----------|-------|-------|---------|---------|-------|-------|------|--------|------|------|--------|--------|--------|--------|--------|--------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8   | 23/7 | 22/6 | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Reset |

|                             | TDIOF                           | 31:16     | _     | _     | _       | _       | _     | _     | _    | _      | _    | _    | _      | _      | _      | _      | _      | _      | 0000      |

| 6140                        | TRISF                           | 15:0      | _     | _     | TRISF13 | TRISF12 | _     | _     | _    | TRISF8 | _    | _    | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 313F      |

| 6150                        | PORTF                           | 31:16     | -     | _     | _       | _       | _     | -     | _    | _      | -    |      | -      |        | _      |        | _      | _      | 0000      |

| 0150                        | FUNIF                           | 15:0      | -     | —     | RF13    | RF12    | _     |       | _    | RF8    |      |      | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx      |

| 6160                        | LATF                            | 31:16     | —     | —     | _       |         | —     | _     | _    |        | -    | _    | _      | _      | _      | _      | —      | —      | 0000      |

| 0100                        | LAIF                            | 15:0      |       | —     | LATF13  | LATF12  |       | -     |      | LATF8  |      | -    | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx      |

| 6170                        | ODCF                            | 31:16     | —     | _     | _       | —       | _     |       | _    |        |      |      | _      |        | —      |        | -      | -      | 0000      |

| 0170                        | ODCF                            | 15:0      | _     | _     | ODCF13  | ODCF12  | _     | -     | —    | ODCF8  | _    | -    | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

|              |                         | -                    | -                  |                         |                   |                   |                      |                  |

|--------------|-------------------------|----------------------|--------------------|-------------------------|-------------------|-------------------|----------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

| 24.24        | U-0                     | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 31:24        | —                       | —                    | —                  | —                       | _                 | —                 | _                    | —                |

| 23:16        | U-0                     | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0                  | U-0              |

| 23.10        | —                       | —                    | —                  | —                       | _                 | —                 | _                    | —                |

| 45.0         | R/W-0                   | R/W-0                | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 15:8         | ALRMEN <sup>(1,2)</sup> | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> |                   | AMASK             | <3:0> <sup>(2)</sup> |                  |

| 7.0          | R/W-0                   | R/W-0                | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 7:0          |                         |                      |                    | ARPT<7:0                | > <sup>(2)</sup>  |                   |                      |                  |

#### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | , read as '0'      |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

- bit 14 **CHIME:** Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(3)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

#### bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read.

The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain.

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(2)</sup>

1111 = Reserved

- 1010 = Reserved

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1000 = Once a month

- 0111 = Once a week

- 0110 = Once a day

- 0101 = Every hour

- 0100 = Every 10 minutes

- 0011 = Every minute

- 0010 = Every 10 seconds

- 0001 = Every second

- 0000 = Every half-second

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0 > = 0.0 and CHIME = 0.

- **2:** This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is only reset on a Power-on Reset (POR).

# REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER (CONTINUED)

bit 13 **SIDLE:** CAN Stop in Idle bit 1 = CAN Stops operation when system enters Idle mode 0 = CAN continues operation when system enters Idle mode

# bit 12 Unimplemented: Read as '0'

- bit 11 CANBUSY: CAN Module is Busy bit

- 1 = The CAN module is active

- 0 = The CAN module is completely disabled

- bit 10-5 Unimplemented: Read as '0'

#### bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID)

- 10010 = Compare up to data byte 2 bit 6 with EID17 (CiRXFn<17>)

- •

- •

- •

00001 = Compare up to data byte 0 bit 7 with EID0 (CiRXFn<0>) 00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

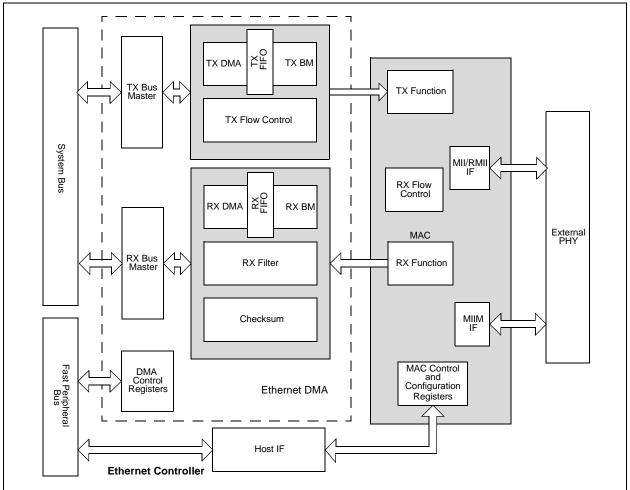

# 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

# FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

# REGISTER 25-14: ETHIRQ: ETHERNET CONTROLLER INTERRUPT REQUEST REGISTER

| bit 6 | PKTPEND: Packet Pending Interrupt bit                                                                                                                                                                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | 1 = RX packet pending in memory                                                                                                                                                                                                                     |

|       | 0 = RX packet is not pending in memory                                                                                                                                                                                                              |

|       | This bit is set when the BUFCNT counter has a value other than '0'. It is cleared by either a Reset or by writing the BUFCDEC bit to decrement the BUFCNT counter. Writing a '0' or a '1' has no effect.                                            |

| bit 5 | RXACT: Receive Activity Interrupt bit                                                                                                                                                                                                               |

|       | <ul><li>1 = RX packet data was successfully received</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                     |

|       | This bit is set whenever RX packet data is stored in the RXBM FIFO. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                          |

| bit 3 | TXDONE: Transmit Done Interrupt bit                                                                                                                                                                                                                 |

|       | <ul><li>1 = TX packet was successfully sent</li><li>0 = No interrupt pending</li></ul>                                                                                                                                                              |

|       | This bit is set when the currently transmitted TX packet completes transmission, and the Transmit Status Vector is loaded into the first descriptor used for the packet. It is cleared by either a Reset or CPU write of a '1' to the CLR register. |

| bit 2 | TXABORT: Transmit Abort Condition Interrupt bit                                                                                                                                                                                                     |

|       | <ul><li>1 = TX abort condition occurred on the last TX packet</li><li>0 = No interrupt pending</li></ul>                                                                                                                                            |

|       | This bit is set when the MAC aborts the transmission of a TX packet for one of the following reasons:                                                                                                                                               |

|       | Jumbo TX packet abort                                                                                                                                                                                                                               |

|       | Underrun abort                                                                                                                                                                                                                                      |

|       | Excessive defer abort                                                                                                                                                                                                                               |

|       | Late collision abort                                                                                                                                                                                                                                |

|       | Excessive collisions abort                                                                                                                                                                                                                          |

|       | This bit is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                                                                                    |

| bit 1 | RXBUFNA: Receive Buffer Not Available Interrupt bit                                                                                                                                                                                                 |

|       | <ul> <li>1 = RX Buffer Descriptor Not Available condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                 |

|       | This bit is set by a RX Buffer Descriptor Overrun condition. It is cleared by either a Reset or a CPU write of a '1' to the CLR register.                                                                                                           |

| bit 0 | RXOVFLW: Receive FIFO Over Flow Error bit                                                                                                                                                                                                           |

|       | <ul> <li>1 = RX FIFO Overflow Error condition has occurred</li> <li>0 = No interrupt pending</li> </ul>                                                                                                                                             |

|       | RXOVFLW is set by the RXBM Logic for an RX FIFO Overflow condition. It is cleared by either a Reset or CPU write of a '1' to the CLR register.                                                                                                      |

|       |                                                                                                                                                                                                                                                     |

**Note:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

#### REGISTER 25-20: ETHFRMRXOK: ETHERNET CONTROLLER FRAMES RECEIVED OK STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FRMRXOKCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FRMRXOKCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |

### Legend:

| 3                 |                  |                        |                    |  |

|-------------------|------------------|------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 FRMRXOKCNT<15:0>: Frames Received OK Count bits

Increment count for frames received successfully by the RX Filter. This count will not be incremented if there is a Frame Check Sequence (FCS) or Alignment error.

Note 1: This register is only used for RX operations.

- 2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

- **3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

# **30.0 INSTRUCTION SET**

The PIC32MX5XX/6XX/7XX family instruction set complies with the MIPS32 Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- Core Extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

# TABLE 32-14: VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |         |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |         |                    |       |                                                                 |

|--------------------|---------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|-------|-----------------------------------------------------------------|

| Param.<br>No.      | Symbol  | Characteristics                                              | Min.                                                                                                                                                                                                                                                                              | Typical | Max.               | Units | Comments                                                        |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                                                 | —       | 10                 | μs    | See Note 1                                                      |

| D313               | DACREFH | CVREF Input Voltage<br>Reference Range                       | AVss                                                                                                                                                                                                                                                                              | _       | AVdd               | V     | CVRSRC with CVRSS = 0                                           |

|                    |         |                                                              | VREF-                                                                                                                                                                                                                                                                             | _       | VREF+              | V     | CVRSRC with CVRSS = 1                                           |

| D314               | DVref   | CVREF Programmable<br>Output Range                           | 0                                                                                                                                                                                                                                                                                 | —       | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                 |

|                    |         |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                 | —       | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/32<br>step size |

| D315               | DACRES  | Resolution                                                   | —                                                                                                                                                                                                                                                                                 | —       | DACREFH/<br>24     |       | CVRCON <cvrr> = 1</cvrr>                                        |

|                    |         |                                                              | —                                                                                                                                                                                                                                                                                 | _       | DACREFH/<br>32     |       | CVRCON <cvrr> = 0</cvrr>                                        |

| D316 DACAC         |         | Absolute Accuracy <sup>(2)</sup>                             | —                                                                                                                                                                                                                                                                                 |         | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                         |

|                    |         |                                                              | —                                                                                                                                                                                                                                                                                 |         | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                         |

**Note 1:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

2: These parameters are characterized but not tested.

#### TABLE 32-15: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |         |      |       |                                                 |

|--------------------|--------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|-------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                                                                                                                                                                                                                                                  | Typical | Max. | Units | Comments                                        |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                                                                                                                                                                                                                                                     | 10      | —    | μF    | Capacitor must be low series resistance (1 ohm) |

| D322               | TPWRT  | Power-up Timer Period           | _                                                                                                                                                                                                                                                                                     | 64      | _    | ms    | —                                               |

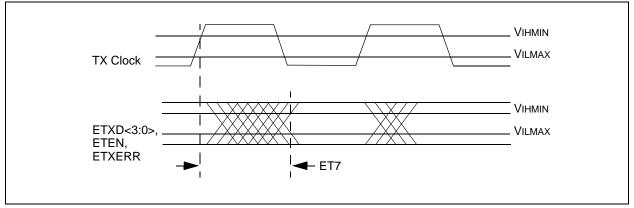

### FIGURE 32-21: TRANSMIT SIGNAL TIMING RELATIONSHIPS AT THE MII

# PIC32MX5XX/6XX/7XX

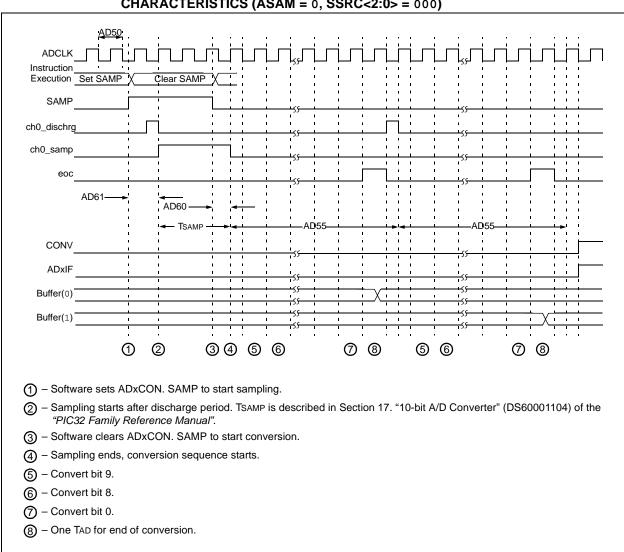

# FIGURE 32-23: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

#### Section Name Update Description 4.0 "Memory Organization" Updated all register tables to include the Virtual Address and All Resets columns. Updated the title of Figure 4-4 to include the PIC32MX575F256L device. Updated the title of Figure 4-6 to include the PIC32MX695F512L and PIC32MX695F512H devices. Also changed PIC32MX795F512L to PIC32MX795F512H. Updated the title of Table 4-3 to include the PIC32MX695F512H device. Updated the title of Table 4-5 to include the PIC32MX575F5256L device. Updated the title of Table 4-6 to include the PIC32MX695F512L device. Reversed the order of Table 4-11 and Table 4-12. Reversed the order of Table 4-14 and Table 4-15. Updated the title of Table 4-15 to include the PIC32MX575F256L and PIC32MX695F512L devices. Updated the title of Table 4-45 to include the PIC32MX575F256L device. Updated the title of Table 4-47 to include the PIC32MX695F512H and PIC32MX695F512L devices. 1.0 "I/O Ports" Updated the second paragraph of **1.1.2** "Digital Inputs" and removed Table 12-1. 22.0 "10-bit Analog-to-Digital Updated the ADC Conversion Clock Period Block Diagram (see Figure 22-2). Converter (ADC)" 1.0 "Special Features" Removed references to the ENVREG pin in 1.3 "On-Chip Voltage Regulator". Updated the first sentence of 1.3.1 "On-Chip Regulator and POR" and 1.3.2 "On-Chip Regulator and BOR". Updated the Connections for the On-Chip Regulator (see Figure 1-2). 1.0 "Electrical Characteristics" Updated the Absolute Maximum Ratings and added Note 3. Added Thermal Packaging Characteristics for the 121-pin XBGA package (see Table 1-3). Updated the Operating Current (IDD) DC Characteristics (see Table 1-5). Updated the Idle Current (IIDLE) DC Characteristics (see Table 1-6). Updated the Power-Down Current (IPD) DC Characteristics (see Table 1-7). Removed Note 1 from the Program Flash Memory Wait State Characteristics (see Table 1-12). Updated the SPIx Module Slave Mode (CKE = 1) Timing Characteristics, changing SP52 to SP35 between the MSb and Bit 14 on SDOx (see Figure 1-13). 1.0 "Packaging Information" Added the 121-pin XBGA package marking information and package details. "Product Identification System" Added the definition for BG (121-lead 10x10x1.1 mm, XBGA). Added the definition for Speed.

#### TABLE B-1: MAJOR SECTION UPDATES (CONTINUED)

| TABLE B-4: | SECTION UPDATES  | (CONTINUED) |

|------------|------------------|-------------|

|            | OLOHON OF BATTLO |             |

| Section Name              | Update Description                                                                                                 |

|---------------------------|--------------------------------------------------------------------------------------------------------------------|

| 4.0 "Memory Organization" | • Table 4-13:                                                                                                      |

| (Continued)               | - Changed register U4RG to U1BRG                                                                                   |

|                           | - Changed register U5RG to U3BRG                                                                                   |

|                           | - Changed register U6RG to U2BRG                                                                                   |

|                           | • Table 4-14:                                                                                                      |

|                           | <ul> <li>Updated the All Resets values for the following registers: SPI3STAT,<br/>SPI2STAT and SPI4STAT</li> </ul> |

|                           | • Table 4-15: Updated the All Resets values for the SPI1STAT register                                              |

|                           | Table 4-17: Added note 2                                                                                           |

|                           | Table 4-19: Added note 2                                                                                           |

|                           | <ul> <li>Table 4-20: Updated the All Resets values for the CM1CON and<br/>CM2CON registers</li> </ul>              |

|                           | • Table 4-21:                                                                                                      |

|                           | <ul> <li>Updated the All Resets values as 0000 for the CVRCON register</li> <li>Updated note 2</li> </ul>          |

|                           | • Table 4-38: Updated the All Resets values for the PMSTAT register                                                |

|                           | <ul> <li>Table 4-40: Updated the All Resets values for the CHECON and<br/>CHETAG registers</li> </ul>              |

|                           | <ul> <li>Table 4-42: Updated the bit value of bit 29/13 as '—' for the DEVCFG3<br/>register</li> </ul>             |

|                           | • Table 4-44:                                                                                                      |

|                           | - Updated the note references in the entire table                                                                  |

|                           | - Changed existing note 1 to note 4                                                                                |

|                           | - Added notes 1, 2 and 3                                                                                           |

|                           | <ul> <li>Changed bits 23/7 in U1PWRC to UACTPND</li> </ul>                                                         |

|                           | <ul> <li>Changed register U1DDR to U1ADDR</li> </ul>                                                               |

|                           | <ul> <li>Changed register U4DTP1 to U1BDTP1</li> </ul>                                                             |

|                           | <ul> <li>Changed register U4DTP2 to U1BDTP2</li> </ul>                                                             |

|                           | <ul> <li>Changed register U4DTP3 to U1BDTP3</li> </ul>                                                             |

|                           | • Table 4-45:                                                                                                      |

|                           | <ul> <li>Updated the All Resets values for the C1CON and C1VEC registers</li> </ul>                                |

|                           | <ul> <li>Changed bits 30/14 in C1CON to FRZ</li> </ul>                                                             |

|                           | <ul> <li>Changed bits 27/11 in C1CON to CANBUSY</li> </ul>                                                         |

|                           | <ul> <li>Changed bits 22/6-16/0 in C1VEC to ICODE&lt;6:0&gt;</li> </ul>                                            |

|                           | <ul> <li>Changed bits 22/6-16/0 in C1TREC to RERRCNT&lt;7:0&gt;</li> </ul>                                         |

|                           | - Changed bits 31/15-24/8 in C1TREC to TERRCNT<7:0>                                                                |

|                           | • Table 4-46:                                                                                                      |

|                           | - Updated the All Resets values for the C2CON and C2VEC registers                                                  |

|                           | - Changed bits 30/14 in C1CON to FRZ                                                                               |

|                           | - Changed bits 27/11 in C1CON to CANBUSY                                                                           |

|                           | - Changed bits 22/6-16/0 in C1VEC register to ICODE<6:0>                                                           |

|                           | - Changed bits 22/6-16/0 in C1TREC register to RERRCNT<7:0>                                                        |

|                           | <ul> <li>Changed bits 31/15-24/8 in C1TREC to TERRCNT&lt;7:0&gt;</li> </ul>                                        |