Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 80MHz                                                                            |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512l-80v-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1- | <u>I: PINOU</u>                               | T I/O DES       | CRIPTION            | NS (CONT        | INUED | )                    |                                                   |  |  |  |

|----------|-----------------------------------------------|-----------------|---------------------|-----------------|-------|----------------------|---------------------------------------------------|--|--|--|

|          |                                               | Pin Nur         | nber <sup>(1)</sup> |                 | Pin   | Buffer               |                                                   |  |  |  |

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP | 121-Pin<br>TFBGA    | 124-pin<br>VTLA | Туре  | Туре                 | Description                                       |  |  |  |

| SDI1     | —                                             | 9               | E1                  | B5              | I     | ST                   | SPI1 data in                                      |  |  |  |

| SDO1     | —                                             | 72              | D9                  | B39             | 0     | _                    | SPI1 data out                                     |  |  |  |

| SS1      | _                                             | 69              | E10                 | A45             | I/O   | ST                   | SPI1 slave synchronization or frame pulse I/O     |  |  |  |

| SCK3     | 49                                            | 48              | K9                  | A31             | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI3 |  |  |  |

| SDI3     | 50                                            | 52              | K11                 | A36             | I     | ST                   | SPI3 data in                                      |  |  |  |

| SDO3     | 51                                            | 53              | J10                 | B29             | 0     |                      | SPI3 data out                                     |  |  |  |

| SS3      | 43                                            | 47              | L9                  | B26             | I/O   | ST                   | SPI3 slave synchronization or frame pulse I/O     |  |  |  |

| SCK2     | 4                                             | 10              | E3                  | A7              | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI2 |  |  |  |

| SDI2     | 5                                             | 11              | F4                  | B6              | I     | ST                   | SPI2 data in                                      |  |  |  |

| SDO2     | 6                                             | 12              | F2                  | A8              | 0     |                      | SPI2 data out                                     |  |  |  |

| SS2      | 8                                             | 14              | F3                  | A9              | I/O   | ST                   | SPI2 slave synchronization or frame pulse I/O     |  |  |  |

| SCK4     | 29                                            | 39              | L6                  | B22             | I/O   | ST                   | Synchronous serial clock input/output<br>for SPI4 |  |  |  |

| SDI4     | 31                                            | 49              | L10                 | B27             | I     | ST                   | SPI4 data in                                      |  |  |  |

| SDO4     | 32                                            | 50              | L11                 | A32             | 0     |                      | SPI4 data out                                     |  |  |  |

| SS4      | 21                                            | 40              | K6                  | A27             | I/O   | ST                   | SPI4 slave synchronization or frame pulse I/O     |  |  |  |

| SCL1     | 44                                            | 66              | E11                 | B36             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C1 |  |  |  |

| SDA1     | 43                                            | 67              | E8                  | A44             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C1  |  |  |  |

| SCL3     | 51                                            | 53              | J10                 | B29             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C3 |  |  |  |

| SDA3     | 50                                            | 52              | K11                 | A36             | I/O   | ST                   | Synchronous serial data input/output for I2C3     |  |  |  |

| SCL2     | _                                             | 58              | H11                 | A39             | I/O   | ST                   | Synchronous serial clock input/output<br>for I2C2 |  |  |  |

| SDA2     | _                                             | 59              | G10                 | B32             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C2  |  |  |  |

| SCL4     | 6                                             | 12              | F2                  | A8              | I/O   | ST                   | Synchronous serial clock input/outpu<br>for I2C4  |  |  |  |

| SDA4     | 5                                             | 11              | F4                  | B6              | I/O   | ST                   | Synchronous serial data input/output<br>for I2C4  |  |  |  |

| SCL5     | 32                                            | 50              | L11                 | A32             | I/O   | ST                   | Synchronous serial clock input/outpu<br>for I2C5  |  |  |  |

| SDA5     | 31                                            | 49              | L10                 | B27             | I/O   | ST                   | Synchronous serial data input/output<br>for I2C5  |  |  |  |

| -        | CMOS = CMO<br>ST = Schmitt 1<br>TTL = TTL inp | Frigger input   |                     |                 |       | nalog = A<br>= Outpu | Analog input P = Power<br>t I = Input             |  |  |  |

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

NOTES:

#### 7.1 **Control Registers**

#### **TABLE 7-2:** INTERRUPT REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H AND PIC32MX575F512H DEVICES

|                             | 1                               |               | CJZIWIA       |         |         |                               |                               |                             |            |         |                       |                       |                       |                       |               |        |        |               | 1             |

|-----------------------------|---------------------------------|---------------|---------------|---------|---------|-------------------------------|-------------------------------|-----------------------------|------------|---------|-----------------------|-----------------------|-----------------------|-----------------------|---------------|--------|--------|---------------|---------------|

| ess                         |                                 |               |               |         |         |                               |                               |                             |            | Bits    |                       |                       |                       |                       |               |        |        |               |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14   | 29/13   | 28/12                         | 27/11                         | 26/10                       | 25/9       | 24/8    | 23/7                  | 22/6                  | 21/5                  | 20/4                  | 19/3          | 18/2   | 17/1   | 16/0          | All<br>Resets |

| 4000                        | INITOON                         | 31:16         | —             | _       | _       | _                             | _                             | —                           | -          | _       | _                     | _                     |                       | _                     | —             | _      | _      | SS0           | 0000          |

| 1000                        | INTCON                          | 15:0          | —             | —       | _       | MVEC                          | —                             |                             | TPC<2:0>   |         | —                     | —                     | _                     | INT4EP                | INT3EP        | INT2EP | INT1EP | INT0EP        | 0000          |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | _             | _       | _       | —                             | _                             | _                           | —          | —       | —                     | _                     |                       |                       | —             |        | _      | —             | 0000          |

| 1010                        | INTSTAT                         | 15:0          | —             | —       | —       | —                             | —                             |                             | SRIPL<2:0> |         | —                     | —                     |                       |                       | VEC<5:0       | )>     |        |               | 0000          |

| 1020                        | IPTMR                           | 31:16<br>15:0 |               |         |         |                               |                               |                             |            | IPTMR<3 | 1:0>                  |                       |                       |                       |               |        |        |               | 0000          |

| 1030                        | IFS0                            |               | I2C1MIF       | I2C1SIF | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF | _          | _       | _                     | OC5IF                 | IC5IF                 | T5IF                  | INT4IF        | OC4IF  | IC4IF  | T4IF          | 0000          |

|                             |                                 | 15:0          | INT3IF        | OC3IF   | IC3IF   | T3IF                          | INT2IF                        | OC2IF                       | IC2IF      | T2IF    | INT1IF                | OC1IF                 | IC1IF                 | T1IF                  | INT0IF        | CS1IF  | CS0IF  | CTIF          | 0000          |

|                             |                                 | 31:16         | IC3EIF        | IC2EIF  | IC1EIF  | _                             | _                             | CAN1IF                      | USBIF      | FCEIF   | DMA7IF <sup>(2)</sup> | DMA6IF <sup>(2)</sup> | DMA5IF <sup>(2)</sup> | DMA4IF <sup>(2)</sup> | DMA3IF        | DMA2IF | DMA1IF | DMA0IF        | 0000          |

| 1040                        | IFS1                            |               |               |         |         |                               |                               | U2TXIF                      | U2RXIF     | U2EIF   | <b>U3TXIF</b>         | <b>U3RXIF</b>         | <b>U3EIF</b>          |                       |               |        |        |               |               |

| 1040                        | 11 31                           | 15:0          | RTCCIF        | FSCMIF  | —       | —                             | —                             | SPI4TXIF                    | SPI4RXIF   | SPI4EIF | SPI2TXIF              | SPI2RXIF              | SPI2EIF               | CMP2IF                | CMP1IF        | PMPIF  | AD1IF  | CNIF          | 0000          |

|                             |                                 |               |               |         |         |                               |                               | I2C5MIF                     | I2C5SIF    | I2C5BIF | I2C4MIF               | I2C4SIF               | I2C4BIF               |                       |               |        |        |               |               |

| 1050                        | IFS2                            | 31:16         | _             | —       | —       | —                             |                               | —                           | _          | —       | —                     | —                     | _                     | _                     |               |        | —      | —             | 0000          |

|                             |                                 | 15:0          | —             | —       | —       | —                             | U5TXIF                        | U5RXIF                      | U5EIF      | U6TXIF  | U6RXIF                | U6EIF                 | U4TXIF                | U4RXIF                | U4EIF         | PMPEIF | IC5EIF | IC4EIF        | 0000          |

| 1060                        | IEC0                            | 31:16         | I2C1MIE       | I2C1SIE | I2C1BIE | U1TXIE<br>SPI3TXIE            | U1RXIE<br>SPI3RXIE            | U1EIE<br>SPI3EIE            | _          | _       | _                     | OC5IE                 | IC5IE                 | T5IE                  | INT4IE        | OC4IE  | IC4IE  | T4IE          | 0000          |

| 1000                        | ILC0                            |               |               |         |         | I2C3MIE                       | I2C3SIE                       | I2C3BIE                     |            |         |                       |                       |                       |                       |               |        |        |               |               |

|                             |                                 | 15:0          | INT3IE        | OC3IE   | IC3IE   | T3IE                          | INT2IE                        | OC2IE                       | IC2IE      | T2IE    | INT1IE                | OC1IE                 | IC1IE                 | T1IE                  | INT0IE        | CS1IE  | CS0IE  | CTIE          | 0000          |

|                             |                                 | 31:16         | <b>IC3EIE</b> | IC2EIE  | IC1EIE  | —                             | —                             | CAN1IE                      | USBIE      | FCEIE   | DMA7IE <sup>(2)</sup> | DMA6IE <sup>(2)</sup> | DMA5IE <sup>(2)</sup> | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b> | DMA2IE | DMA1IE | <b>DMA0IE</b> | 0000          |

| 1070                        | IEC1                            |               |               |         |         |                               |                               | U2TXIE                      | U2RXIE     | U2EIE   | <b>U3TXIE</b>         | U3RXIE                | <b>U3EIE</b>          |                       |               |        |        |               |               |

| 1070                        | 1201                            | 15:0          | RTCCIE        | FSCMIE  | —       | —                             | —                             | SPI4TXIE                    | SPI4RXIE   | SPI4EIE | SPI2TXIE              | SPI2RXIE              | SPI2EIE               | CMP2IE                | CMP1IE        | PMPIE  | AD1IE  | CNIE          | 0000          |

|                             |                                 |               |               |         |         |                               |                               | I2C5MIE                     | I2C5SIE    | I2C5BIE | I2C4MIE               | I2C4SIE               | I2C4BIE               |                       |               |        |        |               |               |

| 1080                        | IEC2                            | 31:16         | —             | —       | —       | _                             | —                             | —                           | —          | —       | —                     | —                     | _                     | —                     | —             | —      | —      | —             | 0000          |

|                             |                                 | 15:0          | —             | —       | —       | —                             | U5TXIE                        | U5RXIE                      | U5EIE      | U6TXIE  | U6RXIE                | U6EIE                 | U4TXIE                | U4RXIE                |               | PMPEIE | IC5EIE | IC4EIE        | 0000          |

| 1090                        | IPC0                            | 31:16         | —             | —       | —       |                               | INT0IP<2:0>                   |                             | INTOIS     |         | —                     | —                     | _                     |                       | S1IP<2:0>     |        | CS1IS  |               | 0000          |

|                             |                                 | 15:0          | —             | —       | —       |                               | CS0IP<2:0><br>s '0'. Reset v  |                             | CS0IS      |         | —                     | —                     | —                     | C                     | CTIP<2:0>     |        | CTIS   | <1:0>         | 0000          |

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET Note 1: and INV Registers" for more information.

These bits are not available on PIC32MX534/564/664/764 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                 | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   | —                 | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | —                 | RDWR              | [                 | DMACH<2:0>       | •                |

### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

# Legend:

| 0                 |                  |                      |                    |  |

|-------------------|------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3 RDWR: Read/Write Status bit

1 = Last DMA bus access was a read

0 = Last DMA bus access was a write

# bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

# REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        |                   |                   |                   | DMAADDR           | R<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | 7:0 DMAADDR<7:0>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

# bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|----------------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0                        | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 |                            | _                 |                   | _                    | _                 | _                | —                |  |  |  |  |

| 22.16        | R/W-1             | R/W-1                      | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        |                   | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                      |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-1             | R/W-1                      | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 15:8         |                   |                            |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |

| 7:0          | S-0               | S-0                        | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |  |

| 7.0          | CFORCE            | CABORT                     | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | —                |  |  |  |  |

# REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                                                                                  |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                                                                                             |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag<br>00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                                                                                  |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                                                                                        |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | •                                                                                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer                                                                   |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                                                                                              |

|           | <ul> <li>1 = A DMA transfer is forced to begin when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                           |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                                                                                               |

|           | <ul> <li>1 = A DMA transfer is aborted when this bit is written to a '1'</li> <li>0 = This bit always reads '0'</li> </ul>                                                   |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                                                                                                |

|           | <ul><li>1 = Abort transfer and clear CHEN on pattern match</li><li>0 = Pattern match is disabled</li></ul>                                                                   |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs</li> <li>0 = Interrupt number CHSIRQ is ignored and does not start a transfer</li> </ul>     |

| bit 3     | AIRQEN: Channel Abort IRQ Enable bit                                                                                                                                         |

|           | <ul> <li>1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs</li> <li>0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer</li> </ul> |

| bit 2-0   | Unimplemented: Read as '0'                                                                                                                                                   |

|           |                                                                                                                                                                              |

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

# REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 5 **CHDDIF:** Channel Destination Done Interrupt Flag bit

- 1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

- 0 = No interrupt is pending

- bit 4 CHDHIF: Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

0 = No interrupt is pending

#### bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

#### bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

#### bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected (either the source or the destination address is invalid)

- 0 = No interrupt is pending

# TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                        |                                 |           |       |       |       |       |       |       |      |      | Bits |      |      |          |        |        |         |        |            |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Addres<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Kange | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 53A0                       | U1EP10                          | 31:16     | _     | _     | _     | _     | _     | —     | _    | _    |      | _    | —    | —        | -      |        | _       | _      | 0000       |

| 55A0                       | UIEFIU                          | 15:0      | —     | —     | _     | _     | _     | —     | _    | —    | —    | —    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                       | U1EP11                          | 31:16     | -     | _     | _     |       |       | _     |      |      |      | _    | _    | —        |        |        | _       |        | 0000       |

| 5560                       | UIEFII                          | 15:0      | -     | _     | _     |       |       | _     |      |      |      | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                       | U1EP12                          | 31:16     | Ι     | -     |       | -     |       | _     |      |      | _    | —    | —    | _        | -      | -      | _       | -      | 0000       |

| 5300                       | UTEPTZ                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | —    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5200                       |                                 | 31:16     |       | _     | _     | —     | _     | -     | —    | —    | _    | -    | —    | —        | —      | _      | _       | _      | 0000       |

| 53D0                       | U1EP13                          | 15:0      | Ι     | -     | _     | _     | _     | -     | _    | _    | —    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

|                            |                                 | 31:16     |       | _     | _     | _     | _     | _     | _    | _    | _    |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                       | U1EP14                          | 15:0      | _     | _     | _     | _     | _     | —     | _    | _    | _    | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                       |                                 | 31:16     | _     | _     | _     |       | -     | _     | _    | _    | -    | _    | —    | _        |        |        | —       | -      | 0000       |

| 53F0                       | U1EP15                          | 15:0      | _     | —     | —     | -     |       | —     | -    | —    |      | _    | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1:

All registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

This register does not have associated SET and INV registers. 2:

3: This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined. 4:

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 | _                 | -                 | _                 | _                 | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | _                 |                   |                   |                   |                   |                  | —                |

| 7:0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |

| 7.0          | ID                | —                 | LSTATE            |                   | SESVD             | SESEND            |                  | VBUSVD           |

# REGISTER 11-3: U10TGSTAT: USB OTG STATUS REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a "type B" cable has been inserted into the USB receptacle

- 0 = A "type A" OTG cable has been inserted into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has been stable for the previous 1 ms

- 0 = USB line state (SE0 (U1CON<6> and JSTATE (U1CON<7>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

#### TABLE 12-3: PORTC REGISTER MAP FOR PIC32MX534F064H, PIC32MX564F064H, PIC32MX564F128H, PIC32MX575F256H, PIC32MX575F512H, PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H, PIC32MX695F512H, PIC32MX764F128H, PIC32MX775F256H, PIC32MX775F512H AND PIC32MX795F512H DEVICES

| ess                         |                                 | n         | Bits    |          |            |             |             |             |            |         | ő    |      |      |      |      |      |      |      |            |

|-----------------------------|---------------------------------|-----------|---------|----------|------------|-------------|-------------|-------------|------------|---------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14    | 29/13      | 28/12       | 27/11       | 26/10       | 25/9       | 24/8    | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     | —       | _        | -          | —           | _           | -           | —          | _       | -    | -    | -    | _    | —    | _    | _    | -    | 0000       |

| 6060                        | IRISC                           | 15:0      | TRISC15 | TRISC14  | TRISC13    | TRISC12     | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | F000       |

| 6000                        | PORTC                           | 31:16     | —       | -        |            | —           | —           |             | -          |         |      | _    |      | _    | _    | -    | _    |      | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14     | RC13       | RC12        | _           | -           | —          | -       | -    | -    | -    | -    |      | -    |      | -    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14   | LATC13     | LATC12      | _           | _           | -          | —       | _    | —    | _    | _    | _    | _    | _    | _    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | _       | _        | _          | _           | _           | _           | _          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14   | ODCC13     | ODCC12      | _           | _           | —          | _       | _    | _    | _    | _    | _    | _    | _    | _    | 0000       |

| Logon                       | 4                               | - unkno   |         | Pocot: - | unimplomon | ted read as | '0' Poset v | luce are ch | we in hove | locimol |      |      |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

#### TABLE 12-4: PORTC REGISTER MAP FOR PIC32MX534F064L, PIC32MX564F064L, PIC32MX564F128L, PIC32MX575F256L, PIC32MX575F512L, PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L, PIC32MX695F512L, PIC32MX764F128L. PIC32MX775F256L. PIC32MX775F512L AND PIC32MX795F512L DEVICES

| ess                         |                                 | 0         |         | Bits    |         |         |       |       |      |      |      |      |      |        | ú      |        |        |      |            |

|-----------------------------|---------------------------------|-----------|---------|---------|---------|---------|-------|-------|------|------|------|------|------|--------|--------|--------|--------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14   | 29/13   | 28/12   | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4   | 19/3   | 18/2   | 17/1   | 16/0 | All Resets |

| 6080                        | TRISC                           | 31:16     |         | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 6060                        | TRISC                           | 15:0      | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _     | _     | _    | _    | _    | _    | _    | TRISC4 | TRISC3 | TRISC2 | TRISC1 | _    | FOOF       |

| 6000                        | PORTC                           | 31:16     | _       | —       | —       | —       | —     | —     | —    | —    | _    | —    | —    | —      | —      | —      | —      | —    | 0000       |

| 6090                        | PURIC                           | 15:0      | RC15    | RC14    | RC13    | RC12    | _     | _     | —    | —    | _    | —    | —    | RC4    | RC3    | RC2    | RC1    | —    | xxxx       |

| 60A0                        | LATC                            | 31:16     | _       | _       | _       | _       | _     | _     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 60A0                        | LAIC                            | 15:0      | LATC15  | LATC14  | LATC13  | LATC12  | _     | _     | —    | —    | _    | —    | —    | LATC4  | LATC3  | LATC2  | LATC1  | —    | xxxx       |

| 60B0                        | ODCC                            | 31:16     | —       | _       | _       | —       | _     | —     | _    | _    | _    | _    | _    | _      | _      | _      | _      | _    | 0000       |

| 00B0                        | ODCC                            | 15:0      | ODCC15  | ODCC14  | ODCC13  | ODCC12  | _     | _     | _    | _    | _    | _    | _    | ODCC4  | ODCC3  | ODCC2  | ODCC1  | _    | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information

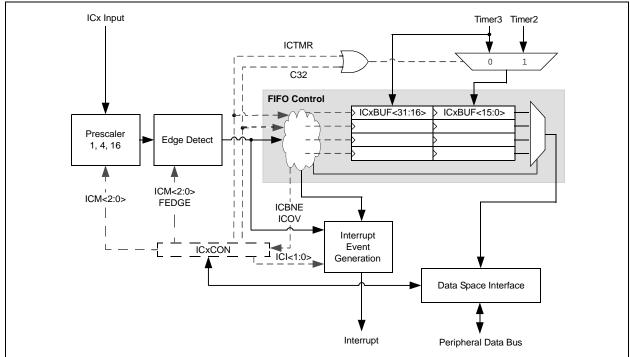

# 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122) of the "*PIC32 Family Reference Manual*", which is available from the Microchip web site (www.microchip.com/PIC32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during Sleep and Idle modes

- Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input Capture module can also be used to provide additional sources of external interrupts

# FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | —                       |                   | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | —                 | _                       | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | _                 | _                 |                   |                         | FILHIT<4:0>       |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | l                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

# REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

# REGISTER 24-10: CIFLTCONO: CAN FILTER CONTROL REGISTER 0 (CONTINUED)

| bit 15    | FLTEN1: Filter 1 Enable bit<br>1 = Filter is enabled               |

|-----------|--------------------------------------------------------------------|

|           | 0 = Filter is disabled                                             |

| bit 14-13 | MSEL1<1:0>: Filter 1 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 12-8  | FSEL1<4:0>: FIFO Selection bits                                    |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 7     | FLTEN0: Filter 0 Enable bit                                        |

|           | 1 = Filter is enabled<br>0 = Filter is disabled                    |

| bit 6-5   | MSEL0<1:0>: Filter 0 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 4-0   | FSEL0<4:0>: FIFO Selection bits                                    |

| DIL 4-0   | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1    |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

# REGISTER 24-16: CIFLTCON6: CAN FILTER CONTROL REGISTER 6 (CONTINUED)

| bit 15    | FLTEN25: Filter 25 Enable bit                                                                          |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL25<1:0>: Filter 25 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected                                                                        |

|           | 00 = Acceptance Mask 0 selected                                                                        |

| bit 12-8  | FSEL25<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           |                                                                                                        |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN24: Filter 24 Enable bit                                                                          |

|           | 1 = Filter is enabled                                                                                  |

|           | 0 = Filter is disabled                                                                                 |

| bit 6-5   | MSEL24<1:0>: Filter 24 Mask Select bits                                                                |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected                                                                        |

|           | 00 = Acceptance Mask 0 selected                                                                        |

| bit 4-0   | FSEL24<4:0>: FIFO Selection bits                                                                       |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           |                                                                                                        |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

|           |                                                                                                        |

#### REGISTER 25-21: ETHFCSERR: ETHERNET CONTROLLER FRAME CHECK SEQUENCE ERROR STATISTICS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                   | —                 |                   |                   | -                 |                   | -                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | —                 | —                 | _                 | _                 | _                 | _                 | _                |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | FCSERRCNT<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | FCSERRCNT<7:0>    |                   |                   |                   |                   |                  |                  |  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FCSERRCNT<15:0>:** FCS Error Count bits Increment count for frames received with FCS error and the frame length in bits is an integral multiple of 8 bits.

#### **Note 1:** This register is only used for RX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should be only done for debug/test purposes.

# REGISTER 25-24: EMAC1CFG2: ETHERNET CONTROLLER MAC CONFIGURATION 2 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7            | Bit<br>30/22/14/6            | Bit<br>29/21/13/5              | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>25/16/8/0 |

|--------------|------------------------------|------------------------------|--------------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                          | U-0                          | U-0                            | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                              |                              | _                              | —                 | _                 |                   |                  | —                |

| 23:16        | U-0                          | U-0                          | U-0                            | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                              |                              | _                              | —                 | _                 |                   |                  | —                |

|              | U-0                          | R/W-1                        | R/W-0                          | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                            | EXCESS<br>DFR                | BPNOBK<br>OFF                  | NOBK<br>OFF       |                   | —                 | LONGPRE          | PUREPRE          |

|              | R/W-1                        | R/W-0                        | R/W-1                          | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | AUTO<br>PAD <sup>(1,2)</sup> | VLAN<br>PAD <sup>(1,2)</sup> | PAD<br>ENABLE <sup>(1,3)</sup> | CRC<br>ENABLE     | DELAYCRC          | HUGEFRM           | LENGTHCK         | FULLDPLX         |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

bit 14 **EXCESSDER:** Excess Defer bit

1 = The MAC will defer to carrier indefinitely as per the Standard

0 = The MAC will abort when the excessive deferral limit is reached

#### bit 13 **BPNOBKOFF:** Backpressure/No Backoff bit

- 1 = The MAC after incidentally causing a collision during backpressure will immediately retransmit without backoff reducing the chance of further collisions and ensuring transmit packets get sent

- 0 = The MAC will not remove the backoff

#### bit 12 NOBKOFF: No Backoff bit

- 1 = Following a collision, the MAC will immediately retransmit rather than using the Binary Exponential Backoff algorithm as specified in the Standard

- 0 = Following a collision, the MAC will use the Binary Exponential Backoff algorithm

#### bit 11-10 Unimplemented: Read as '0'

- bit 9 LONGPRE: Long Preamble Enforcement bit

- 1 = The MAC only allows receive packets which contain preamble fields less than 12 bytes in length

- 0 = The MAC allows any length preamble as per the Standard

#### bit 8 **PUREPRE:** Pure Preamble Enforcement bit

- 1 = The MAC will verify the content of the preamble to ensure it contains 0x55 and is error-free. A packet with errors in its preamble is discarded

- 0 = The MAC does not perform any preamble checking

- bit 7 AUTOPAD: Automatic Detect Pad Enable bit<sup>(1,2)</sup>

- 1 = The MAC will automatically detect the type of frame, either tagged or untagged, by comparing the two octets following the source address with 0x8100 (VLAN Protocol ID) and pad accordingly

- 0 = The MAC does not perform automatic detection

#### Note 1: Table 25-6 provides a description of the pad function based on the configuration of this register.

- 2: This bit is ignored if the PADENABLE bit is cleared.

- 3: This bit is used in conjunction with the AUTOPAD and VLANPAD bits.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware

# 26.1 Control Registers

# TABLE 26-1: COMPARATOR REGISTER MAP

| ess                      | Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |      | 6     |       |            |

|--------------------------|----------------------------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Addr<br>(BF80_#) |                                                                |           | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 4.000                    |                                                                | 31:16     | _     | _     |       | —     |       | _     |      |      |      | —      | —    | —    |      | -    | —     | -     | 0000       |

| A000                     | CM1CON                                                         | 15:0      | ON    | COE   | CPOL  | —     | _     | _     | _    | COUT | EVPO | L<1:0> | —    | CREF | _    | _    | CCH   | <1:0> | 00C3       |

| A010                     | CM2CON                                                         | 31:16     | _     | _     | _     | _     | _     | _     |      | _    | _    | —      | —    | —    |      |      | —     | _     | 0000       |

| AUTU                     |                                                                | 15:0      | ON    | COE   | CPOL  | -     | -     | -     |      | COUT | EVPO | L<1:0> | —    | CREF |      |      | CCH   | <1:0> | 00C3       |

| A060                     | CMSTAT                                                         | 31:16     |       | -     | —     | —     | —     | —     | —    | —    | —    | —      | —    | —    | —    | —    | —     | —     | 0000       |

| A060                     |                                                                | 15:0      |       | _     | SIDL  | _     |       | _     |      |      |      | _      | _    | _    |      |      | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# 31.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 31.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# TABLE 32-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHA        | RACTERIS | STICS                         |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |      |       |                                            |  |  |  |

|---------------|----------|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|--|--|

| Param.<br>No. | Symbol   | Charact                       | eristics                  | Min.                                                                                                                                                                                                                                                                                  | Max. | Units | Conditions                                 |  |  |  |

| IS10          | TLO:SCL  | Clock Low Time                | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   | —    | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |  |

|               |          |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                   | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |  |  |

|               |          |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                   |      | μs    | —                                          |  |  |  |

| IS11          | THI:SCL  | Clock High Time               | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                   | —    | μS    | PBCLK must operate at a minimum of 800 kHz |  |  |  |