Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | -                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512lt-80i-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

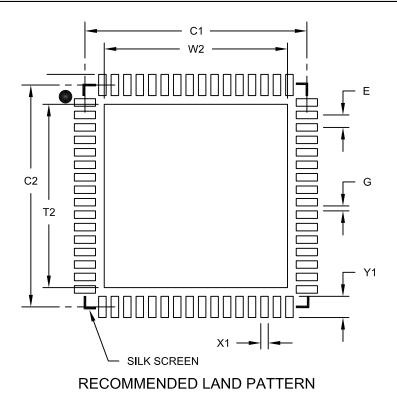

#### TABLE 5: PIN NAMES FOR 64-PIN USB AND ETHERNET DEVICES

| TABLE 5: PIN NAMES FOR 64-PIN USB AND ETHERNET DEVICES |                                                                                                |                         |                                               |  |  |  |  |  |  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------|-----------------------------------------------|--|--|--|--|--|--|

| 64                                                     | -PIN QFN <sup>(2)</sup> AND TQFP (TOP VIEW)                                                    |                         |                                               |  |  |  |  |  |  |

|                                                        | PIC32MX664F064H<br>PIC32MX664F128H<br>PIC32MX675F256H<br>PIC32MX675F512H<br>PIC32MX695F512H 64 | 1                       |                                               |  |  |  |  |  |  |

|                                                        | 04                                                                                             | 1                       |                                               |  |  |  |  |  |  |

|                                                        | QFN                                                                                            | <b>1</b> <sup>(2)</sup> | <sup>64</sup> <b>TQFP</b>                     |  |  |  |  |  |  |

| Pin #                                                  | Full Pin Name                                                                                  | Pin #                   | Full Pin Name                                 |  |  |  |  |  |  |

| 1                                                      | ETXEN/PMD5/RE5                                                                                 | 33                      | USBID/RF3                                     |  |  |  |  |  |  |

| 2                                                      | ETXD0/PMD6/RE6                                                                                 | 34                      | VBUS                                          |  |  |  |  |  |  |

| 3                                                      | ETXD1/PMD7/RE7                                                                                 | 35                      | VUSB3V3                                       |  |  |  |  |  |  |

| 4                                                      | SCK2/U6TX/U3RTS/PMA5/CN8/RG6                                                                   | 36                      | D-/RG3                                        |  |  |  |  |  |  |

| 5                                                      | SDA4/SDI2/U3RX/PMA4/CN9/RG7                                                                    | 37                      | D+/RG2                                        |  |  |  |  |  |  |

| 6                                                      | SCL4/SDO2/U3TX/PMA3/CN10/RG8                                                                   | 38                      | Vdd                                           |  |  |  |  |  |  |

| 7                                                      | MCLR                                                                                           | 39                      | OSC1/CLKI/RC12                                |  |  |  |  |  |  |

| 8                                                      | SS2/U6RX/U3CTS/PMA2/CN11/RG9                                                                   | 40                      | OSC2/CLKO/RC15                                |  |  |  |  |  |  |

| 9                                                      | Vss                                                                                            | 41                      | Vss                                           |  |  |  |  |  |  |

| 10                                                     | Vdd                                                                                            | 42                      | RTCC/AERXD1/ETXD3/IC1/INT1/RD8                |  |  |  |  |  |  |

| 11                                                     | AN5/C1IN+/Vbuson/CN7/RB5                                                                       | 43                      | AERXD0/ETXD2/SS3/U4RX/U1CTS/SDA1/IC2/INT2/RD9 |  |  |  |  |  |  |

| 12                                                     | AN4/C1IN-/CN6/RB4                                                                              | 44                      | ECOL/AECRSDV/SCL1/IC3/PMCS2/PMA15/INT3/RD10   |  |  |  |  |  |  |

| 13                                                     | AN3/C2IN+/CN5/RB3                                                                              | 45                      | ECRS/AEREFCLK/IC4/PMCS1/PMA14/INT4/RD11       |  |  |  |  |  |  |

| 14                                                     | AN2/C2IN-/CN4/RB2                                                                              | 46                      | OC1/INT0/RD0                                  |  |  |  |  |  |  |

| 15                                                     | PGEC1/AN1/VREF-/CVREF-/CN3/RB1                                                                 | 47                      | SOSCI/CN1/RC13                                |  |  |  |  |  |  |

| 16                                                     | PGED1/AN0/VREF+/CVREF+/PMA6/CN2/RB0                                                            | 48                      | SOSCO/T1CK/CN0/RC14                           |  |  |  |  |  |  |

| 17                                                     | PGEC2/AN6/OCFA/RB6                                                                             | 49                      | EMDIO/AEMDIO/SCK3/U4TX/U1RTS/OC2/RD1          |  |  |  |  |  |  |

| 18                                                     | PGED2/AN7/RB7                                                                                  | 50                      | SDA3/SDI3/U1RX/OC3/RD2                        |  |  |  |  |  |  |

| 19                                                     | AVdd                                                                                           | 51                      | SCL3/SDO3/U1TX/OC4/RD3                        |  |  |  |  |  |  |

| 20                                                     | AVss                                                                                           | 52                      | OC5/IC5/PMWR/CN13/RD4                         |  |  |  |  |  |  |

| 21                                                     | AN8/SS4/U5RX/U2CTS/C1OUT/RB8                                                                   | 53                      | PMRD/CN14/RD5                                 |  |  |  |  |  |  |

| 22                                                     | AN9/C2OUT/PMA7/RB9                                                                             | 54                      | AETXEN/ETXERR/CN15/RD6                        |  |  |  |  |  |  |

| 23                                                     | TMS/AN10/CVREFOUT/PMA13/RB10                                                                   | 55                      | ETXCLK/AERXERR/CN16/RD7                       |  |  |  |  |  |  |

| 24                                                     | TDO/AN11/PMA12/RB11                                                                            | 56                      | VCAP                                          |  |  |  |  |  |  |

| 25                                                     | Vss                                                                                            | 57                      | VDD                                           |  |  |  |  |  |  |

| 26                                                     | Vdd                                                                                            | 58                      | AETXD1/ERXD3/RF0                              |  |  |  |  |  |  |

| 27                                                     | TCK/AN12/PMA11/RB12                                                                            | 59                      | AETXD0/ERXD2/RF1                              |  |  |  |  |  |  |

| 28                                                     | TDI/AN13/PMA10/RB13                                                                            | 60                      | ERXD1/PMD0/RE0                                |  |  |  |  |  |  |

| 29                                                     | AN14/SCK4/U5TX/U2RTSU2RTS/PMALH/PMA1/RB14                                                      | 61                      | ERXD0/PMD1/RE1                                |  |  |  |  |  |  |

| 30                                                     | AN15/EMDC/AEMDC/OCFB/PMALL/PMA0/CN12/RB15                                                      | 62                      | ERXDV/ECRSDV/PMD2/RE2                         |  |  |  |  |  |  |

| 31                                                     | SDA5/SDI4/U2RX/PMA9/CN17/RF4                                                                   | 63                      | ERXCLK/EREFCLK/PMD3/RE3                       |  |  |  |  |  |  |

| 32                                                     | SCL5/SDO4/U2TX/PMA8/CN18/RF5                                                                   | 64                      | ERXERR/PMD4/RE4                               |  |  |  |  |  |  |

|                                                        |                                                                                                |                         |                                               |  |  |  |  |  |  |

Note 1: Shaded pins are 5V tolerant.

2: The metal plane at the bottom of the QFN device is not connected to any pins and is recommended to be connected to Vss externally.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

### TABLE 3-3: PIC32MX5XX/6XX/7XX FAMILY CORE EXCEPTION TYPES

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error.<br>Fetch reference to protected address.                                                                 |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error.<br>Load reference to protected address.                                                                   |

| AdES      | Store address alignment error.<br>Store to protected address.                                                                           |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

#### **TABLE 7-3**: INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND PIC32MX695F512H DEVICES (CONTINUED)

| ess                                      |                                 |           |       |       |       |       |             |       |               | В                | its  |      |           |                            |             |             |                      |        |            |

|------------------------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------|-------|---------------|------------------|------|------|-----------|----------------------------|-------------|-------------|----------------------|--------|------------|

| Virtual Address<br>(BF88_#)<br>Reclister | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11       | 26/10 | 25/9          | 24/8             | 23/7 | 22/6 | 21/5      | 20/4                       | 19/3        | 18/2        | 17/1                 | 16/0   | All Resets |

| 4000                                     | IPC4                            | 31:16     | —     | _     | —     |       | INT4IP<2:0> |       | INT4IS<1:0>   |                  | —    | -    | —         |                            | OC4IP<2:0>  | •           | OC4IS                | 5<1:0> | 0000       |

| 10D0                                     | IPC4                            | 15:0      | _     | -     | _     |       | IC4IP<2:0>  |       | IC4IS         | <1:0>            | _    | _    | _         |                            | T4IP<2:0>   |             | T4IS                 | <1:0>  | 0000       |

| 10E0                                     | IPC5                            | 31:16     | _     | -     | _     | _     | _           | _     | _             | _                | _    | _    | _         |                            | OC5IP<2:0>  | •           | OC5IS                | 5<1:0> | 0000       |

| IUEU                                     | IPC5                            | 15:0      | —     | _     | -     |       | IC5IP<2:0>  |       | IC5IS         | <1:0>            | —    |      |           |                            | T5IP<2:0>   |             | T5IS<                | <1:0>  | 0000       |

|                                          |                                 | 31:16     | _     | -     | _     |       | AD1IP<2:0>  |       | AD1IS         | S<1:0>           | _    | _    | _         |                            | CNIP<2:0>   |             | CNIS                 | <1:0>  | 0000       |

| 10F0                                     | IPC6                            |           |       |       |       |       |             |       |               |                  |      |      | U1IP<2:0> |                            | U1IS-       | <1:0>       |                      |        |            |

| IOFU                                     | IFCO                            | 15:0      | —     | —     | —     |       | I2C1IP<2:0> |       | I2C1IS<1:0> — |                  |      |      | —         |                            | SPI3IP<2:0> | >           | SPI3IS               | S<1:0> | 0000       |

|                                          |                                 |           |       |       |       |       |             |       |               |                  |      |      |           | I2C3IP<2:0>                |             | I2C3IS<1:0> |                      |        |            |

|                                          |                                 |           |       |       |       |       | U3IP<2:0>   |       | U3IS-         | <1:0>            |      |      |           |                            |             |             |                      |        |            |

| 1100                                     | IPC7                            | 31:16     | —     | -     | —     |       | SPI2IP<2:0> |       | SPI2IS        | S<1:0>           | —    | —    | —         |                            | CMP2IP<2:0  | >           | CMP2I                | S<1:0> | 0000       |

| 1100                                     | 11 07                           |           |       |       |       |       | I2C4IP<2:0> |       | 12C415        | S<1:0>           |      |      |           |                            |             |             |                      |        |            |

|                                          |                                 | 15:0      | _     | —     |       | (     | CMP1IP<2:0: | >     | CMP1          | S<1:0>           | —    |      |           |                            | PMPIP<2:0>  | >           | PMPIS<1:0>           |        | 0000       |

|                                          |                                 | 31:16     | —     | —     | —     | F     | RTCCIP<2:0: | >     | RTCCI         | S<1:0>           | —    | —    |           | I                          | FSCMIP<2:0  | >           | FSCM                 | S<1:0> | 0000       |

| 1110                                     | IPC8                            |           |       |       |       |       |             |       |               |                  |      |      |           |                            | U2IP<2:0>   |             | U2IS-                | <1:0>  |            |

|                                          | 11 00                           | 15:0      | —     | -     | —     | —     | —           | —     | —             | —                | —    | —    | —         |                            | SPI4IP<2:0> | >           | SPI4IS               | S<1:0> | 0000       |

|                                          |                                 |           |       |       |       |       |             |       |               |                  |      |      |           |                            | I2C5IP<2:0> | >           | 12C515               | S<1:0> |            |

| 1120                                     | IPC9                            | 31:16     | —     | —     | —     |       | DMA3IP<2:0: |       | DMA3          |                  | —    | _    |           |                            | DMA2IP<2:0  |             | DMA2                 |        | 0000       |

| 1120                                     | 11 00                           | 15:0      | _     | —     |       |       | DMA1IP<2:0: |       | DMA1          |                  | —    | _    |           |                            | DMA0IP<2:0  |             | DMA0I                |        | 0000       |

| 1130                                     | IPC10                           | 31:16     | —     | —     | —     |       | MA7IP<2:0>  |       |               | <1:0> <b>(2)</b> | —    | —    |           |                            | MA6IP<2:0>  |             | DMA6IS               |        | 0000       |

| 1130                                     | 11 010                          | 15:0      | _     | —     |       | D     | MA5IP<2:0>  | (2)   | DMA5IS        | <1:0> <b>(2)</b> | —    | _    |           | DMA4IP<2:0> <sup>(2)</sup> |             | DMA4IS      | <1:0> <sup>(2)</sup> | 0000   |            |

| 1140                                     | IPC11                           | 31:16     | —     | —     | —     | _     | —           | —     | —             | —                | —    | _    | _         | —                          | _           | —           | —                    | —      | 0000       |

|                                          |                                 | 15:0      | —     | —     | —     |       | USBIP<2:0>  |       | USBIS         |                  | —    | —    | —         |                            | FCEIP<2:0>  |             | FCEIS                |        | 0000       |

| 1150                                     | IPC12                           | 31:16     | —     | —     | —     |       | U5IP<2:0>   |       | U5IS-         | <1:0>            | —    | _    | _         |                            | U6IP<2:0>   |             | U6IS-                | <1:0>  | 0000       |

| 1100                                     | 11 012                          | 15:0      | _     | —     | —     |       | U4IP<2:0>   |       | U4IS-         | <1:0>            | —    | _    | —         |                            | ETHIP<2:0>  |             | ETHIS                | i<1:0> | 0000       |

Legend: x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information. These bits are not available on PIC32MX664 devices. This register does not have associated CLR, SET, and INV registers.

2:

3:

# TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |       |                         |       |             | Bi                    | its         |             |              |                            |             |        |                      |                      |             |   |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------------------------|-------|-------------|-----------------------|-------------|-------------|--------------|----------------------------|-------------|--------|----------------------|----------------------|-------------|---|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11                   | 26/10 | 25/9        | 24/8                  | 23/7        | 22/6        | 21/5         | 20/4                       | 19/3        | 18/2   | 17/1                 | 16/0                 | All Resets  |   |        |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |       | INT4IP<2:0>             |       | INT4IS      | S<1:0>                | _           | —           | -            |                            | OC4IP<2:0>  |        | OC4IS                | 6<1:0>               | 0000        |   |        |        |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |       | IC4IP<2:0>              |       | IC4IS       | <1:0>                 | _           | _           | _            |                            | T4IP<2:0>   |        | T4IS-                | <1:0>                | 0000        |   |        |        |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |       | SPI1IP<2:0>             |       | SPI1IS      | 6<1:0>                | _           | _           | _            |                            | OC5IP<2:0>  |        | OC5IS                | S<1:0>               | 0000        |   |        |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |       | IC5IP<2:0>              |       | IC5IS       | <1:0>                 | -           |             | _            |                            | T5IP<2:0>   |        | T5IS-                | <1:0>                | 0000        |   |        |        |      |

|                             |                                 | 31:16     | _     | _     | _     |       | AD1IP<2:0>              |       | AD1IS       | S<1:0>                | _           | _           | _            |                            | CNIP<2:0>   |        | CNIS                 | <1:0>                | 0000        |   |        |        |      |

| 10F0                        | IPC6                            |           |       |       |       |       | I2C1IP<2:0> I2C1IS<1:0> |       |             |                       |             |             | U1IP<2:0>    |                            | U1IS-       | <1:0>  |                      |                      |             |   |        |        |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     |       |                         |       | I2C1IS<1:0> |                       | I2C1IS<1:0> |             | I2C1IS<1:0>  |                            | —           | —      | —                    |                      | SPI3IP<2:0> | • | SPI3IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |       |                         |       |             |                       |             |             |              | I2C3IP<2:0>                |             |        | 12C315               | I2C3IS<1:0>          |             |   |        |        |      |

|                             |                                 |           |       |       |       |       | U3IP<2:0>               |       | U3IS        | U3IS<1:0>             |             |             |              |                            |             |        |                      |                      |             |   |        |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |       | SPI2IP<2:0>             |       | SPI2IS      | S<1:0>                | —           | —           | —            | (                          | CMP2IP<2:0  | >      | CMP2I                | S<1:0>               | 0000        |   |        |        |      |

| 1100                        | 11 07                           |           |       |       |       |       | I2C4IP<2:0>             |       | 12C415      | S<1:0>                |             |             |              |                            |             |        |                      |                      |             |   |        |        |      |

|                             |                                 | 15:0      | _     |       |       | (     | CMP1IP<2:0              | >     | CMP1I       | S<1:0>                | _           | _           |              | PMPIP<2:0>                 |             | PMPIS  | S<1:0>               | 0000                 |             |   |        |        |      |

|                             |                                 | 31:16     | _     |       |       | F     | RTCCIP<2:0              | >     | RTCCI       | S<1:0>                | _           | _           |              | I                          | FSCMIP<2:0  | >      | FSCMI                | S<1:0>               | 0000        |   |        |        |      |

| 1110                        | IPC8                            |           |       |       |       |       |                         |       |             |                       |             |             |              |                            | U2IP<2:0>   |        | U2IS-                | <1:0>                |             |   |        |        |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |       | I2C2IP<2:0>             |       | 12C2IP<2:0> |                       | 12C215      | I2C2IS<1:0> |              | 2IS<1:0>                   | —           | —      | l — [                |                      | SPI4IP<2:0> |   | SPI4IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |       |                         |       |             |                       |             |             |              |                            | I2C5IP<2:0> |        | 12C515               | S<1:0>               |             |   |        |        |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |       | DMA3IP<2:0              |       | DMA3I       | S<1:0>                | _           |             |              |                            | DMA2IP<2:0  |        | DMA2I                | S<1:0>               | 0000        |   |        |        |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |       | DMA1IP<2:0              |       | DMA1I       |                       | _           |             |              |                            | DMA0IP<2:0  |        | DMA0I                | S<1:0>               | 0000        |   |        |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI    | MA7IP<2:0>              | (2)   | DMA7IS      | i<1:0> <sup>(2)</sup> | —           | _           | —            | D                          | MA6IP<2:0>  | (2)    | DMA6IS               | <1:0> <sup>(2)</sup> | 0000        |   |        |        |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI    | MA5IP<2:0>              | (2)   | DMA5IS      | i<1:0> <sup>(2)</sup> | _           | _           | —            | DMA4IP<2:0> <sup>(2)</sup> |             | DMA4IS | <1:0> <sup>(2)</sup> | 0000                 |             |   |        |        |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _     | _                       |       | _           |                       |             |             | _            | _                          | —           |        | —                    |                      | 0000        |   |        |        |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |       | USBIP<2:0>              |       | USBIS       | S<1:0>                | _           | _           | — FCEIP<2:0> |                            | FCEIS       | <1:0>  | 0000                 |                      |             |   |        |        |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |       | U5IP<2:0>               |       | U5IS-       | <1:0>                 | _           |             | -            |                            | U6IP<2:0>   |        | U6IS-                | <1:0>                | 0000        |   |        |        |      |

| 1150                        | IFUIZ                           | 15:0      | _     | -     | -     |       | U4IP<2:0>               |       | U4IS-       | <1:0>                 |             |             |              |                            | ETHIP<2:0>  |        | ETHIS                | i<1:0>               | 0000        |   |        |        |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

NOTES:

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 **SOSCEN:** Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

#### bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

Note: Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | CHEWEN            | —                 | _                 | —                 | —                 | -                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 |                   | —                 | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   | —                 | —                 |                   | —                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | —                 |                   | CHEID             | X<3:0>           |                  |

#### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |  |

|-------------------|------------------|-----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |  |

#### bit 31 CHEWEN: Cache Access Enable bits

- These bits apply to registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3.

- 1 = The cache line selected by CHEIDX<3:0> is writeable

- 0 = The cache line selected by CHEIDX<3:0> is not writeable

- bit 30-4 **Unimplemented:** Write '0'; ignore read

#### bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|

| 24.24        | U-0                   | U-0              |

| 31:24        |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |

| 00.16        | U-0                   | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | —                 | _                     | —                |

| 15:8         | U-0                   | U-0              |

| 10.0         |                   | _                 | _                 | _                 | —                 | —                 | _                     | —                |

|              | R/W-0                 | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup> |                  |

|              | DISEE             | DIVIXEE           | DIVIAEE           | DIVEE             | DENGEE            | UKU16EE           | EOFEE <sup>(2)</sup>  | PIDEE            |

#### REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| 5                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

| bit 31-8 | Unimplemented: Read as '0'                                                               |

|----------|------------------------------------------------------------------------------------------|

| bit 7    | BTSEE: Bit Stuff Error Interrupt Enable bit                                              |

|          | <ul><li>1 = BTSEF interrupt is enabled</li><li>0 = BTSEF interrupt is disabled</li></ul> |

| bit 6    | BMXEE: Bus Matrix Error Interrupt Enable bit                                             |

|          | 1 = BMXEF interrupt is enabled                                                           |

|          | 0 = BMXEF interrupt is disabled                                                          |

| bit 5    | DMAEE: DMA Error Interrupt Enable bit                                                    |

|          | <ul><li>1 = DMAEF interrupt is enabled</li><li>0 = DMAEF interrupt is disabled</li></ul> |

| bit 4    | BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit                                |

|          | 1 = BTOEF interrupt is enabled                                                           |

- 0 = BTOEF interrupt is disabled

- bit 3 DFN8EE: Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup> bit 1

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

- Note 1: Device mode.

- 2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|--------------------------|-------------------|-----------------------|-----------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 31:24        |                   |                   | —                        | —                 |                       |                       | —                | —                    |

| 00.40        | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 23:16        | -                 | -                 | —                        | —                 | _                     | -                     | —                | —                    |

| 15:8         | U-0               | U-0               | U-0                      | U-0               | U-0                   | U-0                   | U-0              | U-0                  |

| 15.6         |                   |                   | —                        | —                 |                       |                       | —                | —                    |

|              | R-x               | R-x               | R/W-0                    | R/W-0             | R/W-0                 | R/W-0                 | R/W-0            | R/W-0                |

| 7:0          | JSTATE            | SE0               | PKTDIS <sup>(4)</sup>    | USBRST            | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST           | USBEN <sup>(4)</sup> |

|              | JUNE              | 320               | TOKBUSY <sup>(1,5)</sup> | 030631            | TIOSTEIN'             | KESUME"               | FFDKOI           | SOFEN <sup>(5)</sup> |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE was detected on the USB

- 0 = JSTATE was not detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single-ended zero was detected on the USB

0 = Single-ended zero was not detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

- bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

- bit 2 **RESUME:** RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set RESUME for 10 ms in Device mode, or for 25 ms in Host mode, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         |                   | —                 |                   |                   |                   |                   |                  | —                |

| 7.0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           |                   |                   |                  | UASUSPND         |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

- bit 6 **UOEMON:** USB OE Monitor Enable bit

- $1 = \overline{OE}$  signal is active; it indicates intervals during which the D+/D- lines are driving

- $0 = \overline{OE}$  signal is inactive

- bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------------|--------------------|-------------------|-------------------|-------------------|------------------------------|------------------|------------------|

| 31:24        | U-0                     | U-0                | U-0               | U-0               | U-0               | U-0                          | U-0              | U-0              |

| 31.24        | —                       | _                  | _                 | —                 | _                 | —                            | —                | —                |

| 22:16        | U-0                     | R/W-0              | U-0               | U-0               | U-0               | R/W-0                        | R/W-0            | R/W-0            |

| 23:16        |                         | WAKFIL             |                   | —                 | _                 | SEG2PH<2:0> <sup>(1,4)</sup> |                  | ,4)              |

| 15.0         | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            | R/W-0            |

| 15:8         | SEG2PHTS <sup>(1)</sup> | SAM <sup>(2)</sup> | Ş                 | SEG1PH<2:0        | >                 | PRSEG<2:0>                   |                  |                  |

| 7.0          | R/W-0                   | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0                        | R/W-0            | R/W-0            |

| 7:0          | SJW<1:0> <sup>(3)</sup> |                    | BRP<5:0>          |                   |                   |                              |                  |                  |

### REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER

| Legend:           | HC = Hardware Clear | S = Settable bit          |                    |  |

|-------------------|---------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit    | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set    | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-23 Unimplemented: Read as '0'

- bit 22 **WAKFIL:** CAN Bus Line Filter Enable bit 1 = Use CAN bus line filter for wake-up 0 = CAN bus line filter is not used for wake-up

- bit 21-19 Unimplemented: Read as '0'

| bit 18-16 | SEG2PH<2:0>: Phase Buffer Segment 2 bits <sup>(1,4)</sup>                     |

|-----------|-------------------------------------------------------------------------------|

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x Tq                                                        |

| bit 15    | SEG2PHTS: Phase Segment 2 Time Select bit <sup>(1)</sup>                      |

|           | 1 = Freely programmable                                                       |

|           | 0 = Maximum of SEG1PH or Information Processing Time, whichever is greater    |

| bit 14    | SAM: Sample of the CAN Bus Line bit <sup>(2)</sup>                            |

|           | 1 = Bus line is sampled three times at the sample point                       |

|           | 0 = Bus line is sampled once at the sample point                              |

| bit 13-11 | SEG1PH<2:0>: Phase Buffer Segment 1 bits <sup>(4)</sup>                       |

|           | 111 = Length is 8 x TQ                                                        |

|           | •                                                                             |

|           | •                                                                             |

|           | •                                                                             |

|           | 000 = Length is 1 x Tq                                                        |

|           |                                                                               |

| Note 1:   | SEG2PH $\leq$ SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically. |

| 2:        | 3 Time bit sampling is not allowed for BRP < 2.                               |

| 3:        | SJW ≤ SEG2PH.                                                                 |

| 4:        | The Time Quanta per bit must be greater than 7 (that is, $TQBIT > 7$ ).       |

|           |                                                                               |

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 51.24        | —                 | _                 | _                 | _                 | —                       | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | —                       | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 15:8         | —                 | _                 | _                 | FILHIT<4:0>       |                         |                   |                  |                  |

| 7.0          | U-0               | R-1               | R-0               | R-0               | R-0                     | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   |                   | ļ                 | CODE<6:0> <sup>(1</sup> | )                 |                  |                  |

### REGISTER 24-4: CiVEC: CAN INTERRUPT CODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-13 Unimplemented: Read as '0'

| bit 12-8 | FILHIT<4:0>: Filter Hit Number bit                  |

|----------|-----------------------------------------------------|

|          | 11111 = Filter 31                                   |

|          | 11110 = Filter 30                                   |

|          | •                                                   |

|          | •                                                   |

|          | 00001 = Filter 1                                    |

|          | 00000 = Filter 0                                    |

| bit 7    | Unimplemented: Read as '0'                          |

| bit 6-0  | ICODE<6:0>: Interrupt Flag Code bits <sup>(1)</sup> |

|          | 11111111 = Reserved                                 |

|          | •                                                   |

|          | •                                                   |

|          | •<br>1001001 = Reserved                             |

|          | 1001000 = Invalid message received (IVRIF)          |

|          | 1001111 = CAN module mode change (MODIF)            |

|          | 1000110 = CAN timestamp timer (CTMRIF)              |

|          | 1000101 = Bus bandwidth error (SERRIF)              |

|          | 1000100 = Address error interrupt (SERRIF)          |

|          | 1000011 = Receive FIFO overflow interrupt (RBOVIF)  |

|          | 1000010 = Wake-up interrupt (WAKIF)                 |

|          | 1000001 = Error Interrupt (CERRIF)                  |

|          | 1000000 = No interrupt                              |

|          | 0111111 = Reserved                                  |

|          | •                                                   |

|          | •                                                   |

|          | 0100000 = Reserved                                  |

|          | 0011111 = FIFO31 Interrupt (CiFSTAT<31> set)        |

|          | 0011110 = FIFO30 Interrupt (CiFSTAT<30> set)        |

|          | •                                                   |

|          | •                                                   |

|          | 0000001 = FIFO1 Interrupt (CiFSTAT<1> set)          |

|          | 0000000 = FIFO0 Interrupt (CiFSTAT<0> set)          |

|          |                                                     |

Note 1: These bits are only updated for enabled interrupts.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|--|--|--|

| 31:24        | R/W-0              | R/W-0              |  |  |  |

| 31.24        |                   |                   |                   | CiFIFOB           | A<31:24>          |                   |                    |                    |  |  |  |

| 23:16        | R/W-0              | R/W-0              |  |  |  |

| 23.10        |                   | CiFIFOBA<23:16>   |                   |                   |                   |                   |                    |                    |  |  |  |

| 15:8         | R/W-0              | R/W-0              |  |  |  |

| 0.61         | CiFIFOBA<15:8>    |                   |                   |                   |                   |                   |                    |                    |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0 <sup>(1)</sup> | R-0 <sup>(1)</sup> |  |  |  |

| 7:0          |                   | CiFIFOBA<7:0>     |                   |                   |                   |                   |                    |                    |  |  |  |

#### REGISTER 24-19: CIFIFOBA: CAN MESSAGE BUFFER BASE ADDRESS REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 CiFIFOBA<31:0>: CAN FIFO Base Address bits

These bits define the base address of all message buffers. Individual message buffers are located based on the size of the previous message buffers. This address is a physical address. Bits <1:0> are read-only and read as '0', forcing the messages to be 32-bit word-aligned in device RAM.

**Note 1:** This bit is unimplemented and will always read '0', which forces word-alignment of messages.

**Note:** This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

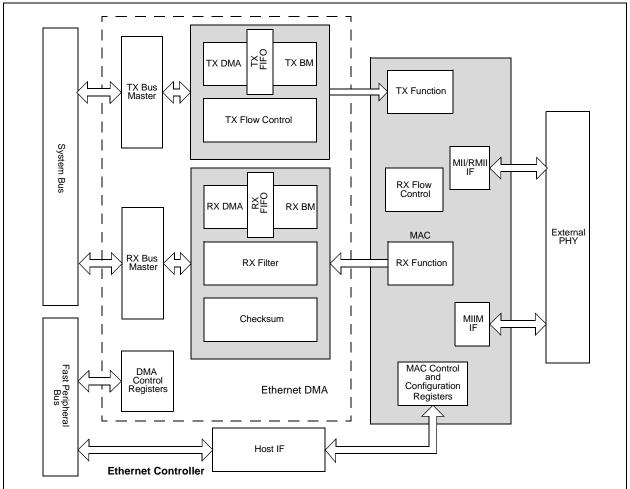

### 25.0 ETHERNET CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 35. "Ethernet Controller" (DS60001155) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Ethernet controller is a bus master module that interfaces with an off-chip Physical Layer (PHY) to implement a complete Ethernet node in a system.

Key features of the Ethernet Controller include:

- Supports 10/100 Mbps data transfer rates

- Supports full-duplex and half-duplex operation

- Supports RMII and MII PHY interface

- Supports MIIM PHY management interface

- Supports both manual and automatic Flow Control

- RAM descriptor-based DMA operation for both receive and transmit path

- · Fully configurable interrupts

- Configurable receive packet filtering

- CRC check

- 64-byte pattern match

- Broadcast, multicast and unicast packets

- Magic Packet™

- 64-bit hash table

- Runt packet

- Supports packet payload checksum calculation

- · Supports various hardware statistics counters

Figure 25-1 illustrates a block diagram of the Ethernet controller.

### FIGURE 25-1: ETHERNET CONTROLLER BLOCK DIAGRAM

#### REGISTER 25-18: ETHSCOLFRM: ETHERNET CONTROLLER SINGLE COLLISION FRAMES STATISTICS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24     | -                 | —                 | _                 | —                 | -                 | —                 | _                | —                |  |  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | _                 | —                 | _                 | _                 | _                 | —                 | _                | —                |  |  |

| 15.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | SCOLFRMCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | SCOLFRMCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **SCOLFRMCNT<15:0>:** Single Collision Frame Count bits Increment count for frames that were successfully transmitted on the second try.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

#### TABLE 32-33: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHARACTERISTICS |         |                               |                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-Temp} \end{array}$ |      |       |                                            |  |

|--------------------|---------|-------------------------------|---------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|--|

| Param.<br>No.      | Symbol  | Charact                       | eristics                  | Min.                                                                                                                                                                                                                                                                                  | Max. | Units | Conditions                                 |  |

| IS10               | TLO:SCL | Clock Low Time                | 100 kHz mode              | 4.7                                                                                                                                                                                                                                                                                   | _    | μS    | PBCLK must operate at a minimum of 800 kHz |  |

|                    |         |                               | 400 kHz mode              | 1.3                                                                                                                                                                                                                                                                                   | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                   |      | μs    | —                                          |  |

| IS11               | THI:SCL | Clock High Time               | 100 kHz mode              | 4.0                                                                                                                                                                                                                                                                                   | —    | μS    | PBCLK must operate at a minimum of 800 kHz |  |

|                    |         |                               | 400 kHz mode              | 0.6                                                                                                                                                                                                                                                                                   | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0.5                                                                                                                                                                                                                                                                                   | —    | μs    | —                                          |  |

| IS20               | TF:SCL  | SDAx and SCLx<br>Fall Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                     | 300  | ns    | CB is specified to be from                 |  |

|                    |         |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | 10 to 400 pF                               |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                     | 100  | ns    |                                            |  |

| IS21               | TR:SCL  | SDAx and SCLx<br>Rise Time    | 100 kHz mode              | —                                                                                                                                                                                                                                                                                     | 1000 | ns    | CB is specified to be from                 |  |

|                    |         |                               | 400 kHz mode              | 20 + 0.1 Св                                                                                                                                                                                                                                                                           | 300  | ns    | 10 to 400 pF                               |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | —                                                                                                                                                                                                                                                                                     | 300  | ns    |                                            |  |

| IS25               | TSU:DAT | Data Input<br>Setup Time      | 100 kHz mode              | 250                                                                                                                                                                                                                                                                                   |      | ns    |                                            |  |

|                    |         |                               | 400 kHz mode              | 100                                                                                                                                                                                                                                                                                   |      | ns    |                                            |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 100                                                                                                                                                                                                                                                                                   |      | ns    |                                            |  |

| IS26               | Thd:dat | Data Input<br>Hold Time       | 100 kHz mode              | 0                                                                                                                                                                                                                                                                                     |      | ns    | _                                          |  |

|                    |         |                               | 400 kHz mode              | 0                                                                                                                                                                                                                                                                                     | 0.9  | μs    |                                            |  |

|                    |         |                               | 1 MHz mode <sup>(1)</sup> | 0                                                                                                                                                                                                                                                                                     | 0.3  | μs    |                                            |  |

| IS30               | Tsu:sta | Start Condition<br>Setup Time | 100 kHz mode              | 4700                                                                                                                                                                                                                                                                                  |      | ns    | Only relevant for Repeated                 |  |