Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | -                                                                                 |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

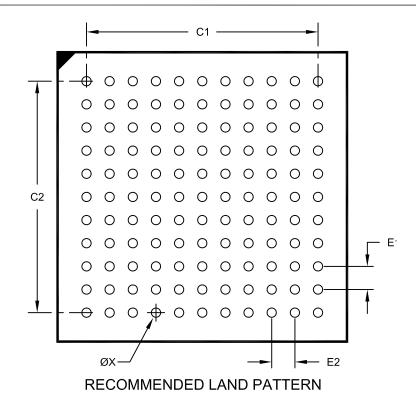

| Package / Case             | 121-TFBGA                                                                         |

| Supplier Device Package    | 121-TFBGA (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512lt-80v-bg |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                  | USB, Ethernet, and CAN |                         |                  |     |          |        |                        |                                          |                       |                    |                                 |                              |             |         |      |       |                         |

|------------------|------------------------|-------------------------|------------------|-----|----------|--------|------------------------|------------------------------------------|-----------------------|--------------------|---------------------------------|------------------------------|-------------|---------|------|-------|-------------------------|

| Device           | Pins                   | Program Memory (KB)     | Data Memory (KB) | USB | Ethernet | CAN    | Timers/Capture/Compare | DMA Channels<br>(Programmable/Dedicated) | UART <sup>(2,3)</sup> | SPI <sup>(3)</sup> | I <sup>2</sup> C <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Comparators | dSd/dMd | JTAG | Trace | Packages <sup>(4)</sup> |

| PIC32MX764F128H  | 64                     | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F256H  | 64                     | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX775F512H  | 64                     | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX795F512H  | 64                     | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 3                  | 4                               | 16                           | 2           | Yes     | Yes  | No    | PT,<br>MR               |

| PIC32MX764F128L  | 100                    | 128 + 12 <sup>(1)</sup> | 32               | 1   | 1        | 1      | 5/5/5                  | 4/6                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F256L  | 100                    | 256 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX775F512L  | 100                    | 512 + 12 <sup>(1)</sup> | 64               | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG           |

| PIC32MX795F512L  | 100                    | 512 + 12 <sup>(1)</sup> | 128              | 1   | 1        | 2      | 5/5/5                  | 8/8                                      | 6                     | 4                  | 5                               | 16                           | 2           | Yes     | Yes  | Yes   | PT, PF,<br>BG, TL       |

| Legend: PF, PT = | TQFF                   | P MR = C                | QFN              |     | BG       | G = TF | BGA                    |                                          | TL = \                | /TLA               | 5)                              |                              |             |         |      |       |                         |

#### TABLE 3: PIC32MX7XX USB, ETHERNET, AND CAN FEATURES

Note 1: This device features 12 KB boot Flash memory.

2: CTS and RTS pins may not be available for all UART modules. Refer to the "Device Pin Tables" section for more information.

3: Some pins between the UART, SPI and I<sup>2</sup>C modules may be shared. Refer to the "Device Pin Tables" section for more information.

4: Refer to Section 34.0 "Packaging Information" for more information.

5: 100-pin devices other than those listed here are available in the VTLA package upon request. Please contact your local Microchip Sales Office for details.

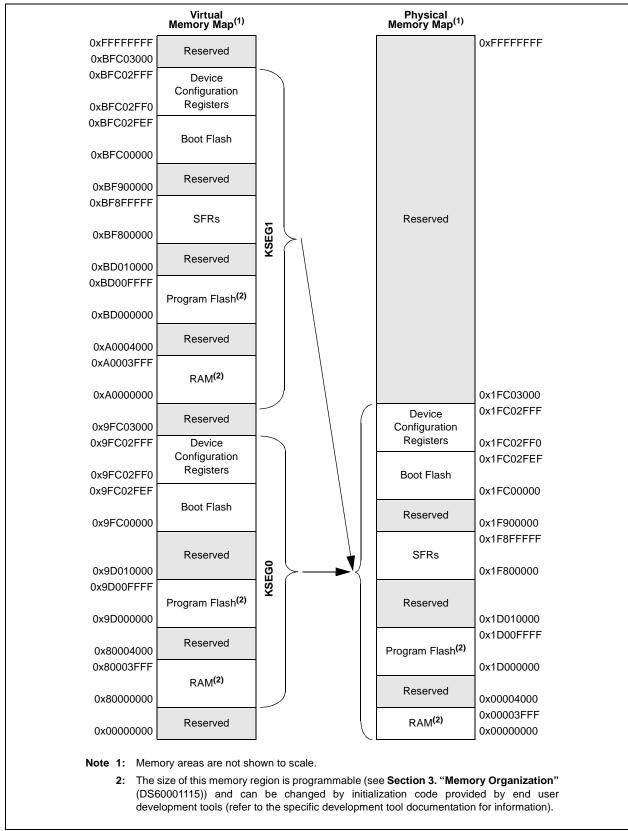

## FIGURE 4-2: MEMORY MAP ON RESET FOR PIC32MX534F064H AND PIC32MX534F064L DEVICES

|                             |                                 | P             | PIC32M                                                                                     | X695F5 <sup>°</sup> | 12H DE  | VICES                         |                               |                               |                               |                             |                               |                               |                             |                       |               |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------------------------------------------------------------------------------------------|---------------------|---------|-------------------------------|-------------------------------|-------------------------------|-------------------------------|-----------------------------|-------------------------------|-------------------------------|-----------------------------|-----------------------|---------------|--------|--------|--------|------------|

| ess                         |                                 |               |                                                                                            |                     |         |                               |                               |                               |                               | В                           | its                           |                               |                             |                       |               |        |        |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                                                                      | 30/14               | 29/13   | 28/12                         | 27/11                         | 26/10                         | 25/9                          | 24/8                        | 23/7                          | 22/6                          | 21/5                        | 20/4                  | 19/3          | 18/2   | 17/1   | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         |                                                                                            |                     | —       | —                             | _                             |                               | _                             |                             | _                             | —                             |                             | _                     |               |        | _      | SS0    | 0000       |

| 1000                        | INTCON                          | 15:0          | —                                                                                          | _                   | _       | MVEC                          | _                             |                               | TPC<2:0>                      |                             | _                             | -                             |                             | INT4EP                | INT3EP        | INT2EP | INT1EP | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | —                                                                                          | —                   | —       | —                             | —                             | —                             | —                             | —                           | —                             | —                             | —                           | —                     | —             | —      | —      | —      | 0000       |

| 1010                        |                                 | 15:0          |                                                                                            | —                   | —       | —                             | _                             |                               | SRIPL<2:0>                    |                             | —                             | —                             |                             |                       | VEC           | <5:0>  |        |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |                                                                                            |                     |         |                               |                               |                               |                               | IPTMR                       | <31:0>                        |                               |                             |                       |               |        |        |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF                                                                                    | I2C1SIF             | I2C1BIF | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF   | _                             | _                           | _                             | OC5IF                         | IC5IF                       | T5IF                  | INT4IF        | OC4IF  | IC4IF  | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF                                                                                     | OC3IF               | IC3IF   | T3IF                          | INT2IF                        | OC2IF                         | IC2IF                         | T2IF                        | INT1IF                        | OC1IF                         | IC1IF                       | T1IF                  | <b>INT0IF</b> | CS1IF  | CS0IF  | CTIF   | 0000       |

|                             |                                 | 31:16         | <b>IC3EIF</b>                                                                              | IC2EIF              | IC1EIF  | ETHIF                         | —                             | _                             | USBIF                         | FCEIF                       | DMA7IF <sup>(2)</sup>         | DMA6IF <sup>(2)</sup>         | DMA5IF <sup>(2)</sup>       | DMA4IF <sup>(2)</sup> | DMA3IF        | DMA2IF | DMA1IF | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF                                                                                     | FSCMIF              | _       | _                             | _                             | U2TXIF<br>SPI4TXIF<br>I2C5MIF | U2RXIF<br>SPI4RXIF<br>I2C5SIF | U2EIF<br>SPI4EIF<br>I2C5BIF | U3TXIF<br>SPI2TXIF<br>I2C4MIF | U3RXIF<br>SPI2RXIF<br>I2C4SIF | U3EIF<br>SPI2EIF<br>I2C4BIF | CMP2IF                | CMP1IF        | PMPIF  | AD1IF  | CNIF   | 0000       |

|                             |                                 | 31:16         |                                                                                            |                     |         |                               | _                             | _                             | _                             | _                           | _                             | _                             | _                           | _                     |               | _      | _      | _      | 0000       |

| 1050                        | IFS2                            | 15:0          | _                                                                                          | _                   | _       | _                             | U5TXIF                        | U5RXIF                        | U5EIF                         | U6TXIF                      | U6RXIF                        | U6EIF                         | U4TXIF                      | U4RXIF                | U4EIF         | PMPEIF | IC5EIF | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE                                                                                    | I2C1SIE             | I2C1BIE | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE   | _                             |                             | _                             | OC5IE                         | IC5IE                       | T5IE                  | INT4IE        | OC4IE  | IC4IE  | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE                                                                                     | OC3IE               | IC3IE   | T3IE                          | INT2IE                        | OC2IE                         | IC2IE                         | T2IE                        | INT1IE                        | OC1IE                         | IC1IE                       | T1IE                  | INT0IE        | CS1IE  | CS0IE  | CTIE   | 0000       |

|                             |                                 | 31:16         | IC3EIE                                                                                     | IC2EIE              | IC1EIE  | ETHIE                         | —                             | _                             | USBIE                         | FCEIE                       | DMA7IE <sup>(2)</sup>         | DMA6IE <sup>(2)</sup>         | DMA5IE <sup>(2)</sup>       | DMA4IE <sup>(2)</sup> | <b>DMA3IE</b> | DMA2IE | DMA1IE | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE                                                                                     | FSCMIE              | _       | _                             | -                             | U2TXIE<br>SPI4TXIE<br>I2C5MIE | U2RXIE<br>SPI4RXIE<br>I2C5SIE | U2EIE<br>SPI4EIE<br>I2C5BIE | U3TXIE<br>SPI2TXIE<br>I2C4MIE | U3RXIE<br>SPI2RXIE<br>I2C4SIE | U3EIE<br>SPI2EIE<br>I2C4BIE | CMP2IE                | CMP1IE        | PMPIE  | AD1IE  | CNIE   | 0000       |

|                             |                                 | 31:16         |                                                                                            | _                   | _       | _                             | _                             | _                             |                               | _                           | _                             | _                             | _                           | _                     |               | _      | _      | _      | 0000       |

| 1080                        | IEC2                            | 15:0          | _                                                                                          | _                   | _       | _                             | U5TXIE                        | U5RXIE                        | U5EIE                         | U6TXIE                      | U6RXIE                        | U6EIE                         | U4TXIE                      | U4RXIE                | U4EIE         | PMPEIE | IC5EIE | IC4EIE | 0000       |

|                             |                                 | 31:16         | _                                                                                          | _                   | _       |                               | INT0IP<2:0>                   |                               | INTOIS                        |                             | _                             | _                             | _                           |                       | CS1IP<2:0>    |        | CS1IS  |        | 0000       |

| 1090                        | IPC0                            | 15:0          | _                                                                                          | _                   | _       |                               | CS0IP<2:0>                    |                               | CSOIS                         | S<1:0>                      | _                             | _                             | _                           |                       | CTIP<2:0>     |        | CTIS   |        | 0000       |

| 1040                        | IPC1                            | 31:16         | _                                                                                          | _                   | _       |                               | INT1IP<2:0>                   |                               | INT1IS                        | S<1:0>                      | _                             | _                             | _                           | (                     | OC1IP<2:0>    |        | OC1IS  | S<1:0> | 0000       |

| 10A0                        | IPUT                            | 15:0          | _                                                                                          | _                   | _       |                               | IC1IP<2:0>                    |                               | IC1IS                         | <1:0>                       | _                             | _                             |                             |                       | T1IP<2:0>     |        | T1IS-  | <1:0>  | 0000       |

| 10B0                        | IPC2                            | 31:16         |                                                                                            | —                   | _       |                               | INT2IP<2:0>                   |                               | INT2IS                        | S<1:0>                      | —                             | —                             | _                           | OC2IP<2:0>            |               | •      | OC2IS  | S<1:0> | 0000       |

| 10D0                        | 1602                            | 15:0          | _                                                                                          | —                   | —       |                               | IC2IP<2:0>                    |                               | IC2IS                         | <1:0>                       | —                             | —                             | _                           |                       | T2IP<2:0>     |        | T2IS-  | <1:0>  | 0000       |

| 10C0                        | IPC3                            | 31:16         | —                                                                                          | —                   | -       |                               | INT3IP<2:0>                   |                               | INT3IS                        | S<1:0>                      | —                             | —                             |                             | OC3IP<2:0>            |               | OC3IS  | S<1:0> | 0000   |            |

| 1000                        | 1 00                            | 15:0          |                                                                                            | —                   | —       |                               | IC3IP<2:0>                    |                               | IC3IS                         | <1:0>                       | —                             | —                             | —                           |                       | T3IP<2:0>     |        | T3IS-  | <1:0>  | 0000       |

| Legend                      | <b>d:</b> x =                   | unknow        | own value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                     |         |                               |                               |                               |                               |                             |                               |                               |                             |                       |               |        |        |        |            |

#### **TABLE 7-3:** INTERRUPT REGISTER MAP FOR PIC32MX664F064H, PIC32MX664F128H, PIC32MX675F256H, PIC32MX675F512H AND DIC22MV605E512U DEVICES

DS60001156J-page 79

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does not have associated CLR, SET, and INV registers. 3:

© 2009-2016 Microchip Technology Inc.

|                             |                                 | P             | IC32M)        | <b>(695F5</b> 1 | 12L DE      | /ICES                         |                               |                             |                    |                  |                       |                       |                       |                         |            |        |                |        |            |

|-----------------------------|---------------------------------|---------------|---------------|-----------------|-------------|-------------------------------|-------------------------------|-----------------------------|--------------------|------------------|-----------------------|-----------------------|-----------------------|-------------------------|------------|--------|----------------|--------|------------|

| SS                          |                                 |               |               |                 |             |                               |                               |                             |                    | Bi               | its                   |                       |                       |                         |            |        |                |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14           | 29/13       | 28/12                         | 27/11                         | 26/10                       | 25/9               | 24/8             | 23/7                  | 22/6                  | 21/5                  | 20/4                    | 19/3       | 18/2   | 17/1           | 16/0   | All Resets |

| 1000                        | INTCON                          | 31:16         | _             | _               | —           | —                             | _                             |                             | —                  | —                | —                     | —                     | _                     | _                       | _          | —      | —              | SS0    | 0000       |

| 1000                        | introom                         | 15:0          | —             | —               | —           | MVEC                          | —                             |                             | TPC<2:0>           |                  | —                     | —                     | —                     | INT4EP                  | INT3EP     | INT2EP | INT1EP         | INT0EP | 0000       |

| 1010                        | INTSTAT <sup>(3)</sup>          | 31:16         | _             | _               |             |                               | _                             |                             |                    |                  |                       |                       | _                     | 0000                    |            |        |                |        |            |

|                             |                                 | 15:0          |               |                 | —           | —                             | _                             |                             | SRIPL<2:0>         | •                | —                     | —                     |                       |                         | VEC        | <5:0>  |                |        | 0000       |

| 1020                        | IPTMR                           | 31:16<br>15:0 |               |                 |             |                               |                               |                             |                    | IPTMR            | <31:0>                |                       |                       |                         |            |        |                |        | 0000       |

| 1030                        | IFS0                            | 31:16         | I2C1MIF       | I2C1SIF         | I2C1BIF     | U1TXIF<br>SPI3TXIF<br>I2C3MIF | U1RXIF<br>SPI3RXIF<br>I2C3SIF | U1EIF<br>SPI3EIF<br>I2C3BIF | SPI1TXIF           | SPI1RXIF         | SPI1EIF               | OC5IF                 | IC5IF                 | T5IF                    | INT4IF     | OC4IF  | IC4IF          | T4IF   | 0000       |

|                             |                                 | 15:0          | INT3IF        | OC3IF           | IC3IF       | T3IF                          | INT2IF                        | OC2IF                       | IC2IF              | T2IF             | INT1IF                | OC1IF                 | IC1IF                 | T1IF                    | INTOIF     | CS1IF  | CS0IF          | CTIF   | 0000       |

|                             |                                 | 31:16         | IC3EIF        | IC2EIF          | IC1EIF      | ETHIF                         | —                             | _                           | USBIF              | FCEIF            | DMA7IF <sup>(2)</sup> | DMA6IF <sup>(2)</sup> | DMA5IF <sup>(2)</sup> | DMA4IF <sup>(2)</sup>   | DMA3IF     | DMA2IF | DMA1IF         | DMA0IF | 0000       |

| 1040                        | IFS1                            | 15:0          | RTCCIF        | FSCMIF          | I2C2MIF     | I2C2SIF                       | I2C2BIF                       | U2TXIF<br>SPI4TXIF          | U2RXIF<br>SPI4RXIF | U2EIF<br>SPI4EIF | U3TXIF<br>SPI2TXIF    | U3RXIF<br>SPI2RXIF    | U3EIF<br>SPI2EIF      | CMP2IF                  | CMP1IF     | PMPIF  | AD1IF          | CNIF   | 0000       |

|                             |                                 |               |               |                 |             |                               |                               | I2C5MIF                     | I2C5SIF            | I2C5BIF          | I2C4MIF               | I2C4SIF               | I2C4BIF               |                         |            |        |                |        |            |

| 1050                        | IFS2                            | 31:16         | _             |                 | _           | _                             |                               | —                           | _                  | —                | —                     | _                     | _                     | —                       | —          | —      | _              | —      | 0000       |

|                             |                                 | 15:0          | _             | _               | _           | -                             | U5TXIF                        | U5RXIF                      | U5EIF              | U6TXIF           | U6RXIF                | U6EIF                 | U4TXIF                | U4RXIF                  | U4EIF      | PMPEIF | IC5EIF         | IC4EIF | 0000       |

| 1060                        | IEC0                            | 31:16         | I2C1MIE       | I2C1SIE         | I2C1BIE     | U1TXIE<br>SPI3TXIE<br>I2C3MIE | U1RXIE<br>SPI3RXIE<br>I2C3SIE | U1EIE<br>SPI3EIE<br>I2C3BIE | SPI1TXIE           | SPI1RXIE         | SPI1EIE               | OC5IE                 | IC5IE                 | T5IE                    | INT4IE     | OC4IE  | IC4IE          | T4IE   | 0000       |

|                             |                                 | 15:0          | INT3IE        | OC3IE           | IC3IE       | T3IE                          | INT2IE                        | OC2IE                       | IC2IE              | T2IE             | INT1IE                | OC1IE                 | IC1IE                 | T1IE                    | INT0IE     | CS1IE  | CS0IE          | CTIE   | 0000       |

|                             |                                 | 31:16         | <b>IC3EIE</b> | IC2EIE          | IC1EIE      | ETHIE                         | _                             | -                           | USBIE              | FCEIE            | DMA7IE <sup>(2)</sup> | DMA6IE <sup>(2)</sup> | DMA5IE <sup>(2)</sup> | DMA4IE <sup>(2)</sup>   | DMA3IE     | DMA2IE | DMA1IE         | DMA0IE | 0000       |

| 1070                        | IEC1                            | 15:0          | RTCCIE        | FSCMIE          | I2C2MIE     | I2C2SIE                       | I2C2BIE                       | U2TXIE<br>SPI4TXIE          | U2RXIE<br>SPI4RXIE | U2EIE<br>SPI4EIE | U3TXIE<br>SPI2TXIE    | U3RXIE<br>SPI2RXIE    | U3EIE<br>SPI2EIE      | CMP2IE                  | CMP1IE     | PMPIE  | AD1IE          | CNIE   | 0000       |

|                             |                                 |               |               |                 |             |                               |                               | I2C5MIE                     | I2C5SIE            | I2C5BIE          | I2C4MIE               | I2C4SIE               | I2C4BIE               |                         |            |        |                |        |            |

| 1080                        | IEC2                            | 31:16         | —             | _               | —           | —                             | —                             | -                           | —                  | —                | —                     | —                     | —                     | —                       | —          | —      | —              | —      | 0000       |

| 1000                        | 1202                            | 15:0          | —             |                 | —           | —                             | U5TXIE                        | U5RXIE                      | U5EIE              | U6TXIE           | U6RXIE                | U6EIE                 | U4TXIE                | U4RXIE                  | U4EIE      | PMPEIE | IC5EIE         | IC4EIE | 0000       |

| 1090                        | IPC0                            | 31:16         | -             | _               |             |                               | INT0IP<2:0>                   |                             |                    | S<1:0>           |                       |                       | _                     |                         | CS1IP<2:0> |        | CS1IS          |        | 0000       |

|                             |                                 | 15:0          | —             | —               | —           |                               | CS0IP<2:0>                    |                             |                    | S<1:0>           | —                     | —                     | —                     |                         | CTIP<2:0>  |        | CTIS           |        | 0000       |

| 10A0                        | IPC1                            | 31:16         | _             |                 | _           |                               | INT1IP<2:0>                   |                             |                    | S<1:0>           | _                     | _                     | _                     |                         | OC1IP<2:0> | •      | OC1IS          |        | 0000       |

|                             |                                 | 15:0          | _             | _               | _           |                               | IC1IP<2:0>                    |                             |                    | <1:0>            | _                     | _                     | _                     |                         | T1IP<2:0>  |        | T1IS-          |        | 0000       |

| 10B0                        | IPC2                            | 31:16         | _             | _               | —           |                               | INT2IP<2:0>                   |                             |                    | S<1:0>           | —                     | _                     | _                     | OC2IP<2:0>              |            | •      | OC2IS          |        | 0000       |

|                             |                                 | 15:0          | _             |                 |             |                               | IC2IP<2:0><br>INT3IP<2:0>     |                             |                    | <1:0><br>S<1:0>  |                       |                       |                       |                         | T2IP<2:0>  |        | T2IS-<br>OC3IS | -      | 0000       |

| 10C0                        | IPC3                            | 31:16<br>15:0 | _             |                 |             |                               | IC3IP<2:0>                    |                             |                    | <1:0>            |                       |                       |                       | OC3IP<2:0><br>T3IP<2:0> |            | T3IS-  |                | 0000   |            |

| Legend                      | d: x=                           |               | n value on F  | Reset; — = u    | Inimplement | ed, read as '                 |                               | ues are sho                 |                    |                  | I                     | I                     |                       | 1                       | .011 \2.02 |        | 1010           |        | 0000       |

#### **TABLE 7-6:** INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND

Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Note 1: Registers" for more information.

These bits are not available on PIC32MX664 devices. 2:

This register does note have associated CLR, SET, and INV registers. 3:

## TABLE 7-6: INTERRUPT REGISTER MAP FOR PIC32MX664F064L, PIC32MX664F128L, PIC32MX675F256L, PIC32MX675F512L AND PIC32MX695F512L DEVICES (CONTINUED)

| ess                         |                                 |           |       |       |       |             |                            |             |             | Bi                    | its   |             |       |             |             |             |             |                      |            |            |        |            |             |            |        |        |      |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------------|----------------------------|-------------|-------------|-----------------------|-------|-------------|-------|-------------|-------------|-------------|-------------|----------------------|------------|------------|--------|------------|-------------|------------|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12       | 27/11                      | 26/10       | 25/9        | 24/8                  | 23/7  | 22/6        | 21/5  | 20/4        | 19/3        | 18/2        | 17/1        | 16/0                 | All Resets |            |        |            |             |            |        |        |      |

| 10D0                        | IPC4                            | 31:16     | _     | —     | -     |             | INT4IP<2:0>                |             | INT4IS      | S<1:0>                | _     | —           | -     |             | OC4IP<2:0>  |             | OC4IS       | 6<1:0>               | 0000       |            |        |            |             |            |        |        |      |

| 1000                        | IPC4                            | 15:0      | _     | _     | _     |             | IC4IP<2:0>                 |             | IC4IS       | <1:0>                 | _     | _           | _     |             | T4IP<2:0>   |             | T4IS-       | <1:0>                | 0000       |            |        |            |             |            |        |        |      |

| 4050                        | IPC5                            | 31:16     | —     | _     | _     |             | SPI1IP<2:0>                |             | SPI1IS      | 6<1:0>                | _     | _           | _     |             | OC5IP<2:0>  |             | OC5IS       | S<1:0>               | 0000       |            |        |            |             |            |        |        |      |

| 10E0                        | IPC5                            | 15:0      | _     | _     | _     |             | IC5IP<2:0>                 |             | IC5IS       | <1:0>                 | -     |             | _     |             | T5IP<2:0>   |             | T5IS-       | <1:0>                | 0000       |            |        |            |             |            |        |        |      |

|                             |                                 | 31:16     | _     | _     | _     |             | AD1IP<2:0>                 |             | AD1IS       | S<1:0>                | _     | _           | _     |             | CNIP<2:0>   |             | CNIS        | <1:0>                | 0000       |            |        |            |             |            |        |        |      |

| 10F0                        | IPC6                            |           |       |       |       |             |                            |             |             |                       |       |             |       | U1IP<2:0>   |             | U1IS-       | <1:0>       |                      |            |            |        |            |             |            |        |        |      |

| IUFU                        | IFCO                            | 15:0      | —     | —     | —     | I2C1IP<2:0> |                            | I2C1IS<1:0> |             | I2C1IS<1:0>           |       | I2C1IS<1:0> |       | —           | —           | —           |             | SPI3IP<2:0>          | •          | SPI3IS     | S<1:0> | 0000       |             |            |        |        |      |

|                             |                                 |           |       |       |       |             |                            |             |             |                       |       |             |       | I2C3IP<2:0> |             | 12C315      | I2C3IS<1:0> |                      |            |            |        |            |             |            |        |        |      |

|                             |                                 |           |       |       |       |             | U3IP<2:0>                  |             | U3IS<1:0>   |                       |       |             |       |             |             |             | CMP2IS<1:0> |                      |            |            |        |            |             |            |        |        |      |

| 1100                        | IPC7                            | 31:16     | —     | —     | —     |             | SPI2IP<2:0>                |             | SPI2IS      | S<1:0>                | —     | —           | —     | (           | CMP2IP<2:0  | >           |             |                      | 0000       |            |        |            |             |            |        |        |      |

| 1100                        | 11 07                           |           |       |       |       |             | I2C4IP<2:0>                |             | I2C4IS<1:0> |                       |       |             |       |             |             |             |             |                      |            |            |        |            |             |            |        |        |      |

|                             |                                 | 15:0      | _     |       |       | CMP1IP<2:0> |                            |             |             | S<1:0>                | _     | _           |       |             | PMPIP<2:0>  |             | PMPIS       | S<1:0>               | 0000       |            |        |            |             |            |        |        |      |

|                             |                                 | 31:16     | _     |       |       | F           | RTCCIP<2:0>                |             | RTCCIS<1:0> |                       | _     | _           |       | FSCMIP<2:0> |             | FSCMI       | S<1:0>      | 0000                 |            |            |        |            |             |            |        |        |      |

| 1110                        | IPC8                            |           |       |       |       |             |                            |             |             |                       |       |             |       |             |             |             |             |                      |            |            |        |            | U2IP<2:0>   |            | U2IS-  | <1:0>  |      |

| 1110                        | 11 00                           | 15:0      | —     | —     | —     |             | I2C2IP<2:0>                |             | 12C215      | I2C2IS<1:0>           |       | I2C2IS<1:0> |       | I2C2IS<1:0> |             | I2C2IS<1:0> |             | I2C2IS<1:0>          |            | —          | —      |            | SPI4IP<2:0> |            | SPI4IS | S<1:0> | 0000 |

|                             |                                 |           |       |       |       |             |                            |             |             |                       |       |             |       |             | I2C5IP<2:0> |             | 12C515      | S<1:0>               |            |            |        |            |             |            |        |        |      |

| 1120                        | IPC9                            | 31:16     | _     | _     |       |             | DMA3IP<2:0                 |             | DMA3I       | S<1:0>                | _     |             |       |             | DMA2IP<2:0  |             | DMA2I       | S<1:0>               | 0000       |            |        |            |             |            |        |        |      |

| 1120                        | 11 03                           | 15:0      | _     | _     |       |             | DMA1IP<2:0                 |             | DMA1I       |                       | _     |             |       |             | DMA0IP<2:0  |             | DMA0I       | S<1:0>               | 0000       |            |        |            |             |            |        |        |      |

| 1130                        | IPC10                           | 31:16     | —     | —     | —     | DI          | DMA7IP<2:0> <sup>(2)</sup> |             | DMA7IS      | i<1:0> <sup>(2)</sup> | —     | _           | —     | D           | MA6IP<2:0>  | (2)         | DMA6IS      | <1:0> <sup>(2)</sup> | 0000       |            |        |            |             |            |        |        |      |

| 1130                        | 11 010                          | 15:0      | —     | —     | —     | DI          | MA5IP<2:0>                 | (2)         | DMA5IS      | i<1:0> <sup>(2)</sup> | _     | _           | —     | D           | MA4IP<2:0>  | (2)         | DMA4IS      | <1:0> <sup>(2)</sup> | 0000       |            |        |            |             |            |        |        |      |

| 1140                        | IPC11                           | 31:16     | —     | -     | _     | _           |                            |             | _           |                       |       |             | _     |             |             | —           |             | 0000                 |            |            |        |            |             |            |        |        |      |

| 1140                        | IFCII                           | 15:0      | —     | —     | —     |             | USBIP<2:0>                 |             | USBIP<2:0>  |                       | USBIS | S<1:0>      | _     | _           | —           | FCEIP<2:0>  |             | FCEIP<2:0>           |            | FCEIP<2:0> |        | FCEIP<2:0> |             | FCEIS<1:0> |        | 0000   |      |

| 1150                        | IPC12                           | 31:16     | _     | _     | -     |             | U5IP<2:0>                  |             | U5IS-       | <1:0>                 | _     |             | -     | U6IP<2:0>   |             | U6IS-       | <1:0>       | 0000                 |            |            |        |            |             |            |        |        |      |

| 1150                        | IFUIZ                           | 15:0      | _     | -     | -     |             | U4IP<2:0>                  |             |             |                       |       |             | U4IS- | <1:0>       |             |             |             |                      | ETHIP<2:0> |            | ETHIS  | i<1:0>     | 0000        |            |        |        |      |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Except where noted, all registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

2: These bits are not available on PIC32MX664 devices.

3: This register does note have associated CLR, SET, and INV registers.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                       | _                 | _                 | _                | —                |  |  |  |

| 22:46        | U-0               | R-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                       | _                 | _                 | —                | —                |  |  |  |

| 45.0         | U-0               | R-0               | U-0               | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | —                 | —                 | _                       | _                 | _                 | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | —                 | —                 |                   | TUN<5:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |

#### REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

## Legend:

| J. J.             |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

| bit 5-0 | <b>TUN&lt;5:0&gt;:</b> FRC Oscillator Tuning bits <sup>(1)</sup><br>100000 = Center frequency -12.5% for PIC32MX575/595/675/695/775/795 devices<br>100000 = Center frequency -1.5% for PIC32MX534/564/664/764 devices<br>100001 = |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 111111 =<br>000000 = Center frequency; Oscillator runs at nominal frequency (8 MHz)<br>000001 =                                                                                                                                   |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 011110 =<br>011111 = Center frequency +12.5% for PIC32MX575/595/675/695/775/795 devices<br>011111 = Center frequency +1.5% for PIC32MX534/564/664/764 devices                                                                     |

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

| Note: | Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the |

|-------|----------------------------------------------------------------------------------------------------------|

|       | "PIC32 Family Reference Manual" for details.                                                             |

### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

- bit 5 **CHDDIF:** Channel Destination Done Interrupt Flag bit

- 1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

- 0 = No interrupt is pending

- bit 4 CHDHIF: Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

0 = No interrupt is pending

#### bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

#### bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

#### bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected (either the source or the destination address is invalid)

- 0 = No interrupt is pending

#### I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED) REGISTER 19-2: **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave) bit 5 This bit is cleared by hardware upon a device address match, and is set by hardware by reception of the slave byte. 1 = Indicates that the last byte received was data 0 = Indicates that the last byte received was device address bit 4 P: Stop bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Stop bit has been detected last 0 = Stop bit was not detected last bit 3 S: Start bit This bit is set or cleared by hardware when a Start, Repeated Start, or Stop condition is detected. 1 = Indicates that a Start (or Repeated Start) bit has been detected last 0 = Start bit was not detected last **R\_W:** Read/Write Information bit (when operating as I<sup>2</sup>C slave) bit 2 This bit is set or cleared by hardware after reception of an I<sup>2</sup>C device address byte. 1 = Read – indicates data transfer is output from slave 0 = Write - indicates data transfer is input to slave **RBF:** Receive Buffer Full Status bit bit 1 This bit is set by hardware when the I2CxRCV register is written with a received byte, and is cleared by hardware when software reads I2CxRCV. 1 = Receive complete, I2CxRCV is full 0 = Receive not complete, I2CxRCV is empty bit 0 TBF: Transmit Buffer Full Status bit This bit is set by hardware when software writes to the I2CxTRN register, and is cleared by hardware upon completion of data transmission.

1 = Transmit in progress, I2CxTRN is full

0 = Transmit complete, I2CxTRN is empty

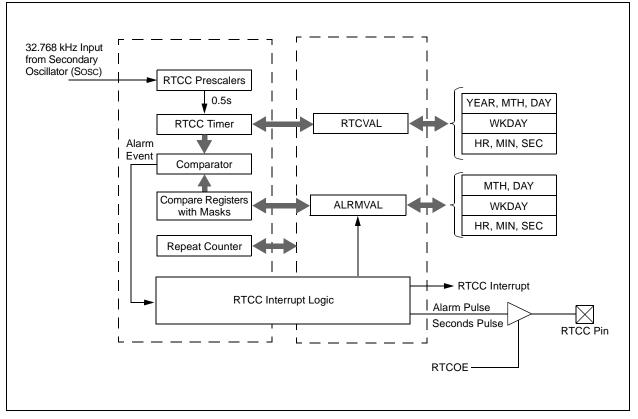

## 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. A simplified block diagram of the RTCC module is illustrated in Figure 22-1. Key features of the RTCC module include:

- Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- Alarm repeat with decrementing counter

- Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

#### FIGURE 22-1: RTCC BLOCK DIAGRAM

### REGISTER 24-1: CICON: CAN MODULE CONTROL REGISTER (CONTINUED)

bit 13 **SIDLE:** CAN Stop in Idle bit 1 = CAN Stops operation when system enters Idle mode 0 = CAN continues operation when system enters Idle mode

## bit 12 Unimplemented: Read as '0'

- bit 11 CANBUSY: CAN Module is Busy bit

- 1 = The CAN module is active

- 0 = The CAN module is completely disabled

- bit 10-5 Unimplemented: Read as '0'

#### bit 4-0 **DNCNT<4:0>:** Device Net Filter Bit Number bits

10011-11111 = Invalid Selection (compare up to 18-bits of data with EID)

- 10010 = Compare up to data byte 2 bit 6 with EID17 (CiRXFn<17>)

- •

- •

- •

00001 = Compare up to data byte 0 bit 7 with EID0 (CiRXFn<0>) 00000 = Do not compare data bytes

**Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

### REGISTER 24-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1 (CONTINUED)

| bit 15    | FLTEN5: Filter 17 Enable bit                                                                           |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | 0 = Filter is disabled                                                                                 |

| bit 14-13 | MSEL5<1:0>: Filter 5 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 12-8  | FSEL5<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| bit 7     | FLTEN4: Filter 4 Enable bit                                                                            |

|           | <ul><li>1 = Filter is enabled</li><li>0 = Filter is disabled</li></ul>                                 |

| bit 6-5   | MSEL4<1:0>: Filter 4 Mask Select bits                                                                  |

|           | 11 = Acceptance Mask 3 selected                                                                        |

|           | 10 = Acceptance Mask 2 selected                                                                        |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                     |

| bit 4-0   | FSEL4<4:0>: FIFO Selection bits                                                                        |

|           | 11111 = Message matching filter is stored in FIFO buffer 31                                            |

|           | 11110 = Message matching filter is stored in FIFO buffer 30                                            |

|           | •                                                                                                      |

|           | •                                                                                                      |

|           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

|           | 00000 = Message matching filter is stored in FIFO buffer 0                                             |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'. |

|              |                   |                   |                   |                   |                   |                   |                  | ,                |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31.24        |                   |                   |                   | SID<              | 10:3>             |                   |                  |                  |  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |  |  |  |

| 23.10        | 23:16             |                   |                   | —                 | EXID              | _                 | EID<1            | 7:16>            |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   |                   |                   | EID<              | 15:8>             |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | EID<7:0>          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 24-18: CIRXFn: CAN ACCEPTANCE FILTER 'n' REGISTER 7 (n = 0 THROUGH 31)

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | -                 |                   |                   | —                 |                   | -                 |                  | _                |

| 23:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10     | -                 |                   |                   | —                 |                   | -                 |                  | _                |

| 15:8      | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0      | _                 | _                 | _                 | —                 | _                 | R                 | XBUFSZ<6:        | 4>               |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0              | U-0              |

|           |                   | RXBUFS            | SZ<3:0>           |                   |                   | _                 | _                | _                |

### REGISTER 25-2: ETHCON2: ETHERNET CONTROLLER CONTROL REGISTER 2

## Legend:

| Logona.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-11 Unimplemented: Read as '0'

bit 10-4 RXBUFSZ<6:0>: RX Data Buffer Size for All RX Descriptors (in 16-byte increments) bits

111111 = RX data Buffer size for descriptors is 2032 bytes

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

.

Note 1: This register is only used for RX operations.

2: The bits in this register may only be changed while the RXEN bit (ETHCON1<8>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|-------------------------|

| 31:24        | U-0                      | U-0                     |

|              | —                 | —                 | —                 | —                 | —                 | -                 | —                        | —                       |

| 23:16        | U-0                      | U-0                     |

|              | —                 | —                 | —                 | —                 | —                 | -                 | —                        | _                       |

| 15:8         | U-0                      | U-0                     |

| 15:8         | —                 | —                 | —                 | —                 | —                 | -                 | —                        | —                       |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0                   |

|              |                   | —                 | _                 | _                 | _                 | TESTBP            | TESTPAUSE <sup>(1)</sup> | SHRTQNTA <sup>(1)</sup> |

### REGISTER 25-30: EMAC1TEST: ETHERNET CONTROLLER MAC TEST REGISTER

#### Legend:

| Logonan           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 TESTBP: Test Backpressure bit

- 1 = The MAC will assert backpressure on the link. Backpressure causes preamble to be transmitted, raising carrier sense. A transmit packet from the system will be sent during backpressure.

0 = Normal operation

#### bit 1 **TESTPAUSE:** Test PAUSE bit<sup>(1)</sup>

- 1 = The MAC Control sub-layer will inhibit transmissions, just as if a PAUSE Receive Control frame with a non-zero pause time parameter was received

- 0 = Normal operation

### bit 0 SHRTQNTA: Shortcut PAUSE Quanta bit<sup>(1)</sup>

- 1 = The MAC reduces the effective PAUSE Quanta from 64 byte-times to 1 byte-time

- 0 = Normal operation

- **Note 1:** This bit is only for testing purposes.

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

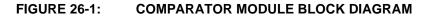

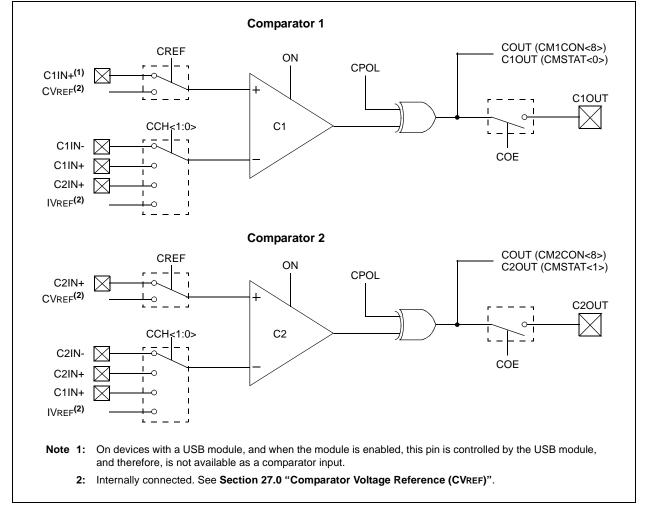

## 26.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 19.** "Comparator" (DS60001110) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Comparator module contains two comparators that can be configured in a variety of ways.

Key features of the Comparator module include:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be inverted

- Selectable interrupt generation

A block diagram of the Comparator module is illustrated in Figure 26-1.

### REGISTER 29-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

| DC CHARACTERISTICS |                                                                                                                            |                                                                                                                       | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated) |      |      |                          |                                                                                         |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------|------|--------------------------|-----------------------------------------------------------------------------------------|--|

|                    |                                                                                                                            |                                                                                                                       |                                                                          |      |      |                          | -40°C $\leq$ TA $\leq$ +85°C for Industrial<br>-40°C $\leq$ TA $\leq$ +105°C for V-temp |  |

| Param.             | Symbol                                                                                                                     | Characteristic                                                                                                        | Min.                                                                     | Тур. | Max. | Units                    | Conditions                                                                              |  |

| DO10               | Vol                                                                                                                        | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - All I/O<br>output pins not defined as 8x<br>Sink Driver pins | _                                                                        | _    | 0.4  | V                        | $\text{IOL} \leq 10 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                             |  |