Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 80MHz                                                                             |

| Connectivity               | CANbus, I <sup>2</sup> C, SPI, UART/USART, USB OTG                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 16x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx575f512lt-80v-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 8: PIN NAMES FOR 100-PIN USB AND ETHERNET DEVICES

## **100-PIN TQFP (TOP VIEW)**

#### PIC32MX664F064L PIC32MX664F128L PIC32MX675F256L PIC32MX675F512L PIC32MX695F512L

100

| Pin # | Full Pin Name                                                |

|-------|--------------------------------------------------------------|

| 1     | AERXERR/RG15                                                 |

| 2     | VDD                                                          |

| 3     | PMD5/RE5                                                     |

| 4     | PMD6/RE6                                                     |

| 5     | PMD7/RE7                                                     |

| 6     | T2CK/RC1                                                     |

| 7     | T3CK/RC2                                                     |

| 8     | T4CK/RC3                                                     |

| 9     | T5CK/SDI1/RC4                                                |

| 10    | ECOL/SCK2/U6TX/U3RTS/PMA5/CN8/RG6                            |

| 11    | ECRS/SDA4/SDI2/U3RX/PMA4/CN9/RG7                             |

| 12    | ERXDV/AERXDV/ECRSDV/AECRSDV/SCL4/SDO2/U3TX/PMA3/CN10/RG8     |

| 13    | MCLR                                                         |

| 14    | ERXCLK/AERXCLK/EREFCLK/AEREFCLK/SS2/U6RX/U3CTS/PMA2/CN11/RG9 |

| 15    | Vss                                                          |

| 16    | VDD                                                          |

| 17    | TMS/RA0                                                      |

| 18    | AERXD0/INT1/RE8                                              |

| 19    | AERXD1/INT2/RE9                                              |

| 20    | AN5/C1IN+/VBUSON/CN7/RB5                                     |

| 21    | AN4/C1IN-/CN6/RB4                                            |

| 22    | AN3/C2IN+/CN5/RB3                                            |

| 23    | AN2/C2IN-/CN4/RB2                                            |

| 24    | PGEC1/AN1/CN3/RB1                                            |

| 25    | PGED1/AN0/CN2/RB0                                            |

| 26    | PGEC2/AN6/OCFA/RB6                                           |

| 27    | PGED2/AN7/RB7                                                |

| 28    | Vref-/CVref-/AERXD2/PMA7/RA9                                 |

| 29    | VREF+/CVREF+/AERXD3/PMA6/RA10                                |

| 30    | AVdd                                                         |

| 31    | AVss                                                         |

| 32    | AN8/C1OUT/RB8                                                |

| 33    | AN9/C2OUT/RB9                                                |

| 34    | AN10/CVREFOUT/PMA13/RB10                                     |

| 35    | AN11/ERXERR/AETXERR/PMA12/RB11                               |

| Pin # | Full Pin Name                               |

|-------|---------------------------------------------|

| 36    | Vss                                         |

| 37    | VDD                                         |

| 38    | TCK/RA1                                     |

| 39    | SCK4/U5TX/U2RTS/RF13                        |

| 40    | SS4/U5RX/U2CTS/RF12                         |

| 41    | AN12/ERXD0/AECRS/PMA11/RB12                 |

| 42    | AN13/ERXD1/AECOL/PMA10/RB13                 |

| 43    | AN14/ERXD2/AETXD3/PMALH/PMA1/RB14           |

| 44    | AN15/ERXD3/AETXD2/OCFB/PMALL/PMA0/CN12/RB15 |

| 45    | Vss                                         |

| 46    | Vdd                                         |

| 47    | AETXD0/SS3/U4RX/U1CTS/CN20/RD14             |

| 48    | AETXD1/SCK3/U4TX/U1RTS/CN21/RD15            |

| 49    | SDA5/SDI4/U2RX/PMA9/CN17/RF4                |

| 50    | SCL5/SDO4/U2TX/PMA8/CN18/RF5                |

| 51    | USBID/RF3                                   |

| 52    | SDA3/SDI3/U1RX/RF2                          |

| 53    | SCL3/SDO3/U1TX/RF8                          |

| 54    | VBUS                                        |

| 55    | VUSB3V3                                     |

| 56    | D-/RG3                                      |

| 57    | D+/RG2                                      |

| 58    | SCL2/RA2                                    |

| 59    | SDA2/RA3                                    |

| 60    | TDI/RA4                                     |

| 61    | TDO/RA5                                     |

| 62    | Vdd                                         |

| 63    | OSC1/CLKI/RC12                              |

| 64    | OSC2/CLKO/RC15                              |

| 65    | Vss                                         |

| 66    | AETXCLK/SCL1/INT3/RA14                      |

| 67    | AETXEN/SDA1/INT4/RA15                       |

| 68    | RTCC/EMDIO/AEMDIO/IC1/RD8                   |

| 69    | SS1/IC2/RD9                                 |

| 70    | SCK1/IC3/PMCS2/PMA15/RD10                   |

1

Note 1: Shaded pins are 5V tolerant.

# PIC32MX5XX/6XX/7XX

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                                               | nber <sup>(1)</sup> |                  | D:              | Duffer      |                      |                                                   |

|----------|-----------------------------------------------|---------------------|------------------|-----------------|-------------|----------------------|---------------------------------------------------|

| Pin Name | 64-Pin<br>QFN/TQFP                            | 100-Pin<br>TQFP     | 121-Pin<br>TFBGA | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type       | Description                                       |

| RG0      | —                                             | 90                  | A5               | A61             | I/O         | ST                   | PORTG is a bidirectional I/O port                 |

| RG1      | —                                             | 89                  | E6               | B50             | I/O         | ST                   |                                                   |

| RG6      | 4                                             | 10                  | E3               | A7              | I/O         | ST                   |                                                   |

| RG7      | 5                                             | 11                  | F4               | B6              | I/O         | ST                   |                                                   |

| RG8      | 6                                             | 12                  | F2               | A8              | I/O         | ST                   |                                                   |

| RG9      | 8                                             | 14                  | F3               | A9              | I/O         | ST                   |                                                   |

| RG12     | —                                             | 96                  | C3               | A65             | I/O         | ST                   |                                                   |

| RG13     | —                                             | 97                  | A3               | B55             | I/O         | ST                   | -                                                 |

| RG14     | —                                             | 95                  | C4               | B54             | I/O         | ST                   |                                                   |

| RG15     | —                                             | 1                   | B2               | A2              | I/O         | ST                   |                                                   |

| RG2      | 37                                            | 57                  | H10              | B31             | Ι           | ST                   | PORTG input pins                                  |

| RG3      | 36                                            | 56                  | J11              | A38             | I           | ST                   |                                                   |

| T1CK     | 48                                            | 74                  | B11              | B40             |             | ST                   | Timer1 external clock input                       |

| T2CK     | —                                             | 6                   | D1               | A5              | I           | ST                   | Timer2 external clock input                       |

| T3CK     | —                                             | 7                   | E4               | B4              |             | ST                   | Timer3 external clock input                       |

| T4CK     | —                                             | 8                   | E2               | A6              |             | ST                   | Timer4 external clock input                       |

| T5CK     | —                                             | 9                   | E1               | B5              |             | ST                   | Timer5 external clock input                       |

| U1CTS    | 43                                            | 47                  | L9               | B26             |             | ST                   | UART1 clear to send                               |

| U1RTS    | 49                                            | 48                  | K9               | A31             | 0           |                      | UART1 ready to send                               |

| U1RX     | 50                                            | 52                  | K11              | A36             | I           | ST                   | UART1 receive                                     |

| U1TX     | 51                                            | 53                  | J10              | B29             | 0           | _                    | UART1 transmit                                    |

| U3CTS    | 8                                             | 14                  | F3               | A9              | I           | ST                   | UART3 clear to send                               |

| U3RTS    | 4                                             | 10                  | E3               | A7              | 0           | _                    | UART3 ready to send                               |

| U3RX     | 5                                             | 11                  | F4               | B6              | I           | ST                   | UART3 receive                                     |

| U3TX     | 6                                             | 12                  | F2               | A8              | 0           | _                    | UART3 transmit                                    |

| U2CTS    | 21                                            | 40                  | K6               | A27             | I           | ST                   | UART2 clear to send                               |

| U2RTS    | 29                                            | 39                  | L6               | B22             | 0           |                      | UART2 ready to send                               |

| U2RX     | 31                                            | 49                  | L10              | B27             | I           | ST                   | UART2 receive                                     |

| U2TX     | 32                                            | 50                  | L11              | A32             | 0           |                      | UART2 transmit                                    |

| U4RX     | 43                                            | 47                  | L9               | B26             | 1           | ST                   | UART4 receive                                     |

| U4TX     | 49                                            | 48                  | K9               | A31             | 0           | _                    | UART4 transmit                                    |

| U6RX     | 8                                             | 14                  | F3               | A9              | I           | ST                   | UART6 receive                                     |

| U6TX     | 4                                             | 10                  | E3               | A7              | 0           | _                    | UART6 transmit                                    |

| U5RX     | 21                                            | 40                  | K6               | A27             | I           | ST                   | UART5 receive                                     |

| U5TX     | 29                                            | 39                  | L6               | B22             | 0           |                      | UART5 transmit                                    |

| SCK1     | _                                             | 70                  | D11              | B38             | I/O         | ST                   | Synchronous serial clock input/output<br>for SPI1 |

| 5        | CMOS = CMO<br>ST = Schmitt T<br>TL = TTL inpu | rigger input        |                  |                 |             | nalog = A<br>= Outpu | Analog input P = Power                            |

Note 1: Pin numbers are only provided for reference. See the "Device Pin Tables" section for device pin availability.

2: See 25.0 "Ethernet Controller" for more information.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32 architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

## 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e, is also available by accessing the CP0 registers, listed in Table 3-2.

| Register<br>Number | Register<br>Name        | Function                                                                 |

|--------------------|-------------------------|--------------------------------------------------------------------------|

| 0-6                | Reserved                | Reserved.                                                                |

| 7                  | HWREna                  | Enables access via the RDHWR instruction to selected hardware registers. |

| 8                  | BadVAddr <sup>(1)</sup> | Reports the address for the most recent address-related exception.       |

| 9                  | Count <sup>(1)</sup>    | Processor cycle count.                                                   |

| 10                 | Reserved                | Reserved.                                                                |

| 11                 | Compare <sup>(1)</sup>  | Timer interrupt control.                                                 |

| 12                 | Status <sup>(1)</sup>   | Processor status and control.                                            |

| 12                 | IntCtl <sup>(1)</sup>   | Interrupt system status and control.                                     |

| 12                 | SRSCtl <sup>(1)</sup>   | Shadow register set status and control.                                  |

| 12                 | SRSMap <sup>(1)</sup>   | Provides mapping from vectored interrupt to a shadow set.                |

| 13                 | Cause <sup>(1)</sup>    | Cause of last general exception.                                         |

| 14                 | EPC <sup>(1)</sup>      | Program counter at last exception.                                       |

| 15                 | PRId                    | Processor identification and revision.                                   |

| 15                 | Ebase                   | Exception vector base register.                                          |

| 16                 | Config                  | Configuration register.                                                  |

| 16                 | Config1                 | Configuration Register 1.                                                |

| 16                 | Config2                 | Configuration Register 2.                                                |

| 16                 | Config3                 | Configuration Register 3.                                                |

| 17-22              | Reserved                | Reserved.                                                                |

| 23                 | Debug <sup>(2)</sup>    | Debug control and exception status.                                      |

| 24                 | DEPC <sup>(2)</sup>     | Program counter at last debug exception.                                 |

| 25-29              | Reserved                | Reserved.                                                                |

| 30                 | ErrorEPC <sup>(1)</sup> | Program counter at last error.                                           |

| 31                 | DESAVE <sup>(2)</sup>   | Debug handler scratchpad register.                                       |

|                    | <b>I</b>                |                                                                          |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

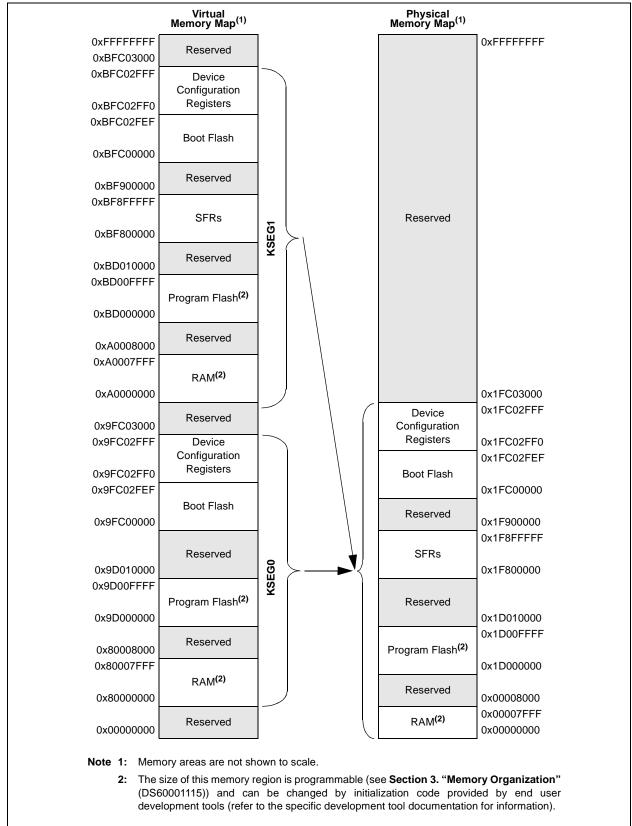

# FIGURE 4-1: MEMORY MAP ON RESET FOR PIC32MX564F064H, PIC32MX564F064L, PIC32MX664F064H AND PIC32MX664F064L DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | NVMDATA<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | NVMD/             | ATA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

| Legend:           |                                 |                      |                    |

|-------------------|---------------------------------|----------------------|--------------------|

| R = Readable bit  | = Readable bit W = Writable bit |                      | ad as '0'          |

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

**Note:** The bits in this register are only reset by a Power-on Reset (POR).

## REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | >                 |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | NVMSRCADDR<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                              |                      |                    |

|-------------------|------------------------------|----------------------|--------------------|

| R = Readable bit  | eadable bit W = Writable bit |                      | ad as '0'          |

| -n = Value at POR | '1' = Bit is set             | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

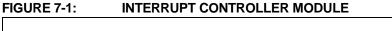

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 8. "Interrupts"** (DS60001108) in the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32).

PIC32MX5XX/6XX/7XX devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The Interrupt Controller module includes the following features:

- Up to 96 interrupt sources

- Up to 64 interrupt vectors

- Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable sub-priority levels within each priority

- Dedicated shadow set for user-selectable priority level

- Software can generate any interrupt

- User-configurable interrupt vector table location

- · User-configurable interrupt vector spacing

A simplified block diagram of the Interrupt Controller module is illustrated in Figure 7-1.

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Interment Course(1)              | IRQ    | Vector      |               | Interrupt Bit Location |             |              |  |  |

|----------------------------------|--------|-------------|---------------|------------------------|-------------|--------------|--|--|

| Interrupt Source <sup>(1)</sup>  | Number | Number      | Flag          | Enable                 | Priority    | Sub-Priority |  |  |

|                                  | Highe  | est Natural | Order Priorit | y                      |             |              |  |  |

| CT – Core Timer Interrupt        | 0      | 0           | IFS0<0>       | IEC0<0>                | IPC0<4:2>   | IPC0<1:0>    |  |  |

| CS0 – Core Software Interrupt 0  | 1      | 1           | IFS0<1>       | IEC0<1>                | IPC0<12:10> | IPC0<9:8>    |  |  |

| CS1 – Core Software Interrupt 1  | 2      | 2           | IFS0<2>       | IEC0<2>                | IPC0<20:18> | IPC0<17:16>  |  |  |

| INT0 – External Interrupt 0      | 3      | 3           | IFS0<3>       | IEC0<3>                | IPC0<28:26> | IPC0<25:24>  |  |  |

| T1 – Timer1                      | 4      | 4           | IFS0<4>       | IEC0<4>                | IPC1<4:2>   | IPC1<1:0>    |  |  |

| IC1 – Input Capture 1            | 5      | 5           | IFS0<5>       | IEC0<5>                | IPC1<12:10> | IPC1<9:8>    |  |  |

| OC1 – Output Compare 1           | 6      | 6           | IFS0<6>       | IEC0<6>                | IPC1<20:18> | IPC1<17:16>  |  |  |

| INT1 – External Interrupt 1      | 7      | 7           | IFS0<7>       | IEC0<7>                | IPC1<28:26> | IPC1<25:24>  |  |  |

| T2 – Timer2                      | 8      | 8           | IFS0<8>       | IEC0<8>                | IPC2<4:2>   | IPC2<1:0>    |  |  |

| IC2 – Input Capture 2            | 9      | 9           | IFS0<9>       | IEC0<9>                | IPC2<12:10> | IPC2<9:8>    |  |  |

| OC2 – Output Compare 2           | 10     | 10          | IFS0<10>      | IEC0<10>               | IPC2<20:18> | IPC2<17:16>  |  |  |

| INT2 – External Interrupt 2      | 11     | 11          | IFS0<11>      | IEC0<11>               | IPC2<28:26> | IPC2<25:24>  |  |  |

| T3 – Timer3                      | 12     | 12          | IFS0<12>      | IEC0<12>               | IPC3<4:2>   | IPC3<1:0>    |  |  |

| IC3 – Input Capture 3            | 13     | 13          | IFS0<13>      | IEC0<13>               | IPC3<12:10> | IPC3<9:8>    |  |  |

| OC3 – Output Compare 3           | 14     | 14          | IFS0<14>      | IEC0<14>               | IPC3<20:18> | IPC3<17:16>  |  |  |

| INT3 – External Interrupt 3      | 15     | 15          | IFS0<15>      | IEC0<15>               | IPC3<28:26> | IPC3<25:24>  |  |  |

| T4 – Timer4                      | 16     | 16          | IFS0<16>      | IEC0<16>               | IPC4<4:2>   | IPC4<1:0>    |  |  |

| IC4 – Input Capture 4            | 17     | 17          | IFS0<17>      | IEC0<17>               | IPC4<12:10> | IPC4<9:8>    |  |  |

| OC4 – Output Compare 4           | 18     | 18          | IFS0<18>      | IEC0<18>               | IPC4<20:18> | IPC4<17:16>  |  |  |

| INT4 – External Interrupt 4      | 19     | 19          | IFS0<19>      | IEC0<19>               | IPC4<28:26> | IPC4<25:24>  |  |  |

| T5 – Timer5                      | 20     | 20          | IFS0<20>      | IEC0<20>               | IPC5<4:2>   | IPC5<1:0>    |  |  |

| IC5 – Input Capture 5            | 21     | 21          | IFS0<21>      | IEC0<21>               | IPC5<12:10> | IPC5<9:8>    |  |  |

| OC5 – Output Compare 5           | 22     | 22          | IFS0<22>      | IEC0<22>               | IPC5<20:18> | IPC5<17:16>  |  |  |

| SPI1E – SPI1 Fault               | 23     | 23          | IFS0<23>      | IEC0<23>               | IPC5<28:26> | IPC5<25:24>  |  |  |

| SPI1RX – SPI1 Receive Done       | 24     | 23          | IFS0<24>      | IEC0<24>               | IPC5<28:26> | IPC5<25:24>  |  |  |

| SPI1TX – SPI1 Transfer Done      | 25     | 23          | IFS0<25>      | IEC0<25>               | IPC5<28:26> | IPC5<25:24>  |  |  |

| U1E – UART1 Error                |        |             |               |                        |             |              |  |  |

| SPI3E – SPI3 Fault               | 26     | 24          | IFS0<26>      | IEC0<26>               | IPC6<4:2>   | IPC6<1:0>    |  |  |

| I2C3B – I2C3 Bus Collision Event |        |             |               |                        |             |              |  |  |

| U1RX – UART1 Receiver            |        |             |               |                        |             |              |  |  |

| SPI3RX – SPI3 Receive Done       | 27     | 24          | IFS0<27>      | IEC0<27>               | IPC6<4:2>   | IPC6<1:0>    |  |  |

| I2C3S - I2C3 Slave Event         |        |             |               |                        |             |              |  |  |

| U1TX – UART1 Transmitter         |        |             |               |                        |             |              |  |  |

| SPI3TX – SPI3 Transfer Done      | 28     | 24          | IFS0<28>      | IEC0<28>               | IPC6<4:2>   | IPC6<1:0>    |  |  |

| I2C3M – I2C3 Master Event        | 1      |             |               |                        |             |              |  |  |

| I2C1B – I2C1 Bus Collision Event | 29     | 25          | IFS0<29>      | IEC0<29>               | IPC6<12:10> | IPC6<9:8>    |  |  |

| I2C1S – I2C1 Slave Event         | 30     | 25          | IFS0<30>      | IEC0<30>               | IPC6<12:10> | IPC6<9:8>    |  |  |

| I2C1M – I2C1 Master Event        | 31     | 25          | IFS0<31>      | IEC0<31>               | IPC6<12:10> | IPC6<9:8>    |  |  |

| CN – Input Change Interrupt      | 32     | 26          | IFS1<0>       | IEC1<0>                | IPC6<20:18> | IPC6<17:16>  |  |  |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX5XX USB and CAN Features", TABLE 2: "PIC32MX6XX USB and Ethernet Features" and TABLE 3: "PIC32MX7XX USB, Ethernet, and CAN Features" for the list of available peripherals.

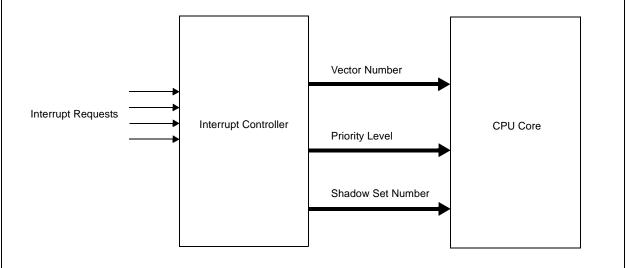

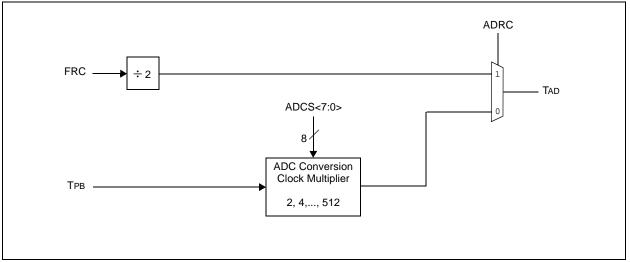

## 8.0 OSCILLATOR CONFIGURATION

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32). The Oscillator module has the following features:

- A total of four external and internal oscillator options as clock sources

- On-chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

Figure 8-1shows the Oscillator module block diagram.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        | LTAGBOOT          | —                 | _                 | -                 | —                 | _                 | _                | —                |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 10.0         | LTAG<11:4>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |

| 7:0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |  |  |

## REGISTER 9-3: CHETAG: CACHE TAG REGISTER

## Legend:

| 3                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31 LTAGBOOT: Line Tag Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line Tag Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

#### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   |                   | _                 | _                 |                  |                  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   | _                 | _                 |                  | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   |                   |                   |                   | _                 | _                 |                  | -                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

|              | _                 |                   |                   |                   |                   |                   | FRMH<2:0>        |                  |

## REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

|-------------------|------------------|--------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** Upper 3 bits of the Frame Numbers bits These register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                   | _                 |                   | —                 |                   | _                 |                  | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.6         | —                 | _                 | —                 | —                 | —                 | _                 | —                | —                |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   | PID<              | :3:0>             |                   | EP<3:0>           |                   |                  |                  |  |

## REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-4 PID<3:0>: Token Type Indicator bits<sup>(1)</sup> 1101 = SETUP (TX) token type transaction 1001 = IN (RX) token type transaction 0001 = OUT (TX) token type transaction Note: All other values not listed, are Reserved and must not be used.

## bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

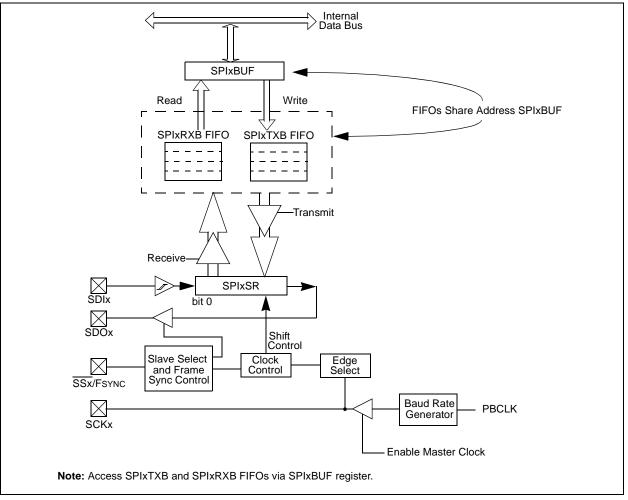

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX5XX/6XX/7XX family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. The following are some of the key features of the SPI module:

- Master mode and Slave mode support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs

- based on 32/16/8-bit data width

Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

## 22.1 Control Registers

## TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 |           |              | Bits    |         |                       |             |                   |                   |            |              |          |            |              |         |         |         |       |            |

|-----------------------------|---------------------------------|-----------|--------------|---------|---------|-----------------------|-------------|-------------------|-------------------|------------|--------------|----------|------------|--------------|---------|---------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15        | 30/14   | 29/13   | 28/12                 | 27/11       | 26/10             | 25/9              | 24/8       | 23/7         | 22/6     | 21/5       | 20/4         | 19/3    | 18/2    | 17/1    | 16/0  | All Resets |

| 0200                        | RTCCON                          | 31:16     | _            | _       | —       | —                     | _           | _                 |                   |            |              |          | CAL<       | 9:0>         |         |         |         |       | 0000       |

| 0200                        | RICCON                          | 15:0      | ON           | _       | SIDL    | —                     | —           | _                 |                   |            | RTSECSEL     | RTCCLKON |            |              | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000       |

| 0210                        | RTCALRM                         | 31:16     | _            | _       | _       | —                     | —           | _                 |                   |            | —            | _        |            |              | —       |         | _       | —     | 0000       |

| 0210                        | RICALKI                         | 15:0      | ALRMEN       | CHIME   | PIV     | ALRMSYNC              |             | AMASI             | <b>&lt;</b> <3:0> |            | ARPT<7:0>    |          |            |              |         | 0000    |         |       |            |

| 0220                        | RTCTIME                         | 31:16     |              | HR10    | 0<3:0>  |                       | HR01<3:0>   |                   |                   | MIN10<3:0> |              |          | MIN01<3:0> |              |         | xxxx    |         |       |            |

| 0220                        | RICTIVIE                        | 15:0      |              | SEC1    | 0<3:0>  |                       |             | SEC0 <sup>2</sup> | <3:0>             |            | _            | _        | -          |              | -       | -       | _       | —     | xx00       |

| 0000                        | RTCDATE                         | 31:16     |              | YEAR'   | 10<3:0> |                       | YEAR01<3:0> |                   |                   |            | MONTH10<3:0> |          |            | MONTH01<3:0> |         |         | xxxx    |       |            |

| 0230                        | RICDATE                         | 15:0      |              | DAY1    | 0<3:0>  |                       |             | DAY01             | l<3:0>            |            | _            | _        | -          |              |         | WDAYC   | )1<3:0> |       | xx00       |

| 0040                        |                                 | 31:16     |              | HR10    | )<3:0>  |                       |             | HR01              | <3:0>             |            | MIN10<3:0>   |          |            |              | MIN01   | <3:0>   |         | xxxx  |            |

| 0240                        | ALRMTIME                        | 15:0      |              | SEC1    | 0<3:0>  |                       | SEC01<3:0>  |                   |                   | _          | _            | —        | —          | _            | —       | _       | _       | xx00  |            |

| 0050                        |                                 | 31:16     | _            |         | _       | —                     | _           |                   |                   |            |              | MONTH1   | 0<3:0>     |              |         | MONTH   | 01<3:0> |       | 00xx       |

| 0250                        | ALRMDATE                        | 15:0      |              | DAY1    | 0<3:0>  |                       |             | DAY01<3:0>        |                   |            | _            | _        | _          | _            |         | WDAYC   | )1<3:0> |       | xx0x       |

| l egen                      | ، بام                           |           | n voluo on D | aaati u |         | hrown value on Reset: |             |                   |                   |            |              |          |            |              |         |         |         |       |            |

PIC32MX5XX/6XX/7XX

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.1.1 "CLR, SET and INV Registers" for more information.

# PIC32MX5XX/6XX/7XX

## REGISTER 24-2: CiCFG: CAN BAUD RATE CONFIGURATION REGISTER (CONTINUED)

```

bit 10-8 PRSEG<2:0>: Propagation Time Segment bits<sup>(4)</sup>

111 = \text{Length is 8 x Tq}

000 = \text{Length is } 1 \times TQ

SJW<1:0>: Synchronization Jump Width bits<sup>(3)</sup>

bit 7-6

11 = \text{Length is } 4 \times \text{Tq}

10 = Length is 3 x TQ

01 = Length is 2 x TQ

00 = \text{Length is } 1 \times TQ

BRP<5:0>: Baud Rate Prescaler bits

bit 5-0

111111 = TQ = (2 x 64)/FSYS

111110 = TQ = (2 x 63)/FSYS

000001 = TQ = (2 \times 2)/FSYS

000000 = TQ = (2 \times 1)/FSYS

Note 1: SEG2PH \leq SEG1PH. If SEG2PHTS is clear, SEG2PH will be set automatically.

2: 3 Time bit sampling is not allowed for BRP < 2.

```

- $\textbf{3:} \quad SJW \leq SEG2PH.$

- **4:** The Time Quanta per bit must be greater than 7 (that is, TQBIT > 7).

Note: This register can only be modified when the CAN module is in Configuration mode (OPMOD<2:0> (CiCON<23:21>) = 100).

## **REGISTER 24-21:** CiFIFOINTn: CAN FIFO INTERRUPT REGISTER 'n' (n = 0 THROUGH 31)

- bit 9 TXHALFIF: FIFO Transmit FIFO Half Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is  $\leq$  half full 0 = FIFO is > half full TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 8 **TXEMPTYIF:** Transmit FIFO Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) 1 = FIFO is empty 0 = FIFO is not empty, at least 1 message queued to be transmitted TXEN = 0: (FIFO configured as a receive buffer) Unused, reads '0' bit 7-4 Unimplemented: Read as '0' bit 3 **RXOVFLIF:** Receive FIFO Overflow Interrupt Flag bit TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = Overflow event has occurred 0 = No overflow event occured bit 2 **RXFULLIF:** Receive FIFO Full Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is full 0 = FIFO is not full RXHALFIF: Receive FIFO Half Full Interrupt Flag bit<sup>(1)</sup> bit 1 TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is  $\geq$  half full 0 = FIFO is < half full bit 0 **RXNEMPTYIF:** Receive Buffer Not Empty Interrupt Flag bit<sup>(1)</sup> TXEN = 1: (FIFO configured as a transmit buffer) Unused, reads '0' TXEN = 0: (FIFO configured as a receive buffer) 1 = FIFO is not empty, has at least 1 message 0 = FIFO is empty

- Note 1: This bit is read-only and reflects the status of the FIFO.

The processor will exit, or 'wake-up', from Sleep mode on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep mode. The interrupt priority must be greater than the current CPU priority.

- On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

## 28.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a WAIT instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- · On any form of device Reset

- On a WDT time-out interrupt

#### 28.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The Peripheral Bus (PB) can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as USB, interrupt controller, DMA, bus matrix and prefetch cache are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

## TABLE 32-13: COMPARATOR SPECIFICATIONS

| DC CHA        |        | STICS                                 | $\begin{array}{l} \mbox{Standard Operating Conditions (see Note 3): 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-Temp} \end{array}$ |         |      |       |                                                                                        |  |  |

|---------------|--------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol | Characteristics                       | Min.                                                                                                                                                                                                                                                                                           | Typical | Max. | Units | Comments                                                                               |  |  |

| D300          | Vioff  | Input Offset Voltage                  | —                                                                                                                                                                                                                                                                                              | ±7.5    | ±25  | mV    | Avdd = Vdd,<br>Avss = Vss                                                              |  |  |

| D301          | VICM   | Input Common Mode Voltage             | 0                                                                                                                                                                                                                                                                                              | —       | Vdd  | V     | Avdd = Vdd,<br>Avss = Vss<br>(Note 2)                                                  |  |  |

| D302          | CMRR   | Common Mode Rejection Ratio           | 55                                                                                                                                                                                                                                                                                             | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |  |  |

| D303          | TRESP  | Response Time                         | —                                                                                                                                                                                                                                                                                              | 150     | 400  | ns    | AVDD = VDD,<br>AVss = Vss<br>(Notes 1, 2)                                              |  |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid |                                                                                                                                                                                                                                                                                                |         | 10   | μS    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |  |  |

| D305          | IVref  | Internal Voltage Reference            | 0.57                                                                                                                                                                                                                                                                                           | 0.6     | 0.63 | V     | For devices without<br>BGSEL<1:0>                                                      |  |  |

|               |        |                                       | 1.14                                                                                                                                                                                                                                                                                           | 1.2     | 1.26 | V     | BGSEL<1:0> = 00                                                                        |  |  |

|               |        |                                       | 0.57                                                                                                                                                                                                                                                                                           | 0.6     | 0.63 | V     | BGSEL<1:0> = 01                                                                        |  |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

2: These parameters are characterized but not tested.

**3:** The Comparator module is functional at VBORMIN < VDD < VDDMIN, but with degraded performance. Unless otherwise stated, module functionality is tested, but not characterized.

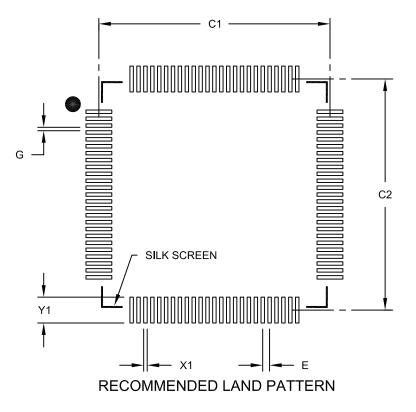

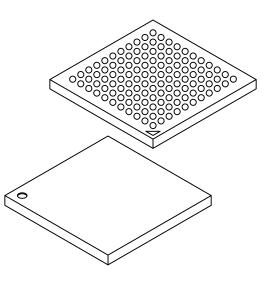

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |

|---------------------------|-------------|------|----------|------|

| Dimensior                 | n Limits    | MIN  | NOM      | MAX  |

| Contact Pitch             | E           |      | 0.40 BSC |      |

| Contact Pad Spacing       | C1          |      | 13.40    |      |

| Contact Pad Spacing       | C2          |      | 13.40    |      |

| Contact Pad Width (X100)  | X1          |      |          | 0.20 |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |

| Distance Between Pads     | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

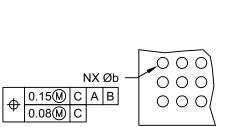

# 121-Ball Plastic Thin Profile Fine Pitch Ball Grid Array (BG) - 10x10x1.10 mm Body [TFBGA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

DETAIL B

|                    | Units    |          |           |      |  |  |

|--------------------|----------|----------|-----------|------|--|--|

| Dimension          | l Limits | MIN      | NOM       | MAX  |  |  |

| Number of Contacts | N        |          | 121       |      |  |  |

| Contact Pitch      | е        | 0.80 BSC |           |      |  |  |

| Overall Height     | Α        | 1.00     | 1.10      | 1.20 |  |  |

| Ball Height        | A1       | 0.25     | 0.30      | 0.35 |  |  |

| Overall Width      | E        |          | 10.00 BSC |      |  |  |

| Array Width        | E1       |          | 8.00 BSC  |      |  |  |

| Overall Length     | D        |          | 10.00 BSC |      |  |  |

| Array Length       | D1       | 8.00 BSC |           |      |  |  |

| Contact Diameter   | b        | 0.35     | 0.40      | 0.45 |  |  |

Notes:

- 1. Ball A1 visual index feature may vary, but must be located within the hatched area.

- 2. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances. REF: Reference Dimension, usually without tolerance, for information purposes only.

- 3. The outer rows and colums of balls are located with respect to datums A and B.

- 4. Ball interface to package body: 0.37mm nominal diameter.

Microchip Technology Drawing C04-148 Rev F Sheet 2 of 2

## TABLE B-7: MAJOR SECTION UPDATES (CONTINUED)

| Section Name                      | Update Description                                                                                                   |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------|

| 32.0 "Electrical Characteristics" | Note 4 in the Operating Current specification was updated (see Table 32-5).                                          |

|                                   | Note 3 in the Idle Current specification was updated (see Table 32-6).                                               |

|                                   | Note 6 references in the Power-Down Current specification were updated (see Table 32-7).                             |

|                                   | The Program Memory parameters, D135, D136, and D137, and Note 4 were updated (see Table 32-11).                      |

|                                   | The Voltage Reference Specifications were updated (see Table 32-14).                                                 |

|                                   | Parameter DO50 (Cosco) was added to the Capacitive Loading Requirements on Output Pins (see Table 32-16).            |

|                                   | The EJTAG Timing Characteristics were updated (see Figure 32-28).                                                    |

|                                   | The maximum value for parameters ET13 and ET14 were updated in the Ethernet Module Specifications (see Table 32-35). |

|                                   | Parameter PM7 (TDHOLD) was updated (see Table 32-40).                                                                |

| 34.0 "Packaging Information"      | Packaging diagrams were updated.                                                                                     |

| Product Identification System     | The Speed and Program Memory Size were updated and Note 1 was added.                                                 |